(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-60856

(P2010-60856A)

(43) 公開日 平成22年3月18日(2010.3.18)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2 H 0 9 3   |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 2 H 1 9 3   |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 5 C 0 0 6   |

|                             | G09G 3/20 | 5 C 0 8 0   |

|                             | G09G 3/20 | 6 2 3 D     |

審査請求 未請求 請求項の数 4 O L (全 27 頁) 最終頁に続く

|           |                              |          |                                               |

|-----------|------------------------------|----------|-----------------------------------------------|

| (21) 出願番号 | 特願2008-226644 (P2008-226644) | (71) 出願人 | 502356528<br>株式会社 日立ディスプレイズ<br>千葉県茂原市早野3300番地 |

| (22) 出願日  | 平成20年9月4日 (2008.9.4)         | (74) 代理人 | 100083552<br>弁理士 秋田 収喜                        |

|           |                              | (74) 代理人 | 100103746<br>弁理士 近野 恵一                        |

|           |                              | (72) 発明者 | 桶 隆太郎<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内    |

|           |                              | (72) 発明者 | 小野 記久雄<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内   |

最終頁に続く

## (54) 【発明の名称】表示装置

## (57) 【要約】

【課題】 液晶表示装置の画質の低下を防ぐ。

【解決手段】 第1の電極および第2の電極を有する画素がマトリクス状に配置されており、隣接する第1の映像信号線と第2の映像信号線との間には、第1の映像信号線に接続された第1の電極と、第2の映像信号線に接続された第1の電極とが交互に配置されている表示装置であって、1フレーム期間を同じ長さのR個の1/Rフレーム期間に分割し、1フレーム期間中に1本の映像信号線に加える階調電圧の電位と第2の電極に加える電圧の電位との高低の関係は1/Rフレーム期間毎に反転しており、1個の1/Rフレーム期間に第1の映像信号線に加える階調電圧の電位と第2の電極に加える電圧の電位の関係と第2の映像信号線に加える階調電圧の電位と第2の電極に加える電圧の電位の関係とは逆の関係になっており、かつ、個数Rが2以上走査信号線の本数以下の整数のいずれかである表示装置。

【選択図】

図9 (b)

## 【特許請求の範囲】

## 【請求項 1】

第1の電極および第2の電極を有する画素がマトリクス状に配置されている表示パネルと、前記第1の電極に第1の電圧を加える第1の回路と、前記第2の電極に第2の電圧を加える第2の回路とを有し、

前記表示パネルは、複数個の前記第1の電極、1個または複数個の前記第2の電極、複数本の走査信号線、複数本の映像信号線、および複数個のTFT素子を有する表示装置であって、

前記複数個の前記第1の電極は、それぞれ、前記TFT素子を介して1本の前記映像信号線に接続しており、

隣接する第1の映像信号線と第2の映像信号線との間には、前記TFT素子を介して前記第1の映像信号線に接続された前記第1の電極と、前記TFT素子を介して前記第2の映像信号線に接続された前記第1の電極とが、前記映像信号線の延在方向に沿って交互に配置されており、

前記映像信号線を挟んで隣接する2個の前記第1の電極は、それぞれ、前記TFT素子を介して接続している前記映像信号線との向きの関係が同じ関係であり、

前記第2の回路は、それぞれの前記画素の前記第2の電極に、あらかじめ定められた電位の前記第2の電圧を加え、

前記第1の回路は、それぞれの前記画素の前記第1の電極に前記第1の電圧を加えるときには、

前記映像信号線を挟んで隣接する2個の前記第1の電極に加える前記第1の電圧は、一方の前記第1の電極に加える前記第1の電圧の電位と前記第2の電圧の電位との高低の関係と、他方の前記第1の電極に加える前記第1の電圧の電位と前記第2の電圧の電位との高低の関係とが、逆の関係になり、

1本の前記映像信号線に前記TFT素子を介して接続された複数個の前記第1の電極に加える前記第1の電圧は、当該複数個の前記第1の電極のすべてに1回ずつ前記第1の電圧を加える1フレーム期間を、概ね同じ長さのR個の1/Rフレーム期間に分割し、

1個の前記1/Rフレーム期間に前記映像信号線を介して前記第1の電極に加える前記第1の電圧は、当該第1の電圧の電位と前記第2の電圧の電位との高低の関係が同じ関係になり、かつ、

前記1フレーム期間において連続する2個の前記1/Rフレーム期間に前記映像信号線を介して前記第1の電極に加える前記第1の電圧は、一方の前記1/Rフレーム期間における前記第1の電圧の電位と前記第2の電圧の電位との高低の関係と、他方の前記1/Rフレーム期間における前記第1の電圧の電位と前記第2の電圧の電位との高低の関係とが、逆の関係になるように加え、

1フレーム期間における前記1/Rフレーム期間の個数Rは、2以上、前記走査信号線の本数以下の整数のいずれかであることを特徴とする表示装置。

## 【請求項 2】

前記第1の回路は、前記複数個の前記第1の電極に前記第1の電圧を加えるときに、それぞれの前記画素における前記第1の電圧の電位と前記第2の電圧の電位との関係が、前記1フレーム期間毎に逆の関係になるように加えることを特徴とする請求項1に記載の表示装置。

## 【請求項 3】

前記1フレーム期間における前記1/Rフレーム期間の個数Rは、3以上20以下の整数のいずれかであることを特徴とする請求項1に記載の表示装置。

## 【請求項 4】

前記表示パネルは、2枚の基板の間に液晶材料を封入した液晶表示パネルであることを特徴とする請求項1に記載の表示装置。

## 【発明の詳細な説明】

## 【技術分野】

10

20

30

40

50

## 【0001】

本発明は、表示装置に関し、特に、隣接する2本の映像信号線との間に、一方の映像信号線に接続された画素電極と、他方の映像信号線に接続された画素電極とが交互に配置されている液晶表示装置に適用して有効な技術に関するものである。

## 【背景技術】

## 【0002】

従来、アクティブマトリクス方式の液晶表示装置（以下、単に液晶表示装置という）は、たとえば、テレビやパーソナル・コンピュータ（P C）用のディスプレイなどに用いられている。また、液晶表示装置は、たとえば、携帯電話端末、P D A、および携帯型ゲーム機などの携帯型電子機器の表示部にも用いられている。

10

## 【0003】

液晶表示装置は、2枚の基板の間に液晶材料を封入した液晶表示パネル、および当該液晶表示パネルを駆動する駆動回路を有する。また、液晶表示装置は、非発光型の表示装置であり、たとえば、液晶表示パネルの背面側にバックライト（面状照明装置）が配置されている。

## 【0004】

液晶表示パネルの表示領域は、画素電極および対向電極（共通電極と呼ぶこともある）を有する画素がマトリクス状に配置されており、画素電極と対向電極の電位差により液晶材料中の液晶分子の向きを制御し、それぞれの画素の階調（明るさ）を制御する。

20

## 【0005】

また、液晶表示パネルは、複数本の走査信号線、複数本の映像信号線、複数個のアクティブ素子を有する。アクティブ素子は、たとえば、T F T 素子であり、表示領域にマトリクス状に配置されている。このとき、それぞれのT F T 素子は、ゲートが走査信号線に接続しており、ドレインが映像信号線に接続している。また、それぞれのT F T 素子のソースには、画素電極が接続している。

## 【0006】

ところで、液晶表示パネルを駆動するときには、たとえば、それぞれの画素の対向電極に加えるコモン電圧の電位を一定にしておき、画素電極に加える階調電圧の電位を変えることで、それぞれの画素の階調を制御する。このとき、それぞれの画素における階調電圧の電位とコモン電圧の電位との高低の関係は、あらかじめ定められたフレーム期間毎（たとえば、1フレーム期間毎）に反転させる。以下、それぞれの画素における階調電圧の電位とコモン電圧の電位との高低の関係を、画素の極性という。また、階調電圧の電位がコモン電圧の電位よりも高い場合を正極性といい、階調電圧の電位がコモン電圧の電位よりも低い場合を負極性という。

30

## 【0007】

また、液晶表示パネルの駆動方法には、たとえば、列毎反転駆動、ライン反転駆動、およびドット反転駆動などの駆動方法がある。

## 【0008】

従来の一般的な液晶表示パネルにおいて、隣接する2本の映像信号線の間に、映像信号線の延在方向に沿って配置された複数個の画素電極は、通常、すべての画素電極が、T F T 素子（アクティブ素子）を介して同じ1本の映像信号線に接続している。そのため、このような液晶表示パネルをドット反転駆動で駆動する場合、駆動回路の消費電力および発熱量が増加するという問題がある。

40

## 【0009】

上記のような問題に対し、近年、たとえば、隣接する2本の映像信号線との間に、一方の映像信号線に接続された画素電極と、他方の映像信号線に接続された画素電極とを交互に配置した液晶表示パネルが提案されている（たとえば、特許文献1を参照。）。

## 【特許文献1】特開2007-47664号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

50

## 【0010】

液晶表示パネルのそれぞれの画素は、その構成から、たとえば、画素電極と映像信号線との間に生じる寄生容量を有する。1つの画素の画素電極は、通常、隣接する2本の映像信号線の間に配置されている。そのため、1つの画素には、隣接する2本の映像信号線のうちの一方の映像信号線との間に第1の寄生容量が生じ、他方の映像信号線との間に第2の寄生容量が生じる。

## 【0011】

液晶表示パネルの一方の基板に映像信号線および画素電極を形成する場合、映像信号線と画素電極は、それぞれ別の工程で形成する。このとき、隣接する第1の映像信号線と第2の映像信号線との間に配置する画素電極は、通常、第1の映像信号線との平面距離と、第2の映像信号線との平面距離とが同じ距離になるように形成される。

10

## 【0012】

しかしながら、映像信号線を形成する工程、および画素電極を形成する工程は、それぞれ、フォトリソグラフィー技術を用いて形成する。そのため、隣接する第1の映像信号線と第2の映像信号線との間に配置される画素電極の形成位置にずれが生じ、たとえば、第1の映像信号線との平面距離と、第2の映像信号線との平面距離とが異なる距離になることがある。

## 【0013】

また、第1の映像信号線と第2の映像信号線との間に配置された複数個の画素電極の形成位置に、走査信号線の延在方向に沿ったずれが生じる場合、通常、すべての画素電極の形成位置が同じ方向、すなわち、第1の映像信号線側または第2の映像信号線側のいずれかにずれる。

20

## 【0014】

このように、画素電極の形成位置が第1の映像信号線側または第2の映像信号線側にずれると、たとえば、画素電極と第1の映像信号線との間に生じる第1の寄生容量の大きさと、当該画素電極と第2の映像信号線との間に生じる第2の寄生容量の大きさに違いが生じ、画素電極の電位が変動する。

## 【0015】

特許文献1に記載されたような液晶表示パネルをドット反転駆動で駆動する場合、1フレーム期間中、第1の映像信号線に入力される階調電圧の電位とコモン電圧の電位との高低の関係、および第2の映像信号線に入力される階調電圧の電位とコモン電圧の電位との高低の関係は、それぞれ常に同じ関係である。また、1フレーム期間中に、第1の映像信号線に入力される階調電圧の電位とコモン電圧の電位との高低の関係と、第2の映像信号線に入力される階調電圧の電位とコモン電圧の電位との高低の関係とは、反対の関係である。

30

## 【0016】

したがって、特許文献1に記載されたような液晶表示パネルをドット反転駆動で駆動する場合、画素電極と第1の映像信号線との間に生じる第1の寄生容量の大きさと、当該画素電極と第2の映像信号線との間に生じる第2の寄生容量の大きさに違いが生じると、たとえば、画素電極の電位の変動に偏りが生じ、画質が低下するという問題があった。

40

## 【0017】

本発明の目的は、液晶表示装置の画質の低下を防ぐことが可能な技術を提供することにある。

## 【0018】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面によって明らかになるであろう。

## 【課題を解決するための手段】

## 【0019】

本願において開示される発明のうち、代表的なものの概略を説明すれば、以下の通りである。

50

## 【0020】

(1) 第1の電極および第2の電極を有する画素がマトリクス状に配置されている表示パネルと、前記第1の電極に第1の電圧を加える第1の回路と、前記第2の電極に第2の電圧を加える第2の回路とを有し、前記表示パネルは、複数個の前記第1の電極、1個または複数個の前記第2の電極、複数本の走査信号線、複数本の映像信号線、および複数個のTFT素子を有する表示装置であって、前記複数個の前記第1の電極は、それぞれ、前記TFT素子を介して1本の前記映像信号線に接続しており、隣接する第1の映像信号線と第2の映像信号線との間には、前記TFT素子を介して前記第1の映像信号線に接続された前記第1の電極と、前記TFT素子を介して前記第2の映像信号線に接続された前記第1の電極とが、前記映像信号線の延在方向に沿って交互に配置されており、前記映像信号線を挟んで隣接する2個の前記第1の電極は、それぞれ、前記TFT素子を介して接続している前記映像信号線との向きの関係が同じ関係であり、前記第2の回路は、それぞれの前記画素の前記第2の電極に、あらかじめ定められた電位の前記第2の電圧を加え、前記第1の回路は、それぞれの前記画素の前記第1の電極に前記第1の電圧を加えるときに、前記映像信号線を挟んで隣接する2個の前記第1の電極に加える前記第1の電圧は、一方の前記第1の電極に加える前記第1の電圧の電位と前記第2の電圧の電位との高低の関係と、他方の前記第1の電極に加える前記第1の電圧の電位と前記第2の電圧との高低の関係とが、逆の関係になり、1本の前記映像信号線に前記TFT素子を介して接続された複数個の前記第1の電極に加える前記第1の電圧は、当該複数個の前記第1の電極のすべてに1回ずつ前記第1の電圧を加える1フレーム期間を、概ね同じ長さのR個の1/Rフレーム期間に分割し、1個の前記1/Rフレーム期間に前記映像信号線を介して前記第1の電極に加える前記第1の電圧は、当該第1の電圧の電位と前記第2の電圧の電位との高低の関係が同じ関係になり、かつ、前記1フレーム期間において連続する2個の前記1/Rフレーム期間に前記映像信号線を介して前記第1の電極に加える前記第1の電圧は、一方の前記1/Rフレーム期間における前記第1の電圧の電位と前記第2の電圧の電位との高低の関係と、他方の前記1/Rフレーム期間における前記第1の電圧の電位と前記第2の電圧との高低の関係とが、逆の関係になるように加え、1フレーム期間における前記1/Rフレーム期間の個数Rは、2以上、前記走査信号線の本数以下の整数のいずれかである表示装置。

## 【0021】

(2) 前記(1)の表示装置において、前記第1の回路は、前記複数個の前記第1の電極に前記第1の電圧を加えるときに、それぞれの前記画素における前記第1の電圧の電位と前記第2の電圧の電位との関係が、前記1フレーム期間毎に逆の関係になるように加える表示装置。

## 【0022】

(3) 前記(1)の表示装置において、前記1フレーム期間における前記1/Rフレーム期間の個数Rは、3以上20以下の整数のいずれかである表示装置。

## 【0023】

(4) 前記(1)の表示装置において、前記表示パネルは、2枚の基板の間に液晶材料を封入した液晶表示パネルである表示装置。

## 【発明の効果】

## 【0024】

本発明の表示装置によれば、液晶表示装置の画質の低下を防ぐことができる。

## 【発明を実施するための最良の形態】

## 【0025】

以下、本発明について、図面を参照して実施の形態(実施例)とともに詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

## 【0026】

10

20

30

40

50

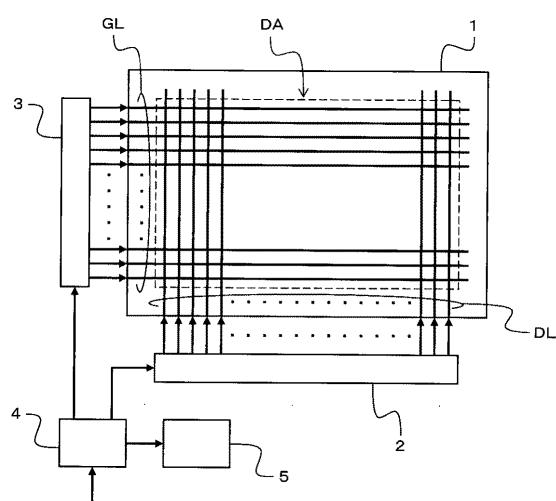

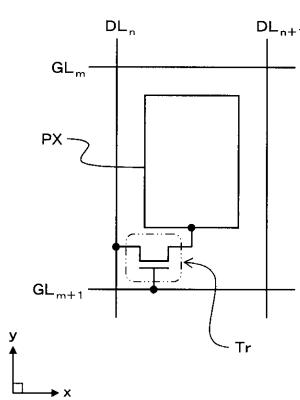

図1( a )乃至図1( c )は、本発明に関わる液晶表示装置の概略構成の一例を示す模式図である。

図1( a )は、液晶表示装置の概略構成の一例を示す模式図である。図1( b )は、液晶表示パネルの1つの画素の回路構成の一例を示す模式図である。図1( c )は、液晶表示パネルの1つの画素の回路構成の別の表現方法の一例を示す模式図である。

【0027】

本発明は、たとえば、液晶表示装置に適用される。液晶表示装置は、たとえば、図1( a )に示すように、液晶表示パネル1、第1の駆動回路2、第2の駆動回路3、制御回路4、およびバックライト5を有する。

【0028】

液晶表示パネル1は、第1の基板および第2の基板の2枚の基板の間に液晶材料を封入した表示パネルである。このとき、第1の基板には、たとえば、複数本の走査信号線GLおよび複数本の映像信号線DLが設けられている。なお、図1( a )には、複数本の走査信号線GLのうちの一部、および複数本の映像信号線DLのうちの一部のみを示しており、実際の液晶表示パネルには、さらに多数本の走査信号線GLおよび映像信号線DLが設けられている。

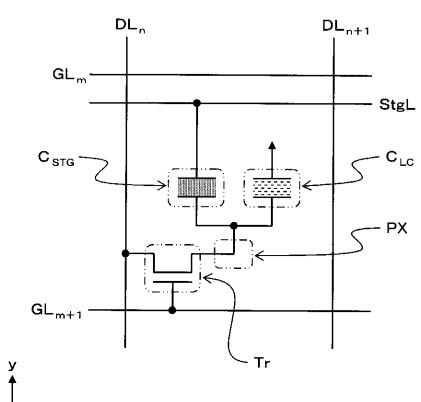

【0029】

液晶表示パネル1の表示領域DAは、複数の画素がマトリクス状に配置されており、表示領域DAにおいて1つの画素が占有する領域は、隣接する2本の走査信号線GLと隣接する2本の映像信号線DLとで囲まれる領域に相当する。このとき、1つの画素は、たとえば、図1( b )に示すように、TFT素子Tr(アクティブ素子)および画素電極PXを有する。また、1つの画素は、図1( b )には示していない対向電極を有し、画素電極PX、対向電極、および液晶材料による画素容量CLc(液晶容量と呼ぶこともある)が形成されている。また、1つの画素には、たとえば、画素電極PX、保持容量線StgL、および絶縁層による保持容量CSTG(補助容量または蓄積容量と呼ぶこともある)が形成されている。なお、近年の液晶表示パネルでは、保持容量CSTGを設けない場合もある。

【0030】

また、図1( b )に示した例では、TFT素子Trのゲートが、隣接する2本の走査信号線GL<sub>m</sub>、GL<sub>m+1</sub>のうちの下側の走査信号線GL<sub>m+1</sub>に接続しているが、これに限らず、上側の走査信号線GL<sub>m</sub>に接続してもよい。

【0031】

また、図1( b )に示した例では、TFT素子Trのドレインが、隣接する2本の映像信号線DL<sub>n</sub>、DL<sub>n+1</sub>のうちの左側の映像信号線DL<sub>n</sub>に接続しているが、本発明に関わる液晶表示装置では、後述するように、1つの表示領域DAにTFT素子Trのドレインが左側の映像信号線DL<sub>n</sub>に接続している画素と、右側の映像信号線DL<sub>n+1</sub>に接続している画素が存在する。

【0032】

なお、TFT素子Trのドレインとソースは、バイアスの関係、すなわちTFT素子Trがオンになったときの映像信号線DLの電位と画素電極PXの電位との関係によって入れ替わるが、本明細書では、映像信号線DLに接続しているほうをドレインという。

【0033】

また、1つの画素の回路構成を図示するときには、たとえば、図1( c )に示すように、TFT素子Trおよび画素電極PXのみを示すこともある。以下の説明で参照する図面において、画素の回路構成を図示するときには、図1( c )に示したような簡略化した構成で示す。

【0034】

第1の駆動回路2は、それぞれの各画素に加える階調電圧(映像信号)を生成し、映像信号線DLに出力する駆動回路である。第1の駆動回路2における階調電圧の生成方法については、後述する。

## 【0035】

第2の駆動回路3は、第1の駆動回路2から映像信号線DLに出力された階調電圧を加える画素（画素電極PX）を選択する駆動回路である。このとき、第2の駆動回路3は、複数本の走査信号線GLのそれぞれに、1フレーム期間を1周期とする走査信号を出力している。1本の走査信号線GLに出力する走査信号は、たとえば、1フレーム期間を走査信号線の本数で除した期間（1ライン選択期間）の間だけHレベルの電位であり、残りの期間はLレベルの電位であるような電圧信号である。また、それぞれの走査信号線GLに出力する走査信号は、電位がHレベルである期間が異なる。なお、Hレベルの電位は、TFT素子Trがオン（導通状態）になる電位であり、Lレベルの電位は、TFT素子Trがオフ（非導通状態）になる電位である。

10

## 【0036】

第1の駆動回路2および第2の駆動回路3は、それぞれ、たとえば、液晶表示パネル1または液晶表示パネル1に接続されたフレキシブルプリント配線板（図示しない）に搭載されたICチップに形成されていてもよいし、液晶表示パネル1（第1の基板）に内蔵されていてもよい。

## 【0037】

制御回路4は、外部からの入力信号や電力に基づき、第1の駆動回路2および第2の駆動回路3の動作、バックライト5の動作（たとえば、輝度）などを制御する回路である。また、制御回路4は、たとえば、対向電極や保持容量線StgLに加える電圧を生成する回路などが形成されている。

20

## 【0038】

バックライト5は、たとえば、冷陰極蛍光管などの蛍光管、発光ダイオード（LED）などの発光素子であり、当該発光素子が発した光は、図示していない反射板、光拡散板、プリズムシートなどをを利用して面状光線に変換した後、液晶表示パネル1に照射される。

## 【0039】

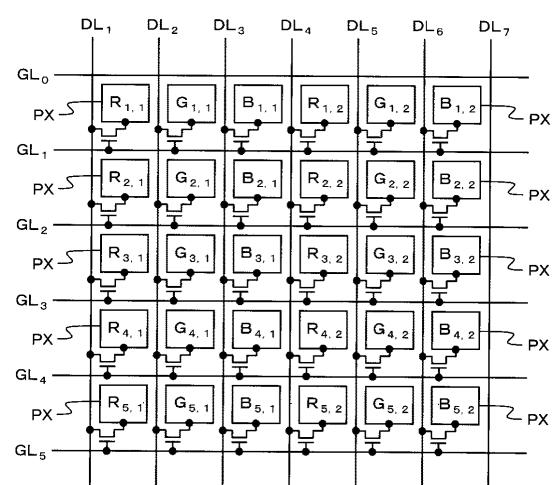

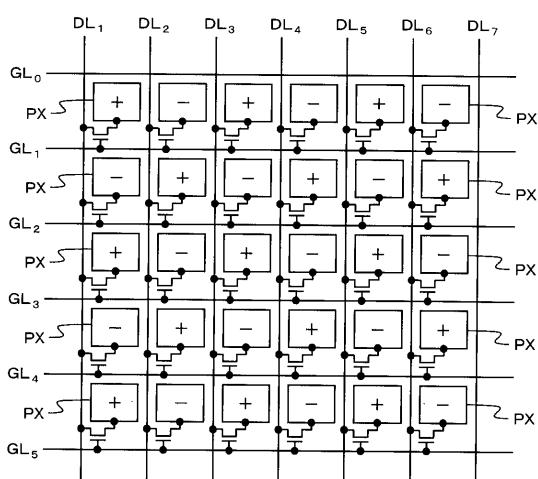

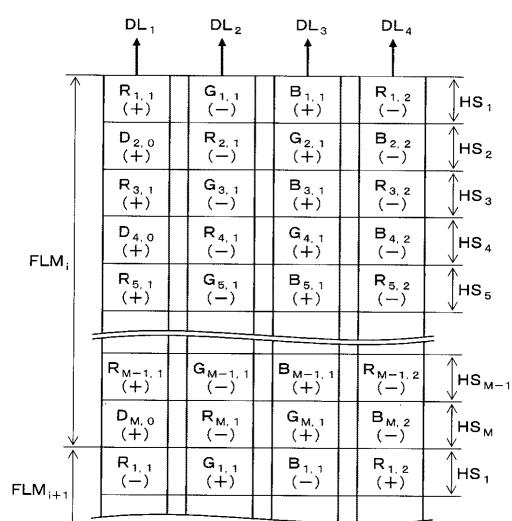

図2は、従来の液晶表示パネルにおける画素電極と映像信号線との接続方法の一例を示す模式図である。

なお、図2には、表示領域DAの左上の角部にある横6画素、縦5画素分の領域の画素の配置の一例を示している。また、図2において、それぞれの画素電極PXに記したR<sub>m,u</sub>、G<sub>m,u</sub>、B<sub>m,u</sub>（m=1, 2, 3, 4, 5, u=1, 2）は、それぞれの画素電極PXに加える階調電圧である。

30

## 【0040】

従来の一般的な液晶表示パネル1は、たとえば、図2に示すように、隣接する2本の映像信号線DL<sub>n</sub>、DL<sub>n+1</sub>（n=1, 2, 3, 4, 5, 6）の間に、映像信号線DL<sub>n</sub>の延在方向に沿って並んだ画素電極PXのそれぞれに接続しているTFT素子Trのドラインが、すべて同じ映像信号線DL<sub>n</sub>に接続している。このとき、隣接する2本の走査信号線GL<sub>m</sub>、GL<sub>m+1</sub>（m=0, 1, 2, 3, 4）の間に、走査信号線GL<sub>m</sub>の延在方向に沿って並んだ画素電極PXのそれぞれに接続しているTFT素子Trのゲートは、すべて同じ走査信号線GL<sub>m+1</sub>に接続している。なお、図2において、GL<sub>0</sub>は、ダミーの走査信号線である。

40

## 【0041】

以下、画素電極PXと映像信号線DL<sub>n</sub>との接続関係が、図2に示したような関係になっている液晶表示パネル1を、整列配置の液晶表示パネルという。

## 【0042】

液晶表示パネル1が、RGB方式のカラー表示に対応している場合、1つの画素は赤色（R）、緑色（G）、および青色（B）のうちのいずれか一色の階調表示を行う。このとき、映像や画像の1ドットの色は、一般に、走査信号線GL<sub>m</sub>の延在方向に沿って連続する3つの画素で表現し、添え字m, uの組み合わせが同じ階調電圧R<sub>m,n</sub>, G<sub>m,u</sub>, B<sub>m,u</sub>（たとえば、R<sub>1,1</sub>, G<sub>1,1</sub>, B<sub>1,1</sub>）が加えられる3つの画素で表現する。階調電圧R<sub>m,u</sub>が加えられる画素電極PXを有する画素は、赤色の階調表示を行う

50

画素であり、赤色のカラーフィルタを有する。階調電圧  $G_{m,u}$  が加えられる画素電極  $P_X$  を有する画素は、緑色の階調表示を行う画素であり、緑色のカラーフィルタを有する。階調電圧  $B_{m,u}$  が加えられる画素電極  $P_X$  を有する画素は、青色の階調表示を行う画素であり、青色のカラーフィルタを有する。

【0043】

整列配置の液晶表示パネル1を駆動するときには、たとえば、次のような駆動方法で駆動する。

【0044】

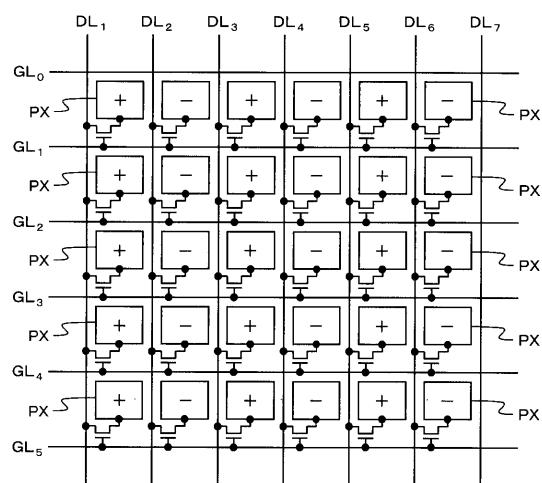

図3(a)および図3(b)は、図2に示した液晶表示パネルの駆動方法の一例を示す模式図である。

図3(a)は、液晶表示パネルを列毎反転駆動で駆動するときの画素の極性を示す模式図である。図3(b)は、階調電圧の出力方法の一例を示す模式図である。

なお、図3(a)には、図2と同じ部分、すなわち表示領域DAの左上の角部にある横6画素、縦5画素分の領域の画素の極性の一例を示している。

【0045】

液晶表示パネル1を駆動するときには、それぞれの画素において、画素電極  $P_X$  に加えた階調電圧と対向電極に加えたコモン電圧との電位差で変わる電界の強度により液晶材料中の液晶分子の向き(配向)を制御し、たとえば、バックライト5からの光の透過量を制御する。このとき、それぞれの画素における階調電圧の電位とコモン電圧の電位との高低の関係、すなわちそれぞれの画素の極性は、あらかじめ定められたフレーム期間毎(たとえば、1フレーム期間毎)に反転させる。なお、1フレーム期間は、すべての画素の画素電極  $P_X$  に1回ずつ階調電圧を加える期間であり、一般的な液晶表示装置の場合、たとえば、1/60秒または1/120秒である。

【0046】

また、液晶表示パネル1の駆動方法を、1フレーム期間における各画素の極性の観点で分類すると、列毎反転駆動、ライン反転駆動、ドット反転駆動の3種類に大別される。

【0047】

列毎反転駆動は、たとえば、図3(a)に示すように、1フレーム期間における各画素の極性を見たときに、走査信号線  $GL_m$  の延在方向で隣接する2つの画素の極性は反対の極性であり、映像信号線  $DL_n$  の延在方向に並んだ複数個の画素の極性は同じ極性である駆動方法である。なお、図3(a)において、それぞれの画素電極  $P_X$  に示した+または-の記号は、当該画素電極  $P_X$  を有する画素の極性を表しており、+は階調電圧の電位がコモン電圧の電位よりも高い正極性の画素であり、-は階調電圧の電位がコモン電圧の電位よりも低い負極性の画素であることを意味する。

【0048】

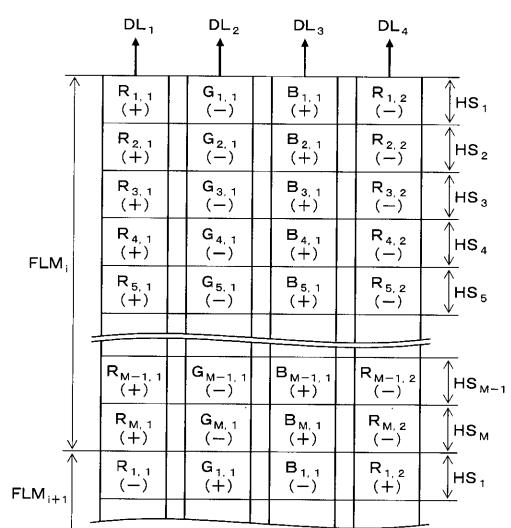

整列配置の液晶表示パネル1を列毎反転駆動で駆動する場合、第1の駆動回路2は、たとえば、図3(b)に示すような順番で、それぞれの階調電圧  $R_{m,u}$ ,  $G_{m,u}$ ,  $B_{m,u}$  ( $m = 1, 2, 3, \dots, M$ ,  $u = 1, 2, \dots, N$ )を、所定の映像信号線  $DL_n$  ( $n = 1, 2, 3, \dots, 3N$ )に加える(出力する)。なお、図3(b)において、 $FLM_i$ ,  $FLM_{i+1}$ は、それぞれフレーム期間であり、 $HS_m$ は、走査信号線  $GL_m$  の走査信号がHレベルになるライン選択期間である。

【0049】

このとき、1本の映像信号線  $DL_n$  に加わる階調電圧は、1フレーム期間中に出力される階調電圧の電位とコモン電圧の電位との関係が常に同じである。また、それぞれの階調電圧の電位とコモン電圧の電位との関係は、1フレーム期間毎に反転する。

【0050】

また、図を参照した説明は省略するが、ライン反転駆動は、たとえば、1フレーム期間における各画素の極性を見たときに、映像信号線  $DL_n$  の延在方向で隣接する2つの画素の極性は反対の極性であり、走査信号線  $GL_m$  の延在方向に並んだ複数個の画素の極性は同じ極性である駆動方法である。

10

20

30

40

50

## 【0051】

図4(a)および図4(b)は、図2に示した液晶表示パネルの駆動方法の別の一例を示す模式図である。

図4(a)は、液晶表示パネルをドット反転駆動で駆動するときの画素の極性を示す模式図である。図4(b)は、階調電圧の出力方法の一例を示す模式図である。

なお、図4(a)には、図2と同じ部分、すなわち表示領域DAの左上の角部にある横6画素、縦5画素分の領域の画素の極性の一例を示している。

## 【0052】

ドット反転駆動は、たとえば、図4(a)に示すように、1フレーム期間における各画素の極性を見たときに、走査信号線 $GL_m$ の延在方向で隣接する2つの画素の極性が反対の極性であり、かつ、映像信号線 $DL_n$ の延在方向で隣接する2つの画素の極性も反対の極性である駆動方法である。なお、図4(a)において、それぞれの画素電極 $PX$ に示した+または-の記号は、当該画素電極 $PX$ を有する画素の極性を表しており、+は階調電圧の電位がコモン電圧の電位よりも高い正極性の画素であり、-は階調電圧の電位がコモン電圧の電位よりも低い負極性の画素であることを意味する。

10

## 【0053】

整列配置の液晶表示パネル1をドット反転駆動で駆動する場合、第1の駆動回路2は、たとえば、図4(b)に示すような順番で、それぞれの階調電圧 $R_{m,u}, G_{m,u}, B_{m,u}$ ( $m = 1, 2, 3, \dots, M$ 。 $u = 1, 2, \dots, N$ )を、所定の映像信号線 $DL_n$ ( $n = 1, 2, 3, \dots, 3N$ )に出力する。なお、図4(b)において、 $FL_{M_i}, FLM_{i+1}$ は、それぞれフレーム期間であり、 $HS_m$ は、走査信号線 $GL_m$ の走査信号がHレベルになるライン選択期間である。

20

## 【0054】

このとき、1本の映像信号線 $DL_n$ に出力される階調電圧は、1フレーム期間中に出力される階調電圧の電位とコモン電圧の電位との関係が1ライン選択期間 $HS_m$ 毎に反転している。また、それぞれの階調電圧の電位とコモン電圧の電位との関係は、1フレーム期間毎に反転する。

20

## 【0055】

列毎反転駆動は、走査信号線 $GL_m$ の延在方向で隣接する2つの画素の極性は反対の極性であるものの、映像信号線 $DL_n$ の延在方向で隣接する2つの画素の極性は同じ極性である。そのため、液晶表示パネル1に表示される映像や画像に、たとえば、視線移動の縦筋流れと呼ばれる現象が発生し、画質が低下する。

30

## 【0056】

また、ライン反転駆動は、映像信号線 $DL_n$ の延在方向で隣接する2つの画素の極性は反対の極性であるものの、走査信号線 $GL_m$ の延在方向に並んだ複数個の画素の極性は同じ極性である。そのため、液晶表示パネル1に表示される映像や画像に、たとえば、横スメアまたは残像と呼ばれる現象が発生し、画質が低下する。

30

## 【0057】

したがって、整列配置の液晶表示パネル1の駆動方法は、画質を向上させるという観点ではドット反転駆動が望ましい。

40

## 【0058】

一方、整列配置の液晶表示パネル1をドット反転駆動またはライン反転駆動で駆動させる場合は、1フレーム期間中に1本の映像信号線 $DL_n$ に入力する階調電圧の電位とコモン電圧の電位との関係を、1ライン選択期間 $HS_m$ 毎に反転させる必要がある。そのため、第1の駆動回路2の消費電力および発熱量が増加する。

## 【0059】

したがって、整列配置の液晶表示パネル1を有する液晶表示装置は、第1の駆動回路2の消費電力および発熱量を低減するという観点では列毎反転駆動が望ましい。

## 【0060】

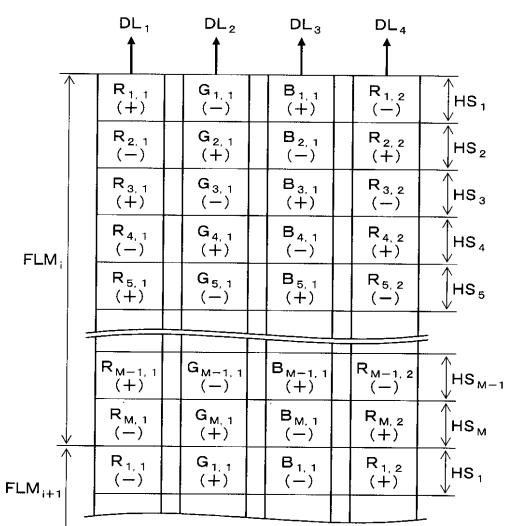

図5は、本発明に関わる液晶表示パネルにおける画素の配置の一例を示す模式図である

50

。

## 【0061】

整列配置の液晶表示パネル1を有する液晶表示装置は、上記のように、画質の低下を防ぐことと、第1の駆動回路2の消費電力および発熱量を低減することを両立させることが難しい。

## 【0062】

画質の低下を防ぐことと、第1の駆動回路2の消費電力および発熱量を低減することを両立させる方法としては、たとえば、液晶表示パネル1における各画素の配置を、図5に示すような配置にする方法が提案されている。なお、図5には、表示領域DAの左上の角部にある横6画素、縦5画素分の領域の画素の配置の一例を示している。また、図5において、GL<sub>0</sub>はダミーの走査信号線、DL<sub>0</sub>はダミーの映像信号線である。

10

## 【0063】

また、図5において、それぞれの画素電極PXに記したR<sub>m,u</sub>、G<sub>m,u</sub>、B<sub>m,u</sub>(m=1, 2, 3, 4, 5。u=1, 2)は、それぞれの画素電極PXに加える階調電圧である。

## 【0064】

また、図5において、隣接する2本の映像信号線DL<sub>0</sub>、DL<sub>1</sub>の間に配置されている画素電極PXは、表示領域DAの外側に配置されるダミーの画素電極であり、当該ダミーの画素電極PXに記したD<sub>m,0</sub>は、ダミーの階調電圧である。

20

## 【0065】

図5に示した液晶表示パネルにおいて、隣接する2本の映像信号線DL<sub>n</sub>、DL<sub>n+1</sub>の間には、TFT素子Trを介して一方の映像信号線DL<sub>n</sub>に接続している画素電極PXと、TFT素子Trを介して他方の映像信号線DL<sub>n+1</sub>に接続している画素電極PXとが、映像信号線DL<sub>n</sub>の延在方向に沿って交互に並んでいる。

30

## 【0066】

このとき、1本の映像信号線DL<sub>n</sub>(n=1, 2, 3, ..., 3N+1)に接続しているTFT素子Trをみると、添え字mが奇数の走査信号線GL<sub>m</sub>にゲートが接続しているTFT素子Trと、添え字mが偶数の走査信号線GL<sub>m</sub>にゲートが接続しているTFT素子Trとは、走査信号線の延在方向でみた映像信号線DL<sub>n</sub>との位置関係が反転している。以下、図5に示したような画素の配置を、千鳥配置という。

40

## 【0067】

また、図2に示した整列配置の液晶表示パネル1は、走査信号線GL<sub>m</sub>の延在方向に沿って3N個(Nドット分)の画素が並んでいる場合、表示領域DAの画素電極PXに加える階調電圧を伝送する映像信号線DLは3N本である。

## 【0068】

これに対し、千鳥配置の液晶表示パネル1は、走査信号線GL<sub>m</sub>の延在方向に沿って3N個(Nドット分)の画素が並んでいる場合、表示領域DAの画素電極PXに加える階調電圧を伝送する映像信号線DLは3N+1本である。このとき、表示領域DAの右端に配置される映像信号線DL<sub>3N+1</sub>に接続している画素電極PXは、添え字mが奇数の走査信号線GL<sub>m</sub>にゲートが接続しているTFT素子Trを介して接続している画素電極PXがダミーの画素電極になる。また、図5に示した例では、表示領域DAの右端に配置される映像信号線DL<sub>3N+1</sub>に接続している画素電極PXのうちの、添え字mが偶数の走査信号線GL<sub>m</sub>にゲートが接続しているTFT素子Trを介して接続している画素電極PXが階調電圧B<sub>m,N</sub>を加える画素電極になる。

40

## 【0069】

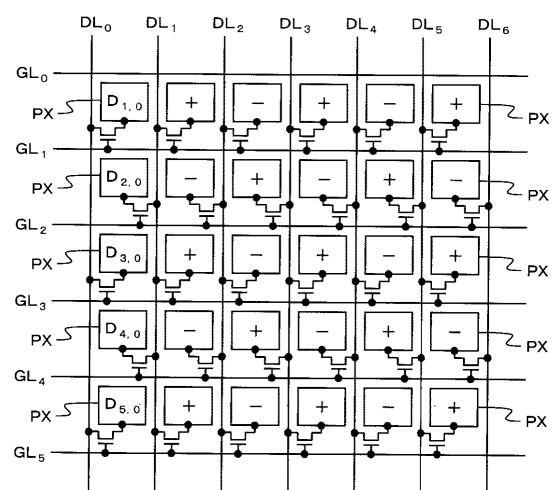

図6(a)および図6(b)は、図5に示した液晶表示パネルの駆動方法の一例を示す模式図である。

図6(a)は、図5に示した液晶表示パネルをドット反転駆動で駆動するときの画素の極性を示す模式図である。図6(b)は、階調電圧の出力方法の一例を示す模式図である。

50

なお、図6(a)には、図5と同じ部分、すなわち表示領域DAの左上の角部にある横6画素、縦5画素分の領域の画素の極性の一例を示している。

【0070】

千鳥配置の液晶表示パネル1をドット反転駆動で駆動するときには、たとえば、図6(a)に示すように、1フレーム期間における各画素の極性を見たときに、映像や画像の表示に寄与する階調電圧 $R_{m,u}, G_{m,u}, B_{m,u}$ が加わる画素電極PXを有する画素の極性がドット反転になるようになる。なお、図6(a)において、それぞれの画素電極PXに示した+または-の記号は、当該画素電極PXを有する画素の極性を表している。

【0071】

千鳥配置の液晶表示パネル1をドット反転駆動で駆動する場合、第1の駆動回路2は、たとえば、図6(b)に示すような順番で、それぞれの階調電圧 $R_{m,u}, G_{m,u}, B_{m,u}$ ( $m = 1, 2, 3, \dots, M$ ,  $u = 1, 2, \dots, N$ )を、所定の映像信号線 $DL_n$ ( $n = 1, 2, 3, \dots, 3N + 1$ )に出力する。

【0072】

このとき、表示領域DAの左端に配置される映像信号線 $DL_1$ は、図6に示したように、添え字mが偶数の走査信号線 $GL_m$ の走査信号がHレベルになるライン選択期間 $HS_m$ に、ダミーの階調電圧 $D_{m,0}$ が入力される。このダミーの階調電圧 $D_{m,0}$ が加えられる画素電極PXを有する画素は、映像や画像の表示に寄与しないので、ダミーの階調電圧 $D_{m,0}$ は任意の電位の電圧信号でよい。したがって、第1の駆動回路2においてダミーの階調電圧 $D_{m,0}$ を生成するときには、ダミーの階調電圧 $D_{m,0}$ の電位とコモン電圧の電位との高低の関係が、映像信号線 $DL_1$ に入力する階調電圧 $R_{m,1}$ の電位とコモン電圧の電位との高低の関係と同じ関係になるように生成する。

【0073】

また、図示は省略するが、表示領域DAの右端に配置される映像信号線 $DL_{3N+1}$ は、添え字mが奇数の走査信号線 $GL_m$ の走査信号がHレベルになるライン選択期間 $HS_m$ に、ダミーの階調電圧が入力される。したがって、第1の駆動回路2において映像信号線 $DL_{3N+1}$ に加えるダミーの階調電圧を生成するときには、ダミーの階調電圧の電位とコモン電圧の電位との高低の関係が、映像信号線 $DL_{3N+1}$ に入力する階調電圧 $B_{m,N}$ の電位とコモン電圧の電位との高低の関係と同じ関係になるように生成する。

【0074】

こうすると、1本の映像信号線 $DL_n$ に出力される階調電圧は、1フレーム期間中に出力される階調電圧の電位とコモン電圧の電位との関係がすべて同じ関係になる。また、それぞれの階調電圧の電位とコモン電圧の電位との関係は、1フレーム期間毎に反転する。

【0075】

すなわち、図5に示した千鳥配置の液晶表示パネル1をドット反転駆動で駆動する場合の、第1の駆動回路2における階調電圧の生成処理は、整列配置の液晶表示パネルを列毎反転駆動で駆動する場合の生成処理に相当する。したがって、千鳥配置の液晶表示パネル1を有する液晶表示装置は、画質の低下を防ぐことと、第1の駆動回路2の消費電力および発熱量を低減することを両立させることができる。

【0076】

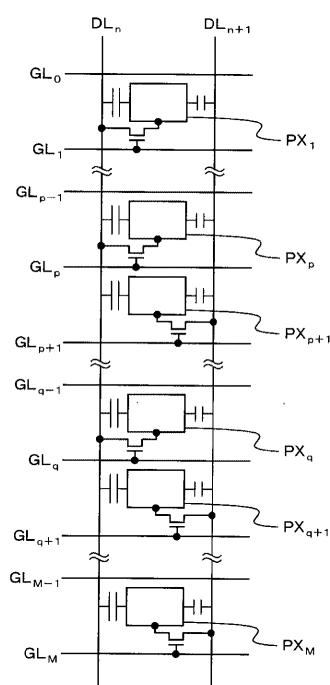

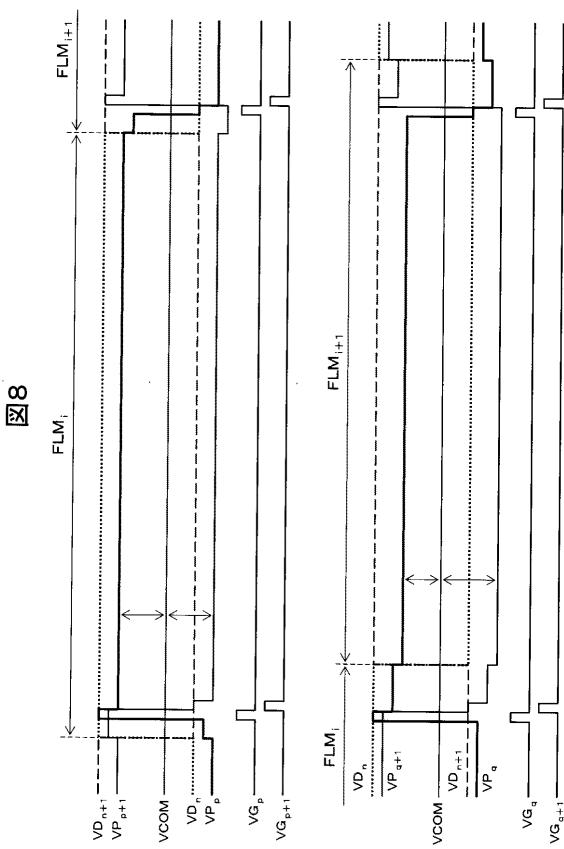

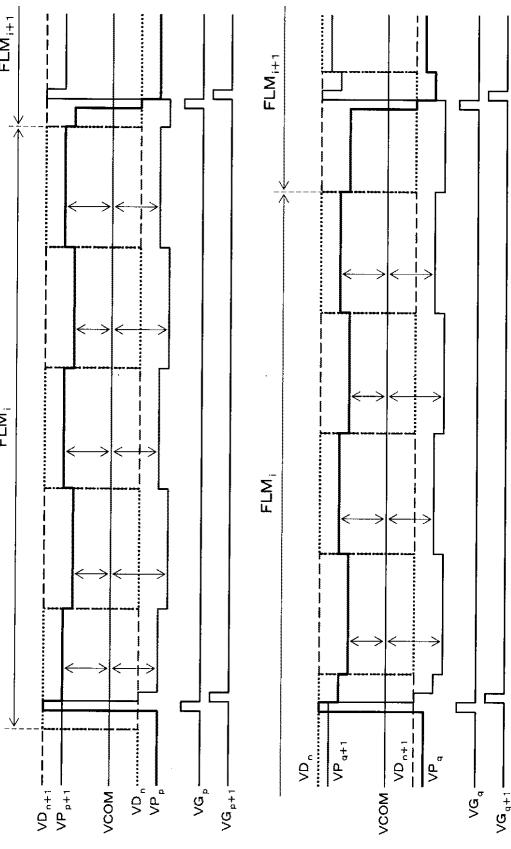

図7および図8は、千鳥配置の液晶表示パネルをドット反転駆動で駆動する場合の問題点の一例を説明するための模式図である。

図7は、千鳥配置の液晶表示パネルにおける寄生容量の一例を示す模式図である。図8は、図7に示した画素電極の電位の推移の一例を示す模式図である。

【0077】

千鳥配置の液晶表示パネル1において、複数本の映像信号線 $DL$ および画素電極PXは、ともに第1の基板に配置される。このとき、隣接する2本の映像信号線 $DL_n, DL_{n+1}$ の間に配置する画素電極PXは、通常、一方の映像信号線 $DL_n$ との平面距離と、他方の映像信号線 $DL_{n+1}$ との平面距離とが、同じ距離になるように形成する。

【0078】

10

20

30

40

50

しかしながら、複数本の映像信号線  $D_L$  を形成する工程と、画素電極  $P_X$  を形成する工程とは、独立した工程であり、かつ、それぞれの工程は、フォトリソグラフィー技術を利用して行われる。そのため、実際に得られた第1の基板（液晶表示パネル1）において、隣接する2本の映像信号線  $D_L_n$ ,  $D_L_{n+1}$  と、その間に配置された画素電極  $P_X$  との位置関係を調べたときに、たとえば、画素電極  $P_X$  と映像信号線  $D_L_n$  との平面距離が、画素電極  $P_X$  と他方の映像信号線  $D_L_{n+1}$  との平面距離よりも短くなることがある。

#### 【0079】

液晶表示パネル1のように、隣接する2本の映像信号線  $D_L_n$ ,  $D_L_{n+1}$  の間に画素電極  $P_X_m$  を配置した場合、当該画素電極  $P_X_m$  と一方の映像信号線  $D_L_n$  との間に第1の寄生容量が生じ、当該画素電極  $P_X_m$  と他方の映像信号線  $D_L_{n+1}$  との間に第2の寄生容量が生じる。

10

#### 【0080】

このとき、画素電極  $P_X_m$  と映像信号線  $D_L_n$  との平面距離が、当該画素電極  $P_X_m$  と映像信号線  $D_L_{n+1}$  との平面距離よりも短いと、たとえば、図7に示すように、第1の寄生容量が第2の寄生容量よりも大きくなる。またこのとき、隣接する2本の映像信号線  $D_L_n$ ,  $D_L_{n+1}$  の間に配置されたM個の画素電極  $P_X_m$  の形成位置にずれが生じる場合、通常、同じ方向にずれが生じる。したがって、隣接する2本の映像信号線  $D_L_n$ ,  $D_L_{n+1}$  の間に配置された画素電極  $P_X_m$  を有する画素は、それぞれ、第1の寄生容量のほうが大きくなる。

20

#### 【0081】

またこのとき、千鳥配置の液晶表示パネル1をドット反転駆動で駆動すると、1フレーム期間中に、それぞれの映像信号線  $D_L_n$ ,  $D_L_{n+1}$  に加わる階調電圧の電位とコモン電圧の電位との関係は、常に同じ関係である。そのため、図7に示した、画素電極  $P_X_p$  の電位  $V_{P_p}$ 、画素電極  $P_X_{p+1}$  の電位  $V_{P_{p+1}}$ 、画素電極  $P_X_q$  の電位  $V_{P_q}$ 、画素電極  $P_X_{q+1}$  の電位  $V_{P_{q+1}}$  は、それぞれ、たとえば、図8に示すように推移する。

#### 【0082】

なお、図8において、 $V_{G_p}$ ,  $V_{G_{p+1}}$ ,  $V_{G_q}$ ,  $V_{G_{q+1}}$  は、それぞれ、図7に示した走査信号線  $G_L_p$ ,  $G_L_{p+1}$ ,  $G_L_q$ ,  $G_L_{q+1}$  に加わる走査信号である。また、図8において、 $V_{D_n}$ ,  $V_{D_{n+1}}$  は、それぞれ、図7に示した映像信号線  $D_L_n$ ,  $D_L_{n+1}$  に加わる階調電圧である。また、図8に示した例では、説明を簡単にするために、1フレーム期間中にそれぞれの映像信号線  $D_L_n$ ,  $D_L_{n+1}$  に加わる階調電圧  $V_{D_n}$ ,  $V_{D_{n+1}}$  の電位を一定にしている。すなわち、図8には、映像信号線  $D_L_n$ ,  $D_L_{n+1}$  を介して階調電圧が書き込まれるすべての画素電極に、同じ電位の階調電圧を加える場合を例示している。

30

#### 【0083】

画素電極  $P_X_p$  の電位  $V_{P_p}$  は、走査信号  $V_{G_p}$  がHレベルになるライン選択期間に、映像信号線  $D_L_n$  に加わる階調電圧  $V_{D_n}$  の電位になり、当該ライン選択期間が終了したときに、若干電位が下がる。同様に、画素電極  $P_X_p$  の電位  $V_{P_{p+1}}$  は、走査信号  $V_{G_{p+1}}$  がHレベルになるライン選択期間に、映像信号線  $D_L_{n+1}$  に加わる階調電圧  $V_{D_{n+1}}$  の電位になり、当該ライン選択期間が終了したときに、若干電位が下がる。その後、画素電極  $P_X_p$  の電位  $V_{P_p}$  および画素電極  $P_X_{p+1}$  の電位  $V_{P_{p+1}}$  は、フレーム期間  $F_L M_i$  の終了時刻までほぼ一定に保たれる。このとき、電位  $V_{P_p}$  とコモン電圧  $V_{COM}$  の電位との電位差と、電位  $V_{P_{p+1}}$  とコモン電圧  $V_{COM}$  の電位との電位差とは、ほぼ同じであり、画素電極  $P_X_p$  を有する画素と、画素電極  $P_X_{p+1}$  を有する画素は、ほぼ同じ明るさである。

40

#### 【0084】

そして、フレーム期間  $F_L M_i$  が終了し、次のフレーム期間  $F_L M_{i+1}$  が開始する時点で、映像信号線  $D_L_n$ ,  $D_L_{n+1}$  に加わる階調電圧  $V_{D_n}$ ,  $V_{D_{n+1}}$  の電位が反転すると、それにともない、画素電極  $P_X_p$  の電位  $V_{P_p}$  および画素電極  $P_X_{p+1}$  の電位

50

$V P_{p+1}$  が変動する。

【0085】

このとき、図7に示したように、映像信号線  $D L_n$  との間に生じる第1の寄生容量が、映像信号線  $D L_{n+1}$  との間に生じる第2の寄生容量よりも大きいと、画素電極  $P X_p$  の電位  $V P_p$  および画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  に対する影響が大きいのは、映像信号線  $D L_n$  の階調電圧  $V D_n$  である。そのため、画素電極  $P X_p$  の電位  $V P_p$  および画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  は、それぞれ、低くなるほうに変動する。したがって、画素電極  $P X_p$  を有する画素は変動前よりも暗くなり、画素電極  $P X_{p+1}$  を有する画素は、変動前よりも明るくなる。

【0086】

そして、画素電極  $P X_p$  の電位  $V P_p$  は、フレーム期間  $F L M_{i+1}$  において走査信号  $V G_p$  がHレベルになるライン選択期間に、映像信号線  $D L_n$  に加わる階調電圧  $V D_n$  の電位になり、当該ライン選択期間が終了したときに、若干電位が下がる。同様に、画素電極  $P X_p$  の電位  $V P_{p+1}$  は、フレーム期間  $F L M_{i+1}$  において走査信号  $V G_{p+1}$  がHレベルになるライン選択期間に、映像信号線  $D L_{n+1}$  に加わる階調電圧  $V D_{n+1}$  の電位になり、当該ライン選択期間が終了したときに、若干電位が下がる。

【0087】

また、画素電極  $P X_q$  の電位  $V P_q$  および画素電極  $P X_{q+1}$  の電位  $V P_{q+1}$  は、それぞれ、画素電極  $P X_p$  の電位  $V P_p$  および画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  と同様の推移をするので、詳細な説明は省略する。

【0088】

このとき、画素電極  $P X_p$  および画素電極  $P X_{p+1}$  は、フレーム期間  $F L M_i$  が開始してからまもない時刻に階調電圧  $V D_n$ ,  $V D_{n+1}$  が加えられる。そのため、画素電極  $P X_p$  を有する画素と、画素電極  $P X_{p+1}$  を有する画素がほぼ同じ明るさである期間が長い。

【0089】

これに対し、画素電極  $P X_q$  および画素電極  $P X_{q+1}$  は、フレーム期間  $F L M_i$  が開始してからしばらく経過した時刻に階調電圧  $V D_n$ ,  $V D_{n+1}$  が加えられる。そのため、画素電極  $P X_q$  を有する画素と、画素電極  $P X_{q+1}$  を有する画素がほぼ同じ明るさである期間が短い。

【0090】

フレーム期間  $F L M_i$  が終了し、次のフレーム期間  $F L M_{i+1}$  が開始するときの、階調電圧  $V D_n$ ,  $V D_{n+1}$  の電位の反転にともなう画素電極  $P X$  の電位の変動による画素の明るさの変動の度合いを横筋レベルとし、画素電極  $P X_q$  を有する画素およびその周辺の画素における横筋レベルを1とすると、画素電極  $P X_p$  を有する画素およびその周辺の画素における横筋レベルは、ほぼ0である。

【0091】

したがって、千鳥配置の液晶表示パネル1を従来のような単純なドット反転駆動で駆動すると、たとえば、表示領域DAの上端部における横筋レベルと下端部における横筋レベルの差が大きくなり、画質が低下するという問題がある。

【実施例】

【0092】

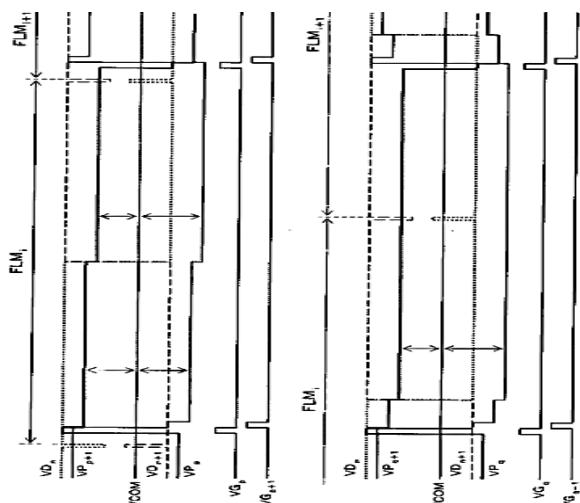

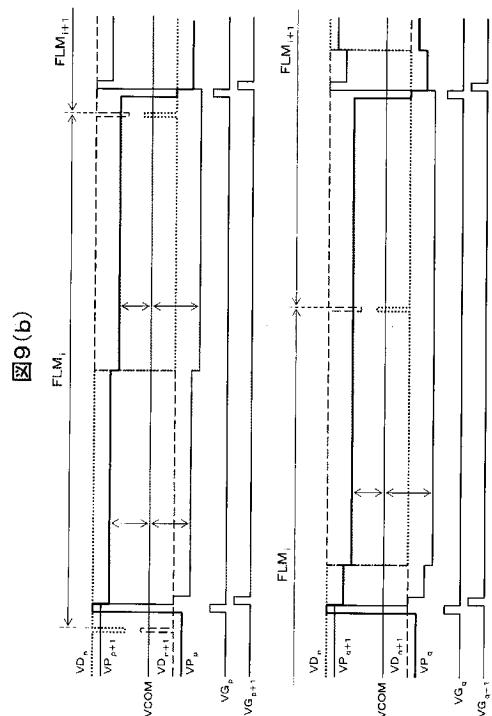

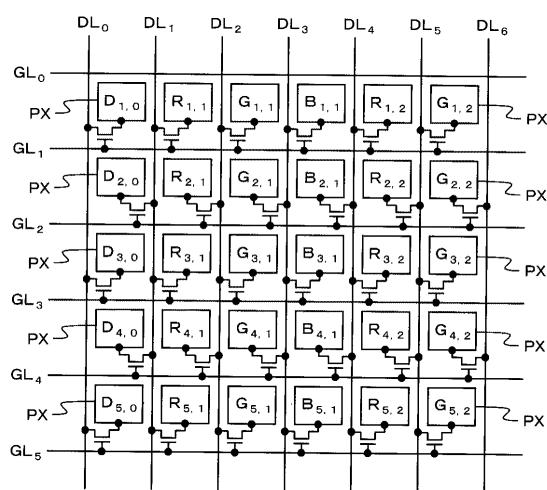

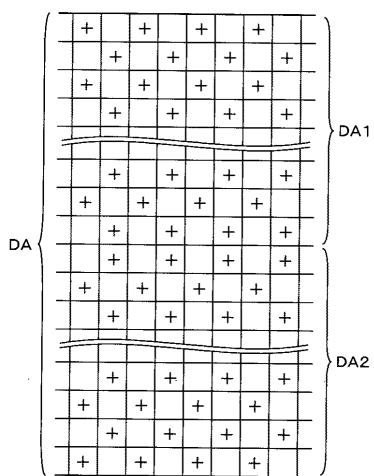

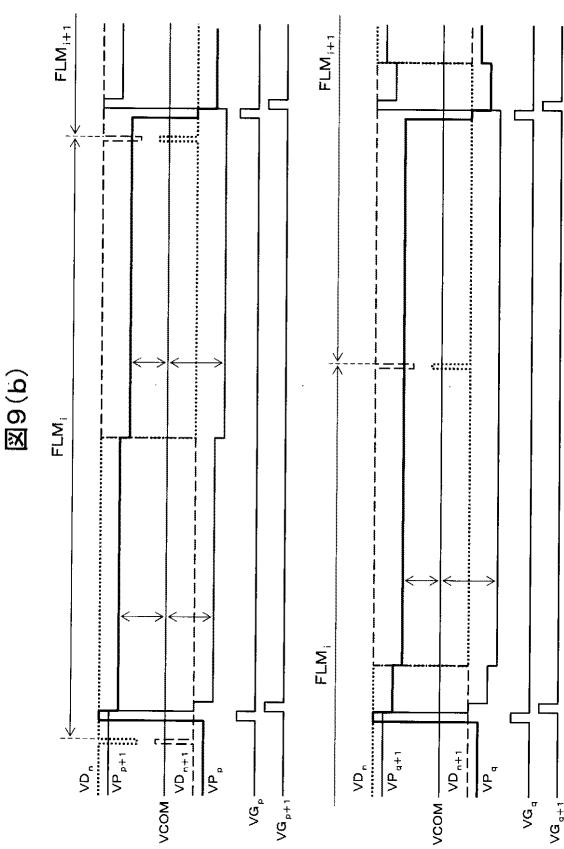

図9(a)および図9(b)は、本発明による一実施例の液晶表示パネルの駆動方法の原理を示す模式図である。

図9(a)は、本発明による一実施例の液晶表示パネルの駆動方法の原理を示す模式図である。図9(b)は、本実施例の液晶表示パネルの駆動方法において1フレーム期間を2個の1/2フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

【0093】

本実施例では、千鳥配置の液晶表示パネル1をドット反転駆動させたときに生じる画質

10

20

30

40

50

の低下を防ぐための駆動方法について説明する。

【0094】

本実施例の液晶表示パネル1の駆動方法は、基本的には、従来の駆動方法と同様であり、千鳥配置の液晶表示パネル1をドット反転駆動で駆動させる。ただし、本実施例の駆動方法では、1フレーム期間中を、概ね同じ長さのR個の1/Rフレーム期間に分割し、1フレーム期間に1本の映像信号線DLに入力する階調電圧の電位とコモン電圧の電位との関係を、1/Rフレーム期間毎に反転させる。

【0095】

本実施例の液晶表示パネルの駆動方法において、たとえば、1フレーム期間を2個の1/2フレーム期間に分割した場合は、1フレーム期間に1本の映像信号線DLに入力する階調電圧の電位とコモン電圧の電位との関係を、1/2フレーム期間毎に反転させる。そのため、1フレーム期間における表示領域DAの各画素の極性は、たとえば、図9(a)に示すようになる。すなわち、表示領域DAの上半分の領域DA1における各画素の極性、および下半分の領域DA2における各画素の極性は、それぞれドット反転駆動で駆動したときの関係になり、かつ、2つの領域DA1, DA2の境界線を挟んで隣接する2つの画素の極性が、同じ極性になる。

10

【0096】

図8に示したような画素電極PXの電位の変動に起因する横筋の度合い(横筋レベル)は、通常、2本の映像信号線DL<sub>n</sub>, DL<sub>n+1</sub>に加わる階調電圧の電位とコモン電圧の電位との関係が同じ関係である期間で考える。したがって、1本の映像信号線DLに入力する階調電圧の電位とコモン電圧の電位との関係を、1/2フレーム期間毎に反転させる場合の横筋は、1/2フレーム期間に階調電圧が加わる画素の間で考えればよい。

20

【0097】

このとき、図7に示したように、画素電極PX<sub>m</sub>と映像信号線DL<sub>n</sub>との間に生じる第1の寄生容量が、画素電極PX<sub>m</sub>と映像信号線DL<sub>n+1</sub>との間に生じる第2の寄生容量よりも大きくなつてあり、4つの画素電極PX<sub>p</sub>, PX<sub>p+1</sub>, PX<sub>q</sub>, PX<sub>q+1</sub>が上半分の領域DA1にあるとすると、画素電極PX<sub>p</sub>の電位VP<sub>p</sub>、画素電極PX<sub>p+1</sub>の電位VP<sub>p+1</sub>、画素電極PX<sub>q</sub>の電位VP<sub>q</sub>、画素電極PX<sub>q+1</sub>の電位VP<sub>q+1</sub>は、それぞれ、たとえば、図9(b)に示すように推移する。

30

【0098】

なお、図9(b)において、VG<sub>p</sub>, VG<sub>p+1</sub>, VG<sub>q</sub>, VG<sub>q+1</sub>は、それぞれ、図7に示した走査信号線GL<sub>p</sub>, GL<sub>p+1</sub>, GL<sub>q</sub>, GL<sub>q+1</sub>に加わる走査信号である。また、図9(b)において、VD<sub>n</sub>, VD<sub>n+1</sub>は、それぞれ、図7に示した映像信号線DL<sub>n</sub>, DL<sub>n+1</sub>に加わる階調電圧である。また、図9(b)に示した例では、説明を簡単にするために、1フレーム期間中にそれぞれの映像信号線DL<sub>n</sub>, DL<sub>n+1</sub>に加わる階調電圧VD<sub>n</sub>, VD<sub>n+1</sub>の電位を一定にしている。すなわち、図9(b)には、映像信号線DL<sub>n</sub>, DL<sub>n+1</sub>を介して階調電圧が書き込まれるすべての画素電極PXに、同じ電位の階調電圧を加える場合を例示している。

【0099】

画素電極PX<sub>p</sub>の電位VP<sub>p</sub>は、走査信号VG<sub>p</sub>がHレベルになるライン選択期間に、映像信号線DL<sub>n</sub>に加わる階調電圧VD<sub>n</sub>の電位になり、当該ライン選択期間が終了したときに、若干電位が下がる。同様に、画素電極PX<sub>p</sub>の電位VP<sub>p+1</sub>は、走査信号VG<sub>p+1</sub>がHレベルになるライン選択期間に、映像信号線DL<sub>n+1</sub>に加わる階調電圧VD<sub>n+1</sub>の電位になり、当該ライン選択期間が終了したときに、若干電位が下がる。その後、画素電極PX<sub>p</sub>の電位VP<sub>p</sub>および画素電極PX<sub>p</sub>の電位VP<sub>p+1</sub>は、前半の1/2フレーム期間の終了時刻までほぼ一定に保たれる。このとき、電位VP<sub>p</sub>とコモン電圧VCOMの電位との電位差と、電位VP<sub>p+1</sub>とコモン電圧VCOMの電位との電位差とは、ほぼ同じであり、画素電極PX<sub>p</sub>を有する画素と、画素電極PX<sub>p+1</sub>を有する画素は、ほぼ同じ明るさである。

40

【0100】

50

そして、フレーム期間  $F L M_i$  における前半の 1 / 2 フレーム期間が終了し、後半の 1 / 2 フレーム期間が開始する時点で、映像信号線  $D L_n, D L_{n+1}$  に加わる階調電圧  $V D_n, V D_{n+1}$  の電位が反転すると、それにともない、画素電極  $P X_p$  の電位  $V P_p$  および画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  が変動する。

#### 【0101】

このとき、図 7 に示したように、映像信号線  $D L_n$  との間に生じる第 1 の寄生容量が、映像信号線  $D L_{n+1}$  との間に生じる第 2 の寄生容量よりも大きい場合、画素電極  $P X_p$  の電位  $V P_p$  および画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  に対する影響が大きいのは、映像信号線  $D L_n$  の階調電圧  $V D_n$  である。そのため、画素電極  $P X_p$  の電位  $V P_p$  および画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  は、それぞれ、低くなるほうに変動する。したがって、画素電極  $P X_p$  を有する画素は変動前よりも暗くなり、画素電極  $P X_{p+1}$  を有する画素は、変動前よりも明るくなる。

#### 【0102】

またこのとき、各画素の極性を 1 フレーム期間毎に反転させるとすると、フレーム期間  $F L M_{i+1}$  の前半の 1 / 2 フレーム期間における階調電圧  $V D_n$  の電位とコモン電圧  $V COM$  の電位との関係、および階調電圧  $V D_{n+1}$  の電位とコモン電圧  $V COM$  の電位との関係は、直前のフレーム期間  $F L M_i$  の後半の 1 / 2 フレーム期間における関係と同じ関係になる。

#### 【0103】

そして、画素電極  $P X_p$  の電位  $V P_p$  は、フレーム期間  $F L M_{i+1}$  において走査信号  $V G_p$  が H レベルになるライン選択期間に、映像信号線  $D L_n$  に加わる階調電圧  $V D_n$  の電位になり、当該ライン選択期間が終了したときに、若干電位が下がる。同様に、画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  は、フレーム期間  $F L M_{i+1}$  において走査信号  $V G_{p+1}$  が H レベルになるライン選択期間に、映像信号線  $D L_{n+1}$  に加わる階調電圧  $V D_{n+1}$  の電位になり、当該ライン選択期間が終了したときに、若干電位が下がる。

#### 【0104】

また、画素電極  $P X_q$  の電位  $V P_q$  および画素電極  $P X_{q+1}$  の電位  $V P_{q+1}$  は、それぞれ、画素電極  $P X_p$  の電位  $V P_p$  および画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  と同様の推移をするので、詳細な説明は省略する。

#### 【0105】

1 フレーム期間中に 2 本の映像信号線  $D L_n, D L_{n+1}$  に加わる階調電圧  $V D_n, V D_{n+1}$  の電位とコモン電圧  $V COM$  の電位との関係が、1 / 2 フレーム期間毎に反転する場合、画素電極  $P X_p$  の電位  $V P_p$  および画素電極  $P X_{p+1}$  の電位  $V P_{p+1}$  は、前半の 1 / 2 フレーム期間が終了した時点で変動する。そのため、図 8 に示した画素電極  $P X_q$  を有する画素およびその周辺の画素における横筋レベルを 1 とすると、電位  $V P_p$  が図 9 (b) に示したように推移する画素電極  $P X_p$  を有する画素およびその周辺の画素における横筋レベルは、約 1 / 2 である。

#### 【0106】

これに対し、図 8 に示した画素電極  $P X_q$  を有する画素およびその周辺の画素における横筋レベルを 1 とすると、電位  $V P_q$  が図 9 (b) に示したように推移する画素電極  $P X_{q+1}$  を有する画素およびその周辺の画素における横筋レベルは、約 1 (2 / 2) である。

#### 【0107】

また、図を参照した説明は省略するが、図 9 (a) に示した、表示領域  $D A$  の下半分の領域  $D A_2$  にある画素電極  $P X$ 、すなわち、フレーム期間の後半の 1 / 2 フレーム期間に階調電圧が加わる画素電極  $P X$  の電位も、同様に、映像信号線  $D L_n, D L_{n+1}$  に加える階調電圧の電位とコモン電圧の電位との高低の関係が反転するときに変動する。

#### 【0108】

このように、1 フレーム期間中に 1 本の映像信号線  $D L$  に加える階調電圧の電位とコモン電圧の電位との関係を 1 / 2 フレーム期間毎に反転させた場合、表示領域  $D A$  の上下方向の中心付近における横筋レベルを 1 としたときに、表示領域  $D A$  の上端付近および下端

付近における横筋レベルが 1 / 2 になる。すなわち、1 フレーム期間中に 1 本の映像信号線  $D_L$  に加える階調電圧の電位とコモン電圧の電位との関係を 1 / 2 フレーム期間毎に反転させた場合、表示領域  $D_A$  における最大の横筋レベルと最小の横筋レベルとの差が、図 8 に示した場合に比べて小さくなる。したがって、1 フレーム期間中に 1 本の映像信号線  $D_L$  に加える階調電圧の電位とコモン電圧の電位との関係を 1 / 2 フレーム期間毎に反転させた場合、横筋による画質の低下を目立ちにくくすることができる。

#### 【0109】

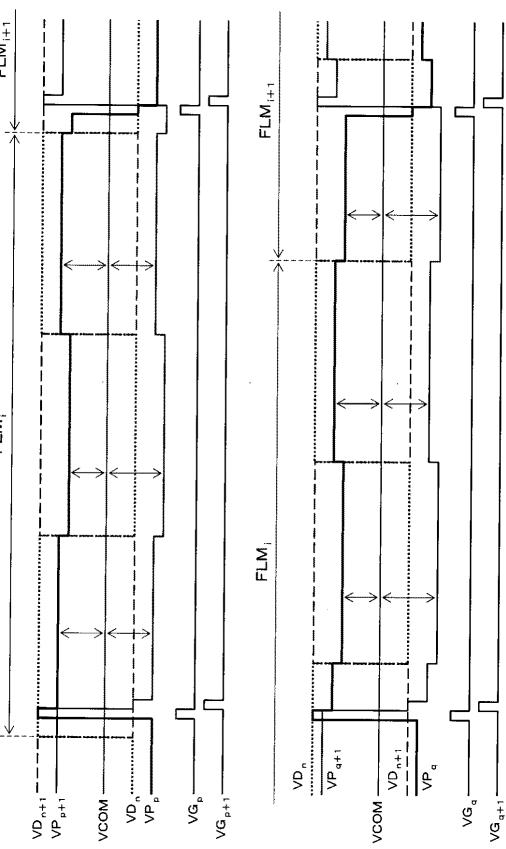

図 10 は、本実施例の液晶表示パネルの駆動方法において 1 フレーム期間を 3 個の 1 / 3 フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

#### 【0110】

本実施例の液晶表示パネルの駆動方法では、たとえば、1 フレーム期間を 3 個の 1 / 3 フレーム期間に分割し、1 フレーム期間中に 1 本の映像信号線  $D_L$  に加える階調電圧の電位とコモン電圧の電位との関係を、1 / 3 フレーム期間毎に反転させてもよい。

#### 【0111】

このとき、図 7 (a) に示した 4 つの画素電極  $PX_p$ ,  $PX_{p+1}$ ,  $PX_q$ ,  $PX_{q+1}$  が、たとえば、1 フレーム期間における 3 個の 1 / 3 フレーム期間のうちの、最初の 1 / 3 フレーム期間に階調電圧が加わる画素電極であるとすると、画素電極  $PX_p$  の電位  $VP_p$ 、画素電極  $PX_{p+1}$  の電位  $VP_{p+1}$ 、画素電極  $PX_q$  の電位  $VP_q$ 、画素電極  $PX_{q+1}$  の電位  $VP_{q+1}$  は、それぞれ、たとえば、図 10 に示すように推移する。

#### 【0112】

1 フレーム期間中に 2 本の映像信号線  $D_L_n$ ,  $D_L_{n+1}$  に加わる階調電圧  $VD_n$ ,  $VD_{n+1}$  の電位とコモン電圧  $VCOM$  の電位との関係が、1 / 3 フレーム期間毎に反転する場合、画素電極  $PX_p$  の電位  $VP_p$  および画素電極  $PX_{p+1}$  の電位  $VP_{p+1}$  は、最初の 1 / 3 フレーム期間が終了した時点、2 番目の 1 / 2 フレーム期間が終了した時点、および最後の 1 / 3 フレーム期間が終了した時点で変動する。そのため、図 8 に示した画素電極  $PX_q$  を有する画素およびその周辺の画素における横筋レベルを 1 とすると、電位  $VP_p$  が図 10 に示したように推移する画素電極  $PX_p$  を有する画素およびその周辺の画素における横筋レベルは、約 1 / 3 である。

#### 【0113】

これに対し、図 8 に示した画素電極  $PX_q$  を有する画素およびその周辺の画素における横筋レベルを 1 とすると、電位  $VP_q$  が図 10 に示したように推移する画素電極  $PX_q$  を有する画素およびその周辺の画素における横筋レベルは、約 2 / 3 である。

#### 【0114】

また、図を参照した説明は省略するが、図 10 に示した、1 フレーム期間の 2 番目の 1 / 3 フレーム期間または最後の 1 / 3 フレーム期間に階調電圧が加わる画素電極  $PX$  の電位も、同様に、映像信号線  $D_L_n$ ,  $D_L_{n+1}$  に加える階調電圧の電位とコモン電圧の電位との高低の関係が反転するときに変動する。

#### 【0115】

このように、1 フレーム期間中に 1 本の映像信号線  $D_L$  に加える階調電圧の電位とコモン電圧の電位との関係を 1 / 3 フレーム期間毎に反転させた場合、表示領域  $D_A$  における最大の横筋レベルと最小の横筋レベルとの差が、図 8 に示した場合に比べて小さくなる。したがって、1 フレーム期間中に 1 本の映像信号線  $D_L$  に加える階調電圧の電位とコモン電圧の電位との関係を 1 / 3 フレーム期間毎に反転させた場合も、横筋による画質の低下を目立ちにくくすることができる。

#### 【0116】

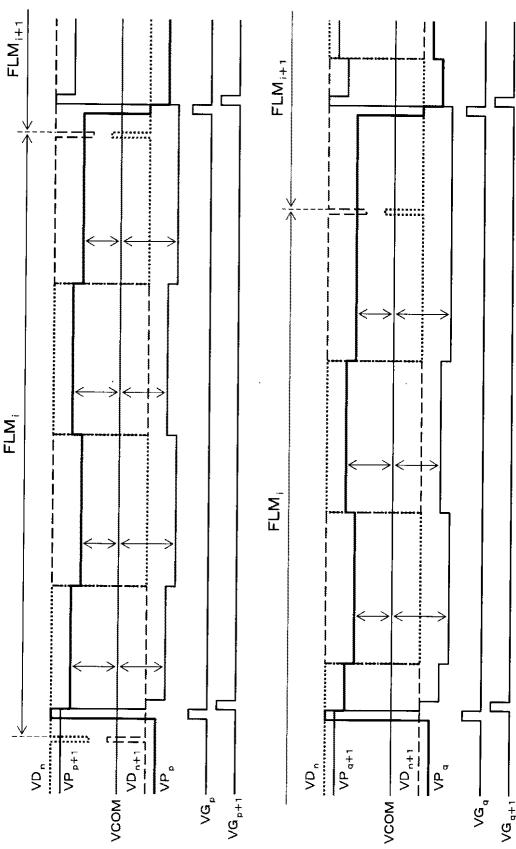

図 11 は、本実施例の液晶表示パネルの駆動方法において 1 フレーム期間を 4 個の 1 / 4 フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

#### 【0117】

本実施例の液晶表示パネルの駆動方法では、たとえば、1 フレーム期間を 4 個の 1 / 4 フレーム期間に分割し、1 フレーム期間中に 1 本の映像信号線  $D_L$  に加える階調電圧の電

10

20

30

40

50

位とコモン電圧の電位との関係を、1/4フレーム期間毎に反転させてもよい。

【0118】

このとき、図7(a)に示した4つの画素電極 $PX_p$ ,  $PX_{p+1}$ ,  $PX_q$ ,  $PX_{q+1}$ が、たとえば、1フレーム期間における4個の1/4フレーム期間のうちの、最初の1/4フレーム期間に階調電圧が加わる画素電極であるとすると、画素電極 $PX_p$ の電位 $V_{P_p}$ 、画素電極 $PX_{p+1}$ の電位 $V_{P_{p+1}}$ 、画素電極 $PX_q$ の電位 $V_{P_q}$ 、画素電極 $PX_{q+1}$ の電位 $V_{P_{q+1}}$ は、それぞれ、たとえば、図11に示すように推移する。

【0119】

1フレーム期間中に2本の映像信号線 $DL_n$ ,  $DL_{n+1}$ に加わる階調電圧 $VD_n$ ,  $VD_{n+1}$ の電位とコモン電圧 $VCOM$ の電位との関係が、1/4フレーム期間毎に反転する場合、画素電極 $PX_p$ の電位 $V_{P_p}$ および画素電極 $PX_{p+1}$ の電位 $V_{P_{p+1}}$ は、当該1フレーム期間における2番目の1/4フレーム期間および3番目の1/4フレーム期間が終了した時点で変動する。そのため、図8に示した画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルを1とすると、電位 $V_{P_p}$ が図11に示したように推移する画素電極 $PX_p$ を有する画素およびその周辺の画素における横筋レベルは、約1/2(2/4)である。

【0120】

これに対し、図8に示した画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルを1とすると、電位 $V_{P_q}$ が図11に示したように推移する画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルは、約3/4である。

【0121】

また、図を参照した説明は省略するが、図11に示した、1フレーム期間の2番目の1/4フレーム期間から最後の1/4フレーム期間のいずれかで階調電圧が加わる画素電極 $PX$ の電位も、同様に、映像信号線 $DL_n$ ,  $DL_{n+1}$ に加える階調電圧の電位とコモン電圧の電位との高低の関係が反転するときに変動する。

【0122】

このように、1フレーム期間中に1本の映像信号線 $DL$ に加える階調電圧の電位とコモン電圧の電位との関係を1/4フレーム期間毎に反転させた場合、表示領域 $DA$ における最大の横筋レベルと最小の横筋レベルとの差が、図8に示した場合に比べて小さくなる。したがって、1フレーム期間中に、1本の映像信号線 $DL$ に加える階調電圧の電位とコモン電圧の電位との関係を1/4フレーム期間毎に反転させた場合も、横筋による画質の低下を目立ちにくくすることができる。

【0123】

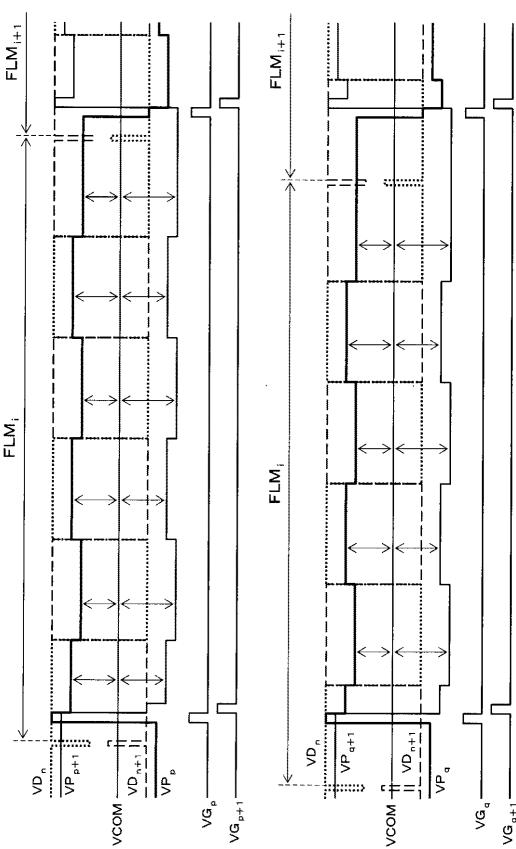

図12は、本実施例の液晶表示パネルの駆動方法において1フレーム期間を5個の1/5フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

【0124】

本実施例の液晶表示パネルの駆動方法では、たとえば、1フレーム期間を5個の1/5フレーム期間に分割し、1フレーム期間中に1本の映像信号線 $DL$ に加える階調電圧の電位とコモン電圧の電位との関係を、1/5フレーム期間毎に反転させてもよい。

【0125】

このとき、図7(a)に示した4つの画素電極 $PX_p$ ,  $PX_{p+1}$ ,  $PX_q$ ,  $PX_{q+1}$ が、たとえば、1フレーム期間における5個の1/5フレーム期間のうちの、最初の1/5フレーム期間に階調電圧が加わる画素電極であるとすると、画素電極 $PX_p$ の電位 $V_{P_p}$ 、画素電極 $PX_{p+1}$ の電位 $V_{P_{p+1}}$ 、画素電極 $PX_q$ の電位 $V_{P_q}$ 、画素電極 $PX_{q+1}$ の電位 $V_{P_{q+1}}$ は、それぞれ、たとえば、図12に示すように推移する。

【0126】

1フレーム期間中に2本の映像信号線 $DL_n$ ,  $DL_{n+1}$ に加わる階調電圧 $VD_n$ ,  $VD_{n+1}$ の電位とコモン電圧 $VCOM$ の電位との関係が、1/5フレーム期間毎に反転する場合、画素電極 $PX_p$ の電位 $V_{P_p}$ および画素電極 $PX_{p+1}$ の電位 $V_{P_{p+1}}$ は、当該1フレーム期間におけるそれぞれの1/5フレーム期間が終了した時点で変動する。そのた

10

20

30

40

50

め、図8に示した画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルを1とすると、電位 $VP_p$ が図12に示したように推移する画素電極 $PX_p$ を有する画素およびその周辺の画素における横筋レベルは、約2/5である。

#### 【0127】

これに対し、図8に示した画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルを1とすると、電位 $VP_q$ が図12に示したように推移する画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルは、約3/5である。

#### 【0128】

また、図を参照した説明は省略するが、図12に示した、1フレーム期間の2番目の1/5フレーム期間から最後の1/2フレーム期間のいずれかで階調電圧が加わる画素電極 $PX$ の電位も、同様に、映像信号線 $DL_n$ ,  $DL_{n+1}$ に加える階調電圧の電位とコモン電圧の電位との高低の関係が反転するときに変動する。

10

#### 【0129】

このように、1フレーム期間中に1本の映像信号線 $DL$ に加える階調電圧の電位とコモン電圧の電位との関係を1/5フレーム期間毎に反転させた場合、表示領域 $DA$ における最大の横筋レベルと最小の横筋レベルとの差が、図8に示した場合に比べて小さくなる。したがって、1フレーム期間中に1本の映像信号線 $DL$ に加える階調電圧の電位とコモン電圧の電位との関係を1/5フレーム期間毎に反転させた場合も、横筋による画質の低下を目立ちにくくすることができる。

20

#### 【0130】

図13は、本実施例の液晶表示パネルの駆動方法において1フレーム期間を6個の1/6フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

#### 【0131】

本実施例の液晶表示パネルの駆動方法では、たとえば、1フレーム期間を6個の1/6フレーム期間に分割し、1フレーム期間中に1本の映像信号線 $DL$ に加える階調電圧の電位とコモン電圧の電位との関係を、1/6フレーム期間毎に反転させてもよい。

30

#### 【0132】

このとき、図7(a)に示した4つの画素電極 $PX_p$ ,  $PX_{p+1}$ ,  $PX_q$ ,  $PX_{q+1}$ が、たとえば、1フレーム期間における6個の1/6フレーム期間のうちの、最初の1/6フレーム期間に階調電圧が加わる画素電極であるとすると、画素電極 $PX_p$ の電位 $VP_p$ 、画素電極 $PX_{p+1}$ の電位 $VP_{p+1}$ 、画素電極 $PX_q$ の電位 $VP_q$ 、画素電極 $PX_{q+1}$ の電位 $VP_{q+1}$ は、それぞれ、たとえば、図13に示すように推移する。

30

#### 【0133】

1フレーム期間中に2本の映像信号線 $DL_n$ ,  $DL_{n+1}$ に加わる階調電圧 $VD_n$ ,  $VD_{n+1}$ の電位とコモン電圧 $VCOM$ の電位との関係が、1/6フレーム期間毎に反転する場合、画素電極 $PX_p$ の電位 $VP_p$ および画素電極 $PX_{p+1}$ の電位 $VP_{p+1}$ は、当該1フレーム期間における2番目の1/6フレーム期間から5番目の1/6フレーム期間までのそれぞれの1/6フレーム期間が終了した時点で変動する。そのため、図8に示した画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルを1とすると、電位 $VP_p$ が図12に示したように推移する画素電極 $PX_p$ を有する画素およびその周辺の画素における横筋レベルは、約2/5である。

40

#### 【0134】

これに対し、図8に示した画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルを1とすると、電位 $VP_q$ が図13に示したように推移する画素電極 $PX_q$ を有する画素およびその周辺の画素における横筋レベルは、約3/5である。

40

#### 【0135】

また、図を参照した説明は省略するが、図13に示した、1フレーム期間の2番目の1/6フレーム期間から最後の1/6フレーム期間のいずれかで階調電圧が加わる画素電極 $PX$ の電位も、同様に、映像信号線 $DL_n$ ,  $DL_{n+1}$ に加える階調電圧の電位とコモン電圧の電位との高低の関係が反転するときに変動する。

50

## 【0136】

このように、1フレーム期間中に1本の映像信号線DLに加える階調電圧の電位とコモン電圧の電位との関係を1/6フレーム期間毎に反転させた場合、表示領域DAにおける最大の横筋レベルと最小の横筋レベルとの差が、図8に示した場合に比べて小さくなる。したがって、1フレーム期間中に1本の映像信号線DLに加える階調電圧の電位とコモン電圧の電位との関係を1/6フレーム期間毎に反転させた場合も、横筋による画質の低下を目立ちにくくすることができる。

## 【0137】

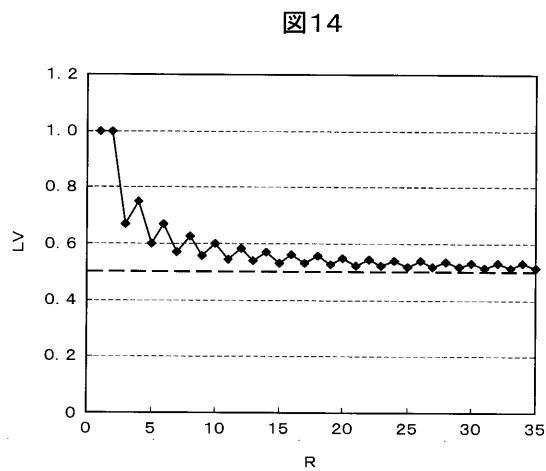

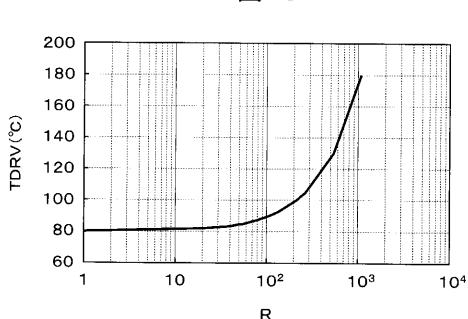

図14および図15は、本実施例の液晶表示パネルの駆動方法における1/Rフレーム期間の長さの設定方法の一例を示す模式図である。

10

図14は、本実施例の液晶表示パネルの駆動方法における1/Rフレーム期間の長さと横筋レベルとの関係の一例を示す模式グラフ図である。図15は、本実施例の液晶表示パネルの駆動方法における1/Rフレーム期間の長さと第1の駆動回路の温度との関係の一例を示す模式グラフ図である。

なお、図14において、横軸は、1フレーム期間における1/Rフレーム期間の個数Rであり、縦軸は、横筋レベルの相対値LVである。また、図14における横筋レベルLVは、図8に示した画素電極VP<sub>q</sub>を有する画素およびその周辺の画素における横筋レベルを1にしている。

また、図15において、横軸は、1フレーム期間における1/Rフレーム期間の個数Rであり、横軸は、第1の駆動回路2の温度TDRV( )である。また、図15における温度TDRVは、1フレーム期間が1/120秒である120Hz駆動の液晶表示装置において、25°の室内で、あらかじめ定められた映像または画像を120分間表示させたときの第1の駆動回路2の温度である。

20

## 【0138】

本実施例の液晶表示パネル1の駆動方法のように、1フレーム期間を、ほぼ同じ長さのR個の1/Rフレーム期間に分割し、1フレーム期間に1本の映像信号線DLに加える階調電圧の電位とコモン電圧の電位との高低の関係を、1/Rフレーム期間毎に反転させると、上記のように、表示領域DAにおける最大の横筋レベルと最小の横筋レベルとの差が、図8に示した場合に比べて小さくなる。

30

## 【0139】

しかしながら、1/Rフレーム期間毎に反転させた場合の最大の横筋レベルと、反転させない場合(図8に示した場合)の最大の横筋レベルとを比較した場合は、たとえば、図14に示すような関係になる。すなわち、1/2フレーム期間毎に反転させる場合、最大の横筋レベルは、反転させない場合の最大の横筋レベルとほぼ等しくなる。

## 【0140】

したがって、本実施例の液晶表示パネル1の駆動方法では、個数Rを、3個以上にすることが望ましい。このとき、個数Rを多くしていく、1/Rフレーム期間を短くしていくば、横筋レベルの相対値LVは、0.5に近づいていく。またこのとき、個数Rの最大値は、液晶表示パネル1に設けられた走査信号線GLの本数であり、個数Rが最大値のときに、横筋レベルの相対値LVが最も小さくなる。

40

## 【0141】

しかしながら、個数Rを多くしていくと、1本の映像信号線DLに加える階調電圧の電位とコモン電圧の電位との関係を反転させる回数が増える。そのため、個数Rを多くしていくと、それに応じて第1の駆動回路2における消費電力や発熱量が増大する。

## 【0142】

本願発明者が、1フレーム期間における1/Rフレーム期間の個数Rと、第1の駆動回路2の温度TDRV( )との関係を調べたところ、たとえば、図15に示すような関係になることがわかった。なお、図15は、上記のように、25°の室内で、あらかじめ定められた映像または画像を120分間表示させたときの個数Rと第1の駆動回路2の温度TDRVとの関係の一例を示している。

50

## 【0143】

このように、個数 R を多くし、1 / R フレーム期間を短くしていくと、横筋レベル LV を低く抑えることができる一方で、液晶表示装置を動作させているときの第 1 の駆動回路 2 の温度が高くなる。第 1 の駆動回路 2 の温度が高くなると、液晶表示パネル 1 や第 1 の駆動回路 2 など収容している筐体の内部温度が上昇し、たとえば、当該第 1 の駆動回路 2 や液晶表示パネル 1 の動作が不安定になり、表示品質が低下するおそれがある。

## 【0144】

したがって、本実施例の液晶表示パネル 1 の駆動方法では、1 フレーム期間を 1 / R フレーム期間に分割するときの個数 R を、たとえば、3 以上 20 以下の整数のいずれかにすることが望ましい。このようにすると、液晶表示装置を動作させたときの第 1 の駆動回路 2 の温度は、従来の個数 R が 1 の場合に比べて 2 ~ 3 度しか上昇しないので、横筋による表示品質の低下、および温度上昇による表示品質の低下の両方を抑えることができる。

10

## 【0145】

なお、上記のような駆動方法で液晶表示パネル 1 を駆動させる場合は、第 1 の駆動回路 2 において階調電圧を生成する順番や、階調電圧の電位とコモン電圧の電位との関係を調整（制御）すればよい。このとき、第 1 の駆動回路 2 は、上記のような方法で、それぞれの映像信号線 DL に階調電圧を入力できる回路構成であればよく、特定の回路構成に限定されることは言うまでもない。

20

## 【0146】

以上説明したように、本実施例の液晶表示パネル 1 の駆動方法によれば、千鳥配置の液晶表示パネルを有する液晶表示装置の、横筋による画質の低下を目立ちにくくすることができる。

20

## 【0147】

また、本実施例の液晶表示パネル 1 の駆動方法によれば、千鳥配置の液晶表示パネルを有する液晶表示装置の、画質の低下を防ぐことと、第 1 の駆動回路 2 の消費電力および発熱量を抑えることを両立できる。

30

## 【0148】

以上、本発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において、種々変更可能であることはもちろんである。

## 【0149】

たとえば、前記実施例では、液晶表示パネル 1 の駆動方法について説明しているが、本発明は、これに限らず、千鳥配置の液晶表示パネル 1 と同様の構成の表示パネルを有する表示装置であれば適用できることはもちろんである。

40

## 【図面の簡単な説明】

## 【0150】

【図 1 ( a )】液晶表示装置の概略構成の一例を示す模式図である。

【図 1 ( b )】液晶表示パネルの 1 つの画素の回路構成の一例を示す模式図である。

40

【図 1 ( c )】液晶表示パネルの 1 つの画素の回路構成の別の表現方法の一例を示す模式図である。

【図 2】従来の液晶表示パネルにおける画素電極と映像信号線との接続方法の一例を示す模式図である。

【図 3 ( a )】液晶表示パネルを列毎反転駆動で駆動するときの画素の極性を示す模式図である。

【図 3 ( b )】階調電圧の出力方法の一例を示す模式図である。

【図 4 ( a )】液晶表示パネルをドット反転駆動で駆動するときの画素の極性を示す模式図である。

【図 4 ( b )】階調電圧の出力方法の一例を示す模式図である。

50

【図 5】本発明に関わる液晶表示パネルにおける画素の配置の一例を示す模式図である。

【図6(a)】図5に示した液晶表示パネルをドット反転駆動で駆動するときの画素の極性を示す模式図である。

【図6(b)】階調電圧の出力方法の一例を示す模式図である。

【図7】千鳥配置の液晶表示パネルにおける寄生容量の一例を示す模式図である。

【図8】図7に示した画素電極の電位の推移の一例を示す模式図である。

【図9(a)】本発明による一実施例の液晶表示パネルの駆動方法の原理を示す模式図である。

【図9(b)】本実施例の液晶表示パネルの駆動方法において1フレーム期間を2個の1/2フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

【図10】本実施例の液晶表示パネルの駆動方法において1フレーム期間を3個の1/3フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。 10

【図11】本実施例の液晶表示パネルの駆動方法において1フレーム期間を4個の1/4フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

【図12】本実施例の液晶表示パネルの駆動方法において1フレーム期間を5個の1/5フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

【図13】本実施例の液晶表示パネルの駆動方法において1フレーム期間を6個の1/6フレーム期間に分割した場合の画素電極の電位の推移の一例を示す模式図である。

【図14】本実施例の液晶表示パネルの駆動方法における1/Rフレーム期間の長さと横筋レベルとの関係の一例を示す模式図である。

【図15】本実施例の液晶表示パネルの駆動方法における1/Rフレーム期間の長さと第1の駆動回路の温度との関係の一例を示す模式グラフ図である。 20

#### 【符号の説明】

##### 【0151】

1 ... 液晶表示パネル

2 ... 第1の駆動回路

3 ... 第2の駆動回路

4 ... 制御回路

5 ... バックライト

GL, GL<sub>0</sub> ~ GL<sub>5</sub>, GL<sub>m</sub>, GL<sub>m+1</sub>, GL<sub>p</sub>, GL<sub>p+1</sub>, GL<sub>q</sub>, GL<sub>q+1</sub>, GL<sub>M-1</sub>, GL<sub>M</sub> ... 走査信号線 30

DL, DL<sub>0</sub> ~ DL<sub>7</sub>, DL<sub>n</sub>, DL<sub>n+1</sub> ... 映像信号線

Tr ... TFT素子

PX, PX<sub>1</sub>, PX<sub>p</sub>, PX<sub>p+1</sub>, PX<sub>q</sub>, PX<sub>q+1</sub>, PX<sub>M</sub> ... 画素電極

VD<sub>n</sub>, VD<sub>n+1</sub> ... 階調電圧

VP<sub>p</sub>, VP<sub>p+1</sub>, VP<sub>q</sub>, VP<sub>q+1</sub> ... 画素電極の電位

VCOM ... コモン電圧

VG<sub>p</sub>, VG<sub>p+1</sub>, VG<sub>q</sub>, VG<sub>q+1</sub> ... 走査信号

【図1(a)】

図1(a)

【図1(b)】

図1(b)

【図1(c)】

図1(c)

【図2】

図2

【図3(a)】

図3(a)

【図3(b)】

図3(b)

【図4(a)】

図4(a)

【図4(b)】

図4(b)

【図5】

図5

【図6(a)】

図6(a)

【図6(b)】

図6(b)

【図7】

図7

【図8】

【図9(a)】

図9(a)

【図9(b)】

【図10】

図10

【図 1 1】

【図 1 3】

【図 1 2】

【図 1 4】

図14

【図 1 5】

図15

## フロントページの続き

(51) Int.Cl.

| F I     | テー<br>マ<br>コ<br>ード |

|---------|--------------------|

| G 0 9 G | 3/20 6 4 2 A       |

| G 0 9 G | 3/20 6 2 4 D       |

| G 0 2 F | 1/133 5 5 0        |

| G 0 2 F | 1/133 5 2 5        |

| G 0 2 F | 1/133 5 7 5        |

(参考)

(72) 発明者 山崎 佐知子

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

F ターム(参考) 2H093 NA16 NA32 NA33 NA34 NA43 NA53 NC12 NC13 NC16 NC34

ND06 ND35 ND39

2H193 ZA04 ZC02 ZC15 ZC20 ZD23 ZF36

5C006 AA16 AA22 AC26 AF44 AF83 BB16 BB21 BC06 BC23 FA22

FA47

5C080 AA10 BB05 CC03 DD01 EE29 EE30 FF11 JJ02 JJ03 JJ04

JJ05 KK02 KK07 KK43 KK47 KK50

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2010060856A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2010-03-18 |

| 申请号            | JP20082226644                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2008-09-04 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 桶 隆太郎<br>小野 記久雄<br>山崎 佐知子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 桶 隆太郎<br>小野 記久雄<br>山崎 佐知子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/36 G09G3/20.611.H G09G3/20.621.M G09G3/20.621.B G09G3/20.623.D G09G3/20.642.A<br>G09G3/20.624.D G02F1/133.550 G02F1/133.525 G02F1/133.575                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA32 2H093/NA33 2H093/NA34 2H093/NA43 2H093/NA53 2H093/NC12 2H093/NC13 2H093/NC16 2H093/NC34 2H093/ND06 2H093/ND35 2H093/ND39 2H193/ZA04 2H193/ZC02 2H193/ZC15 2H193/ZC20 2H193/ZD23 2H193/ZF36 5C006/AA16 5C006/AA22 5C006/AC26 5C006/AF44 5C006/AF83 5C006/BB16 5C006/BB21 5C006/BC06 5C006/BC23 5C006/FA22 5C006/FA47 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD01 5C080/EE29 5C080/EE30 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/KK02 5C080/KK07 5C080/KK43 5C080/KK47 5C080/KK50 2H193/ZA07 2H193/ZA08 2H193/ZB09 2H193/ZC04 2H193/ZC07 2H193/ZC13 2H193/ZC16 2H193/ZD13 2H193/ZF05 2H193/ZF42 2H193/ZF44 2H193/ZG02 2H193/ZG12 2H193/ZG14 2H193/ZH46 2H193/ZH52 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

## 摘要(译)

要解决的问题：提供一种可以防止液晶显示装置中的图像质量劣化的技术。

SOLUTION：在显示装置中，每个具有第一电极和第二电极的像素以矩阵排列，第一电极连接到第一视频信号线，第一电极连接到第二视频信号线，交替排列在第一视频之间信号线和第二视频信号线彼此相邻。一个帧周期被分成相等长度的R个1 / R周期，施加到一个视频信号线的灰度电压的电位与在一个帧周期期间施加到第二电极的电压的电平之间的电平关系是每1 / R期间逆转。施加到第一视频信号线的灰度电压的电位和施加到第二电极的电压的电位之间的电位关系与施加到第二视频信号线的灰度电压的电位和电位的电位之间的电位关系相反。施加到第二电极的电压，R是≥2或等于或低于扫描信号线数的整数。

Z