## (19) **日本国特許庁(JP)**

(51) Int.Cl.

# (12) 公 開 特 許 公 報(A)

FI

(11)特許出願公開番号

テーマコード (参考)

特開2009-14988 (P2009-14988A)

(43) 公開日 平成21年1月22日(2009.1.22)

長野県安曇野市豊科田沢6925 エプソ ンイメージングデバイス株式会社内 Fターム(参考) 2H093 NA16 NA80 NC10 NC12 NC18

ND39 ND60 NH12

NC26 NC34 NC35 NC49 ND38

最終頁に続く

| (51) 1111. 01. |       |                 | 1 1            |          |             | / · · ·         | F (多つ) |

|----------------|-------|-----------------|----------------|----------|-------------|-----------------|--------|

| G09G           | 3/36  | (2006.01)       | GO9G           | 3/36     |             | 2H093           |        |

| G09G           | 3/20  | (2006.01)       | GO9G           | 3/20     | 624A        | 5C006           |        |

| G02F           | 1/133 | (2006.01)       | GO9G           | 3/20     | 624D        | 5C080           |        |

|                |       |                 | GO9G           | 3/20     | 670D        |                 |        |

|                |       |                 | GO9G           | 3/20     | 612G        |                 |        |

|                |       |                 | 審査請求 未         | 請求請求     | 求項の数 5 OL   | (全 10 頁)        | 最終頁に続く |

| (21) 出願番号      |       | 特願2007-176351 ( | (P2007-176351) | (71) 出願。 | 人 304053854 |                 |        |

| (22) 出願日       |       | 平成19年7月4日(2     | 2007.7.4)      |          | エプソンイフ      | <b>リージングデバイ</b> | ス株式会社  |

|                |       |                 |                |          | 長野県安曇野      | F市豊科田沢69        | 25     |

|                |       |                 |                | (74)代理。  | 人 100095728 |                 |        |

|                |       |                 |                |          | 弁理士 上柳      | <b>T</b> 雅誉     |        |

|                |       |                 |                | (74)代理。  | 人 100107261 |                 |        |

|                |       |                 |                |          | 弁理士 須潤      | ፟ 修             |        |

|                |       |                 |                | (74)代理。  | 人 100127661 |                 |        |

|                |       |                 |                |          | 弁理士 宮城      | 一彦              |        |

|                |       |                 |                | (72) 発明: | 者 田尻 憲一     |                 |        |

## (54) 【発明の名称】液晶表示装置

## (57)【要約】

【課題】保持容量線駆動方式を用いた液晶表示装置において、電源立ち上げ時の保持容量線の電位が不定状態となることを防止する。

【解決手段】液晶表示装置の電源30等を立ち上げるための信号を検出すると、最初にゲートドライバ15を起動させることにより発生されたゲート信号に基づいて、保持容量線駆動回路20の第1の極性スイッチング素子SW1のスイッチング状態を決定し、第1の極性スイッチング素子SW1のスイッチング状態の決定後に、保持容量線駆動回路20の高レベルVCOMH及び低レベルVCOMLの電位を発生させるとともに、共通電極ドライバ16に電源電位を供給する。

【選択図】図3

## 【特許請求の範囲】

#### 【請求項1】

ゲート線と、このゲート線にゲート信号を供給するゲートドライバと、ソース線と、このソース線にソース信号を供給するソースドライバと、前記ソース線に接続された第 1 のスイッチング素子を通してソース信号が印加される画素電極と、この画素電極と共通電極との間に配置された液晶と、前記共通電極に共通電極信号を供給する共通電極ドライバと、前記画素電極と前記保持容量線との間に接続された保持容量と、ゲート信号に基づいて前記保持容量線を第 1 の電位と第 2 の電位に交互に切り換える第 2 のスイッチング素子を有する保持容量線駆動回路と、を備えた液晶表示装置において、

該液晶表示装置の電源を立ち上げるための信号を検出すると、最初に前記ゲートドライバを起動させることにより発生されたゲート信号に基づいて前記第2のスイッチング素子のスイッチング状態を決定し、第2のスイッチング素子のスイッチング状態の決定後に、前記第1の電位及び第2の電位を発生させるように制御を行うシーケンス制御回路を設けたことを特徴とする液晶表示装置。

#### 【請求項2】

前記シーケンス制御回路は、前記共通電極ドライバに電源を供給した後に、前記画素スイッチング素子を通して前記画素電極に液晶の表示をオフするためのオフ電位を書き込むように制御を行うことを特徴とする請求項1に記載の液晶表示装置。

#### 【請求項3】

前記シーケンス制御回路は、該液晶表示装置の電源を立ち上げるための信号を検出すると、前記ソース線を前記共通電極と短絡させることを特徴とする請求項1又は請求項2に記載の液晶表示装置。

#### 【請求項4】

前記ソース線と前記共通電極の間に接続された第3のスイッチング素子を備え、前記シーケンス制御回路は第3のスイッチング素子をオンさせることにより、前記ソース線を前記 共通電極と短絡させることを特徴とする請求項3に記載の液晶表示装置。

#### 【請求項5】

前記保持容量線に、前記ゲート信号に基づいて前記保持容量線を第1の電位と第2の電位に交互に切り換える、もう1つのスイッチング素子を設けたことを特徴とする請求項1、 2、3、4のいずれかに記載の液晶表示装置。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、液晶表示装置に関し、特に、電源オン時のシーケンス制御を行うシーケンス制御機能を備えた液晶表示装置に関する。

#### 【背景技術】

## [0002]

従来より、液晶表示装置の駆動方式として保持容量線駆動方式が知られている。この方式は、保持容量線と画素電極の間に保持容量を形成し、画素に表示信号を書き込んだ後に、保持容量線の電位を高レベルと低レベルに交互に切り換えることにより、画素電位を正又は負の方向に変化させる。これにより、表示信号のダイナミックレンジを小さくすることができるので低消費駆動が可能になる。ゲートラッチ方式の場合、ゲートドライバのゲートスキャン動作により出力されるゲート信号に基づいて、極性選択信号(高電位又は低電位のいずれかを選択するための信号)をラッチし、ラッチした極性選択信号に基づいて、スイッチング素子をスイッチングさせて保持容量線の電位を切り換える。

## [0003]

従来、このゲートラッチ方式の液晶表示装置の電源オン時には、電源を立ち上げた後に 、ゲートドライバのゲートスキャン動作を開始していた。

## [0004]

尚、この保持容量線駆動方式を用いた液晶表示装置については、特許文献1に記載され

10

20

30

40

ている。

【特許文献1】特開2002-196358号公報

【発明の開示】

【発明が解決しようとする課題】

[00005]

しかしながら、ゲートラッチ方式の液晶表示装置にあっては、ゲートドライバのゲートスキャン動作開始前では、スイッチング素子のスイッチング状態が不定であり、電源立ち上げ時に保持容量線の電位が不定になるという問題があった。

[0006]

特に、1本の保持容量線の両端にそれぞれスイッチング素子を設けた構成では、電源立ち上げ時に、ショートが起こる可能性がある。即ち、一方のスイッチング素子が高レベルの電位を選択し、他方のスイッチング素子が低レベルの電位を選択した場合に両電位の間でショートが起こる。

【課題を解決するための手段】

[0007]

本発明の液晶表示装置は、ゲート線と、このゲート線にゲート信号を供給するゲートドライバと、ソース線と、このソース線にソース信号を供給するソースドライバと、ソース線に接続された第1のスイッチング素子を通してソース信号が印加される画素電極と、この画素電極と共通電極との間に配置された液晶と、共通電極に共通電極信号を供給する共通電極ドライバと、画素電極と保持容量線との間に接続された保持容量と、ゲート信号に基づいて保持容量線を第1の電位と第2の電位に交互に切り換える第2のスイッチング素子を有する保持容量線駆動回路と、を備えた液晶表示装置において、該液晶表示装置の電源を立ち上げるための信号を検出すると、最初にゲートドライバを起動させることにより発生されたゲート信号に基づいて第2のスイッチング素子のスイッチング状態を決定し、第2のスイッチング素子のスイッチング状態の決定後に、第1の電位及び第2の電位を発生させるように制御を行うシーケンス制御回路を設けたことを特徴とする。

【発明の効果】

[00008]

本発明によれば、保持容量線駆動方式を用いた液晶表示装置において、電源立ち上げ時の保持容量線電位の不定状態を無くすことができる。特に、1本の保持容量線の両端にそれぞれスイッチング素子を設けた構成において、電源立ち上げ時のショートを防止することができる。

【発明を実施するための最良の形態】

[0009]

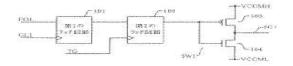

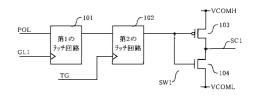

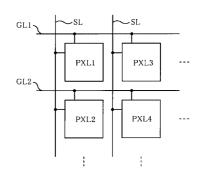

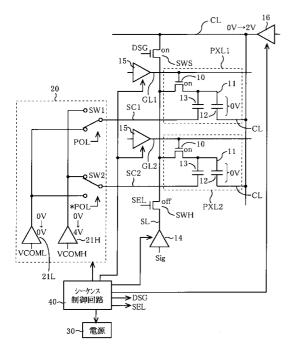

本発明の実施形態による液晶表示装置について図面を参照しながら説明する。図1に示すように、ソース線 S L と第1のゲート線 G L 1の交差点に対応して画素 P X L 1が設けられ、ソース線 S L と第2のゲート線 G L 2の交差点に対応して画素 P X L 2が設けられている。図1では2つの画素 P X L 1 , P X L 2 だけを示したが、実際には図2のように、複数の画素 P X L 1 , P X L 2 , P X L 3 , P X L 4 , ・・・がマトリクス状に配置されている。

[0010]

[0011]

画素 P X L 1 , P X L 2 には、 N チャネル型の薄膜トランジスタ(以下、 T F T という)からなる画素トランジスタ 1 0 、 画素トランジスタ 1 0 のドレインに接続された画素電極 1 1、 画素電極 1 1 と共通電極 C L の間に配置された液晶 1 2 が設けられている。また、第 1 行目の画素 P X L 1 に対応して、第 1 の保持容量線 S C 1 が設けられ、画素 P X L 1 の画素電極 1 1 と第 1 の保持容量線 S C 1 との間に保持容量 1 3 が設けられている。また、第 2 行目の画素 P X L 2 に対応して、第 2 の保持容量線 S C 2 が設けられ、画素 P X L 2 の画素電極 1 1 と第 2 の保持容量線 S C 2 との間に保持容量 1 3 が設けられている。

画素PXL1,PXL2の画素トランジスタ10(本発明の第1のスイッチング素子の

10

20

30

40

ー例)のソースは、ソース線SLに接続されている。1行目の画素PXL1の画素トランジスタ10のゲートは、第1のゲート線GL1に接続され、2行目の画素PXL2の画素トランジスタ10のゲートは、第2のゲート線GL2に接続されている。

[0012]

また、ソース信号Sig(表示信号)をソース線SLに供給するソースドライバ14が設けられている。ソース信号Sigは、一定周期(例えば、一水平周期)で基準電位に対して極性が反転するようになっている。ソースドライバ14とソース線SLとの間には、Nチャネル型TFTからなる水平スイッチング素子SWHが接続されており、水平スイッチング素子SWHが制御信号に応じてオンすると、ソースドライバ14からソース線SLへソース信号Sigを供給することができるようになっている。

[0013]

また、ゲート信号を第1のゲート線GL1,第2のゲート線GL2に供給するゲートドライバ15が設けられている。ゲートドライバ15には、画素トランジスタ10をオンさせるための高レベル(例えば8V)のゲート信号と、画素トランジスタ10をオフさせるための低レベル(例えば・4V)のゲート信号を発生するためDC-DCコンバータ(不図示)が設けられている。

[0014]

ソース線SLと共通電極CLの間には、Nチャネル型TFTからなるスイッチング素子SWSが接続されている。このスイッチング素子SWSは、電源オフ時には制御信号DSGに応じてオンし、ソース線SLを共通電極CLと短絡するために用いられる。

[0015]

また、通常動作時に共通電極 C L に共通電極信号を供給するための共通電極ドライバ 1 6 が設けられている。共通電極信号は、例えば 2 V の直流電位である。

[0016]

また、各保持容量線SCに高レベルの電位VCOMH(例えば、4V)と低レベルの電位VCOML(例えば0V)を1フレーム期間毎に交互に供給するように駆動を行う保持容量線駆動回路20が設けられている。保持容量線駆動回路20は、高レベルの電位VCOMHを出力する第1の保持容量ドライバ21日と、低レベルの電位VCOMLを出力する第2の保持容量ドライバ21L、第1の極性スイッチング素子SW1、第2の極性スイッチング素子SW2を有している。

[0017]

第1の極性スイッチング素子SW1は、極性選択信号POLに応じてスイッチングし、第1の保持容量ドライバ21日からの高レベルの電位VCOMHと第2の保持容量ドライバ21Lからの低レベルの電位VCOMLとを第1の保持容量線SC1に交互に出力する。第2の極性スイッチング素子SW2は、極性選択信号\*POL(極性選択信号POLの反転信号)に応じて、第1の極性スイッチング素子SW1と相補的にスイッチングし、第1の保持容量ドライバ21日からの低レベルの電位VCOMLとを第2の保持容量線SC2に交互に出力する。

[0018]

これにより、隣接する第1の保持容量線SC1と第2の保持容量線SC2は、互いに逆極性(一方が高レベルで他方が低レベル)になるように駆動される。

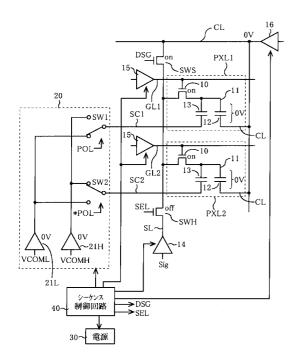

[0019]

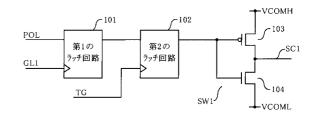

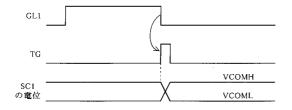

図3に、ゲートラッチ方式を用いた保持容量線駆動回路20の具体的な構成を示す。ここでは、第1の保持容量線SC1を駆動する回路部分だけを示している。また、図4にこの回路部分の動作タイミング図を示す。この回路は、第1のラッチ回路101、第2のラッチ回路102、第1の極性スイッチング素子SW1を有している。第1の極性スイッチング素子SW1は、第2のラッチ回路102の出力がゲートに印加されたPチャネル型TFT103及びNチャネル型TFT104で形成されている。Pチャネル型TFT103のソースには高レベルの電位VCOMLが印加され、Nチャネル型TFT103及スには低レベルの電位VCOMLが印加されている。また、Pチャネル型TFT103及

10

20

30

40

びNチャネル型TFT104のドレインは第1の保持容量線SC1に接続されている。

## [0020]

第1のラッチ回路101は、ゲートドライバ15から第1のゲート線GL1に出力されるゲート信号の立ち上がり(即ち、低レベルから高レベルへの変化)に応じて、極性選択信号POLをラッチする。第2のラッチ回路102は、タイミング制御信号TGの立ち上がりに応じて、第1のラッチ回路101によって保持された極性選択信号POLをラッチする。タイミング制御信号TGは、ゲート信号が低レベルに立ち下がった後に、立ち上がるように調整されている。

## [ 0 0 2 1 ]

したがって、タイミング制御信号TGの立ち上がりに応じて、第2のラッチ回路102の出力は更新され、その出力が高レベルのときはNチャネル型TFT104がオンして第1の保持容量線SC1に低レベルの電位VCOMLが供給され、第2のラッチ回路102の出力が低レベルのときはPチャネル型TFT103がオンして第1の保持容量線SC1に高レベルの電位VCOMHが供給されるようになっている。

#### [0022]

尚、第2の保持容量線SC2を駆動する回路部分も同様に構成されるが、第1のラッチ回路101は、ゲートドライバ15から第2のゲート線GL2に出力されるゲート信号の立ち上がりに応じて、反転された極性選択信号\*POLをラッチする。

#### [0023]

また、ソースドライバ14、ゲートドライバ15、共通電極ドライバ16、保持容量線駆動回路20には、電源30から電源電位が供給される。そして、電源オン時に、ソースドライバ14、ゲートドライバ15、DC-DCコンバータ、共通電極ドライバ16、スイッチング素子SWS、水平スイッチング素子SWH、保持容量線駆動回路20、電源30等の動作をシーケンス制御するシーケンス制御回路40が設けられている。シーケンス制御回路40は、この液晶表示装置の電源をオンするための信号、例えば、電源オンコマンドを検出すると、シーケンス制御を開始するように構成されている。

#### [0024]

上述の液晶表示装置の通常動作時における書き込み動作は以下の通りである。ここでは、1行目の画素 P X L 1 への書き込みについて説明する。ここで、書き込み時には、スイッチング素子 S W S はオフし、水平スイッチング素子 S W H はオンしている。まず、ゲートドライバ 1 5 から高レベルのゲート信号が第 1 のゲート線 G L 1 に一水平期間出力されると、それに応じて画素トランジスタ 1 0 がオンする。このとき、スイッチング素子 S W H はオンしている。そして、ソースドライバ 1 4 からソース線 S L にソース信号 S i g が出力されると、ソース信号 S i g は画素トランジスタ 1 0 を通して画素 P X L 1 に書き込まれる(画素書き込み)。即ち、ソース信号 S i g は画素トランジスタ 1 0 を通して画素電極 1 1 に印加され保持容量 1 3 によって保持される。

## [0025]

その後、ゲート信号が低レベルに立ち下がると、保持容量線駆動回路20の第1の極性スイッチング素子SW1が切り換えられ、第1の保持容量線SC1の電位が変化する。即ち、第1の保持容量線SC1の電位は、高レベルの電位VCOMHから低レベルの電位VCOMLに、又は低レベルVCOMLから高レベルVCOMHに変化する。すると、保持容量13の容量カップリングにより、画素電極11の電位は、画素書き込みされた電位から正又は負の方向に変化する。例えば、第1の保持容量線SC1の電位は、高レベルの電位VCOMLに変化したとすると、画素電極11の電位は、負の方向に変化する。そして、画素電極11に保持された電位に応じて液晶12の光学的制御が行われ、表示が行われる。このような保持容量線駆動方式によれば、画素電極11の電位変化の分だけ、ソース信号Sigのダイナミックレンジを小さくすることができるため、低消費電力駆動が可能である。

## [0026]

50

10

20

30

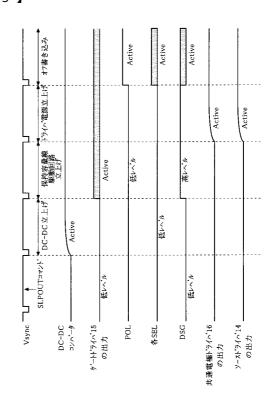

本発明の特徴は、シーケンス制御回路40による電源立ち上げ時のシーケンス制御にあり、以下、これについて図5のタイミング図と、図6の回路図を参照して説明する。なお、図6は、電源立ち上げ時のシーケンス制御を説明する回路図であるが、その回路構成は、図1に示したものと同様である。

## [0027]

まず、液晶表示装置は電源立ち上げ前は、スリープ状態であり、電源30等はオフ状態になっているものとする。この状態において液晶表示装置の電源をオンするための信号として、例えば、電源立ち上げコマンド(SLPOUTコマンド)が検出されると、その後の垂直同期信号Vsyncに同期して、まずゲートドライバ15を起動させるためにDC- DCコンバータを起動する。これにより、画素トランジスタ10をオンさせるための高レベルのゲート信号と、画素トランジスタ10をオフさせるための低レベルのゲート信号を作成するための正及び負の電源電位が発生され、ゲートドライバ15はゲートスキャン動作可能な状態になる。

## [0028]

その後、次に到来する垂直同期信号 V s y n c に同期して、即ち、その次のフレーム期間に入ると、ゲートドライバ15はゲートスキャン動作を開始し、第1のゲート線GL1、第2のゲート線GL2・・・に順次ゲート信号を供給する。これにより、ゲート信号の立ち上がりに基づいて、極性選択信号 P O L が第1のラッチ回路101にラッチされる。第1のラッチ回路101にラッチされた極性選択信号 P O L は、タイミング信号 T G に応じて第2のラッチ回路102にラッチされる。こうして、第1の極性スイッチング素子 S W 1 のスイッチング状態が決定され、同様にして、第2の極性スイッチング素子 S W 2 のスイッチング状態も決定される。また、このフレーム期間に入ると、制御信号 D S G が高レベルになり、スイッチング素子 S W S がオンすることでソース線 S L と共通電極 C L が短絡される。

## [0029]

そして、次に到来する垂直同期信号 V s y n c に同期して、即ち、その次のフレーム期間に入ると、ソースドライバ14、共通電極ドライバ16、及び保持容量線駆動回路20の第1の保持容量ドライバ21H及び第2の保持容量ドライバ21Lに対して、電源30から電源電位が供給される。これにより、第1の保持容量ドライバ21Hから高レベルの電位 V C O M H (例えば、4 V)及び低レベルの電位 V C O M L (例えば、0 V)が発生する。このとき、第1及び第2の極性スイッチング素子SW1,SW2のスイッチング状態は既に決定されているので、第1及び第2の極性スイッチング素子SW1,SW2のスイッチング状態に応じて、第1及び第2の保持容量線SC1,SC2の電位も決定されることになる。

# [0030]

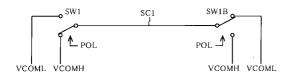

また、図7に示すように、第1の保持容量線SC1の一端に接続された第1の極性スイッチング素子SW1に加えて、同じ構成を有するもう1つの極性スイッチング素子SW1Bを第1の保持容量線SC1の他端に接続して、保持容量線駆動回路20の駆動能力を向上させることがある。このような回路構成の場合に、2つの極性スイッチング素子SW1,SW1Bのスイッチング状態が決定された後に、保持容量線駆動回路20の第1の保持容量ドライバ21Lに対して、電源30から電源電位が供給されるので、高レベルの電位VCOMH及び低レベルの電位VCOMLの間でショートが起こることが防止される。

## [0031]

その後、次に到来する垂直同期信号 V s y n c に同期して、即ち、その次のフレーム期間において、オフ表示、例えば黒表示に対応した電位を各画素 P X L 1 に書き込む。即ちオフ書き込みを行う。他の画素に対しても同様である。このオフ書き込みの動作は、前述した通常動作時の書き込み動作と基本的には同じである。尚、このオフ書き込みは必要に応じて行われるものであり、省略されてもよい。

## 【図面の簡単な説明】

10

20

30

## [0032]

- 【図1】本発明の実施形態による液晶表示装置を示す回路図である。

- 【図2】本発明の実施形態による液晶表示装置の画素の配置図である。

- 【図3】本発明の実施形態による液晶表示装置の保持容量線駆動回路の具体的な構成を示す図である。

- 【図4】本発明の実施形態による液晶表示装置の保持容量線駆動回路の動作タイミング図である。

- 【図 5 】本発明の実施形態による液晶表示装置の電源立ち上げ時のシーケンスを説明するタイミング図である。

- 【図6】本発明の実施形態による液晶表示装置を示す回路図である。

- 【図7】本発明の実施形態による液晶表示装置の保持容量線駆動回路の構成を示す図である。

## 【符号の説明】

## [ 0 0 3 3 ]

10 画素トランジスタ 11 画素電極

1 2 液晶 1 3 保持容量

14 ソースドライバ 15 ゲートドライバ

6 共通電極ドライバ 20 保持容量線駆動回路

2 1 H 第 1 の 保 持 容 量 ド ラ イ バ

2 1 L 第 2 の 保 持 容 量 ド ラ イ バ

3 0 電源 4 0 シーケンス制御回路

101 第1のラッチ回路 102 第2のラッチ回路

103 Pチャネル型TFT 104 Nチャネル型TFT

C L 共通電極

S L ソース線

PXL1,PXL2,PXL3,PXL4··· 画素

G L 1 , G L 2 ゲート線 S C 1 , S C 2 保持容量線

SWS スイッチング素子 SWH 水平スイッチング素子

SW1 第1の極性スイッチング素子

SW1B 極性スイッチング素子

SW2 第2の極性スイッチング素子

30

20

# 【図1】

# 【図2】

# 【図3】

## 【図4】

# 【図5】

# 【図6】

# 【図7】

#### \_\_ フロントページの続き

| (51) Int.CI. |       |      |      |      | FΙ   |         |      |      |       |      |      | テーマ | コード( | (参考) |

|--------------|-------|------|------|------|------|---------|------|------|-------|------|------|-----|------|------|

|              |       |      |      |      | (    | G 0 9 0 | G 3/ | '20  | 6 2 2 | D    |      |     |      |      |

|              |       |      |      |      | (    | G 0 9 0 | G 3/ | 20   | 6 2 4 | Е    |      |     |      |      |

|              |       |      |      |      | (    | G 0 9 0 | G 3/ | 20   | 6 2 3 | C    |      |     |      |      |

|              |       |      |      |      | (    | G 0 9 0 | G 3/ | 20   | 6 2 3 | D    |      |     |      |      |

|              |       |      |      |      | (    | G 0 9 0 | G 3/ | 20   | 6 2 3 | R    |      |     |      |      |

|              |       |      |      |      | (    | G 0 9 0 | G 3/ | 20   | 6 1 1 | Α    |      |     |      |      |

|              |       |      |      |      | (    | 3 0 2 F | = 1/ | 133  | 5 5 0 |      |      |     |      |      |

|              |       |      |      |      | (    | 3 0 2 F | = 1/ | 133  | 5 0 5 |      |      |     |      |      |

|              |       |      |      |      |      |         |      |      |       |      |      |     |      |      |

| F ターム(参考)    | 5C006 | AA16 | AC11 | AC21 | AC22 | AC25    | AC27 | AF44 | AF51  | AF53 | AF64 |     |      |      |

|              |       | AF67 | AF68 | AF69 | AF71 | BB16    | BC03 | BC13 | BF04  | BF11 | BF24 |     |      |      |

|              |       | BF25 | BF27 | BF33 | BF34 | BF42    | FA16 | FA31 | FA38  | FA46 | FA47 |     |      |      |

|              | 5C080 | AA10 | BB05 | DD09 | DD14 | DD18    | DD19 | DD26 | DD29  | EE26 | EE29 |     |      |      |

|              |       | FF03 | FF11 | JJ02 | JJ03 | JJ04    |      |      |       |      |      |     |      |      |

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                          |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| 公开(公告)号        | <u>JP2009014988A</u>                                                                                                                                                                                                            | 公开(公告)日                                                                                                                                                                                                              | 2009-01-22                                                                                      |  |  |  |  |

| 申请号            | JP2007176351                                                                                                                                                                                                                    | 申请日                                                                                                                                                                                                                  | 2007-07-04                                                                                      |  |  |  |  |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

| 申请(专利权)人(译)    | 爱普生影像设备公司                                                                                                                                                                                                                       |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

| [标]发明人         | 田尻憲一                                                                                                                                                                                                                            |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

| 发明人            | 田尻 憲一                                                                                                                                                                                                                           |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                     |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

| FI分类号          | G09G3/36 G09G3/20.624.A G09G3/20.624.D G09G3/20.670.D G09G3/20.612.G G09G3/20.622.D G09G3/20.624.E G09G3/20.623.C G09G3/20.623.D G09G3/20.623.R G09G3/20.611.A G02F1/133. 550 G02F1/133.505                                     |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

| F-TERM分类号      | /NC35 2H093/NC49 2H093/ND38<br>5C006/AC21 5C006/AC22 5C006/<br>/AF64 5C006/AF67 5C006/AF68 5<br>5C006/BF04 5C006/BF11 5C006/E<br>/BF42 5C006/FA16 5C006/FA31 5<br>5C080/DD09 5C080/DD14 5C080/<br>/EE29 5C080/FF03 5C080/FF11 5 | 2H093/ND39 2H093/ND60 2H0 AC25 5C006/AC27 5C006/AF4 C006/AF69 5C006/AF71 5C006 BF24 5C006/BF25 5C006/BF27 C006/FA38 5C006/FA46 5C006 DD18 5C080/DD19 5C080/DD C080/JJ02 5C080/JJ03 5C080/ ZC04 2H193/ZC24 2H193/ZD23 | 7 5C006/BF33 5C006/BF34 5C006<br>6/FA47 5C080/AA10 5C080/BB05<br>26 5C080/DD29 5C080/EE26 5C080 |  |  |  |  |

| 代理人(译)         | 须泽 修<br>宫坂和彦                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                       |                                                                                                                                                                                                                      |                                                                                                 |  |  |  |  |

## 摘要(译)

在使用存储电容器线驱动方法的液晶显示装置中,防止了在电源启动时存储电容器线的电位变为不确定状态。 当检测到用于激活液晶显示装置的电源30等的信号时,基于通过初始激活栅极驱动器15而产生的栅极信号,第一存储电容器线驱动电路20确定极性切换元件SW 1的切换状态,在确定第一极性切换元件SW 1和公共电极驱动器16的切换状态之后,产生存储电容器线驱动电路20的高电平VCOMH和低电平VCOML电位。供应潜力。 点域