(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-178047

(P2006-178047A)

(43) 公開日 平成18年7月6日(2006.7.6)

| (51) Int.C1.                | F 1                                                        | テーマコード (参考) |

|-----------------------------|------------------------------------------------------------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36                                                  | 2 H 093     |

| <b>G02F 1/133</b> (2006.01) | G02F 1/133 5 2 5                                           | 5 C 006     |

| <b>G09G 3/20</b> (2006.01)  | G02F 1/133 5 7 5<br>G09G 3/20 6 1 2 F<br>G09G 3/20 6 2 1 B | 5 C 080     |

|                             | 審査請求 未請求 請求項の数 6 O L (全 18 頁)                              | 最終頁に続く      |

|           |                              |            |                                                                                                     |

|-----------|------------------------------|------------|-----------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2004-369036 (P2004-369036) | (71) 出願人   | 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号                                                        |

| (22) 出願日  | 平成16年12月21日 (2004.12.21)     | (74) 代理人   | 100104695<br>弁理士 島田 明宏                                                                              |

|           |                              | (72) 発明者   | 西久保 圭志<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内                                                          |

|           |                              | F ターム (参考) | 2H093 NA16 NA31 NA32 NA43 NA53<br>NC03 NC10 NC12 NC13 NC21<br>NC22 NC26 NC34 NC49 ND06<br>ND35 ND58 |

|           |                              |            | 最終頁に続く                                                                                              |

(54) 【発明の名称】映像信号線駆動回路およびそれを備える液晶表示装置

## (57) 【要約】 (修正有)

【課題】正極性用および負極性用の階調電圧を好適値に容易に調整でき、基準電圧発生回路を簡易に構成できる映像信号線駆動回路およびそれを備える液晶表示装置を提供する。

【解決手段】映像信号線駆動回路に含まれる或るD/A変換回路3040は、正極性用抵抗分圧回路3041と、負極性用抵抗分圧回路3042と、選択回路3043とを備え、基準電圧発生回路700からの複数の基準電圧V<sub>r</sub>に基づき各抵抗分圧回路で生成される階調電圧から、表示制御回路200からの極性切換制御信号に応じて、受け取ったデジタル信号に対応する正極性の階調電圧と負極性の階調電圧とを選択回路3043によって交互に選択する。このことにより、基準電圧V<sub>r</sub>を直流にできるため基準電圧発生回路を簡易に構成でき、2つの抵抗分圧回路により正極性用および負極性用の階調電圧を好適値に容易に調整できる。

【選択図】 図4

## 【特許請求の範囲】

## 【請求項 1】

画像を表示するための表示部において複数の映像信号線と複数の走査信号線との交差部にそれぞれ対応してマトリクス状に配置された複数の画素形成部に設けられた画素電極と、前記画素電極との間に電圧を印加するために前記画素電極に対応して設けられた共通電極とを備え、前記共通電極に印加されるべき電圧を所定の2種類の電圧の間で所定の期間毎に交互に切り替える液晶表示装置における、前記画像を表す画像信号を受け取り前記画像信号に応じて前記複数の映像信号線に電圧を印加する映像信号線駆動回路であって、

前記複数の映像信号線に印加される電圧の基準となる所定の直流電圧に基づき前記共通電極の電位を基準とした正極性および負極性の電圧をともに含む複数の階調電圧を生成し、前記共通電極の電位を基準とした前記画素電極に印加される電圧の極性が前記所定の期間毎に逆になるよう、生成された前記複数の階調電圧から前記画像信号に対応する正極性または負極性の階調電圧を前記所定の期間毎に交互に選択し、選択された階調電圧を前記複数の映像信号線に印加することを特徴とする、映像信号線駆動回路。

## 【請求項 2】

前記画像を表す画像信号に含まれる前記画素形成部に与えられるべき画素値を示すデジタル信号をアナログ電圧信号に変換し出力するD/A変換回路を含み、

前記D/A変換回路は、

前記直流電圧を分圧することにより複数の正極性の階調電圧を生成する正極性抵抗分圧回路と、

前記直流電圧を分圧することにより複数の負極性の階調電圧を生成する負極性抵抗分圧回路と、

前記複数の正極性の階調電圧および前記複数の負極性の階調電圧から、前記デジタル信号に対応する階調電圧を選択することにより、前記アナログ電圧信号を生成する選択回路と

を含むことを特徴とする、請求項1に記載の映像信号線駆動回路。

## 【請求項 3】

画像を表示するための表示部において複数の映像信号線と複数の走査信号線との交差部にそれぞれ対応してマトリクス状に配置された複数の画素形成部に設けられた画素電極と、前記画素電極との間に電圧を印加するために前記画素電極に対応して設けられた共通電極と、前記画像を表す画像信号を受け取り前記画像信号に応じて前記複数の映像信号線に電圧を印加する映像信号線駆動回路と、前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、前記共通電極を駆動する共通電極駆動回路と、前記映像信号線駆動回路に対し前記複数の映像信号線に印加される電圧の基準となる所定の直流電圧を与える基準電圧発生回路とを備え、

前記共通電極駆動回路は、前記共通電極に印加されるべき電圧を所定の2種類の電圧の間で所定の期間毎に交互に切り替え、

前記映像信号線駆動回路は、前記基準電圧発生回路からの前記直流電圧に基づき前記共通電極の電位を基準とした正極性および負極性の電圧をともに含む複数の階調電圧を生成し、前記共通電極の電位を基準とした前記画素電極に印加される電圧の極性が前記所定の期間毎に逆になるよう、生成された前記複数の階調電圧から前記画像信号に対応する正極性または負極性の階調電圧を前記所定の期間毎に交互に選択し、選択された階調電圧を前記複数の映像信号線に印加することを特徴とする、液晶表示装置。

## 【請求項 4】

前記映像信号線駆動回路は、前記画像を表す画像信号に含まれる前記画素形成部に与えられるべき画素値を示すデジタル信号をアナログ電圧信号に変換し出力するD/A変換回路を含み、

前記D/A変換回路は、

前記基準電圧発生回路からの前記直流電圧を分圧することにより複数の正極性の階調電圧を生成する正極性抵抗分圧回路と、

10

20

30

40

50

前記基準電圧発生回路からの前記直流電圧を分圧することにより複数の負極性の階調電圧を生成する負極性抵抗分圧回路と、

前記複数の正極性の階調電圧および前記複数の負極性の階調電圧から、前記デジタル信号に対応する階調電圧を選択することにより、前記アナログ電圧信号を生成する選択回路と

を含むことを特徴とする、請求項3に記載の液晶表示装置。

【請求項5】

画像を表示するための表示部において複数の映像信号線と複数の走査信号線との交差部にそれぞれ対応してマトリクス状に配置された複数の画素形成部に設けられた画素電極と、前記画素電極との間に電圧を印加するために前記画素電極に対応して設けられた共通電極とを備え、前記共通電極に印加されるべき電圧を所定の2種類の電圧の間で所定の期間毎に交互に切り替える液晶表示装置における、前記画像を表す画像信号を受け取り前記画像信号に応じて前記複数の映像信号線に電圧を印加する映像信号線駆動方法であって、

前記複数の映像信号線に印加される電圧の基準となる所定の直流電圧に基づき前記共通電極の電位を基準とした正極性および負極性の電圧をともに含む複数の階調電圧を生成し、前記共通電極の電位を基準とした前記画素電極に印加される電圧の極性が前記所定の期間毎に逆になるよう、生成された前記複数の階調電圧から前記画像信号に対応する正極性または負極性の階調電圧を前記所定の期間毎に交互に選択し、選択された階調電圧を前記複数の映像信号線に印加することを特徴とする、映像信号線駆動方法。

【請求項6】

画像を表示するための表示部において複数の映像信号線と複数の走査信号線との交差部にそれぞれ対応してマトリクス状に配置された複数の画素形成部に設けられた画素電極と、前記画素電極との間に電圧を印加するために前記画素電極に対応して設けられた共通電極とを備える液晶表示装置において、前記画像を表す画像信号を受け取り前記画像信号に応じて前記複数の映像信号線に電圧を印加する映像信号線駆動ステップと、前記複数の走査信号線を選択的に駆動する走査信号線駆動ステップと、前記共通電極を駆動する共通電極駆動ステップと、前記映像信号線駆動ステップに対し前記複数の映像信号線に印加される電圧の基準となる所定の直流電圧を与える基準電圧発生ステップとを含む液晶表示装置の駆動方法であって、

前記共通電極駆動ステップでは、前記共通電極に印加されるべき電圧を所定の2種類の電圧の間で所定の期間毎に交互に切り替え、

前記映像信号線駆動ステップでは、前記基準電圧発生ステップにおいて与えられる前記直流電圧に基づき前記共通電極の電位を基準とした正極性および負極性の電圧をともに含む複数の階調電圧を生成し、前記共通電極の電位を基準とした前記画素電極に印加される電圧の極性が前記所定の期間毎に逆になるよう、生成された前記複数の階調電圧から前記画像信号に対応する正極性または負極性の階調電圧を前記所定の期間毎に交互に選択し、選択された階調電圧を前記複数の映像信号線に印加することを特徴とする、液晶表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アクティブマトリクス型の液晶表示装置に関するものであり、更に詳しくは、アクティブマトリクス型の共通電極が交流駆動される液晶表示装置における映像信号線駆動回路に関する。

【背景技術】

【0002】

一般に液晶表示装置では、液晶の劣化を抑えると共に表示品位を維持するために交流化駆動が行われている。この交流化駆動方式としては、1フレーム毎に液晶への印加電圧の極性を反転させる駆動方式（フレーム反転駆動方式）が知られている。しかし、この駆動方式によれば表示の際にフリッカ等の表示不具合が発生し易いため、近年では、1水平走

10

20

30

40

50

査線毎に印加電圧の正負極性を反転させつつ1フレーム毎にも正負極性を反転させる駆動方式（「ライン反転駆動方式」と呼ばれる）や、垂直・水平方向に隣り合う画素毎に印加電圧の正負極性を反転させつつ1フレーム毎にも正負極性を反転させる駆動方式（「ドット反転駆動方式」と呼ばれる）が採用されている。

#### 【0003】

このドット反転駆動方式では、フリッカに対するキラーパターンが比較的複雑である為、フリッカが発生しにくく高品位の表示が可能である。しかしこの方式では、液晶パネルの共通電極には直流電圧が印加されており、液晶パネルに印加すべき映像信号の方の極性を共通電極の電位を中心としてその上下の所定電圧に切り替えるため、液晶パネル駆動用ドライバから出力される映像信号の電圧値が大きくなり、ドライバに高い耐圧性能が要求される。そこで、ドライバに高い耐圧性能が要求されない（それ故低コストの）ライン反転駆動方式を採用した液晶表示装置が広く用いられている。

#### 【0004】

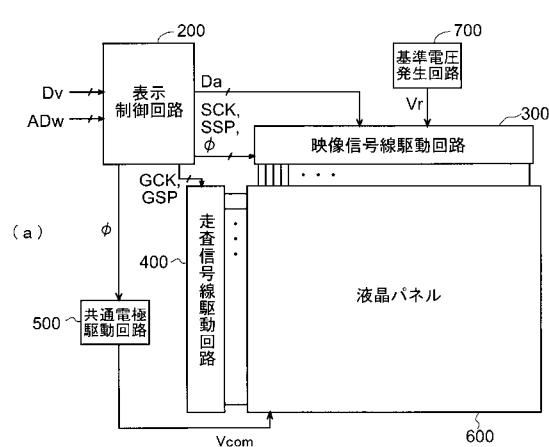

図1(a)は、このライン反転駆動方式を採用した従来の液晶表示装置の構成を示すブロック図である。この従来の液晶表示装置は、表示制御回路200と、映像信号線駆動回路300（「列電極駆動回路」または「データ線駆動回路」とも呼ばれる）と、走査信号線駆動回路（「行電極駆動回路」または「ゲート線駆動回路」とも呼ばれる）400と、共通電極駆動回路500と、アクティブマトリクス型の液晶パネル600と、映像信号線駆動回路300に後述する階調電圧の基準となる電圧を与える基準電圧発生回路700とを備えている。

#### 【0005】

ここで、共通電極駆動回路500は、表示制御回路200からの極性切換制御信号に応じて所定の2種類の電圧を交互に選択することにより共通電極の電位を変化させている。また、基準電圧発生回路700は、映像信号線駆動回路300において表示画面に所定の階調を表示する駆動用映像信号が生成されるときの基準となる複数の基準電圧 $V_r$ を生成し、生成された複数の基準電圧 $V_r$ を映像信号線駆動回路300に与える。この基準電圧 $V_r$ の電位は、液晶パネル600の交流化駆動のために表示制御回路200からの極性切換制御信号に応じて変化する。この電位変化の位相は各階調により異なっており、例えばノーマリホワイトの場合、黒表示に対応する階調電圧を決定する基準電圧は共通電極の電位変化と逆位相になるよう変化し、白表示に対応する階調電圧を決定する基準電圧は共通電極の電位変化と同位相になるよう変化する。

#### 【0006】

さらに映像信号線駆動回路300の具体的な構成について説明する。この映像信号線駆動回路300は、所定のクロックでスタートパルスを転送するシフトレジスタ部と、この転送されたスタートパルスをサンプリングパルスとして受け取ることによりデジタル画像信号 $D_a$ をラッチするデータラッチ部と、ラッチされたデジタル画像信号 $D_a$ に含まれるデジタルデータ信号の電圧をシフトさせるレベルシフタ部と、電圧をシフトされたデジタルデータ信号をアナログ電圧信号に変換するD/A変換部と、アナログ電圧信号を対応する映像信号線に印加するための出力バッファ部とを備えている。このうちD/A変換部についてさらに詳しく説明する。

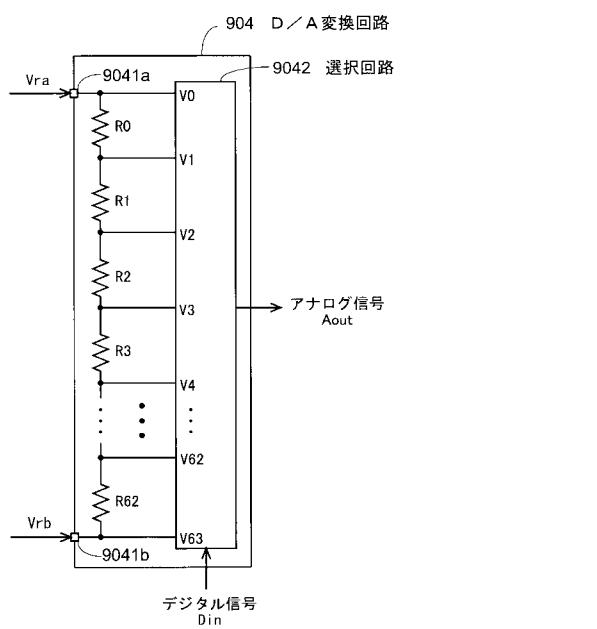

#### 【0007】

図7は、上記D/A変換部に含まれる或るD/A変換回路904の詳細な構成を説明するための図である。D/A変換部は1本の映像信号線あたり1つのD/A変換回路を含んでおり、D/A変換回路904は、D/A変換部に含まれる任意のD/A変換回路である。このD/A変換回路904は、レベルシフタ部からデジタル信号 $D_{in}$ を受け取り、これをアナログ信号 $A_{out}$ に変換する。具体的には、D/A変換回路904は、基準電圧発生回路700からの基準電圧 $V_r$ （ここでは2つの基準電圧 $V_{ra}$ ,  $V_{rb}$ ）に基づき生成される階調表示のためのアナログ電圧（以下「階調電圧」という） $V_0$ ~ $V_{63}$ から、受け取ったデジタル信号 $D_{in}$ に相当する階調電圧を選択し、アナログ信号 $A_{out}$ として出力する。

## 【0008】

このD/A変換回路904は、抵抗分圧回路を構成する63個の抵抗素子R0～R63と、この抵抗分圧回路の両端に加えられる電圧を受け取る第1および第2の端子9041a, 9041bと、選択回路9042とを備える。ここで、基準電圧Vraは、表示制御回路200からの極性切換制御信号に応じて、第1の端子9041aまたは第2の端子9041bに対し1水平走査期間毎に交互に与えられる。また、基準電圧Vrbは、基準電圧Vraより小さい電圧であって、基準電圧Vraが与えられる端子とは異なる第1または第2の端子9041a, 9041bに対し1水平走査期間毎に交互に与えられる。このように、第1および第2の端子9041a, 9041bには、基準電圧Vraまたは基準電圧Vrbが水平走査期間毎に交互に与えられる。

10

## 【0009】

抵抗素子R0～R63は、第1の端子9041aと第2の端子9041bとの間に印加される電圧を分圧する。すなわち、抵抗素子R0～R63は、第1の端子9041aから基準電圧Vraを受け取り、第2の端子9041bから基準電圧Vrbを受け取る所定の水平走査期間中は、上記分圧により、第2の端子9041bの電位を基準として正極性の階調電圧V0～V63を生成し、選択回路9042に与える。その後、抵抗素子R0～R63は、第1の端子9041aから基準電圧Vrbを受け取り、第2の端子9041bから基準電圧Vraを受け取る次の水平走査期間中には、上記分圧により、第2の端子9041bの電位を基準として負極性の階調電圧-V0～-V63を生成し、選択回路9042に与える。

20

## 【0010】

このように、階調電圧も極性切換制御信号に応じて変化するので、アナログ信号Aoutも変化する。また、共通電極の電位は、1水平走査期間毎に反転する。その結果、映像信号線駆動回路300へ出力される映像信号の電位差はドット反転駆動に比べて小さくして済むため、ドライバに高い耐圧性能が要求されることがない。

【特許文献1】特開平10-301538号公報

【特許文献2】特開2001-100711号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0011】

しかし、図7に示すD/A変換回路904の構成では、階調電圧の（第2の端子9041bの電位を基準とした）正負極性が反転される場合にも同一の抵抗分圧回路が使用されるため、正極性の階調電圧と負極性の階調電圧とをともに好適な値に設定することが難しく回路設計には困難が伴う。

30

## 【0012】

また、基準電圧発生回路700は、極性切換制御信号に応じた交流の基準電圧Vrを生成しなければならぬので、その回路構成が複雑となる。さらに、交流の基準電圧Vrを、表示すべき輝度に合わせて適宜に調整（いわゆるガンマ調整）を行う場合、基準電圧発生回路700の回路構成はより複雑となる。

40

## 【0013】

そこで本発明では、正極性の階調電圧と負極性の階調電圧とをともに好適値に調整することが容易にでき、基準電圧発生回路の回路構成を簡易にできる映像信号線駆動回路およびそれを備える液晶表示装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0014】

第1の発明は、画像を表示するための表示部において複数の映像信号線と複数の走査信号線との交差部にそれぞれ対応してマトリクス状に配置された複数の画素形成部に設けられた画素電極と、前記画素電極との間に電圧を印加するために前記画素電極に対応して設けられた共通電極とを備え、前記共通電極に印加されるべき電圧を所定の2種類の電圧の間で所定の期間毎に交互に切り替える液晶表示装置における、前記画像を表す画像信号を

50

受け取り前記画像信号に応じて前記複数の映像信号線に電圧を印加する映像信号線駆動回路であって、

前記複数の映像信号線に印加される電圧の基準となる所定の直流電圧に基づき前記共通電極の電位を基準とした正極性および負極性の電圧をともに含む複数の階調電圧を生成し、前記共通電極の電位を基準とした前記画素電極に印加される電圧の極性が前記所定の期間毎に逆になるよう、生成された前記複数の階調電圧から前記画像信号に対応する正極性または負極性の階調電圧を前記所定の期間毎に交互に選択し、選択された階調電圧を前記複数の映像信号線に印加することを特徴とする。

【0015】

第2の発明は、第1の発明において、

10

前記画像を表す画像信号に含まれる前記画素形成部に与えられるべき画素値を示すデジタル信号をアナログ電圧信号に変換し出力するD/A変換回路を含み、

前記D/A変換回路は、

前記直流電圧を分圧することにより複数の正極性の階調電圧を生成する正極性抵抗分圧回路と、

前記直流電圧を分圧することにより複数の負極性の階調電圧を生成する負極性抵抗分圧回路と、

前記複数の正極性の階調電圧および前記複数の負極性の階調電圧から、前記デジタル信号に対応する階調電圧を選択することにより、前記アナログ電圧信号を生成する選択回路と

20

を含むことを特徴とする。

【0016】

第3の発明は、画像を表示するための表示部において複数の映像信号線と複数の走査信号線との交差部にそれぞれ対応してマトリクス状に配置された複数の画素形成部に設けられた画素電極と、前記画素電極との間に電圧を印加するために前記画素電極に対応して設けられた共通電極と、前記画像を表す画像信号を受け取り前記画像信号に応じて前記複数の映像信号線に電圧を印加する映像信号線駆動回路と、前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、前記共通電極を駆動する共通電極駆動回路と、前記映像信号線駆動回路に対し前記複数の映像信号線に印加される電圧の基準となる所定の直流電圧を与える基準電圧発生回路とを備え、

30

前記共通電極駆動回路は、前記共通電極に印加されるべき電圧を所定の2種類の電圧の間で所定の期間毎に交互に切り替え、

前記映像信号線駆動回路は、前記基準電圧発生回路からの前記直流電圧に基づき前記共通電極の電位を基準とした正極性および負極性の電圧をともに含む複数の階調電圧を生成し、前記共通電極の電位を基準とした前記画素電極に印加される電圧の極性が前記所定の期間毎に逆になるよう、生成された前記複数の階調電圧から前記画像信号に対応する正極性または負極性の階調電圧を前記所定の期間毎に交互に選択し、選択された階調電圧を前記複数の映像信号線に印加することを特徴とする。

【0017】

第4の発明は、第4の発明において、

40

前記映像信号線駆動回路は、前記画像を表す画像信号に含まれる前記画素形成部に与えられるべき画素値を示すデジタル信号をアナログ電圧信号に変換し出力するD/A変換回路を含み、

前記D/A変換回路は、

前記基準電圧発生回路からの前記直流電圧を分圧することにより複数の正極性の階調電圧を生成する正極性抵抗分圧回路と、

前記基準電圧発生回路からの前記直流電圧を分圧することにより複数の負極性の階調電圧を生成する負極性抵抗分圧回路と、

前記複数の正極性の階調電圧および前記複数の負極性の階調電圧から、前記デジタル信号に対応する階調電圧を選択することにより、前記アナログ電圧信号を生成する選択回

50

路と

を含むことを特徴とする。

【0018】

第5の発明は、画像を表示するための表示部において複数の映像信号線と複数の走査信号線との交差部にそれぞれ対応してマトリクス状に配置された複数の画素形成部に設けられた画素電極と、前記画素電極との間に電圧を印加するために前記画素電極に対応して設けられた共通電極とを備え、前記共通電極に印加されるべき電圧を所定の2種類の電圧の間で所定の期間毎に交互に切り替える液晶表示装置における、前記画像を表す画像信号を受け取り前記画像信号に応じて前記複数の映像信号線に電圧を印加する映像信号線駆動方法であって、

前記複数の映像信号線に印加される電圧の基準となる所定の直流電圧に基づき前記共通電極の電位を基準とした正極性および負極性の電圧をともに含む複数の階調電圧を生成し、前記共通電極の電位を基準とした前記画素電極に印加される電圧の極性が前記所定の期間毎に逆になるよう、生成された前記複数の階調電圧から前記画像信号に対応する正極性または負極性の階調電圧を前記所定の期間毎に交互に選択し、選択された階調電圧を前記複数の映像信号線に印加することを特徴とする。

【0019】

第6の発明は、画像を表示するための表示部において複数の映像信号線と複数の走査信号線との交差部にそれぞれ対応してマトリクス状に配置された複数の画素形成部に設けられた画素電極と、前記画素電極との間に電圧を印加するために前記画素電極に対応して設けられた共通電極とを備える液晶表示装置において、前記画像を表す画像信号を受け取り前記画像信号に応じて前記複数の映像信号線に電圧を印加する映像信号線駆動ステップと、前記複数の走査信号線を選択的に駆動する走査信号線駆動ステップと、前記共通電極を駆動する共通電極駆動ステップと、前記映像信号線駆動ステップに対し前記複数の映像信号線に印加される電圧の基準となる所定の直流電圧を与える基準電圧発生ステップとを含む液晶表示装置の駆動方法であって、

前記共通電極駆動ステップでは、前記共通電極に印加されるべき電圧を所定の2種類の電圧の間で所定の期間毎に交互に切り替え、

前記映像信号線駆動ステップでは、前記基準電圧発生ステップにおいて与えられる前記直流電圧に基づき前記共通電極の電位を基準とした正極性および負極性の電圧をともに含む複数の階調電圧を生成し、前記共通電極の電位を基準とした前記画素電極に印加される電圧の極性が前記所定の期間毎に逆になるよう、生成された前記複数の階調電圧から前記画像信号に対応する正極性または負極性の階調電圧を前記所定の期間毎に交互に選択し、選択された階調電圧を前記複数の映像信号線に印加することを特徴とする。

【発明の効果】

【0020】

第1の発明によれば、共通電極の電位を基準とした画素電極に印加される電圧の極性が所定の期間毎に逆になるよう選択された階調電圧を映像信号線に印加するのでドライバに高い耐圧性能が要求されることなく、かつ例えば外部の基準電圧発生回路から供給される基準電圧が直流でよいので、基準電圧発生回路の回路構成を簡易にでき電圧値を適宜に調整（例えばガンマ調整）することが容易な映像信号線駆動回路を提供することができる。

【0021】

第2の発明によれば、ドライバに高い耐圧性能が要求されることなく、かつ基準電圧発生回路の回路構成を簡易にでき電圧値の適宜の調整を容易にできるとともに、正極性用抵抗分圧回路および負極性用抵抗分圧回路に含まれる各抵抗素子の抵抗値を適宜の値に設定し基準電圧を適宜に設定することにより、正極性の階調電圧と負極性の階調電圧とを好適値に設定（設計）することが容易な映像信号線駆動回路を提供することができる。

【0022】

第3の発明によれば、第1の発明と同様に、ドライバに高い耐圧性能が要求されること

10

20

30

40

50

がなく、かつ基準電圧発生回路の回路構成を簡易にでき電圧値の適宜の調整が容易な液晶表示装置を提供することができる。

【0023】

第4の発明によれば、第2の発明と同様に、ドライバに高い耐圧性能が要求されることなく、かつ基準電圧発生回路の回路構成を簡易にでき電圧値の適宜の調整を容易にできるとともに、正極性用抵抗分圧回路および負極性用抵抗分圧回路に含まれる各抵抗素子の抵抗値を適宜の値に設定し基準電圧を適宜に設定することにより、正極性の階調電圧と負極性の階調電圧とを好適値に設定することが容易な液晶表示装置を提供することができる。

【0024】

第5の発明によれば、第1の発明と同様の効果を奏する。

10

【0025】

第6の発明によれば、第3の発明と同様の効果を奏する。

【発明を実施するための最良の形態】

【0026】

以下、本発明の一実施形態について添付図面を参照して説明する。

<1. 全体の構成および動作>

図1(a)は、ライン反転駆動方式を採用した従来の液晶表示装置とほぼ同様の構成を有する、本発明の一実施形態に係る液晶表示装置の構成を示すブロック図である。この液晶表示装置は、表示制御回路200と、映像信号線駆動回路300と、走査信号線駆動回路400と、共通電極駆動回路500と、アクティブマトリクス型の液晶パネル600と、映像信号線駆動回路300に所定の基準となる電圧を与える基準電圧発生回路700とを備えている。なお、この液晶表示装置は、映像信号線駆動回路300に含まれるD/A変換回路の構成が従来の構成とは異なる。この点につき詳しくは後述する。

20

【0027】

この液晶表示装置における表示部としての液晶パネル600は、外部の所定の映像ソース(CPUなど)から受け取る画像データDvの表す画像における水平走査線にそれぞれが対応する複数本の走査信号線(行電極)と、それら複数本の走査信号線のそれぞれと交差する複数本の映像信号線(列電極)と、それら複数本の走査信号線と複数本の映像信号線との交差点にそれぞれ対応して設けられた複数の画素形成部とを含む。各画素形成部の構成は、基本的には従来のアクティブマトリクス型液晶パネルにおける構成と同様である(詳細は後述)。また、この液晶パネル600は、各画素形成部に含まれる画素電極に共通的に設けられかつ液晶層を挟んで各画素電極と対向するように配置された共通電極を備えている。

30

【0028】

本実施形態では、液晶パネル600に表示すべき画像を表す画像データDvと、表示動作のタイミング信号であるアドレス信号ADw(以下「表示制御信号ADw」という)とが、外部の映像ソースから表示制御回路200に送られる。

【0029】

表示制御回路200は、表示制御信号ADwと画像データDvに基づき、液晶パネル用の表示のため映像信号線駆動回路300に与えられるソース用クロック信号SCKおよびソース用スタートパルス信号SSPと、表示のため走査信号線駆動回路400に与えられるゲート用クロック信号GCKおよびゲート用スタートパルス信号GSPとを含む各種信号を生成する。これらの信号は公知であるため詳しい説明は省略する。また、表示制御回路200は、外部の映像ソースから受け取った画像データを表示メモリに書き込んだ後に読み出して、ソースドライバ用デジタル画像信号Daとして出力する。さらに、表示制御回路200は、上記クロック信号等に基づき、液晶パネル600の交流化駆動のための極性切換制御信号を生成する。このようにして、表示制御回路200によって生成される信号のうち、デジタル画像信号Daは映像信号線駆動回路300に、極性切換制御信号は、映像信号線駆動回路300および共通電極駆動回路500に、それぞれ供給される。

40

【0030】

50

映像信号線駆動回路 300 には、上記のように、液晶パネル 600 に表示すべき画像を表すデータが画素単位でデジタル画像信号 D<sub>a</sub> として供給されると共に、タイミングを示す信号としてソース用クロック信号 SCK、ソース用スタートパルス信号 SSP、および極性切換制御信号 などが供給される。映像信号線駆動回路 300 は、これらのデジタル画像信号 D<sub>a</sub>、ソース用クロック信号 SCK、ソース用スタートパルス信号 SSP、および極性切換制御信号 などに基づき、液晶パネル 600 を駆動するためのアナログ電圧（以下「駆動用映像信号」ともいう）D(1), D(2), D(3), … を生成し、これを液晶パネル 600 の各映像信号線に印加する。この駆動用映像信号 D(1), D(2), D(3), … は、液晶パネル 600 の交流化駆動のために、極性切換制御信号 に応じてその極性が反転する。

10

## 【0031】

走査信号線駆動回路 400 は、ゲート用クロック信号 GCK およびゲート用スタートパルス信号 GSP に基づき、液晶パネル 600 における走査信号線を 1 水平走査期間ずつ後述の所定順に選択するために各走査信号線に印加すべき走査信号 G(1), G(2), G(3), … を生成し、全走査信号線のそれぞれを順に選択するためのアクティブな走査信号の各走査信号線への印加を 1 垂直走査期間を周期として繰り返す。

## 【0032】

共通電極駆動回路 500 は、液晶パネル 600 の共通電極に与えるべき電圧である共通電圧 V<sub>com</sub> を生成する。本実施形態では、映像信号線の電圧の振幅を抑えるために、交流化駆動に応じて共通電極の電位をも変化させている。すなわち、共通電極駆動回路 500 は、表示制御回路 200 からの極性切換制御信号 に応じて、1 水平走査期間において 2 種類の基準電圧（例えば 0V および 5V）の間で切り換わる電圧であって 1 垂直走査期間（1 フレーム）毎にも切り替わる電圧を生成し、これを共通電圧 V<sub>com</sub> として液晶パネル 600 の共通電極に供給する。

20

## 【0033】

液晶パネル 600 では、上記のようにして映像信号線に、映像信号線駆動回路 300 によってデジタル画像信号 D<sub>a</sub> に基づく駆動用の映像信号 D(1), D(2), D(3), … が印加され、走査信号線には、走査信号線駆動回路 400 によって走査信号 G(1), G(2), G(3), … が印加され、共通電極には、共通電極駆動回路 500 によって共通電圧 V<sub>com</sub> が印加される。これにより液晶パネル 600 は、外部の映像ソースから受け取った画像データ D<sub>v</sub> の表す画像を表示する。

30

## 【0034】

基準電圧発生回路 700 は、映像信号線駆動回路 300 において表示画面に所定の階調を表示する駆動用映像信号が生成されるときの基準となる複数の基準電圧 V<sub>r</sub> を生成し、生成された複数の基準電圧 V<sub>r</sub> を映像信号線駆動回路 300 に与える。映像信号線駆動回路 300 はこれらの基準電圧 V<sub>r</sub> に基づき駆動用映像信号を生成するが、この動作については後述する。

## 【0035】

## &lt;2. 表示制御回路&gt;

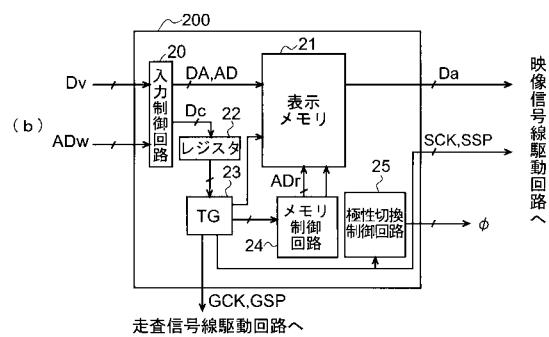

図 1 (b) は、上記の液晶表示装置における表示制御回路 200 の構成を示すブロック図である。この表示制御回路 200 は、入力制御回路 20 と表示メモリ 21 とレジスタ 22 とタイミング発生回路 23 とメモリ制御回路 24 と極性切換制御回路 25 とを備えている。

40

## 【0036】

この表示制御回路 200 が外部の映像ソースから受け取る画像データ D<sub>v</sub> および表示制御信号 ADW は、入力制御回路 20 により、画像データ DA と表示制御データ DC とに振り分けられ、画像データ DA は表示メモリ 21 に書き込まれ、表示制御データ DC はレジスタ 22 に書き込まれる。

## 【0037】

タイミング発生回路（以下「TG」と略記する）23 は、レジスタ 22 に保持される上

50

記表示制御データに基づき、ソース用クロック信号 SCK、ソース用スタートパルス信号 SSP、ゲート用クロック信号 GCK、ゲート用スタートパルス信号 GSP、およびその他のタイミング信号を生成する。

【0038】

メモリ制御回路 24 は、表示メモリ 21 の動作を制御する。この制御に応じて、液晶パネル 600 に表示すべき画像を表すデジタル画像信号 Da が表示メモリ 21 から読み出され、表示制御回路 200 から出力される。このデジタル画像信号 Da は、既述のように映像信号線駆動回路 300 に供給される。

【0039】

極性切換制御回路 25 は、TG23 によって生成されたゲート用クロック信号 GCK およびゲート用スタートパルス信号 GSP に基づき、上記の極性切換制御信号 を生成する。この極性切換制御信号 は、液晶パネル 600 の交流化駆動のための極性反転のタイミングを決定する制御信号であって、既述のように映像信号線駆動回路 300 および共通電極駆動回路 500 に供給される。

【0040】

<3. 液晶パネル>

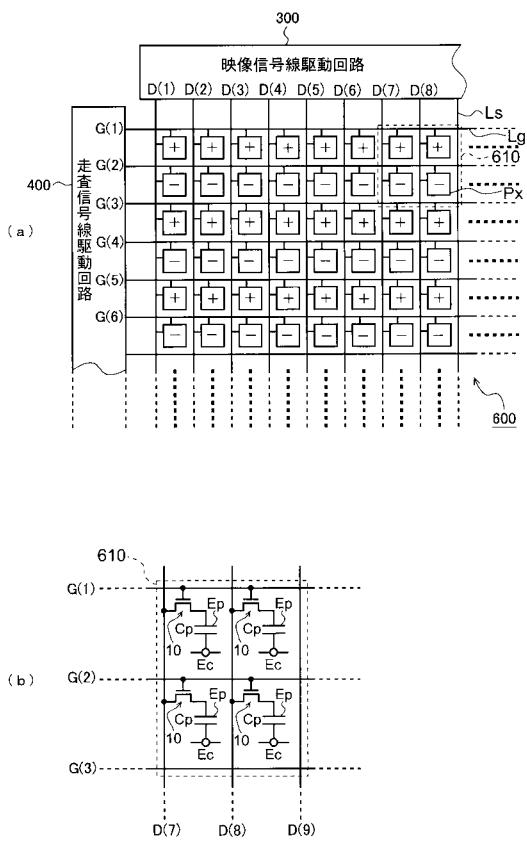

図 2 (a) は、本実施形態における液晶パネル 600 の構成を示す模式図であり、図 2 (b) は、この液晶パネルの一部 (4 つの画素に相当する部分) 610 の等価回路図である。

【0041】

この液晶パネル 600 は、映像信号線駆動回路 300 に接続される複数の映像信号線 Ls と、走査信号線駆動回路 400 に接続される複数の走査信号線 Lg とを備え、当該複数の映像信号線 Ls と当該複数の走査信号線 Lg とは、各映像信号線 Ls と各走査信号線 Lg とが交差するように格子状に配設されている。そして、当該複数の映像信号線 Ls と当該複数の走査信号線 Lg との交差点に対応して複数の画素形成部 Px がそれぞれ設けられている。各画素形成部 Px は、図 2 (b) に示すように、対応する交差点を通過する映像信号線 Ls にソース端子が接続されるとともに、対応する交差点を通過する走査信号線 Lg にゲート端子が接続された TFT (Thin Film Transistor) 10 と、その TFT 10 のドレイン端子に接続された画素電極 Ep と、上記複数の画素形成部 Px に共通的に設けられた共通電極 (「対向電極」ともいう) Ec と、上記複数の画素形成部 Px に共通的に設けられ画素電極 Ep と共通電極 Ec との間に挟持された液晶層とからなる。そして、画素電極 Ep と共通電極 Ec とそれらの間に挟持された液晶層とにより画素容量 Cp が形成される。なお、上記構成からわかるように、いずれかの走査信号線 Lg に印加される走査信号 G (k) がアクティブになると、その走査信号線が選択され、その走査信号線に接続される (各画素形成部 Px の) TFT 10 が導通状態となり、その TFT 10 に接続される画素電極 Ep には、駆動用映像信号 D (j) が映像信号線 Ls を介して印加される。これにより、その印加された駆動用映像信号 D (j) の電圧 (共通電極 Ec の電位を基準とする電圧) が、その画素電極 Ep を含む画素形成部 Px に画素値として書き込まれる。

【0042】

上記のような画素形成部 Px は、マトリクス状に配置されて画素形成マトリクスを構成し、これに伴い、画素形成部 Px に含まれる画素電極 Ep も、マトリクス状に配置されて画素電極マトリクスを構成する。ところで、画素形成部 Px の主要部である画素電極 Ep は、液晶パネルに表示される画像の画素と 1 対 1 に対応し同一視できる。そこで、以下では、説明の便宜上、画素形成部 Px または画素電極 Ep と画素とを同一視するものとし、「画素形成マトリクス」または「画素電極マトリクス」を単に「画素マトリクス」ともいう。

【0043】

図 2 (a) において、各画素形成部 Px に付されている “+” は、或るフレームにおいて当該画素形成部 Px を構成する画素液晶に (すなわち共通電極 Ec を基準として画素電

10

20

30

40

50

極 E p に ) 正極性の電圧が印加されることを意味し、 “ - ” は、当該フレームにおいて当該画素形成部 P x を構成する画素液晶に ( すなわち共通電極 E c を基準として画素電極 E p に ) 負極性の電圧が印加されることを意味し、これら各画素形成部 P x に付された “ + ” と “ - ” により、画素マトリクスにおける極性パターンが示される。図 2 ( a ) に示すように本実施形態では、画素液晶への印加電圧の正負極性を画素マトリクスにおける各行毎に反転させ且つ 1 フレーム毎にも反転させる駆動方式であるライン反転駆動方式が採用されている。

【 0 0 4 4 】

< 4 . 映像信号線駆動回路 >

< 4 . 1 映像信号線駆動回路の構成 >

10

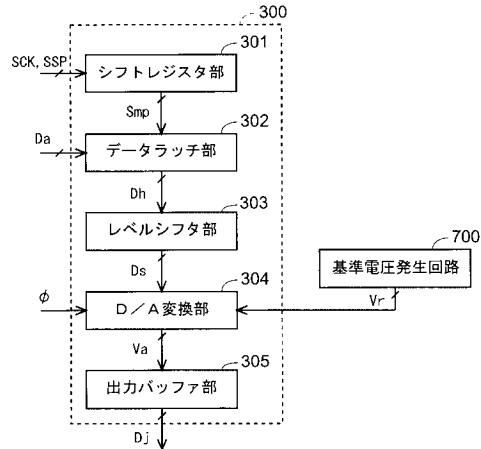

図 3 は、上記映像信号線駆動回路 3 0 0 の構成を示すブロック図である。以下、図 3 を参照し各構成要素について説明する。この映像信号線駆動回路 3 0 0 は、図 1 に示す表示制御回路 2 0 0 から出力されるソース用クロック信号 S C K およびソース用スタートパルス信号 S S P を受け取ることにより所定のサンプリングパルス S m p を出力するシフトレジスタ部 3 0 1 と、表示制御回路 2 0 0 から出力されるデジタル画像信号 D a と上記サンプリングパルス S m p を受け取ることによりデジタル画像信号 D a に含まれる画素値を示すデータをラッチするデータラッチ部 3 0 2 と、このデータラッチ部 3 0 2 によりラッチされたデータの信号電圧をシフトさせるレベルシフタ部 3 0 3 と、このレベルシフタ部 3 0 3 により電圧をシフトされたデジタルデータ信号をアナログ電圧信号に変換する D / A 変換部 3 0 4 と、この D / A 変換部 3 0 4 からのアナログ電圧信号を対応する映像信号線 L s に印加するための出力バッファ部 3 0 5 とを備える。なお、これらの構成要素は、D / A 変換部 3 0 4 を除き、従来の映像信号線駆動回路の構成要素とほぼ同様である。以下、これら各構成要素の動作について図 3 を参照して説明する。

20

【 0 0 4 5 】

< 4 . 2 映像信号線駆動回路の動作 >

シフトレジスタ部 3 0 1 は、複数個のフリップフロップ回路を直列に接続した構成であり、上記ソース用クロック信号 S C K に同期して上記ソース用スタートパルス信号 S S P を各段において順次転送することにより、各段から所定のサンプリングパルス S m p を順次出力する。

30

【 0 0 4 6 】

データラッチ部 3 0 2 は、上記シフトレジスタ部 3 0 1 の各段に対応して 1 つずつ設けられた複数のラッチ回路を備えており、上記サンプリングパルス S m p によりデジタル画像信号 D a に含まれるデータをサンプリングし、その後サンプリングされたデータを所定の期間出力し続ける。具体的には、画素マトリクスにおける或る行 ( 例えは 1 行目 ) の画素形成部 P x に与えられるデジタルデータは、データラッチ部 3 0 2 に含まれるサンプリングメモリ回路 ( 不図示 ) に一旦記憶され、記憶されたデータはデータラッチ部 3 0 2 に含まれるホールドメモリ回路 ( 不図示 ) に与えられる。このホールドメモリ回路は、所定のラッチ信号の立ち上がりで対応するサンプリングメモリ回路の各段からの出力信号を取り込み、その出力信号を出力信号 D h としてレベルシフタ部 3 0 3 に与える。

【 0 0 4 7 】

レベルシフタ部 3 0 3 は、上記シフトレジスタ部 3 0 1 の各段に対応して 1 つずつ設けられた複数のレベルシフタ回路を備えており、上記データラッチ部 3 0 2 からの出力信号 D h を受け取り、D / A 変換部 3 0 4 において適正な入力信号レベルになるよう当該信号の電圧レベルをシフトさせ ( 一般的には上昇させ ) 、レベルシフタ信号 D s として出力する。

40

【 0 0 4 8 】

D / A 変換部 3 0 4 は、上記シフトレジスタ部 3 0 1 の各段に対応して 1 つずつ設けられた複数の D / A 変換回路を備えており、レベルシフタ部 3 0 3 から出力されるデジタル信号であるレベルシフタ信号 D s を受け取り、これを上記デジタルデータに対応するアナログ電圧信号 V a に変換する。具体的には、D / A 変換部 3 0 4 は、基準電圧発生回路 7

50

00からの複数の基準電圧  $V_r$  に基づき生成される階調表示のための複数種類のアナログ電圧（以下「階調電圧」という）から、受け取ったデジタル信号に相当する階調電圧を選択しアナログ電圧信号  $V_a$  として出力する。なお、D/A変換部304に対して、基準電圧発生回路700から複数の基準電圧  $V_r$  が与えられるのは、D/A変換部304において生成される階調電圧をより正確に設定するためであり、このように複数の基準電圧が与えられる構成については周知である（例えば特許文献1および特許文献2を参照）。D/A変換部304の詳しい構成については後述する。

#### 【0049】

出力バッファ部305は、上記シフトレジスタ部301の各段に対応して1つずつ設けられた複数の出力バッファ回路を備えており、この出力バッファ回路は、例えばボルテージフォロワ回路で構成されている。出力バッファ部305は、上記アナログ電圧信号  $V_a$  を映像信号  $D_j$  として映像信号線  $L_s$  に出力する。次に、D/A変換部304の詳しい構成について図を参照して説明する。

#### 【0050】

##### <4.3 D/A変換部の構成および動作>

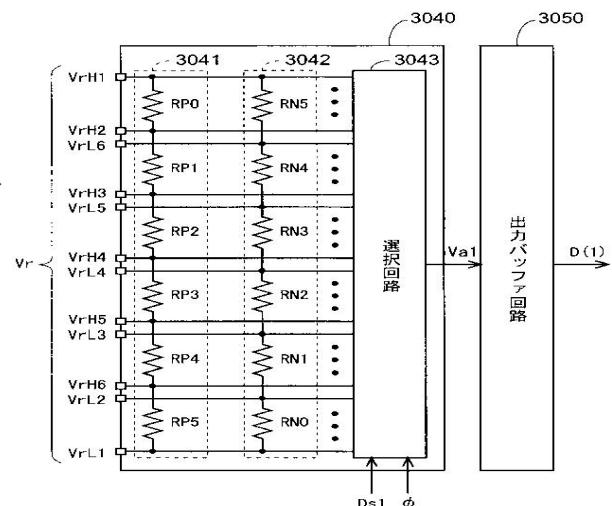

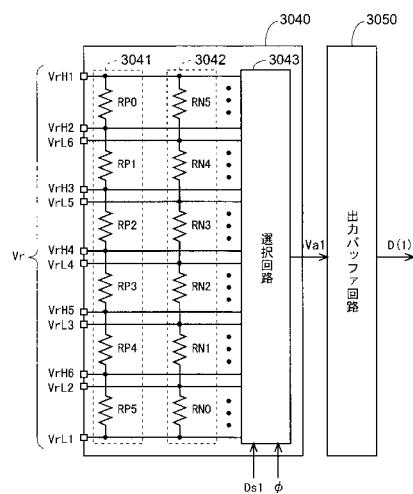

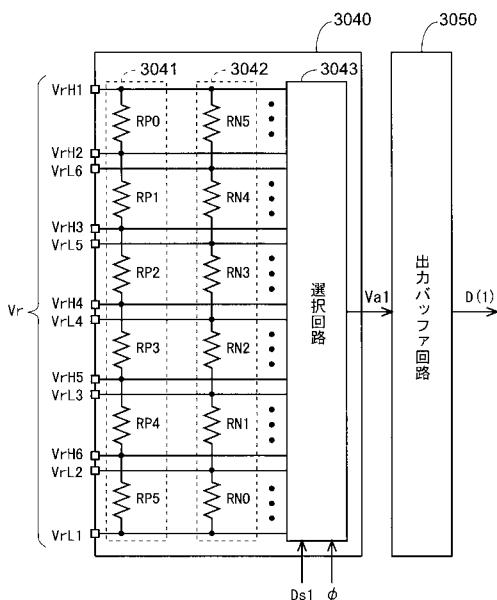

図4は、D/A変換部304に含まれる或るD/A変換回路3040の詳細な構成を説明するための図である。このD/A変換回路3040は、シフトレジスタ部301の第1段に対応して設けられたD/A変換回路である。なお、全てのD/A変換回路は同様の構成であるため、便宜上、上記構成例で説明しその他の回路の説明は省略する。このD/A変換回路3040は、レベルシフタ部303から出力されるレベルシフタ信号  $D_s$  のうち対応するレベルシフタ信号  $D_s1$  を受け取り、これをアナログ電圧信号  $V_a1$  に変換する。具体的には、D/A変換回路3040は、基準電圧発生回路700からの複数の基準電圧  $V_r$  に基づき生成される階調表示のためのアナログ電圧信号から、受け取ったデジタル信号（上記レベルシフタ信号  $D_s1$ ）に相当するアナログ電圧信号を極性切換制御信号に応じて選択し、アナログ電圧信号  $V_a1$  として出力する。このアナログ電圧信号  $V_a1$  は、出力バッファ部305のうちの対応する出力バッファ回路3050に入力され、映像信号  $D(1)$  として出力される。

#### 【0051】

このD/A変換回路3040は、正極性用抵抗分圧回路3041と、負極性用抵抗分圧回路3042と、選択回路3043とを備える。正極性用抵抗分圧回路3041は、それぞれ直列に接続された複数の抵抗素子からなる第1から第6までの正極性用抵抗群  $R_{P0} \sim R_{P5}$  を含んでおり、基準電圧発生回路700からの複数の基準電圧  $V_r$  をさらに細かく分圧して選択回路3043に与える。具体的には、例えば、複数の基準電圧  $V_r$  のうちの第1の正極性用基準電圧  $V_{rH1}$  と第2の正極性用基準電圧  $V_{rH2}$  との間の電圧は、第1の正極性用抵抗群  $R_{P0}$  によりさらに細かく分圧されて選択回路3043に与えられる。また、負極性用抵抗分圧回路3042も正極性用抵抗分圧回路3041と同様にそれぞれ直列に接続された複数の抵抗素子からなる第1から第6までの負極性抵抗群  $R_{N0} \sim R_{N5}$  を含んでおり、基準電圧発生回路700からの複数の基準電圧  $V_r$  をさらに細かく分圧して選択回路3043に与える。

#### 【0052】

なお、ここでの正極性用基準電圧とは、図2(b)に示す共通電極  $E_c$  を基準として画素電極  $E_p$  に正極性の電圧が印加される場合の基準となる電圧を意味し、負極性用基準電圧とは、共通電極  $E_c$  を基準として画素電極  $E_p$  に負極性の電圧が印加される場合の基準となる電圧を意味する。

#### 【0053】

このように、前述した図7に示す従来のD/A変換回路とは異なり、このD/A変換回路3040は、正極性用および負極性用の基準電圧をそれぞれ受け取り分圧する構成である。よって、正極性用抵抗分圧回路3041および負極性用抵抗分圧回路3042に含まれる各抵抗素子の抵抗値を適宜の値に設定（設計）することにより、個別に設定された正極性用の基準電圧と負極性用の基準電圧とをそれぞれ好適な電圧値に分圧することができ

10

20

30

40

50

る。

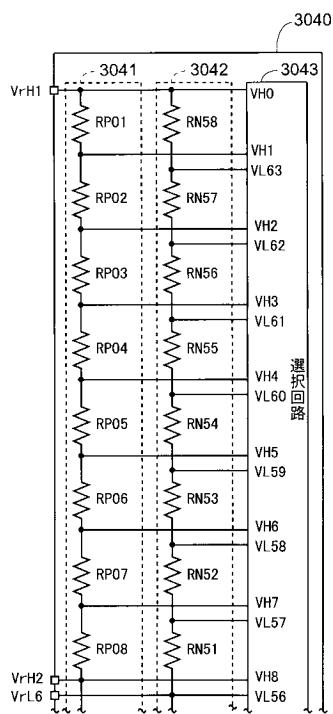

【0054】

図5は、D/A変換回路3040の一部分における詳細な構成を示す図である。この図5では、第1の正極性用抵抗群RP0および第6の負極性用抵抗群RP5により構成される抵抗分圧回路が示されている。この第1の正極性用抵抗群RP0は、8つの抵抗素子RP01～RP08からなり、第1の正極性用基準電圧VrH1と第2の正極性用基準電圧VrH2との間の電圧を分圧することにより、正極性の階調電圧VH0～VH8を生成し、選択回路3043に与える。また、第6の負極性用抵抗群RN5は、8つの抵抗素子RN51～RN58からなり、第1の正極性用基準電圧VrH1と第6の負極性用基準電圧VrL6との間の電圧を分圧することにより、負極性の階調電圧VL56～VL63を生成し、選択回路3043に与える。このように、正極性用抵抗分圧回路3041および負極性用抵抗分圧回路3042により、正極性の階調電圧VH0～VH63および負極性の階調電圧VL0～VL63を生成することができる。これらの階調電圧についてさらに説明する。

10

【0055】

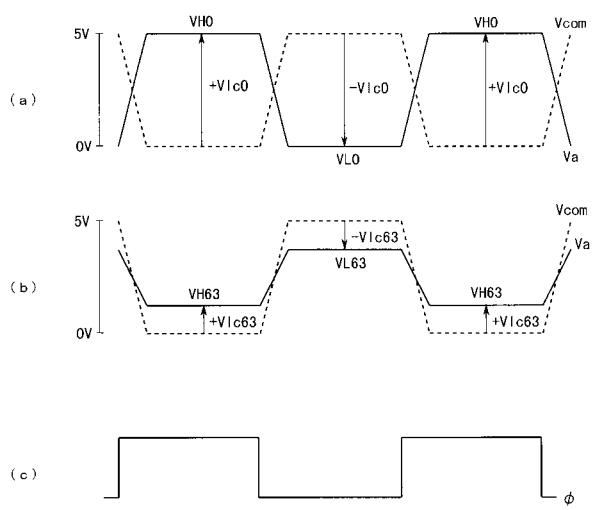

図6は、共通電圧信号Vcomおよびアナログ電圧信号Vaの電位変化を示す波形図である。より詳しくは、図6(a)は、画素形成部Pxにおいて最も暗い表示(黒表示)が行われる場合のアナログ電圧信号Vaの電位変化を示す波形図であり、図6(b)は、画素形成部Pxにおいて最も明るい表示(白表示)が行われる場合のアナログ電圧信号Vaの電位変化を示す波形図であり、図6(c)は、極性切換信号の波形図である。なお、本液晶表示装置は、液晶層に印加される電圧が大きいほど暗い表示となる、いわゆるノーマリー・ホワイト型の表示装置である。

20

【0056】

ここで、共通電圧信号Vcomは、液晶パネル600の共通電極に与えられる電圧信号であり、図6(c)に示す極性切換信号に応じて1水平走査期間毎かつ1垂直走査期間毎に電圧値が切り替わる。また、アナログ電圧信号Vaは、画素形成部Pxに与えられるデジタルデータに相当する電圧信号であり、共通電圧Vcomを基準とした電圧極性が1水平走査期間毎に逆になるよう、極性切換信号に応じて1水平走査期間毎かつ1垂直走査期間毎に電圧値が切り替わる。このような液晶モジュールの交流化駆動方式がライン反転駆動方式と呼ばれることについては前述した。

30

【0057】

図6(a)を参照すると、アナログ電圧信号Vaは、図6(c)に示す極性切換信号の立ち上がりまたは立ち下がりに応じて1水平走査期間毎に階調電圧VH0と階調電圧VL0とに交互に切り替わるため、共通電圧信号Vcomとの電位差(すなわち図2(a)における共通電極Ecを基準として画素電極Epに印加される電圧)は、アナログ電圧信号Vaの電圧が階調電圧VH0であるとき+V1c0[V]となり、階調電圧VL0であるとき-V1c0[V]となる。よって、液晶層に印加される電圧の絶対値は常に|V1c0|[V]となるので、画素形成部Pxにおいて最も暗い表示(黒表示)が継続して行われる。同様に、図6(b)を参照すると、アナログ電圧信号Vaは、図6(c)に示す極性切換信号の立ち上がりまたは立ち下がりに応じて1水平走査期間毎に階調電圧VH63と階調電圧VL63とに交互に切り替わるため、共通電圧信号Vcomとの電位差は、アナログ電圧信号Vaの電圧が階調電圧VH63であるとき+V1c63[V]となり、階調電圧VL63であるとき-V1c63[V]となる。よって、液晶層に印加される電圧の絶対値は常に|V1c63|[V]となるので、画素形成部Pxにおいて最も明るい表示(白表示)が継続して行われる。

40

【0058】

以上のように、アナログ電圧信号Vaは、極性切換信号に応じて正極性および負極性の階調電圧が交互に切り替えられることにより生成される。具体的には、図4に示すD/A変換回路3040の選択回路3043は、各階調電圧に対応するアナログスイッチを含んでおり、表示制御回路200からの極性切換制御信号に応じて、受け取ったデジタル

50

信号（レベルシフタ信号 D<sub>s</sub>1）に対応する正極性の階調電圧と負極性の階調電圧とが交互に選択されるよう対応するアナログスイッチを制御することにより、アナログ電圧信号 V<sub>a</sub>1 を生成し出力する。

【0059】

このように、基準電圧発生回路 700 からの複数の基準電圧は、共通電極を交流駆動する従来の液晶表示装置における基準電圧発生回路からの基準電圧とは異なり、直流電圧（変化しない電圧）である。よって、基準電圧発生回路 700 は、簡易な構成で済む。例えば定電圧回路から出力される所定の電圧を抵抗分圧回路等により複数の基準電圧を生成するような簡易な構成で済む。また、前述したガンマ調整を行う場合、基準電圧発生回路 700 は、例えば定電圧回路から出力される所定の電圧を、可変抵抗を含む抵抗分圧回路およびバッファ回路等により適宜の電圧になるよう調整する構成など、低コストで簡易な構成で済む。

【0060】

<5. 効果>

本実施形態における映像信号線駆動回路 300 およびそれを備える液晶表示装置では、共通電極の電位は 1 水平走査期間毎に変化するのでドライバに高い耐圧性能が要求されることなく、かつ正極性用抵抗分圧回路 3041 および負極性用抵抗分圧回路 3042 に含まれる各抵抗素子の抵抗値を適宜の値に設定して基準電圧発生回路 700 からの正極性用の基準電圧と負極性用の基準電圧とをそれぞれ適宜の値に設定することにより、正極性の階調電圧と負極性の階調電圧とを好適値に設定することが容易にできる。また、基準電圧発生回路 700 から出力すべき複数の基準電圧が直流でよいので、基準電圧発生回路 700 の回路構成を簡易にできガンマ調整等の電圧調整を簡易で低コストな構成で行うことができる。

【0061】

<6. 変形例>

上記実施形態では、正極性用抵抗分圧回路 3041 および負極性用抵抗分圧回路 3042 に含まれるそれぞれの抵抗素子の個数は同数であるが、正極性用抵抗分圧回路 3041 および負極性用抵抗分圧回路 3042 に与えられる基準電圧の個数が異なる場合、正極性の階調電圧と負極性の階調電圧とが同数生成されるよう、上記抵抗素子の個数が異なる構成であってもよい。

【0062】

上記実施形態では、ライン反転駆動方式が採用されているが、n 本（n は 2 以上の自然数）の水平走査線毎に印加電圧の正負極性を反転させつつ 1 フレーム毎にも正負極性を反転させる駆動方式（「n ライン反転駆動方式」と呼ばれる）が採用されてもよいし、フレーム反転駆動方式が採用されてもよい。ここで、1 ドット反転駆動方式（または n ドット反転駆動方式）は、一般的に共通電極の電位が反転されることなく液晶パネルに印加すべき映像信号の極性を反転させるため、ドライバに高い耐圧性能が要求され、採用することができないが、擬似的なドット反転が実現されるように隣り合う 1 組の走査信号線を映像信号線毎に交互に入れ替えて配線するいわゆる疑似ドット反転駆動方式であれば採用してもよい。

【0063】

上記実施形態では、基準電圧発生回路 700 は、映像信号線駆動回路 300 の外部に設けられるが、内部に設けられてもよい。また、映像信号線駆動回路 300 は、液晶パネル 600 の内部に一体化されて設けられてもよい。

【図面の簡単な説明】

【0064】

【図 1】本発明の一実施形態に係る液晶表示装置の構成を示すブロック図である。

【図 2】上記一実施形態における液晶パネルの構成を示す模式図（a）および等価回路図（b）である。

【図 3】上記一実施形態における映像信号線駆動回路の構成を示すブロック図である。

10

20

30

40

50

【図4】上記一実施形態におけるD/A変換部に含まれる或るD/A変換回路の詳細な構成を説明するための図である。

【図5】上記一実施形態におけるD/A変換回路の一部分における詳細な構成を示す図である。

【図6】上記一実施形態における共通電圧信号V<sub>c o m</sub>およびアナログ電圧信号V<sub>a</sub>の電位変化を示す波形図である。

【図7】従来の液晶表示装置におけるD/A変換部に含まれる或るD/A変換回路の詳細な構成を説明するための図である。

【符号の説明】

【0065】

|                    |                    |    |

|--------------------|--------------------|----|

| 1 0                | ... TFT (薄膜トランジスタ) | 10 |

| 2 0 0              | ... 表示制御回路         |    |

| 3 0 0              | ... 映像信号線駆動回路      |    |

| 3 0 1              | ... シフトレジスタ部       |    |

| 3 0 2              | ... データラッチ部        |    |

| 3 0 3              | ... レベルシフタ部        |    |

| 3 0 4              | ... D/A変換部         |    |

| 3 0 5              | ... 出力バッファ部        |    |

| 4 0 0              | ... 走査信号線駆動回路      |    |

| 5 0 0              | ... 共通電極駆動回路       | 20 |

| 6 0 0              | ... 液晶パネル          |    |

| 7 0 0              | ... 基準電圧発生部        |    |

| 3 0 4 0            | ... D/A変換回路        |    |

| 3 0 4 1            | ... 正極性用抵抗分圧回路     |    |

| 3 0 4 2            | ... 負極性用抵抗分圧回路     |    |

| 3 0 4 3            | ... 選択回路           |    |

| 3 0 5 0            | ... 出力バッファ回路       |    |

| L s                | ... 映像信号線(列電極)     |    |

| L g                | ... 走査信号線(行電極)     |    |

| P x                | ... 画素形成部(画素)      | 30 |

| C p                | ... 画素容量           |    |

| E p                | ... 画素電極           |    |

| E c                | ... 共通電極(対向電極)     |    |

| V <sub>c o m</sub> | ... 共通電圧           |    |

| S C K              | ... ソース用クロック信号     |    |

| S S P              | ... ソース用スタートパルス信号  |    |

| G C K              | ... ゲート用クロック信号     |    |

| G S P              | ... ゲート用スタートパルス信号  |    |

|                    | ... 極性切換制御信号       |    |

| D a                | ... デジタル画像信号       | 40 |

| V <sub>a</sub>     | ... アナログ電圧信号       |    |

| V <sub>r</sub>     | ... 基準電圧           |    |

| V H 0 ~ V H 6 3    | ... 正極性の階調電圧       |    |

| V L 0 ~ V L 6 3    | ... 負極性の階調電圧       |    |

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 2 D |

| G 0 9 G | 3/20 | 6 2 3 F |

| G 0 9 G | 3/20 | 6 2 4 E |

| G 0 9 G | 3/20 | 6 4 1 C |

F ターム(参考) 5C006 AA16 AC11 AC21 AC25 AC27 AF42 AF46 AF71 AF83 BB16

BC12 BF02 BF03 BF04 BF11 BF24 BF25 BF43 FA16 FA23

FA41 FA46

5C080 AA10 BB05 DD06 DD22 DD27 EE29 FF11 GG12 JJ02 JJ03

JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 视频信号线驱动电路和具有该电路的液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2006178047A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2006-07-06 |

| 申请号            | JP2004369036                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2004-12-21 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 西久保圭志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 西久保 圭志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G09G3/36 G02F1/133.525 G02F1/133.575 G09G3/20.612.F G09G3/20.621.B G09G3/20.622.D G09G3/20.623.F G09G3/20.624.E G09G3/20.641.C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA31 2H093/NA32 2H093/NA43 2H093/NA53 2H093/NC03 2H093/NC10 2H093/NC12 2H093/NC13 2H093/NC21 2H093/NC22 2H093/NC26 2H093/NC34 2H093/NC49 2H093/ND06 2H093/ND35 2H093/ND58 5C006/AA16 5C006/AC11 5C006/AC21 5C006/AC25 5C006/AC27 5C006/AF42 5C006/AF46 5C006/AF71 5C006/AF83 5C006/BB16 5C006/BC12 5C006/BF02 5C006/BF03 5C006/BF04 5C006/BF11 5C006/BF24 5C006/BF25 5C006/BF43 5C006/FA16 5C006/FA23 5C006/FA41 5C006/FA46 5C080/AA10 5C080/BB05 5C080/DD06 5C080/DD22 5C080/DD27 5C080/EE29 5C080/FF11 5C080/GG12 5C080/JJ02 5C080/JJ03 5C080/JJ04 2H193/ZA04 2H193/ZC02 2H193/ZD23 2H193/ZF03 2H193/ZF22 2H193/ZF36 2H193/ZH40 |         |            |

| 代理人(译)         | 岛田彰                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

### 摘要(译)

解决的问题：提供一种视频信号线驱动电路以及包括该视频信号线驱动电路的液晶显示装置，该视频信号线驱动电路可以容易地将正和负灰度电压调节为合适的值并且可以容易地配置基准电压产生电路。视频信号线驱动电路中包括的D/A转换电路3040包括正电阻分压器电路3041，负电阻分压器电路3042和选择电路3043。根据来自显示控制电路200的极性切换控制信号 $\phi$ ，基于来自电压产生电路700的多个参考电压 $V_r$ ，从由每个电阻分压电路产生的灰度电压接收的与数字信号相对应的正电压。通过选择电路3043交替选择正灰度电压和负灰度电压。结果，可以将参考电压 $V_r$ 设置为直流，从而可以容易地配置参考电压生成电路，并且通过两个电阻分压电路可以容易地将正和负灰度电压调整为合适的值。[选择图]图4