(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-308942

(P2005-308942A)

(43) 公開日 平成17年11月4日(2005.11.4)

(51) Int.Cl.<sup>7</sup>

**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

**H05B 33/14**

F 1

GO9G 3/36

GO2F 1/133 550

GO2F 1/133 575

GO9G 3/20 611H

GO9G 3/20 611J

テーマコード(参考)

2H093

3K007

5C006

5C080

審査請求 未請求 請求項の数 6 O L (全 12 頁) 最終頁に続く

(21) 出願番号

(22) 出願日特願2004-123889(P2004-123889)

平成16年4月20日(2004.4.20)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100086298

弁理士 舟橋 國則

(72) 発明者 鈴木 三佐男

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 飯田 正幸

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

F ターム(参考) 2H093 NA16 NA42 NA43 NA53 NC10

NC12 NC23 NC34 NC35 NC49

ND06 ND36 ND38 ND39 ND52

3K007 AB17 BA06 DB03 GA00 GA04

最終頁に続く

(54) 【発明の名称】表示装置および表示装置の駆動方法

## (57) 【要約】

【課題】画素数が増大すると、相展開駆動法を採用した場合、ビデオ線の本数が少ないと起因して1つの画素に書き込む時間が短くなるため、画素に十分な電位を書き込めなくなる。

【解決手段】アクティブマトリクス型液晶表示装置において、サンプリングスイッチ群132の各トランジスタスイッチSW1～SWnがオフ状態になるときから画素20のTFT21オフ状態になる前、即ち画素20に対する映像信号Vsigの書き込み終了の直前に、信号線17-1～17-nの電位を映像信号Vsigの極性に対応した極性側に変動(シフト)させることで、映像信号Vsigのレベルに応じたビデオ線18の電位よりも大きなレンジで信号線17-1～17-nへの映像信号Vsigの書き込み動作を行い、高精細化・多画素化に伴って映像信号Vsigの書き込み時間が短くなった場合であっても、十分な電位を画素20に書き込めるようにする。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

電気光学素子を含む画素が基板上に行列状に2次元配置され、当該行列状の配列に対して列ごとに信号線が配線されてなる画素アレイ部と、

前記画素アレイ部の前記信号線の各々とビデオ線との間に接続され、当該ビデオ線を通して与えられる映像信号をサンプリングして前記信号線の各々に供給するサンプリングスイッチ群と、

前記サンプリングスイッチ群の各スイッチがオフ状態になるときから前記画素の選択／非選択を制御するスイッチ素子がオフ状態になる前に、前記信号線の電位を前記映像信号の極性に対応した極性側に変動させる制御手段と

を備えたことを特徴とする表示装置。

**【請求項 2】**

前記サンプリングスイッチ群の各スイッチは、NchトランジスタとPchトランジスタとが並列接続されてなり、互いに逆相の水平走査パルスに応答してオン／オフ動作を行うトランスファスイッチであり、

前記制御手段は、前記Nchトランジスタのゲート電極と前記信号線との間に直列に接続された第1のスイッチ素子および第1の容量素子と、前記Pchトランジスタのゲート電極と前記信号線との間に直列に接続された第2のスイッチ素子および第2の容量素子とを有し、前記第1，第2のスイッチ素子が前記映像信号の正極性時に非アクティブ、負極性時にアクティブとなる制御信号に同期してオン／オフ動作を行う

ことを特徴とする請求項1記載の表示装置。

**【請求項 3】**

前記第1，第2の容量素子は、ドレイン電極とソース電極とが共通に接続されてなるMOS容量である

ことを特徴とする請求項2記載の表示装置。

**【請求項 4】**

前記制御信号は、1水平走査期間ごとまたは1フィールド期間ごとに極性が反転することを特徴とする請求項2記載の表示装置。

**【請求項 5】**

前記制御手段は、前記Nchトランジスタのゲート電極と前記第1のスイッチ素子との間に接続された第1の遅延手段と、前記Pchトランジスタのゲート電極と前記第2のスイッチ素子との間に接続された第2の遅延手段とをさらに有する

ことを特徴とする請求項2記載の表示装置。

**【請求項 6】**

電気光学素子を含む画素が基板上に行列状に2次元配置され、当該行列状の配列に対して列ごとに信号線が配線されてなる画素アレイ部と、

前記画素アレイ部の前記信号線の各々とビデオ線との間に接続され、当該ビデオ線を通して与えられる映像信号をサンプリングして前記信号線の各々に供給するサンプリングスイッチ群とを備えた表示装置の駆動方法であって、

前記サンプリングスイッチ群の各スイッチがオフ状態になるときから前記画素の選択／非選択を制御するスイッチ素子がオフ状態になる前に、前記信号線の電位を前記映像信号の極性に対応した極性側に変動させる

ことを特徴とする表示装置の駆動方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置および表示装置の駆動方法に関し、特に電気光学素子を含む画素が行列状に2次元配置されてなる表示装置および当該表示装置の駆動方法に関する。

**【背景技術】****【0002】**

10

20

30

40

50

電気光学素子を含む画素が行列状に2次元配置されてなる表示装置、例えば画素の電気光学素子として液晶セルを用いた液晶表示装置では、液晶セルに対して電圧を印加することによってコントラストを得ている。液晶セルに対する電圧の印加は、アクティブマトリクス型液晶表示装置においては、画素の領域に容量（画素容量）およびスイッチ素子（画素スイッチ）を設け、画素容量に画素スイッチを介して電荷を充電することによって行われる。また、画素容量に対する電荷の充電は、画素アレイ部の各画素を行単位で選択する一方、外部からビデオ線を通して入力される映像信号を、画素アレイ部の画素列ごとに配線された信号線を介して選択行の各画素に書き込むことによって行われる。

### 【0003】

外部から入力される映像信号を画素に書き込む方法としては、一般的に、画素アレイ部のn本の信号線に対してn本のビデオ線を1対1の対応関係をもって配線し、外部のドライバICから入力されるn系統の映像信号をそのまま、n本のビデオ線を介して対応するn本の信号線に供給する方法が知られている。ただし、この書き込み方法では、近年の表示装置の高解像度化、高精細化の傾向に伴って信号線の本数nが増大すると、当該信号線と同数の多数のビデオ線を配線し、これら多数のビデオ線を通して複数系統の映像信号を並列的に入力するのが難しくなる。

### 【0004】

そこで、ビデオ線をn本よりも極めて少ない本数N(N < n)だけ表示パネル上に配線し、外部から映像信号をN相に展開して入力する一方、N本のビデオ線と画素アレイ部の信号線との間にスイッチ回路をN個単位で配置し、これらN個単位のスイッチ回路と同じスイッチ制御信号を用いて同時に駆動することで、選択行の各画素に対してN個の画素を単位として、N相展開された映像信号を同時に書き込む方法（以下、「相展開駆動法」と呼ぶ）が採られている（例えば、特許文献1参照）。この相展開駆動法によれば、表示パネル上に配線するビデオ線の本数を大幅に減らすことができる。

### 【0005】

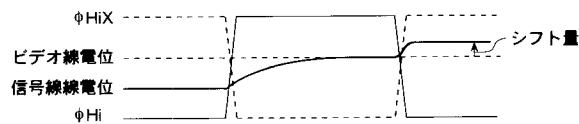

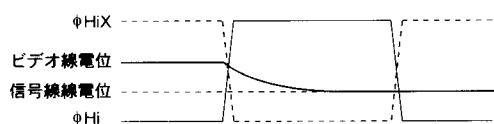

上記相展開駆動法を採用したアクティブマトリクス型液晶表示装置においては、ビデオ線を通して映像信号が入力され、スイッチ回路を駆動するスイッチ制御信号がアクティブになると、そのアクティブ期間においてスイッチ回路がオン状態となってビデオ線を信号線と接続することで、ビデオ線の電位（映像信号に応じて決まる電位）が信号線を通して画素に書き込まれる。そして、図8に示すように、信号線がビデオ線と同電位になった後に、スイッチ制御信号のアクティブ期間が終了し、スイッチ回路がオフ状態となることにより、信号線および画素に映像信号に応じた電位が保持される。

### 【0006】

【特許文献1】特開平11-65536号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

### 【0007】

ここで、スイッチ回路のオン期間は信号線の負荷、画素の負荷および水平方向の画素数によって決まる。近年、高精細な画像表示が求められるようになってきており、表示装置の画素数が増大する傾向にある。このように、高精細化に伴って画素数が増大すると、相展開駆動法を採用した場合、ビデオ線の本数が少ないと起因して1つの画素に書き込む時間が短くなる。これは、1行分の各画素に対して、規格で決められた水平期間内に映像信号を書き込む必要があるためである。1つの画素に書き込む時間が短くなると、画素に十分な電位を書き込めなくなるため、コントラストが低下したり、画素の特性ばらつきに起因して縦スジ状のノイズが生じたりするなど、画質低下の問題が発生する。

### 【0008】

また、特に投射型ディスプレイ向けの液晶表示装置では、当該液晶表示装置に入力される光量が増加する傾向にある。このため、画素内のスイッチ素子からリークする電流がコントラストの低下や滅点（点灯しない画素）などの画質不良を起こしやすくなる。したがって、上述したように、1つの画素に書き込む時間が短くなり、画素に十分な電位を書き

10

20

30

40

50

込めなくなると、光リークによるコントラストの低下や減点などの画質不良が目立ちやすくなる。

#### 【0009】

本発明は、上記課題に鑑みてなされたものであって、その目的とするところは、書き込み時間が短くなった場合においても十分な電位を画素に書き込むことができるとともに、光リークによるコントラストの低下や減点などの画質不良を改善可能な表示装置および当該表示装置の駆動方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0010】

上記目的を達成するために、本発明では、電気光学素子を含む画素が基板上に行列状に2次元配置され、当該行列状の配列に対して列ごとに信号線が配線されてなる画素アレイ部と、前記画素アレイ部の前記信号線の各々とビデオ線との間に接続され、当該ビデオ線を通して与えられる映像信号をサンプリングして前記信号線の各々に供給するサンプリングスイッチ群とを備えた表示装置において、前記サンプリングスイッチ群の各スイッチがオフ状態になるときから前記画素の選択／非選択を制御するスイッチ素子がオフ状態になる前に、前記信号線の電位を前記映像信号の極性に対応した極性側に変動させる構成を採っている。

#### 【0011】

上記構成の表示装置において、サンプリングスイッチ群の各スイッチがオフ（非導通）状態になるときから画素のスイッチ素子がオフ状態になる前、即ち画素に対する映像信号の書き込み終了の直前に、信号線の電位を映像信号の極性に対応した極性側に変動（シフト）させる、具体的には、映像信号の正極性の書き込み時には正極性側に、負極性の書き込み時には負極性側に信号線の電位を変動させることで、映像信号レベルに応じたビデオ線の電位よりも大きなレンジで信号線への映像信号の書き込みを行うことができる。

#### 【発明の効果】

#### 【0012】

本発明によれば、映像信号の画素に対する書き込み終了の直前に、信号線の電位を映像信号の極性に対応した極性側に変動（シフト）させることにより、映像信号レベルに応じたビデオ線の電位よりも大きなレンジで信号線に対する映像信号の書き込みを行うことができるため、書き込み時間が短くなった場合においても十分な電位を画素に書き込むことができるとともに、光リークによるコントラストの低下や減点などの画質不良を改善することができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

#### 【0014】

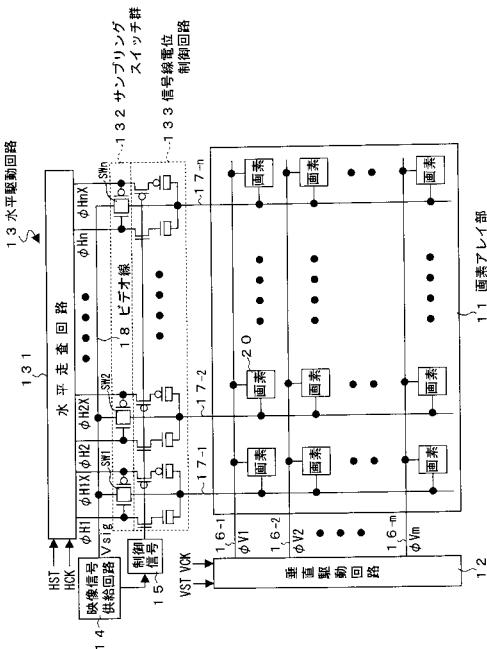

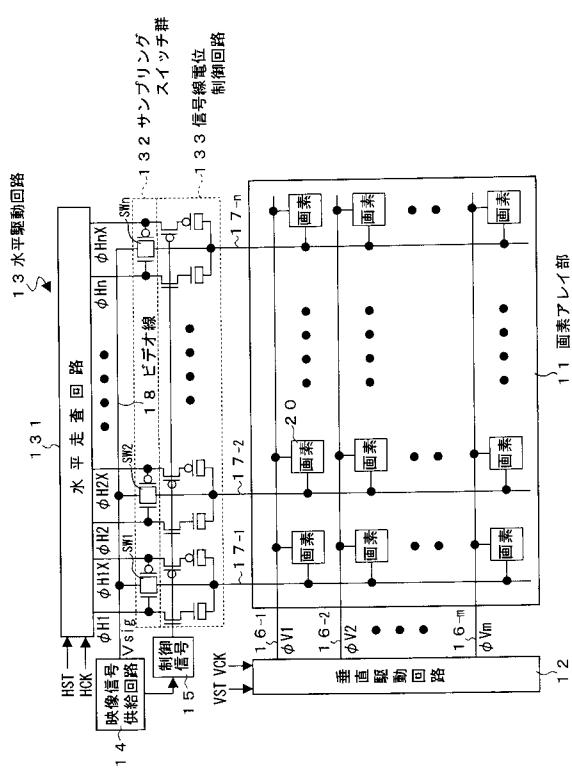

図1は、本発明の一実施形態に係る表示装置の構成の概略を示すブロック図である。ここでは、一例として、画素の電気光学素子として液晶セルを用いたアクティブマトリクス型液晶表示装置を例に挙げて説明するものとする。図1から明らかなように、本実施形態に係るアクティブマトリクス型液晶表示装置は、画素アレイ部11、垂直駆動回路12、水平駆動回路13、映像信号供給回路14および制御信号生成回路15を有する構成となっている。

#### 【0015】

画素アレイ部11は、電気光学素子である液晶セルを含む画素20が、透明絶縁基板、例えば第1のガラス基板（図示せず）上に行列状に2次元配置され、この画素20のm行n列の配列に対して行ごとに走査線16-1～16-mが配線され、列ごとに信号線17-1～17-nが配線された構成となっている。第1のガラス基板は、第2のガラス基板（図示せず）と所定の間隙を持って対向配置され、当該第2のガラス基板との間に液晶材料が封止されることによって表示パネルを構成している。

#### 【0016】

10

20

30

40

50

この表示パネル上に、垂直駆動回路12、水平駆動回路13、映像信号供給回路14および制御信号生成回路15が画素アレイ部11と共に設けられることになる。なお、映像信号供給回路14および制御信号生成回路15については、表示パネルの外に設けることも可能である。

#### 【0017】

図2は、画素(画素回路)20の回路構成の一例を示す回路図である。図2から明らかのように、画素20は、当該画素20の選択/非選択を制御するスイッチ素子である画素トランジスタ、例えばTFT(Thin Film Transistor;薄膜トランジスタ)21と、このTFT21のドレイン電極に画素電極が接続された液晶セル22と、TFT21のドレイン電極に一方の電極が接続された保持容量23とを有する構成となっている。ここで、液晶セル22は、画素電極とこれに対向して形成される対向電極との間で発生する液晶容量C<sub>1c</sub>を意味する。

#### 【0018】

TFT21は、ゲート電極が走査線16(16-1~16-m)に接続され、ソース電極が信号線17(17-1~17-n)に接続されている。また、例えば、液晶セル22の対向電極および保持容量23の他方の電極がコモン線24に対して各画素共通に接続されている。そして、液晶セル22の対向電極には、コモン線24を介してコモン電圧(対向電極電圧)V<sub>com</sub>が各画素共通に与えられる。

#### 【0019】

垂直駆動回路12は、画素アレイ部11の例えれば左側に配置されている。なお、ここでは、画素アレイ部11の左側に垂直駆動回路12を配置する構成を例に挙げて示したが、画素アレイ部11の右側に、あるいは画素アレイ部11の左右両側に垂直駆動回路12を配置する構成を探ることも可能である。垂直駆動回路12は、シフトレジスタやバッファ回路等によって構成され、垂直スタートパルスV<sub>ST</sub>が与えられることで、垂直クロックパルスV<sub>CK</sub>(一般的には、互いに逆相の垂直クロックパルスV<sub>CK</sub>, V<sub>CKX</sub>)に同期して垂直走査パルスV<sub>1~Vm</sub>を順に出力し、画素アレイ部11の走査線16-1~16-mに与えることによって画素20を行単位で順次選択する。

#### 【0020】

水平駆動回路13は、例えば、水平走査回路131、サンプリングスイッチ群132および信号線電位制御回路133を有する構成となっている。水平走査回路131は、シフトレジスタ等によって構成され、水平スタートパルスH<sub>ST</sub>に応答してシフト動作を開始し、当該水平スタートパルスH<sub>ST</sub>を水平クロックパルスH<sub>CK</sub>(一般的には、互いに逆相の水平クロックパルスH<sub>CK</sub>, H<sub>CKX</sub>)に同期して順次シフトすることにより、各転送段の転送パルスを、互いに逆相の水平走査パルスH<sub>1</sub>, H<sub>1X~Hn</sub>, H<sub>nX</sub>として順に出力する。

#### 【0021】

サンプリングスイッチ群132は、画素アレイ部11の信号線17-1~17-nの各々とビデオ線18との間に接続されたスイッチ回路、例えばNchトランジスタとPchトランジスタとが並列接続されてなるトランスファスイッチSW<sub>1~SWn</sub>によって構成され、ビデオ線18を通して映像信号供給回路14から与えられる映像信号V<sub>sig</sub>をサンプリングして信号線17-1~17-nの各々に供給する。

#### 【0022】

映像信号供給回路14は、1H(Hは水平走査期間)反転駆動法を探る場合には1Hごとに、1F(Fフィールド期間)反転駆動法を探る場合には1Fごとに、映像信号V<sub>sig</sub>の極性を反転させてながら当該映像信号V<sub>sig</sub>をビデオ線18に出力する。制御信号生成回路15は、映像信号V<sub>sig</sub>の極性反転に同期して、即ち当該極性反転に同期して映像信号供給回路14から出力される同期信号に基づいて、1Hごとあるいは1Fごとに極性が反転する、具体的には映像信号V<sub>sig</sub>の正極性のときに非アクティブ("L"レベル)、負極性のときにアクティブ("H"レベル)となる制御信号CSを信号線電位制御回路132に与える。

## 【0023】

信号線電位制御回路132は、制御信号生成回路15から与えられる制御信号CSに基づいて、サンプリングスイッチ群132の各トランスマスイッチSW1～SWnがオフ状態になるときから、画素20の選択／非選択を制御するスイッチ素子、即ちTFT21がオフ状態になる前に、信号線17-1～17-nの電位を映像信号Vsigの極性に対応した極性側に変動(シフト)させる、即ち映像信号Vsigが正極性のときには正極性側に、映像信号Vsigが負極性のときには負極性側に変動させる作用をなす。

## 【0024】

## [第1実施例]

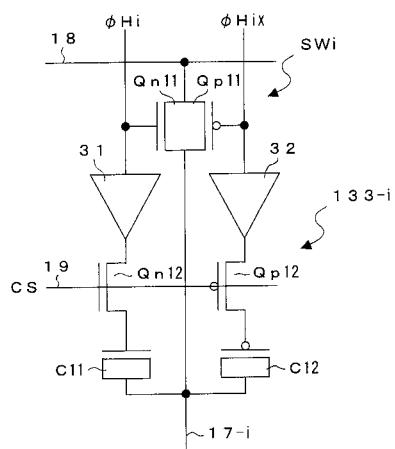

図3は、ある信号線17-iに対応したトランスマスイッチSWiおよび信号線電位制御回路133-iの第1実施例の回路構成を示す回路図である。 10

## 【0025】

図3において、トランスマスイッチSWiは、互いに並列に接続されたNchトランジスタQn11およびPchトランジスタQp11からなり、ビデオ線18と信号線17-iとの間に接続されている。そして、水平走査回路131から、NchトランジスタQn11のゲートには正相の水平走査パルスHiが、PchトランジスタQp11のゲートには逆相の水平走査パルスHiXがそれぞれ与えられる。

## 【0026】

信号線電位制御回路133-iは、2つのスイッチ素子、例えばNchトランジスタQn12およびPchトランジスタQp12と、2つの容量素子C11,C12とから構成されている。NchトランジスタQn12(以下、MOSスイッチQn12と記す)のドレイン電極は、NchトランジスタQn11のゲート電極に接続されている。PchトランジスタQp12(以下、MOSスイッチQp12と記す)のソース電極は、PchトランジスタQp11のゲート電極に接続されている。これらMOSスイッチQn12,Qp12の各ゲート電極には、制御信号生成回路15から出力される制御信号CSが制御線19を通して印加される。 20

## 【0027】

2つの容量素子C11,C12は、各一端がMOSスイッチQn12のソース電極とMOSスイッチQp12のドレイン電極にそれぞれ接続され、其他端が信号線17-iに共通に接続されている。これら容量素子C11,C12としては、例えば、NchトランジスタとPchトランジスタの各々についてドレイン電極とソース電極とを共通に接続してなるMOS容量が用いられる(以下、MOS容量C11,C12と記す)。ただし、MOS容量に限られるものではなく、一般的なキャパシタを始め、配線層間に形成した容量などを用いることも可能であるが、MOS容量を用いた方が、他のトランジスタQn11,Qn12およびPp11,Qp12と同様にポリシリコンで簡単に作ることができるため有利である。 30

## 【0028】

次に、上記構成の第1実施例に係るトランスマスイッチSWiおよび信号線電位制御回路133-iの回路動作について、図4および図5の波形図を用いて説明する。

## 【0029】

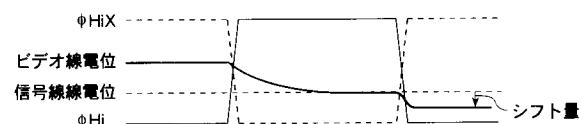

先ず、映像信号Vsigの正極性を信号線17-iを通して画素20に書き込むときの回路動作について、水平走査パルスHi,HiX、信号線17-iの電位およびビデオ線18の電位を示す図4の波形図を用いて説明する。 40

## 【0030】

映像信号Vsigの正極性を書き込むときには、制御信号CSが“L”レベルになる。これにより、MOSスイッチQn12がオフ状態となり、MOSスイッチQp12がオン状態となる。映像信号Vsigの書き込み動作では、初期状態に水平走査パルスHiが“L”レベルに、水平走査パルスHiXが“H”レベルにあり、トランスマスイッチSWiがオフ状態となっているが、水平走査パルスHiが“H”レベルに、水平走査パルスHiXが“L”レベルにそれぞれ遷移することで、トランスマスイッチSWiが 50

オン状態となる。

【0031】

このとき、先に述べたように、MOSスイッチQn12がオフ状態にあるため、MOS容量C11のゲートレベルは変化しない。これに対して、MOS容量C12のゲートレベルは、オン状態にあるMOSスイッチQp12を通して水平走査パルスHiXが“L”レベルが伝わるため、“H”レベルから“L”レベルへ遷移する。

【0032】

続いて、ビデオ線18からの信号線17-iに対する映像信号Vsig(正極性)の書き込みが十分に行われ、トランスマスイッチSWiがオン状態からオフ状態に移行するときの動作について説明する。

10

【0033】

トランスマスイッチSWiがオン状態からオフ状態に移行するときは、水平走査パルスHiが“H”レベルから“L”レベルに、水平走査パルスHiXが“L”レベルから“H”レベルにそれぞれ遷移する。このとき、MOSスイッチQn12がオフ状態にあるため、MOS容量C11のゲートレベルは変化しない。これに対して、MOSスイッチQp12がオン状態にあるため、MOS容量C12のゲートレベルは、水平走査パルスHiXと同様に“H”レベルに変化する。

【0034】

そして、トランスマスイッチSWiがオフ状態になると、信号線17-iはビデオ線18との接続が解除され、フローティング状態となる。このとき同時に、MOS容量C12による容量カップリングを受けるため、信号線17-iの電位は“H”レベル側に変動(シフト)する。その結果、映像信号Vsigの正極性の信号線17-iへの書き込み時には、図4の波形図から明らかなように、当該信号線17-iには映像信号Vsigのレベルに応じたビデオ線18の電位よりも高い電位で書き込みが行われる。

20

【0035】

一方、画素20では、上述した書き込み動作の終了後に、即ち画素20に対して映像信号Vsigの正極性が書き込まれた後に、画素スイッチであるTFT21(図2を参照)がオフ状態となる。換言すれば、信号線17-iを通して画素20に映像信号Vsigの正極性を書き込むときに、信号線17-iの電位をビデオ線18の電位よりも高い電位、即ち正極性側に変動(シフト)させるための上述した書き込み動作は、トランスマスイッチSWiがオフ状態になるときから画素20のTFT21がオフ状態になる前、即ち画素20に対する映像信号Vsigの正極性の書き込み終了直前に行われる。

30

【0036】

次に、映像信号Vsigの負極性を信号線17-iを通して画素20に書き込むときの回路動作について、水平走査パルスHi, HiX、信号線17-iの電位およびビデオ線18の電位を示す図5の波形図を用いて説明する。

【0037】

映像信号Vsigの負極性を書き込むときには、制御信号CSが“H”レベルになる。これにより、MOSスイッチQn12がオン状態となり、MOSスイッチQp12がオフ状態となる。このとき、MOSスイッチQn12がオン状態にあることで、MOS容量C11のゲートには水平走査パルスHiが与えられる。また、MOSスイッチQp12がオフ状態にあることで、MOS容量C12のゲートレベルは変化しない。

40

【0038】

続いて、ビデオ線18からの信号線17-iに対する映像信号Vsig(負極性)の書き込みが十分に行われ、トランスマスイッチSWiがオン状態からオフ状態に移行するときの動作について説明する。

【0039】

トランスマスイッチSWiがオン状態からオフ状態に移行するときは、水平走査パルスHiが“H”レベルから“L”レベルに、水平走査パルスHiXが“L”レベルから“H”レベルにそれぞれ遷移する。このとき、MOSスイッチQp12がオフ状態にあ

50

るため、MOS容量C12のゲートレベルは変化しない。これに対して、MOSスイッチQp11がオン状態にあるため、MOS容量C11のゲートレベルは、水平走査パルスHiと同様に“L”レベルに変化する。

#### 【0040】

そして、トランスマスイッチSWiがオフ状態になると、信号線17-iはビデオ線18との接続が解除され、フローティング状態となる。このとき同時に、MOS容量C11による容量カップリングを受けるため、信号線17-iの電位は“L”レベル側に変動(シフト)する。その結果、映像信号Vsigの負極性の信号線17-iへの書き込み時には、図5の波形図から明らかなように、当該信号線17-iには映像信号Vsigのレベルに応じたビデオ線18の電位よりも低い電位で書き込みが行われる。10

#### 【0041】

一方、画素20では、上述した書き込み動作の終了後に、即ち画素20に映像信号Vsigの負極性が書き込まれた後に、画素スイッチであるTFT21(図2を参照)がオフ状態となる。換言すれば、信号線17-iを通して画素20に映像信号Vsigの負極性を書き込むときに、信号線17-iの電位をビデオ線18の電位よりも低い電位、即ち負極性側に変動(シフト)させるための上述した書き込み動作は、トランスマスイッチSWiがオフ状態になるときから画素20のTFT21がオフ状態になる前、即ち画素20に対する映像信号Vsigの負極性の書き込み終了直前に行われる。20

#### 【0042】

上述したように、アクティブマトリクス型液晶表示装置において、サンプリングスイッチ群132の各トランスマスイッチSW1～SWnがオフ状態になるときから画素20のTFT21オフ状態になる前、即ち画素20に対する映像信号Vsigの書き込み終了の直前に、信号線17-1～17-nの電位を映像信号Vsigの極性に対応した極性側に変動(シフト)させることで、映像信号Vsigのレベルに応じたビデオ線18の電位よりも大きなレンジで信号線17-1～17-nへの映像信号Vsigの書き込み動作を行うことができる。30

#### 【0043】

一例として、従来技術では、3-8[V]の振幅の信号電圧が画素20に書き込まれていたのに対して、17-1～17-nの電位のシフト量±Vを例えば±0.2[V]とすると、本実施形態に係るアクティブマトリクス型液晶表示装置においては、2.8-8.2[V]の振幅の信号電圧を画素20に対して書き込めることになる。30

#### 【0044】

このように、ビデオ線18の電位よりも大きなレンジで信号線17-1～17-nへの映像信号Vsigの書き込み動作を行えることにより、高精細化・多画素化に伴って映像信号Vsigの書き込み時間が短くなった場合であっても、十分な電位を画素20に書き込むことができる。また、特に投射型ディスプレイ向け液晶表示装置において、入射される光量が増加したとしても、光リードによるコントラストの低下や滅点などに対しても、電荷のリーク分をMOS容量C11,C12でオーバーライトする形で液晶層に十分な電界をかけることができるため、コントラスト低下や滅点などの画質不良を改善できる。40

#### 【0045】

また、MOS容量C11,C12の各容量値については自由に設定できるため、その設定によってはビデオ線18の電位(映像信号Vsigのレベルに応じた電位)のレンジを小さくすることができる。これにより、映像信号Vsigの振幅を決める映像信号供給回路14の電源電圧を下げることができるため、当該電源電圧の低下分だけ液晶表示装置全体の消費電力を低減できる。

#### 【0046】

##### [第2実施例]

図6は、ある信号線17-iに対応したトランスマスイッチSWiおよび信号線電位制御回路133-iの第2実施例の回路構成を示す回路図であり、図中、図3と同等部分には同一符号を付して示している。50

## 【0047】

図6から明らかなように、本実施例に係る信号線電位制御回路133-iでは、トランジスタスイッチSWiを構成するトランジスタQn11, Qp11の各ゲート電極と、MOSスイッチQn12のドレイン電極およびMOSスイッチQp12のソース電極との間に、所定の遅延時間を持つ遅延手段、例えばバッファ31, 32をそれぞれ接続した構成を採っている。

## 【0048】

バッファ31, 32の遅延時間については、トランジスタスイッチSWiがオフする時間よりも長く、ビデオ線18から信号線17-iに映像信号Vsigを書き込む時間よりも短くなるように設定する。バッファ31, 32としては、例えば、インバータを偶数段直列に接続した構成のものを用いることができ、また当該インバータの段数によって遅延時間を任意に設定することが可能である。

## 【0049】

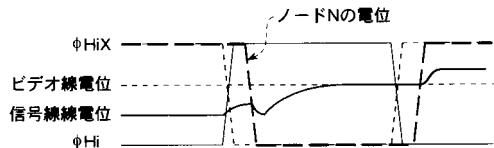

図7は、上記構成の第2実施例に係る信号線電位制御回路133-iを用いた場合において、映像信号Vsigの正極性を信号線17-iを通して画素20に書き込むときの水平走査パルスHi, HiX、バッファ32の出力ノードNの電位、信号線17-iの電位およびビデオ線18の電位を示す波形図である。

## 【0050】

上述したように、上記遅延時間を持つバッファ31, 32を、トランジスタスイッチSWiとMOSスイッチQn12, Qp12との間に設けたことにより、ビデオ線18から信号線17-iに対して映像信号Vsigに応じた電荷が書き込まれ、トランジスタスイッチSWiが完全にオフ状態になり、信号線17-iが完全にフローティングになった後にMOS容量C11, C12が駆動されることになる。このように、信号線17-iが完全にフローティングになったところでMOS容量C11, C12の駆動が行われることにより、信号線17-iの電位シフトを、バラツキが少なく、確実に行うことができる。

## 【0051】

なお、上記実施形態では、点順次駆動方式のアクティブマトリクス型液晶表示装置に適用した場合を例に挙げて説明したが、本発明はこの適用例に限られるものではなく、水平方向の複数ドット(画素)を単位として同時に書き込みを行う複数ドット同時サンプリング駆動方式や、先述した相展開駆動方式のアクティブマトリクス型液晶表示装置にも同様に適用可能である。

## 【0052】

また、上記実施形態では、画素の電気光学素子として液晶セルを用いた液晶表示装置に適用した場合を例に挙げて説明したが、本発明はこの適用例に限られるものではなく、画素の電気光学素子として有機EL(electro luminescence)素子を用いた有機EL表示装置など、電気光学素子を含む画素が行列状に2次元配置されてなる表示装置全般に適用可能である。

## 【図面の簡単な説明】

## 【0053】

【図1】本発明の一実施形態に係るアクティブマトリクス型液晶表示装置の構成の概略を示すブロック図である。

【図2】画素(画素回路)の回路構成の一例を示す回路図である。

【図3】トランジスタスイッチおよび信号線電位制御回路の第1実施例の回路構成を示す回路図である。

【図4】第1実施例に係る映像信号Vsigの正極性を書き込むときの水平走査パルスHi, HiX、信号線電位およびビデオ線電位を示す波形図である。

【図5】第1実施例に係る映像信号Vsigの負極性を書き込むときの水平走査パルスHi, HiX、信号線電位およびビデオ線電位を示す波形図である。

【図6】トランジスタスイッチおよび信号線電位制御回路の第2実施例の回路構成を示す回路図である。

【図7】第2実施例に係る映像信号Vsigの正極性を書き込むときの水平走査パルスHi, HiX、出力ノードNの電位、信号線電位およびビデオ線電位を示す波形図である。

【図8】従来例に係る映像信号Vsigの正極性を書き込むときの水平走査パルスHi, HiX、信号線電位およびビデオ線電位を示す波形図である。

【符号の説明】

【0054】

11...画素アレイ部、12...垂直駆動回路、13...水平駆動回路、14...映像信号供給回路、15...制御信号生成回路、16, 16-1~16-m...走査線、17, 17-1~17-n...信号線、18...ビデオ線、19...制御線、20...画素、21...TFT(画素トランジスタ)、22...液晶セル(液晶容量)、23...保持容量、30, 30-1~30-4...トランスファスイッチ、131...水平走査回路、132...サンプリングスイッチ群、133, 133-i...信号線電位制御回路、SW1~SWn...トランスファスイッチ

【図1】

【図4】

【図5】

【図6】

【図7】

【図8】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 1 B |

| G 0 9 G | 3/20  | 6 2 3 L |

| G 0 9 G | 3/20  | 6 2 3 R |

| G 0 9 G | 3/20  | 6 2 3 Y |

| G 0 9 G | 3/20  | 6 4 1 C |

| G 0 9 G | 3/20  | 6 4 2 A |

| G 0 9 G | 3/20  | 6 4 2 E |

| G 0 9 G | 3/20  | 6 7 0 E |

| G 0 9 G | 3/20  | 6 8 0 C |

| H 0 5 B | 33/14 | A       |

F ターム(参考) 5C006 AA16 AC09 AC11 AC21 AC27 AC28 AF50 AF72 BB16 BC13

BC20 BF03 BF07 BF11 BF25 BF27 BF33 BF34 BF37 EC11

FA12 FA16 FA20 FA22 FA26 FA36 FA37 FA46 FA47 FA54

5C080 AA10 BB05 DD05 DD08 DD10 DD26 EE29 FF11 JJ02 JJ03

JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和显示装置的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2005308942A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2005-11-04 |

| 申请号            | JP2004123889                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2004-04-20 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 鈴木三佐男<br>飯田正幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 鈴木三佐男<br>飯田正幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 H01L51/50 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.575 G09G3/20.611.H G09G3/20.611.J G09G3/20.621.B G09G3/20.623.L G09G3/20.623.R G09G3/20.623.Y G09G3/20.641.C G09G3/20.642.A G09G3/20.642.E G09G3/20.670.E G09G3/20.680.C H05B33/14.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA42 2H093/NA43 2H093/NA53 2H093/NC10 2H093/NC12 2H093/NC23 2H093/NC34 2H093/NC35 2H093/NC49 2H093/ND06 2H093/ND36 2H093/ND38 2H093/ND39 2H093/ND52 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5C006/AA16 5C006/AC09 5C006/AC11 5C006/AC21 5C006/AC27 5C006/AC28 5C006/AF50 5C006/AF72 5C006/BB16 5C006/BC13 5C006/BC20 5C006/BF03 5C006/BF07 5C006/BF11 5C006/BF25 5C006/BF27 5C006/BF33 5C006/BF34 5C006/BF37 5C006/EC11 5C006/FA12 5C006/FA16 5C006/FA20 5C006/FA22 5C006/FA26 5C006/FA36 5C006/FA37 5C006/FA46 5C006/FA47 5C006/FA54 5C080/AA10 5C080/BB05 5C080/DD05 5C080/DD08 5C080/DD10 5C080/DD26 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 2H193/ZA04 2H193/ZC22 2H193/ZD23 2H193/ZF22 2H193/ZF36 3K107/AA01 3K107/BB01 3K107/CC26 3K107/CC32 3K107/EE03 3K107/HH04 |         |            |

| 代理人(译)         | 船桥国则                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

## 摘要(译)

要解决的问题：为了解决由于在相位显影驱动方法中视频线的数量少，因此随着像素数量的增加，在一个像素中写入的时间变短，因此无法在像素中写入足够的电位的问题受雇了。解决方案：有源矩阵型液晶显示装置通过改变（移位）将视频信号Vsigt写入信号线17-1至17-n，其范围大于视频线18的电位，该电位对应于视频信号Vsigt的电平。）在像素20的TFT21从采样开关组132的各个转移开关SW1至SWn关闭之前，信号线17-1至17-n的电位对应于视频信号Vsigt的极性的极性侧关闭，即恰好在写入视频信号Vsigt到像素20之前结束，使得即使当视频信号Vsigt的写入时间随着细度增加和像素数量增加而变短时，也可以在像素20中写入足够的电位。