### (19) **日本国特許庁(JP)**

(E1) Int CI

# (12) 公 開 特 許 公 報(A)

DТ

(11)特許出願公開番号

テーフュード (衆老)

特開2009-103948 (P2009-103948A)

(43) 公開日 平成21年5月14日(2009.5.14)

BC12 BF25 BF50 FA16 5C080 AA10 BB05 DD19 FF11 JJ02 JJ03 JJ04 JJ06

| (51) INT.CI. |       |               | F I            |         |            |        | アー    | くコート | (多)  | 写)   |

|--------------|-------|---------------|----------------|---------|------------|--------|-------|------|------|------|

| G09G         | 3/36  | (2006.01)     | GO9G           | 3/36    |            |        | 2 H ( | 93   |      |      |

| G09G         | 3/20  | (2006.01)     | GO9G           | 3/20    | 623D       |        | 5 C C | 006  |      |      |

| G02F         | 1/133 | (2006.01)     | GO9G           | 3/20    | 621A       |        | 5 C ( | 080  |      |      |

|              |       |               | GO9G           | 3/20    | 612L       |        |       |      |      |      |

|              |       |               | GO9G           | 3/20    | 621B       |        |       |      |      |      |

|              |       |               | 審査請求 未         | 請求      |            | OL     | (全 17 | 7 頁) | 最終」  | 頁に続く |

| (21) 出願番号    |       | 特願2007-276002 | (P2007-276002) | (71) 出原 | 頁人 0000050 | )49    |       |      |      |      |

| (22) 出願日     |       | 平成19年10月24日   | (2007.10.24)   |         | シャー        | プ株式会   | 社     |      |      |      |

|              |       |               |                |         | 大阪府:       | 大阪市阿   | 倍野区   | 長池町  | 22番  | 22号  |

|              |       |               |                | (74) 代理 | ■人 1001046 | 395    |       |      |      |      |

|              |       |               |                |         | 弁理士        | 島田     | 明宏    |      |      |      |

|              |       |               |                | (72) 発明 | 君劉憲        | 太郎     |       |      |      |      |

|              |       |               |                |         | 大阪府:       | 大阪市阿   | 倍野区   | 長池町  | 22番  | 22号  |

|              |       |               |                |         | シャ・        | - プ株式  | 会社内   |      |      |      |

|              |       |               |                | Fター1    | 、(参考) 2H09 | 3 NA16 | NA31  | NA43 | NC02 | NC09 |

|              |       |               |                |         |            | NC11   | NC16  | NC22 | NC23 | NC26 |

|              |       |               |                |         |            | NC34   | NC35  | ND47 |      |      |

|              |       |               |                |         | 5C00       | 6 AC21 | AC27  | AF42 | AF71 | BB16 |

### (54) 【発明の名称】液晶表示装置

### (57)【要約】

【課題】共通電極電圧の変化に起因するデータ信号線駆動回路の破壊を防止する。

【解決手段】共通電極駆動回路23は、極性制御信号REVCに従い、液晶パネル11の共通電極35に対する印加電圧を変化させる。タイミング制御回路21は、極性制御信号REVCが変化するタイミングに合わせて、出力制御信号ZCTRLを変化させる。データ信号線駆動回路13は、出力制御信号ZCTRLに従い、データ信号線Sjをハイインピーダンス状態に設定する。共通電極電圧COMの変化タイミングに合わせてデータ信号線Sjをハイインピーダンス状態に設定し、共通電極電圧が変化したときの突き上げや突き下げによるデータ信号線電圧の変化を抑えて、データ信号線駆動回路13の破壊を防止する。

### 【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

共通電極を交流駆動する液晶表示装置であって、

複数の走査信号線と、複数のデータ信号線と、前記走査信号線および前記データ信号線の交点近傍に設けられた複数のスイッチング素子と、前記スイッチング素子に対応して設けられた複数の画素電極と、前記画素電極に対向する共通電極とを含む液晶パネルと、

前記走査信号線を駆動する走査信号線駆動回路と、

前記データ信号線を駆動するデータ信号線駆動回路と、

前記共通電極に対して、相対的に低い電圧と相対的に高い電圧を切り替えて印加する共通電極駆動回路と、

前記走査信号線駆動回路、前記データ信号線駆動回路および前記共通電極駆動回路に対する制御信号を出力するタイミング制御回路とを備え、

前記データ信号線駆動回路は、前記共通電極の電圧が変化するタイミングに合わせて前記データ信号線をハイインピーダンス状態に設定することを特徴とする、液晶表示装置。

### 【請求項2】

前記データ信号線駆動回路は、前記タイミング制御回路から出力された出力制御信号に従い、前記データ信号線をハイインピーダンス状態に設定することを特徴とする、請求項1に記載の液晶表示装置。

### 【請求項3】

前記共通電極駆動回路は、前記タイミング制御回路から出力された極性制御信号に従い、前記共通電極に印加する電圧を変化させ、

前記タイミング制御回路は、前記極性制御信号が変化するタイミングに応じたタイミングで前記出力制御信号を変化させることを特徴とする、請求項2に記載の液晶表示装置。

### 【請求項4】

前記タイミング制御回路は、外部から値を設定可能なレジスタを含み、前記レジスタに設定された値に応じて、前記極性制御信号と前記出力制御信号が変化するタイミングを切り替えることを特徴とする、請求項3に記載の液晶表示装置。

#### 【請求項5】

前記データ信号線駆動回路は、外部から値を設定可能なレジスタを含み、前記レジスタに設定された値に応じて、前記データ信号線をハイインピーダンス状態に設定するタイミングを切り替えることを特徴とする、請求項1に記載の液晶表示装置。

### 【請求項6】

前記共通電極駆動回路は、前記タイミング制御回路から出力された極性制御信号に従い、前記共通電極に印加する電圧を変化させ、

前記タイミング制御回路は、前記極性制御信号が変化するタイミングに応じて、前記レジスタに設定する値を切り替えることを特徴とする、請求項5に記載の液晶表示装置。

### 【請求項7】

複数の走査信号線と、複数のデータ信号線と、前記走査信号線および前記データ信号線の交点近傍に設けられた複数のスイッチング素子と、前記スイッチング素子に対応して設けられた複数の画素電極と、前記画素電極に対向する共通電極とを含む液晶パネルの駆動方法であって、

前記走査信号線を駆動するステップと、

前記データ信号線を駆動するステップと、

前記共通電極に対して、相対的に低い電圧と相対的に高い電圧を切り替えて印加するステップと、

前記走査信号線、前記データ信号線および前記共通電極を駆動するときのタイミングを 制御するステップとを備え、

前記データ信号線を駆動するステップは、前記共通電極の電圧が変化するタイミングに合わせて前記データ信号線をハイインピーダンス状態に設定することを特徴とする、液晶パネルの駆動方法。

10

20

30

40

#### 【発明の詳細な説明】

【技術分野】

[0001]

本発明は、液晶表示装置に関し、より特定的には、共通電極を交流駆動する液晶表示装置に関する。

【背景技術】

[00002]

液晶表示装置では、焼き付きを防止するために、液晶に対して正極性電圧と負極性電圧を切り替えて印加する交流駆動が行われる。また、データ信号線の電圧振幅を小さくするために、液晶印加電圧の極性に応じて、共通電極に対して相対的に低い電圧と相対的に高い電圧を切り替えて印加する駆動(共通電極の交流駆動)が行われることがある。

[00003]

なお、本願発明に関連して、特許文献 1 には、 2 枚の液晶パネルを備えた液晶表示装置において、各液晶パネルの共通電極電圧を同時に互いに逆極性に反転させることが記載されている。

【特許文献 1 】特開 2 0 0 6 - 7 2 2 1 1 号公報

【発明の開示】

【発明が解決しようとする課題】

[0004]

共通電極を交流駆動する液晶表示装置では、表示画面の画質を向上させるために、共通電極の電圧振幅を大きくすることがある。ところが、共通電極の電圧振幅を大きくすると、共通電極電圧が変化したときに、データ信号線の電圧波形に大きなパルス状のノイズが発生し、データ信号線駆動回路が破壊されることがある。

[0005]

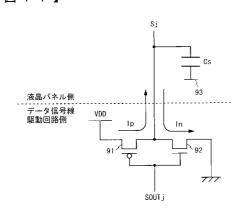

図11は、液晶パネルとデータ信号線駆動回路の一部を示す図である。図11において、破線より上の回路は液晶パネル上に形成されており、破線より下の回路はデータ信号線駆動回路に内蔵されている。データ信号線 S j は、データ信号線駆動回路に内蔵された P チャネル型のトランジスタ 9 1 と N チャネル型のトランジスタ 9 2 とによって駆動される。また、液晶パネルでは、データ信号線 S j と共通電極 9 3 の間に寄生容量 C s が発生する。

[0006]

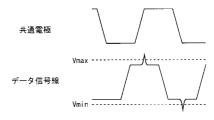

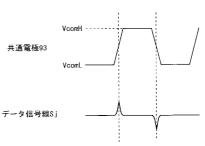

共通電極93の電圧は、図12に示すように、所定の周期で相対的に低いレベルVcomLと相対的に高いレベルVcomHに切り替えられる。共通電極93とデータ信号線Sjの間には寄生容量Csが介在しているので、共通電極電圧がVcomLからVcomHに上昇すると、データ信号線Sjの電圧はその影響を受けて一時的に上昇する(以下、この現象を「突き上げ」という)。また、共通電極電圧がVcomHからVcomLに低下すると、データ信号線Sjの電圧は一時的に低下する(以下、この現象を「突き下げ」という)。

[0007]

共通電極の電圧振幅が小さいときには、突き上げや突き下げが発生しても、データ信号線Sjの電圧はデータ信号線駆動回路の耐圧電圧を超えないので、データ信号線駆動回路が破壊されることはない。しかしながら、共通電極の電圧振幅を大きくすると、突き上げや突き下げによってデータ信号線Sjの電圧が一時的にデータ信号線駆動回路の耐圧電圧を超え、データ信号線駆動回路が破壊されることがある。

[00008]

このようなデータ信号線駆動回路の破壊を防止する方法として、データ信号線駆動回路の出力段トランジスタ(図11ではトランジスタ91、92)のオン抵抗を小さくする方法が考えられる。この方法によれば、共通電極電圧が変化したときの突き上げエネルギーや突き下げエネルギーを電源やグランドに逃がし、突き上げや突き下げの影響を小さくすることができる。

10

20

30

40

### [0009]

しかしながら、出力段トランジスタのオン抵抗を小さくするにも限界があり、この方法 では、共通電極の電圧振幅が大きいときに、突き上げや突き下げによるデータ信号線駆動 回路の破壊を防止できないことがある。

### [0010]

それ故に、本発明は、共通電極電圧の変化に起因するデータ信号線駆動回路の破壊をよ リ 効 果 的 に 防 止 で き る 液 晶 表 示 装 置 を 提 供 す る こ と を 目 的 と す る 。

### 【課題を解決するための手段】

### [0011]

第 1 の 発 明 は 、 共 通 電 極 を 交 流 駆 動 す る 液 晶 表 示 装 置 で あ っ て 、

複 数 の 走 査 信 号 線 と 、 複 数 の デ ー タ 信 号 線 と 、 前 記 走 査 信 号 線 お よ び 前 記 デ ー タ 信 号 線 の交点近傍に設けられた複数のスイッチング素子と、前記スイッチング素子に対応して設 けられた複数の画素電極と、前記画素電極に対向する共通電極とを含む液晶パネルと、

前記走査信号線を駆動する走査信号線駆動回路と、

前記データ信号線を駆動するデータ信号線駆動回路と、

前記共通電極に対して、相対的に低い電圧と相対的に高い電圧を切り替えて印加する共 通電極駆動回路と、

前 記 走 査 信 号 線 駆 動 回 路 、 前 記 デ ー タ 信 号 線 駆 動 回 路 お よ び 前 記 共 通 電 極 駆 動 回 路 に 対 する制御信号を出力するタイミング制御回路とを備え、

前記データ信号線駆動回路は、前記共通電極の電圧が変化するタイミングに合わせて前 記データ信号線をハイインピーダンス状態に設定することを特徴とする。

#### [0012]

第2の発明は、第1の発明において、

前記データ信号線駆動回路は、前記タイミング制御回路から出力された出力制御信号に 従い、前記データ信号線をハイインピーダンス状態に設定することを特徴とする。

### [0013]

第3の発明は、第2の発明において、

前記共通電極駆動回路は、前記タイミング制御回路から出力された極性制御信号に従い 、前記共通電極に印加する電圧を変化させ、

前 記 タイ ミ ン グ 制 御 回 路 は 、 前 記 極 性 制 御 信 号 が 変 化 す る タ イ ミ ン グ に 応 じ た タ イ ミ ン グで前記出力制御信号を変化させることを特徴とする。

### [0014]

第4の発明は、第3の発明において、

前 記 タ イ ミ ン グ 制 御 回 路 は 、 外 部 か ら 値 を 設 定 可 能 な レ ジ ス タ を 含 み 、 前 記 レ ジ ス タ に 設定された値に応じて、前記極性制御信号と前記出力制御信号が変化するタイミングを切 り替えることを特徴とする。

#### [0015]

第5の発明は、第1の発明において、

前 記 デ ー タ 信 号 線 駆 動 回 路 は 、 外 部 か ら 値 を 設 定 可 能 な レ ジ ス タ を 含 み 、 前 記 レ ジ ス タ に 設 定 さ れ た 値 に 応 じ て 、 前 記 デ ー タ 信 号 線 を ハ イ イ ン ピ ー ダ ン ス 状 態 に 設 定 す る タ イ ミ ングを切り替えることを特徴とする。

#### [0016]

第6の発明は、第5の発明において、

前記共通電極駆動回路は、前記タイミング制御回路から出力された極性制御信号に従い 、前記共通電極に印加する電圧を変化させ、

前 記 タ イ ミ ン グ 制 御 回 路 は 、 前 記 極 性 制 御 信 号 が 変 化 す る タ イ ミ ン グ に 応 じ て 、 前 記 レ ジスタに設定する値を切り替えることを特徴とする。

第7の発明は、複数の走査信号線と、複数のデータ信号線と、前記走査信号線および前 記 デ ー タ 信 号 線 の 交 点 近 傍 に 設 け ら れ た 複 数 の ス イ ッ チ ン グ 素 子 と 、 前 記 ス イ ッ チ ン グ 素 10

20

30

40

子に対応して設けられた複数の画素電極と、前記画素電極に対向する共通電極とを含む液晶パネルの駆動方法であって、

前記走査信号線を駆動するステップと、

前記データ信号線を駆動するステップと、

前記共通電極に対して、相対的に低い電圧と相対的に高い電圧を切り替えて印加するステップと、

前記走査信号線、前記データ信号線および前記共通電極を駆動するときのタイミングを制御するステップとを備え、

前記データ信号線を駆動するステップは、前記共通電極の電圧が変化するタイミングに合わせて前記データ信号線をハイインピーダンス状態に設定することを特徴とする。

### 【発明の効果】

#### [ 0 0 1 8 ]

上記第1または第7の発明によれば、共通電極電圧の変化タイミングに合わせてデータ信号線をハイインピーダンス状態に設定することにより、共通電極電圧が変化したときに、その影響を受けてデータ信号線電圧が変化することを防止することができる。したがって、共通電極電圧が変化したときの突き上げや突き下げによるデータ信号線電圧の変化を抑え、データ信号線駆動回路の破壊を効果的に防止することができる。

### [0019]

上記第2の発明によれば、タイミング制御回路から出力された出力制御信号を用いて、データ信号線をハイインピーダンス状態に設定するか否かを切り替えることができる。したがって、データ信号線をハイインピーダンス状態に設定するタイミングをタイミング制御回路で調整して、共通電極電圧の変化に起因するデータ信号線駆動回路の破壊を防止することができる。

### [0020]

上記第3の発明によれば、共通電極電圧の変化タイミングが極性制御信号によって定まる場合に、極性制御信号の変化タイミングに応じたタイミングで出力制御信号を変化させることにより、共通電極電圧の変化タイミングに合わせてデータ信号線をハイインピーダンス状態に設定することができる。これにより、共通電極電圧の変化に起因するデータ信号線駆動回路の破壊を防止することができる。

### [0021]

上記第4の発明によれば、タイミング制御回路のレジスタに値を設定することにより、極性制御信号と出力制御信号の変化タイミングを切り替えることができる。したがって、 共通電極電圧の変化タイミングとデータ信号線のハイインピーダンス期間を好適に調整し 、共通電極電圧の変化に起因するデータ信号線駆動回路の破壊を防止することができる。

### [0022]

上記第5の発明によれば、タイミング制御回路からデータ信号線駆動回路のレジスタに値を設定することにより、データ信号線をハイインピーダンス状態に設定するタイミングを切り換えることができる。したがって、データ信号線をハイインピーダンス状態に設定するタイミングをタイミング制御回路で調整して、共通電極電圧の変化に起因するデータ信号線駆動回路の破壊を防止することができる。

### [ 0 0 2 3 ]

上記第6の発明によれば、共通電極電圧の変化タイミングが極性制御信号によって定まる場合に、極性制御信号の変化タイミングに対応した値をデータ信号線駆動回路のレジスタに設定することにより、共通電極電圧の変化タイミングに合わせてデータ信号線をハイインピーダンス状態に設定することができる。これにより、共通電極電圧の変化に起因するデータ信号線駆動回路の破壊を防止することができる。

### 【発明を実施するための最良の形態】

### [0024]

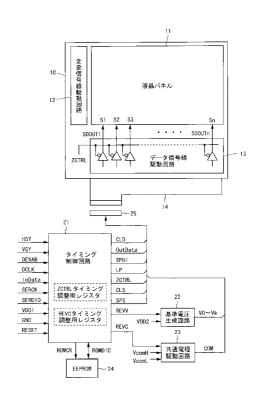

図1は、本発明の実施形態に係る液晶表示装置の構成を示すブロック図である。図1に示す液晶表示装置は、液晶パネル11、走査信号線駆動回路12、データ信号線駆動回路

10

20

30

40

20

30

40

50

13、タイミング制御回路 21、基準電圧生成回路 22、共通電極駆動回路 23、および、EEPROM (Electronically Erasable Programmable Read Only Memory ) 24を備えている。なお、走査信号線駆動回路 12はゲートドライバ回路、データ信号線駆動回路 13はソースドライバ回路とも呼ばれる。

### [ 0 0 2 5 ]

液晶パネル11、走査信号線駆動回路12およびデータ信号線駆動回路13は、パネル基板10に搭載されている。タイミング制御回路21、基準電圧生成回路22、共通電極駆動回路23およびEEPROM24は、制御基板(図示せず)に搭載されている。パネル基板10にはフレキシブル回路基板14が設けられており、フレキシブル回路基板14の一端は制御基板に設けられたコネクタ25に挿入可能に構成されている。制御基板上の回路から出力された信号は、コネクタ25経由でパネル基板10上の回路に供給される。

[0026]

図2は、液晶パネル11の構造を示す図である。図2に示すように、液晶パネル11は、2枚のガラス基板31、32の間に液晶(図示せず)を挟み込んだ構造を有する。一方のガラス基板31には、互いに平行に配置された複数の走査信号線G1~Gmと、走査信号線G1~Gmと前に互いに平行に配置された複数のデータ信号線S1~Snの交点近傍に配置された複数のTFT(Thin Film Transistor:薄膜トランジスタ)33と、TFT33に対応して設けられた複数の画素電極34とが形成される。TFT33はスイッチング素子として機能し、TFT33のゲート端子、ソース端子およびドレイン端子は、それぞれ、1本の走査信号線、1本のデータ信号線および1個の画素電極34に接続される。他方のガラス基板32には、すべての画素電極34と対向するように共通電極35が形成される。

[0027]

走査信号線駆動回路12は、走査信号線G1~Gmを駆動する。より詳細には、走査信号線駆動回路12は、走査信号線G1~Gmの中から1本の走査信号線を順に選択し、選択した走査信号線には選択電圧(例えば、ハイレベル電圧)を印加し、それ以外の走査信号線には非選択電圧(例えば、ローレベル電圧)を印加する。これにより、選択された走査信号線に接続されたn個のTFT33が導通状態となり、導通状態のTFT33に接続されたn個の画素電極34が電圧書き込み可能な状態となる。

[0028]

データ信号線駆動回路13は、データ信号線S1~Snをライン反転駆動する。より詳細には、データ信号線駆動回路13は、データ信号線S1~Snに対して、1ラインごとに表示データに応じた正極性電圧と表示データに応じた負極性電圧を切り替えて印加する。これにより、電圧書き込み可能な状態にあるn個の画素電極34に、表示データに応じた正極性電圧または負極性電圧が書き込まれる。

[0029]

画素電極34に正極性電圧を書き込むときには、共通電極35には相対的に低い電圧VcomLが印加され、画素電極34に負極性電圧を書き込むときには、共通電極35には相対的に高い電圧VcomH(VcomL < VcomH)が印加される。画素電極34は1個の画素に対応し、画素の輝度は画素電極34と共通電極35の電位差によって定まる。したがって、共通電極35に電圧VcomLまたはVcomHを印加し、画素電極34に表示データに応じた正極性電圧または負極性電圧を書き込むことにより、液晶パネル11に所望の画像を表示することができる。

[0030]

タイミング制御回路 2 1、基準電圧生成回路 2 2 および共通電極駆動回路 2 3 は、パネル基板 1 0 に対して映像信号と制御信号を出力する。タイミング制御回路 2 1 には、水平同期信号 H S Y、垂直同期信号 V S Y、水平表示開始位置を指定するデータイネーブル信号 D E N A B、データクロック D C L K、表示データ I n D a t a などが入力される。タイミング制御回路 2 1 は、これらの入力信号に基づき、サンプリングクロック C L D、表示データ O u t D a t a、データ側スタートパルス S P O I、ラッチパルス L P、出力制

御信号 Z C T R L、シフトクロック C L S、走査側スタートパルス S P S、第 1 の極性制御信号 R E V C を出力する。

### [0031]

シフトクロックCLSと走査側スタートパルスSPSは走査信号線駆動回路12に供給され、サンプリングクロックCLD、表示データOutData、データ側スタートパルスSPOI、ラッチパルスLPおよび出力制御信号ZCTRLは、データ信号線駆動回路13に供給される。第1の極性制御信号REVVは基準電圧生成回路22に供給され、第2の極性制御信号REVCは共通電極駆動回路23に供給される。なお、表示データInData、OutDataは例えばRGB各6ビットの映像信号であり、出力制御信号ZCTRL、第1の極性制御信号REVVおよび第2の極性制御信号REVCはハイレベルとローレベルに変化する2値の信号である。

#### [0032]

基準電圧生成回路22は、データ信号線駆動回路13で必要とされる電源電圧を生成する。より詳細には、基準電圧生成回路22は、データ信号線S1~Snに印加される電圧の基準となる複数の基準電圧V0~Vk(kは1以上の整数)を生成し、データ信号線駆動回路13は、供給された基準電圧V0~Vkに基づき、データ信号線S1~Snに印加する電圧を生成する。上述したように、データ信号線駆動回路13は、データ信号線S1~Snに対して、正極性電圧と負極性電圧を切り替えて印加する。これに対応して、基準電圧生成回路22は、基準電圧V0~Vkとして正極性の基準電圧と負極性の基準電圧を切り替えて生成する。

#### [0033]

基準電圧生成回路22には、第1の極性制御信号REVVと電源電圧VDD2(例えば、5.3V)が入力される。基準電圧生成回路22は、第1の極性制御信号REVVがローレベルのときには、電源電圧VDD2に基づき正極性の基準電圧を生成し、第1の極性制御信号REVVがハイレベルのときには、電源電圧VDD2に基づき負極性の基準電圧を生成する。第1の極性制御信号REVVが変化した後、指定された極性の基準電圧VO~Vkが基準電圧生成回路22から出力されるまでには、数μs程度の時間がかかる。

#### [ 0 0 3 4 ]

共通電極駆動回路23は、共通電極35に対して、相対的に低い電圧VcomLと相対的に高い電圧VcomHを切り替えて印加する。より詳細には、共通電極駆動回路23には、第2の極性制御信号REVcomH、および、電圧VcomLが入力される。共通電極駆動回路23は、第2の極性制御信号REVCがローレベルのときには共通電極電圧COMとして電圧VcomLを出力し、第2の極性制御信号REVCがハイレベルのときには共通電極電圧COMとして電圧VcomHを出力する。第2の極性制御信号REVCが変化した後、指定された極性の共通電極電圧COMが共通電極駆動回路23から出力されるまでには、数μs程度の時間がかかる。

### [0035]

タイミング制御回路21は、外部から値を設定可能なレジスタを含み、レジスタに設定された値に応じて、出力制御信号ZCTRLおよび第2の極性制御信号REVCが変化するタイミングを切り替える。タイミング制御回路21は、レジスタに設定された値に応じて、ラッチパルスLPや第1の極性制御信号REVVなどが変化するタイミングを切り替えてもよい。タイミング制御回路21は、ホストとの間でシリアル通信を行うために2個の端子SERCK、SERDIOを有する。これらの端子にクロックとデータを与えることにより、タイミング制御回路21内のレジスタに値を設定することができる。

### [0036]

EEPROM24は、タイミング制御回路21内のレジスタに設定すべき初期値を記憶している。タイミング制御回路21は、EEPROM24との間でシリアル通信を行うために2個の端子ROMCK、ROMDIOを有する。電源投入時に、タイミング制御回路21は、これらの端子を用いてEEPROM24に記憶された初期値を読み出し、読み出した初期値を内部のレジスタに設定する。EEPROM24に記憶された初期値は、端子

10

20

30

40

S E R C K 、 S E R D I O にクロックとデータを与えることにより書き換え可能である。 【 0 0 3 7 】

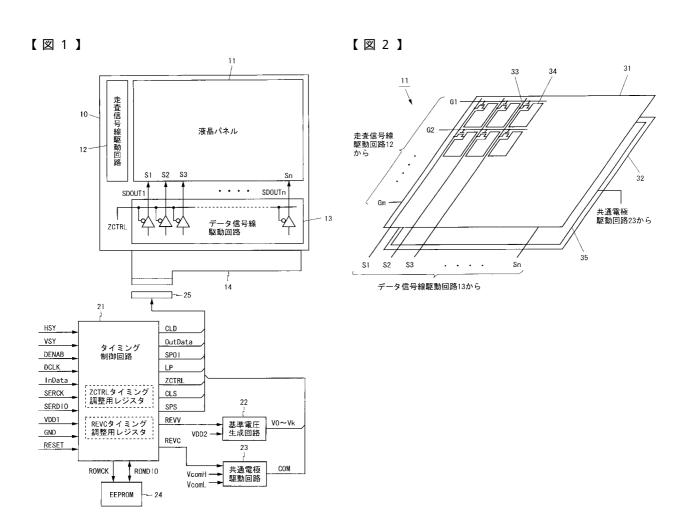

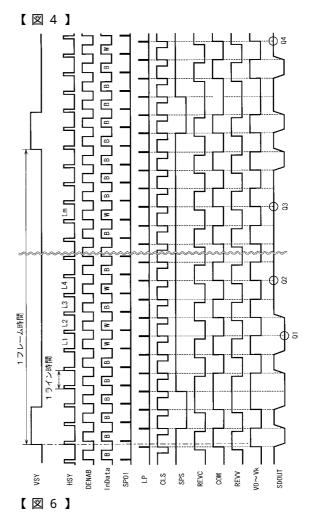

図3は、図1に示す液晶表示装置のタイミングチャートである。ここでは、液晶パネル11はノーマリーホワイト型であるとし、1フレーム時間は奇数個のライン時間に等しいとする。図3において、文字Bは1ライン時間に亘って表示データInDataが黒レベルであることを表し、文字Wは1ライン時間に亘って表示データInDataが白レベルであることを表す。なお、1フレーム時間が偶数個のライン時間に等しい場合のタイミングチャートは、図4に示すようになる。

### [0038]

図3に示すように、垂直同期信号 V S Y は、1 フレーム時間のうち 2 ライン時間だけハイレベルになる。水平同期信号 H S Y は、1 ライン時間の一部でハイレベルになる。データイネーブル信号 D E N A B は、1 ライン時間のうち水平同期信号 H S Y がローレベルである期間の一部でハイレベルになる。データイネーブル信号 D E N A B がハイレベルである間に、有効な表示データ I n D a t a が入力される。

### [0039]

タイミング制御回路 2 1 は、データイネーブル信号 D E N A B が立ち上がると、ハイレベルのデータ側スタートパルス S P O I を出力する。その後、タイミング制御回路 2 1 は、サンプリングクロック C L D に同期して 1 ライン分の表示データ O u t D a t a を順に出力する。データ信号線駆動回路 1 3 は、タイミング制御回路 2 1 から出力された 1 ライン分の表示データを内部メモリ(詳細は後述)に蓄積する。

#### [0040]

タイミング制御回路21は、1ライン分の表示データOutDataを出力するたびに、第1および第2の極性制御信号REVV、REVCを逆のレベルに(ハイレベルならばローレベルに、ローレベルならばハイレベルに)切り替える。第1の極性制御信号REVVが変化してから数μs後に、第1の極性制御信号REVVで指定された極性の基準電圧V0~Vkが基準電圧生成回路22から出力される。また、第2の極性制御信号REVCが変化してから数μs後に、第2の極性制御信号REVCで指定された極性の共通電極電圧COMが共通電極駆動回路23から出力される。

### [0041]

タイミング制御回路 2 1 は、第 1 および第 2 の極性制御信号 R E V V 、 R E V C を逆のレベルに切り替えた後に、ハイレベルのラッチパルス L P を出力する。データ信号線駆動回路 1 3 は、ハイレベルのラッチパルス L P を受け取ると、基準電圧生成回路 2 2 から供給された基準電圧 V 0 ~ V k に基づき、内部メモリに蓄積された表示データに応じた電圧を生成し、データ出力端子 S D O U T n から出力する。出力された電圧は、データ信号線 S 1 ~ S n に印加される。このようにデータ信号線駆動回路 1 3 は、タイミング制御回路 2 1 から出力されたラッチパルス L P に従い、データ信号線 S 1 ~ S n に印加する電圧を変化させる。

### [0042]

タイミング制御回路21は、ハイレベルのラッチパルスLPを出力した後、所定時間だけハイレベルとなるシフトクロックCLSを出力する。走査信号線駆動回路12は、シフトクロックCLSの立ち上がりで走査信号線G1~Gmの選択を切り替え、シフトクロックCLSがハイレベルである間、選択した走査信号線に選択電圧を印加する。これにより、選択電圧が印加された走査信号線に接続されたn個のTFT33が導通状態になり、導通状態のTFT33を介してn個の画素電極34にデータ信号線S1~Snの電圧が書き込まれる。

### [0043]

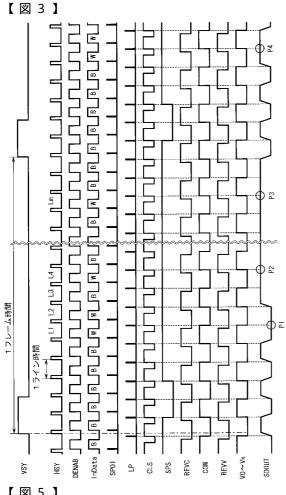

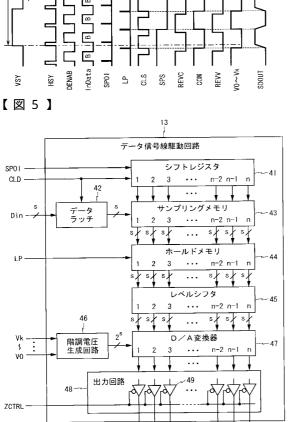

図 5 は、データ信号線駆動回路 1 3 の詳細を示すブロック図である。データ信号線駆動回路 1 3 は、図 3 に示すように、シフトレジスタ 4 1、データラッチ 4 2、サンプリングメモリ 4 3、ホールドメモリ 4 4、レベルシフタ 4 5、階調電圧生成回路 4 6、 D / A 変換器 4 7、および、出力回路 4 8 を含んでいる。

10

20

30

40

20

30

40

50

### [0044]

データ信号線駆動回路13には、タイミング制御回路21から出力されたサンプリングクロックCLD、表示データOutData、データ側スタートパルスSPOI、ラッチパルスLPおよび出力制御信号ZCTRL、並びに、基準電圧生成回路22から出力された基準電圧V0~Vkが入力される。以下、データ信号線駆動回路13に入力される表示データOutDataをDinといい、表示データDinの幅をsビットとする。

#### [0045]

シフトレジスタ41は、n段のシフトレジスタであり、サンプリングクロックCLDに従いデータ側スタートパルスSPOIを順にシフトする。シフトレジスタ41の出力信号は、表示データDinのサンプリング位置を定める。データラッチ42は、サンプリングクロックCLDに従い表示データDinを一時的にラッチし、ラッチしたデータをサンプリングメモリ43に対して出力する。

#### [0046]

サンプリングメモリ 4 3 とホールドメモリ 4 4 は、 s ビットのデータを n 個記憶する。サンプリングメモリ 4 3 は、データラッチ 4 2 にラッチされたデータを、シフトレジスタ 4 1 の出力信号によって指定された位置にサンプリングする。ホールドメモリ 4 4 は、ラッチパルス L P の立ち上がりで、サンプリングメモリ 4 3 に記憶された n 個のデータを一括してラッチする。

### [ 0 0 4 7 ]

レベルシフタ45は、ホールドメモリ44に記憶されたn個のデータについて電圧レベル変換を行う。階調電圧生成回路46は、抵抗分割回路を含み、これを用いて基準電圧V0~Vkに基づき、 補正された2<sup>s</sup> レベルの階調電圧を生成する。D/A変換器47は、レベルシフタ45から出力されたn個のデータ(幅はsビット)のそれぞれについて、階調電圧生成回路46で生成された2<sup>s</sup> レベルの階調電圧のうちから1つの階調電圧を選択する。これにより、レベルシフタ45の出力信号はアナログ信号に変換される。

### [0048]

出力回路48は、オペアンプ(図示せず)と出力バッファ49で構成されたボルテージフォロワをn個含んでいる。出力バッファ49の入力端子はオペアンプの出力端子に接続され、出力バッファ49の制御端子には出力制御信号 ZCTRLが与えられる。出力バッファ49の出力端子は、データ信号線駆動回路13の出力端子SDOUT1~SDOUTnに接続される。

### [0049]

出力制御信号 Z C T R L がローレベルのときには、出力バッファ49は入力信号をそのまま出力する。この場合、出力端子 S D O U T 1~ S D O U T n から表示データ D i n に応じた電圧(D / A 変換器 4 7 の出力電圧)が出力され、出力された電圧はデータ信号線 S 1~ S n に印加される。これに対して、出力制御信号 Z C T R L がハイレベルのときには、出力バッファ 4 9 の出力端子とデータ信号線 S 1~ S n はハイインピーダンス状態になる。

### [0050]

このようにデータ信号線駆動回路13は、タイミング制御回路21から出力された出力制御信号ZCTRLに従い、データ信号線S1~Snに対して表示データに応じた電圧を印加するか、データ信号線S1~Snをハイインピーダンス状態に設定するかを切り替える。したがって、タイミング制御回路21が好適なタイミングで出力制御信号ZCTRLをハイレベルにすれば、データ信号線駆動回路13は共通電極電圧COMが変化するタイミングに合わせてデータ信号線S1~Snをハイインピーダンス状態に設定することができる。

#### [0051]

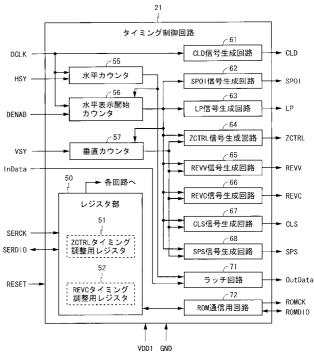

図 6 は、タイミング制御回路 2 1 の詳細を示すブロック図である。タイミング制御回路 2 1 は、レジスタ部 5 0、水平カウンタ 5 5、水平表示開始カウンタ 5 6、垂直カウンタ 5 7、各種の信号生成回路 6 1 ~ 6 8、ラッチ回路 7 1、および、R O M 通信用回路 7 2

を含んでいる。

### [0052]

レジスタ部 5 0 は、液晶パネル 1 1 の駆動に必要な値を記憶する複数のレジスタ(一部を図示)を含んでいる。特に、レジスタ部 5 0 は、出力制御信号 Z C T R L および第 2 の極性制御信号 R E V C が変化するタイミングを調整するために、 Z C T R L タイミング調整用レジスタ 5 1、および、 R E V C タイミング調整用レジスタ 5 2 を含んでいる。これ以外にも、レジスタ部 5 0 は、ラッチパルス L P や第 1 の極性制御信号 R E V V などが変化するタイミングを調整するためのレジスタを含んでいてもよい。

### [0053]

水平カウンタ55は、水平同期信号HSYの立ち下がりでカウント値をリセットし、データクロックDCLKの立ち下がりでカウント値を更新するカウンタである。水平表示開始カウンタ56は、データイネーブル信号DENABの立ち上がりでカウント値をリセットし、データクロックDCLKの立ち下がりでカウント値を更新するカウンタである。水平表示開始カウンタ56は、水平カウンタ55のカウント値がレジスタ部50内のあるレジスタ(図示せず)に設定された値に等しくなったときに、カウント値をリセットしてもよい。

### [0054]

垂直カウンタ57は、垂直同期信号VSYの立ち下がりでカウント値をリセットし、1ライン時間ごとにカウント値を更新するカウンタである。垂直カウンタ57のカウント値は、水平表示開始カウンタ56のカウント値がレジスタ部50内のあるレジスタ(図示せず)に設定された値に等しくなったときに更新される。

#### [0055]

CLD信号生成回路61は、外部から供給されたデータクロックDCLKをバッファリングし、データ信号線駆動回路13に対してサンプリングクロックCLDとして出力する。液晶パネル11の駆動に用いられる制御信号は、すべて、サンプリングクロックCLDの立ち下がりに同期して出力される。SPOI信号生成回路62は、水平表示開始カウンタ56のカウント値が所定値になったときに、ハイレベルのデータ側スタートパルスSPOIを出力する。同様に、LP信号生成回路63は、水平表示開始カウンタ56のカウント値に基づき、ラッチパルスLPを生成する。

### [0056]

ZCTRL信号生成回路64は、水平表示開始カウンタ56のカウント値と垂直カウンタ57のカウント値が所定の条件を満たしているときには、出力制御信号 ZCTRLをハイレベルにし、それ以外のときには出力制御信号 ZCTRLをローレベルにする。同様に、REVV信号生成回路65、REVC信号生成回路66、CLS信号生成回路67およびSPS信号生成回路68は、水平表示開始カウンタ56と垂直カウンタ57のカウント値に基づき、それぞれ、第1の極性制御信号 REVV、第2の極性制御信号 REVC、シフトクロック CLSおよび走査側スタートパルスSPSを生成する。

### [0057]

ラッチ回路71は、外部から供給された表示データInDataをラッチし、データ信号線駆動回路13に対して表示データOutDataとして出力する。この際、ラッチ回路71は、表示データInDataを内部メモリ(図示せず)に一旦蓄積し、所定時間だけ遅延させてから出力してもよい。ラッチ回路71は、表示データInDataが有効でない期間では表示データOutDataを白データや黒データなどに固定する処理(出力マスク処理)を行う。ROM通信用回路72は、EEPROM24との間でシリアル通信を行うための回路である。

### [0058]

なお、タイミング制御回路 2 1 の入出力信号の極性は、図 3 に示した以外でもよい。例えば、水平同期信号 H S Y と垂直同期信号 V S Y がハイアクティブ(ハイレベル時に有効)である場合には、水平カウンタ 5 5 は水平同期信号 H S Y の立ち上がりでカウント値をリセットし、垂直カウンタ 5 7 は垂直同期信号 V S Y の立ち上がりでカウント値をリセッ

10

20

30

40

20

30

40

50

トする。

### [0059]

信号生成回路61~68の中には、レジスタ部50内のレジスタに設定された値に応じて、出力信号が変化するタイミングを切り替える機能を有するものがある。具体的には、 ZCTRL信号生成回路64は、ZCTRLタイミング調整用レジスタ51に設定された値に応じて、出力制御信号ZCTRLが変化するタイミングを切り替える。REVC信号 生成回路66は、REVCタイミング調整用レジスタ52に設定された値に応じて、第2 の極性制御信号REVCが変化するタイミングを切り替える。

### [0060]

例えば、REVCタイミング調整用レジスタ52に設定された値が+3のときには、REVC信号生成回路66は、標準的なタイミングよりもサンプリングクロックCLDの3周期分だけ遅いタイミングで第2の極性制御信号REVCを変化させる。また、REVCタイミング調整用レジスタ52に設定された値が-2のときには、REVC信号生成回路66は、標準的なタイミングよりもサンプリングクロックCLDの2周期分だけ早いタイミングで第2の極性制御信号REVCを変化させる。

#### [0061]

このようにタイミング制御回路 2 1 は、外部から値を設定可能なレジスタを含み、レジスタに設定された値に応じて、出力制御信号 Z C T R L および第 2 の極性制御信号 R E V C が変化するタイミングを切り替える。したがて、データ信号線駆動回路 1 3 は、共通電極 3 5 の電圧が変化するタイミングに合わせてデータ信号線 S 1 ~ S n をハイインピーダンス状態に設定することができる。

### [0062]

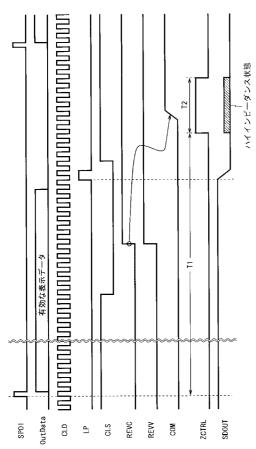

図7は、図1に示す液晶表示装置の1ライン時間分のタイミングチャートである。図7に示すように、タイミング制御回路21は、1ライン分の表示データOutDataを出力した後に、ハイレベルのラッチパルスLPを出力する。タイミング制御回路21は、ラッチパルスLPを出力するより前に、第1および第2の極性制御信号REVV、REVCを逆のレベルに切り替える。共通電極電圧COMは、第2の極性制御信号REVCが変化してから数μs後に変化する。

### [0063]

タイミング制御回路 2 1 は、通常時は出力制御信号 Z C T R L をローレベルにし、共通電極電圧 C O M が変化するときを含む所定の期間 T 2 では出力制御信号 Z C T R L をハイレベルにする。出力制御信号 Z C T R L がハイレベルである間、データ信号線駆動回路 1 3 の出力端子 S D O U T 1 ~ S D O U T n はハイインピーダンス状態になり、データ信号線 S 1 ~ S n もハイインピーダンス状態になる。

### [0064]

共通電極電圧COMが変化するタイミングに合わせて出力制御信号ZCTRLをハイレベルにするためには、ZCTRLタイミング調整用レジスタ51とREVCタイミング調整用レジスタ52に好適な値を設定すればよい。例えば、ZCTRLタイミング調整用レジスタ51には、データ側スタートパルスSPOIの立ち上がりから出力制御信号ZCTRLがハイレベルである 用間T2の長さとが設定される。期間T1、T2の長さを好適に設定することにより、共通電極電圧COMが変化するタイミングに合わせて出力制御信号ZCTRLをハイレベルにすることができる。

### [0065]

共通電極を交流駆動する従来の液晶表示装置では、共通電極電圧が変化したときの突き上げや突き下げによってデータ信号線電圧が一時的にデータ信号線駆動回路の耐圧電圧を超え、データ信号線駆動回路が破壊されることがある。例えば、図3のP1~P4付近や図4のQ1~Q4付近では、データ信号線駆動回路が破壊される可能性がある。これに対して、本実施形態に係る液晶表示装置では、共通電極電圧COMが変化するタイミングに合わせてデータ信号線Sjをハイインピーダンス状態に設定することにより、共通電極電

20

30

40

50

圧 C O M が変化したときの突き上げや突き下げによるデータ信号線 S 1 ~ S n の電圧の変化を防止し、データ信号線駆動回路 1 3 の破壊を防止することができる。

### [0066]

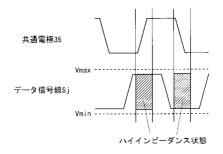

図8は、従来の液晶表示装置の共通電極とデータ信号線の電圧波形を示す図であり、図9は、本実施形態に係る液晶表示装置の共通電極35とデータ信号線Sjの電圧波形を示す図である。図8と図9では、共通電極とデータ信号線の電圧が変化するタイミングは同じである。以下、データ信号線駆動回路の耐圧電圧の最大値をVmax、最小値をVminとする。

### [0067]

従来の液晶表示装置(図8を参照)では、データ信号線の電圧が高い間に共通電極の電圧が上昇すると、データ信号線の電圧は突き上げによって一時的に高くなる。この際、データ信号線の電圧が最大耐圧電圧Vmaxより高くなると、データ信号線駆動回路は破壊される。また、データ信号線の電圧が低い間に共通電極の電圧が下降すると、データ信号線の電圧は突き下げによって一時的に低くなる。この際、データ信号線の電圧が最小耐圧電圧Vminより低くなると、データ信号線駆動回路は破壊される。なお、共通電極の電圧振幅が大きく、データ信号線駆動回路の出力段トランジスタのオン抵抗が高いほど、突き上げや突き下げによるデータ信号線の電圧の変化量は大きくなる。

#### [0068]

これに対して、本実施形態に係る液晶表示装置(図9を参照)では、共通電極電圧COMが変化するときを含む期間T2では、データ信号線Sjはハイインピーダンス状態に設定される。このため、共通電極電圧COMが変化しても、その影響を受けてデータ信号線Sjの電圧が変化することはない。したがって、共通電極電圧COMが変化したときの突き上げや突き下げによるデータ信号線Sjの電圧の変化を抑え、データ信号線駆動回路13の破壊を効果的に防止することができる。

### [0069]

また、データ信号線駆動回路13は、タイミング制御回路21から出力された出力制御信号ZCTRLに従い、データ信号線S1~Snをハイインピーダンス状態に設定する。したがって、データ信号線S1~Snをハイインピーダンス状態に設定するタイミングをタイミング制御回路21で調整して、共通電極電圧COMの変化に起因するデータ信号線駆動回路13の破壊を防止することができる。

### [0070]

また、共通電極駆動回路 2 3 は、タイミング制御回路 2 1 から出力された第 2 の極性制御信号 R E V C に従い共通電極電圧 C O M を変化させ、タイミング制御回路 2 1 は、第 2 の極性制御信号 R E V C が変化するタイミングに応じたタイミングで出力制御信号 Z C T R L を変化させる。したがって、共通電極電圧 C O M の変化タイミングに合わせてデータ信号線 S 1 ~ S j をハイインピーダンス状態に設定し、共通電極電圧 C O M の変化に起因するデータ信号線駆動回路 1 3 の破壊を防止することができる。

### [0071]

また、タイミング制御回路 2 1 は、外部から値を設定可能な Z C T R L タイミング調整 用レジスタ 5 1 と R E V C タイミング調整用レジスタ 5 2 を含み、これらのレジスタに設定された値に応じて、第 2 の極性制御信号 R E V C と出力制御信号 Z C T R L が変化するタイミングを切り替える。したがって、共通電極電圧 C O M の変化タイミングとデータ信号線 S 1 ~ S n のハイインピーダンス期間を好適に調整し、共通電極電圧 C O M の変化に起因するデータ信号線駆動回路 1 3 の破壊を防止することができる。

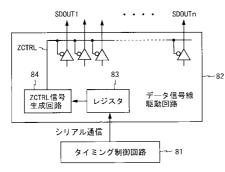

### [ 0 0 7 2 ]

なお、本実施形態に係る液晶表示装置については、図10に示す変形例を構成することができる。図10は、本発明の実施形態の変形例に係る液晶表示装置の主要部を示す図である。図10に示すデータ信号線駆動回路82は、レジスタ83とZCTRL信号生成回路84を含んでいる。タイミング制御回路81は、データ信号線駆動回路82との間でシリアル通信を行い、第2の極性制御信号REVVが変化するタイミングに応じた値をレジ

スタ83に設定する。 Z C T R L 信号生成回路85は、レジスタ83に設定された値に応じたタイミングで出力制御信号 Z C T R L を変化させる。出力制御信号 Z C T R L は、データ信号線S1~Snに表示データに応じた電圧を印加するか、データ信号線S1~Snをハイインピーダンス状態に設定するかを切り替えるために使用される。

[ 0 0 7 3 ]

このようにデータ信号線駆動回路82は、外部から値を設定可能なレジスタ83を含み、レジスタ83に設定された値に応じて、データ信号線S1~Snをハイインピーダンス状態に設定するタイミングを切り替える。図10に示す液晶表示装置でも、図1に示す液晶表示装置と同様に、データ信号線S1~Snをハイインピーダンス状態に設定するタイミングをタイミング制御回路81で調整し、共通電極電圧COMの変化に起因するデータ信号線駆動回路82の破壊を防止することができる。

[0074]

以上に示すように、本発明の液晶表示装置によれば、共通電極電圧の変化タイミングに合わせてデータ信号線をハイインピーダンス状態に設定することにより、共通電極電圧が変化したときの突き上げや突き下げによるデータ信号線電圧の変化を抑え、データ信号線駆動回路の破壊を効果的に防止することができる。

【図面の簡単な説明】

- [0075]

- 【図1】本発明の実施形態に係る液晶表示装置の構成を示すブロック図である。

- 【図2】図1に示す液晶表示装置の液晶パネルの構造を示す図である。

- 【図3】図1に示す液晶表示装置のタイミングチャートである。

- 【図4】図1に示す液晶表示装置の別のタイミングチャートである。

- 【図5】図1に示す液晶表示装置のデータ信号線駆動回路の詳細を示すブロック図である

- 【図6】図1に示す液晶表示装置のタイミング制御回路の詳細を示すブロック図である。

- 【図7】図1に示す液晶表示装置の1ライン時間分のタイミングチャートである。

- 【図8】従来の液晶表示装置の共通電極とデータ信号線の電圧波形を示す図である。

- 【図9】図1に示す液晶表示装置の共通電極とデータ信号線の電圧波形を示す図である。

- 【図10】本発明の実施形態の変形例に係る液晶表示装置の主要部を示すブロック図である。

- 【 図 1 1 】液晶パネルとデータ信号線駆動回路の一部を示す図である。

- 【図12】共通電極とデータ信号線の電圧波形(突き上げなどが発生する場合)を示す図である。

【符号の説明】

- [0076]

- 10...パネル基板

- 1 1 ... 液晶パネル

- 1 2 ... 走 査 信 号 線 駆 動 回 路

- 1 3 ... データ信号線駆動回路

- 1 4 ... フレキシブル回路基板

- 2 1 ... タイミング制御回路

- 2 2 ... 基準電圧生成回路

- 2 3 ... 共通電極駆動回路

- 2 4 ... E E P R O M

- 25…コネクタ

- 3 1 、 3 2 … ガラス基板

- 3 3 ... T F T

- 3 4 ... 画素電極

- 3 5 ... 共通電極

- 4 9 ... 出力バッファ

30

20

10

40

5 1 ... Z C T R L タイミング調整用レジスタ

5 2 ... R E V C タイミング調整用レジスタ

6 4 、 8 5 ... Z C T R L 信号生成回路

6 6 ... R E V C 信号生成回路

VDD1 VDD2 GND

SDOUT1

SD0UTn

## 【図7】

## 【図8】

### 【図9】

### 【図10】

### 【図12】

### 【図11】

# フロントページの続き

(51) Int.CI.

F I

G 0 9 G 3/20 6 2 4 D G 0 9 G 3/20 6 7 0 Z G 0 2 F 1/133 5 5 0

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|--|

| 公开(公告)号        | <u>JP2009103948A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2009-05-14 |  |  |  |  |

| 申请号            | JP2007276002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2007-10-24 |  |  |  |  |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |  |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |  |

| [标]发明人         | 劉憲太郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |  |

| 发明人            | 劉 憲太郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |  |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |  |  |  |  |

| FI分类号          | G09G3/36 G09G3/20.623.D G09G3/20.621.A G09G3/20.612.L G09G3/20.621.B G09G3/20.624.D G09G3/20.670.Z G02F1/133.550                                                                                                                                                                                                                                                                                                                                                                                       |         |            |  |  |  |  |

| F-TERM分类号      | 2H093/NA16 2H093/NA31 2H093/NA43 2H093/NC02 2H093/NC09 2H093/NC11 2H093/NC16 2H093 /NC22 2H093/NC23 2H093/NC26 2H093/NC34 2H093/NC35 2H093/ND47 5C006/AC21 5C006/AC27 5C006/AF42 5C006/AF71 5C006/BB16 5C006/BC12 5C006/BF25 5C006/BF50 5C006/FA16 5C080 /AA10 5C080/BB05 5C080/DD19 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 2H193/ZA04 2H193/ZB07 2H193/ZC04 2H193/ZD01 2H193/ZF02 2H193/ZF04 2H193/ZF05 2H193 /ZF13 2H193/ZF34 2H193/ZF35 2H193/ZF43 2H193/ZF59 2H193/ZH38 2H193/ZH52 |         |            |  |  |  |  |

| 代理人(译)         | 岛田彰                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |  |  |  |  |

### 摘要(译)

为了防止由公共电极电压的变化引起的数据信号线驱动电路的破坏。 公共电极驱动电路根据极性控制信号REVC改变施加到液晶面板的公共电极的电压。定时控制电路21根据极性控制信号REVC改变的定时改变输出控制信号ZCTRL。数据信号线驱动电路13根据输出控制信号ZCTRL将数据信号线Sj设置为高阻抗状态。根据公共电极电压COM的变化时序将数据信号线Sj设置为高阻抗状态,以便抑制当公共电极电压变化时由于推进和推动引起的数据信号线电压的变化,13防止破坏。 点域1