(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-203675

(P2008-203675A)

(43) 公開日 平成20年9月4日(2008.9.4)

(51) Int.Cl.

G02F 1/1343 (2006.01)

F 1

G02F 1/1343

テーマコード(参考)

2 H092

審査請求 未請求 請求項の数 4 O L (全 12 頁)

(21) 出願番号

特願2007-41451 (P2007-41451)

(22) 出願日

平成19年2月21日 (2007.2.21)

(71) 出願人 304053854

エプソンイメージングデバイス株式会社

長野県安曇野市豊科田沢6925

(74) 代理人 100075258

弁理士 吉田 研二

(74) 代理人 100096976

弁理士 石田 純

(72) 発明者 矢田 龍也

長野県安曇野市豊科田沢6925 エプソ

ンイメージングデバイス株式会社内

(72) 発明者 山村 久仁

長野県安曇野市豊科田沢6925 エプソ

ンイメージングデバイス株式会社内

F ターム(参考) 2H092 GA14 JB51 NA01 PA02 PA09

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】画素電極と共に電極とが絶縁膜を介して積層された構成を有する液晶表示装置について良好な表示品位を得ることである。

【解決手段】一対の基板に液晶層を挟持した液晶表示装置10は、複数本の画素列50と、複数本の画素列50中の各画素20を駆動する駆動回路と、を含む。各画素20は、一対の基板の一方の基板に設けられ、絶縁膜を介して積層された画素電極と共に電極と、画素電極および共通電極よりも液晶層側に配置され複数本の画素列50に略平行にラビングされた配向膜と、を有する。駆動回路は、各画素20の画素電極と共に電極との間に、複数本の画素列50を連続するn本(nは2以上の整数)ごとに分けた各プロックBL内では互いに同極性となり、かつ、隣接するプロック間では互いに逆極性となる電圧を印加する。

【選択図】図5

## 【特許請求の範囲】

## 【請求項 1】

一对の基板に液晶層を挟持した液晶表示装置において、複数本の画素列と、前記複数本の画素列中の各画素を駆動する駆動回路と、を備え、

前記各画素は、

前記一对の基板の一方の基板に設けられ、絶縁膜を介して積層された画素電極と共に電極と、

前記画素電極および前記共通電極よりも液晶層側に配置され前記複数本の画素列に略平行にラビングされた配向膜と、を含み、

前記駆動回路は、前記各画素の前記画素電極と前記共通電極との間に、前記複数本の画素列を連続する  $n$  本 ( $n$  は 2 以上の整数) ごとに分けた各ブロック内では互いに同極性となり、かつ、隣接する前記ブロック間では互いに逆極性となる電圧を印加することを特徴とする液晶表示装置。

## 【請求項 2】

請求項 1 に記載の液晶表示装置であって、

前記  $n$  の値が連続する 1 フレーム期間で互いに異なることを特徴とする液晶表示装置。

## 【請求項 3】

一对の基板に液晶層を挟持した液晶表示装置において、 $m$  本 ( $m$  は 3 以上の整数) の画素列と、前記  $m$  本の画素列中の各画素を駆動する駆動回路と、を備え、

前記各画素は、

前記一对の基板の一方の基板に設けられ、絶縁膜を介して積層された画素電極と共に電極と、

前記画素電極および前記共通電極よりも液晶層側に配置され前記複数本の画素列に略平行にラビングされた配向膜と、を含み、

前記駆動回路は、前記各画素の前記画素電極と前記共通電極との間に、前記  $m$  本の画素列を 2 個以上かつ ( $m - 1$ ) 個以下に分けた各ブロック内では互いに同極性となり、かつ、隣接する前記ブロック間では互いに逆極性となる電位を印加することを特徴とする液晶表示装置。

## 【請求項 4】

請求項 3 に記載の液晶表示装置であって、

前記ブロックの個数が連続する 1 フレーム期間で互いに異なることを特徴とする液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、液晶表示装置に係り、特に画素電極と共に電極とが絶縁膜を介して積層された構成を有する液晶表示装置に関する。

## 【背景技術】

## 【0002】

F F S (Fringe Field Switching) 方式の液晶表示装置では、液晶の配向を制御する画素電極と共に電極との両方が同じ基板に設けられており、この 2 つの電極は絶縁膜を介して積層されている。当該電極のうちで上側の電極すなわち液晶層側の電極にはスリットが設けられている。スリットの長手方向 (長辺方向) と略平行にラビング処理がなされ、上記電極間の電圧がオフ電圧の場合、液晶分子はスリットの長手方向と略平行に配向する

10

20

30

40

50

(初期配向状態)。オフ電圧よりも高い電圧を上記電極間に印加した場合、当該電極間にスリットを通じて電界が生じる。この電界はスリットの長辺に対して垂直な方向に発生し、液晶分子は当該電界方向に沿うように基板に平行な面内で回転する。液晶分子の回転角を制御することによって、透過光量が制御される。

【0003】

【特許文献1】特開平11-202356号公報

【特許文献2】特開2003-57670号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

画素電極が上電極の場合、スリットを通じて電界の他に、隣接する画素電極間にわたる電界が発生しうる。隣接画素電極間の電界がラビング方向と交差する領域では、液晶分子が初期配向状態からずれるので、当該領域の透過率が高くなり、光漏れが発生してしまう。

【0005】

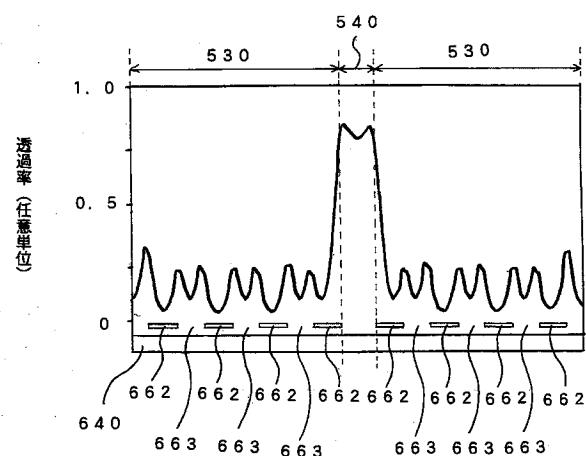

図9に上記光漏れの様子を説明する図を示す。図9は、画素電極のスリット部663とスリット部663を挟んで並ぶ枝部662とを横切る断面、すなわちラビング方向を横切る断面について、透過率をシミュレーションした図である。なお、画素電極は不図示の絶縁膜を介して共通電極640と積層されている。図9には、隣接画素電極間領域540と当該領域540を挟んで並ぶ2つの画素電極領域530とを図示し、画素電極領域530の階調レベルが約20%の場合を例示している。

【0006】

図9によれば、画素電極領域530での透過率に比べて、隣接画素電極間領域540での透過率が高くなる場合があることが分かる。この場合、画素電極領域530よりも隣接画素電極間領域540の方が輝度が高くなり、例えばコントラスト等が低下して表示品位が低下するという問題がある。

【0007】

一般に、隣接画素電極間の距離が短いほど、隣接画素電極間の電界は強くなる。このため、高精細化が進むほど、隣接画素電極間領域540での光漏れが発生しやすい。

【0008】

また、隣接画素電極間領域540の液晶分子は、両側の画素電極の電位変動の影響を受けるので、配向状態が不安定である。このため、隣接画素電極間領域540での光漏れは、フリッカーのようにちらつき、強調されて見える傾向にある。この点においても、表示品位が低下するという問題がある。

【0009】

上記の光漏れおよびちらつきは、例えばライン反転駆動のように隣接画素電極間の電圧が大きくなる場合に、発生しやすくなる。

【0010】

ここで、上記光漏れを防止する対策として、隣接画素電極間領域540を遮光膜によって遮光することが考えられる。しかし、上記ちらつきを抑制するためには、隣接画素電極間領域540から斜め方向へ出射する光を含めて遮光する必要がある。このため、遮光膜の拡大を招くことになる。一般に、FFS方式の構造では画素電極と共通電極との積層構造によって保持容量が形成されるので、保持容量が別個に設けられた構造に比べて開口率が高いという特長がある。上記の遮光膜の拡大はFFSの特長を低減する可能性がある。

【0011】

また、上記ちらつきを防止する対策として、画素電極への印加電圧を下げるこによって隣接画素電極間の電圧を低下させることが考えられる。しかし、この対策では、画素電極領域530の透過率が低下してしまい、表示品位上、好ましくない場合がある。

【0012】

また、上記ちらつきを防止する他の対策として、フレーム反転駆動によって隣接画素電

10

20

30

40

50

極間の電圧を低下させることが考えられる。しかし、この対策では、画面全体でのちらつきが発生する場合があり、これを抑制するために駆動周波数を高くする必要が生じる。

【0013】

本発明の目的は、画素電極と共に電極とが絶縁膜を介して積層された構成を有する液晶表示装置であって良好な表示品位を得ることが可能な液晶表示装置を提供することである。

【課題を解決するための手段】

【0014】

本発明に係る液晶表示装置は、一対の基板に液晶層を挟持した液晶表示装置において、複数本の画素列と、前記複数本の画素列中の各画素を駆動する駆動回路と、を備え、前記各画素は、前記一対の基板の一方の基板に設けられ、絶縁膜を介して積層された画素電極と共に電極と、前記画素電極および前記共通電極よりも液晶層側に配置され前記複数本の画素列に略平行にラビングされた配向膜と、を含み、前記駆動回路は、前記各画素の前記画素電極と前記共通電極との間に、前記複数本の画素列を連続する  $n$  本 ( $n$  は 2 以上の整数) ごとに分けた各ブロック内では互いに同極性となり、かつ、隣接する前記ブロック間では互いに逆極性となる電圧を印加することを特徴とする。一般に、隣接する画素で画素電極と共に電極との間の電圧が互いに逆極性になる場合、同極性の場合に比べて、当該隣接画素の画素電極間の電圧が高くなる。しかし、上記構成によれば、互いに逆極性の電圧が印加される隣接画素の数が削減される。このため、隣接画素の画素電極の間の領域で発生する光漏れ等を抑制することができ、良好な表示品位が得られる。

10

20

30

【0015】

また、前記  $n$  の値が連続する 1 フレーム期間で互いに異なることが好ましい。上記構成によれば、互いに逆極性の電圧が同じ画素に継続的に印加されることが抑制される。このため、同じ位置に継続的に光り漏れ等が発生することが抑制される。したがって、良好な表示品位が得られる。

【0016】

本発明に係る液晶表示装置は、一対の基板に液晶層を挟持した液晶表示装置において、 $m$  本 ( $m$  は 3 以上の整数) の画素列と、前記  $m$  本の画素列中の各画素を駆動する駆動回路と、を備え、前記各画素は、前記一対の基板の一方の基板に設けられ、絶縁膜を介して積層された画素電極と共に電極と、前記画素電極および前記共通電極よりも液晶層側に配置され前記複数本の画素列に略平行にラビングされた配向膜と、を含み、前記駆動回路は、前記各画素の前記画素電極と前記共通電極との間に、前記  $m$  本の画素列を 2 個以上かつ ( $m - 1$ ) 個以下に分けた各ブロック内では互いに同極性となり、かつ、隣接する前記ブロック間では互いに逆極性となる電位を印加することを特徴とする。一般に、隣接する画素で画素電極と共に電極との間の電圧が互いに逆極性になる場合、同極性の場合に比べて、当該隣接画素の画素電極間の電圧が高くなる。しかし、上記構成によれば、互いに逆極性の電圧が印加される隣接画素の数が削減される。このため、隣接画素の画素電極の間の領域で発生する光漏れ等を抑制することができ、良好な表示品位が得られる。

30

【0017】

また、前記ブロックの個数が連続する 1 フレーム期間で互いに異なることが好ましい。上記構成によれば、互いに逆極性の電圧が同じ画素に継続的に印加されることが抑制される。このため、同じ位置に継続的に光り漏れ等が発生することが抑制される。したがって、良好な表示品位が得られる。

40

【発明を実施するための最良の形態】

【0018】

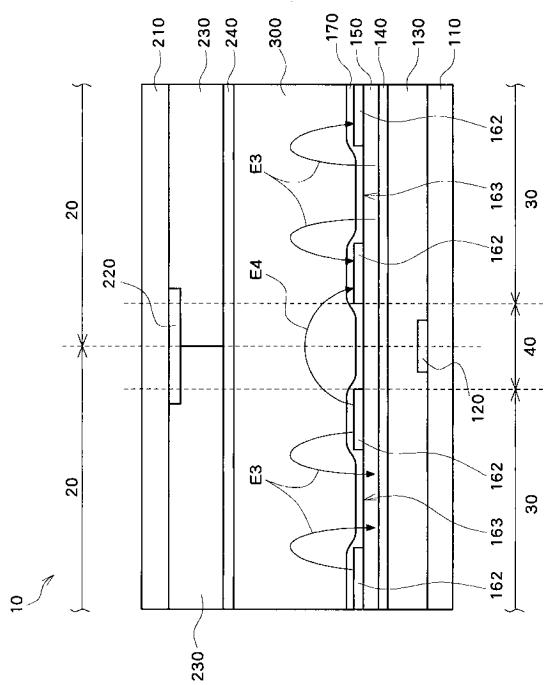

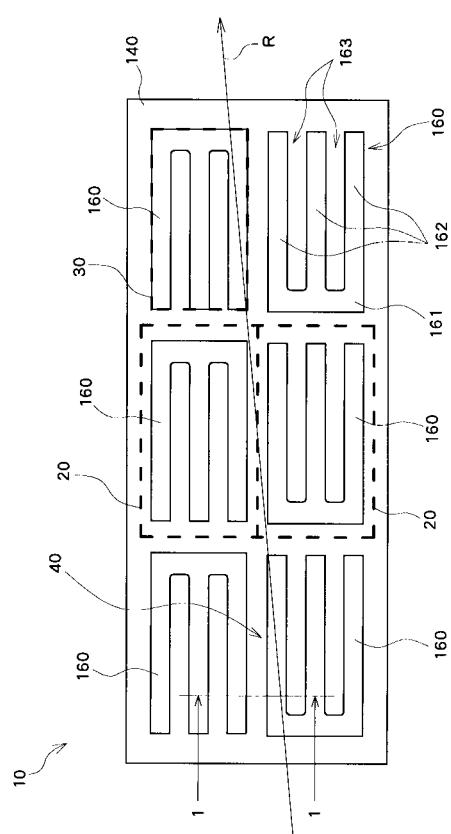

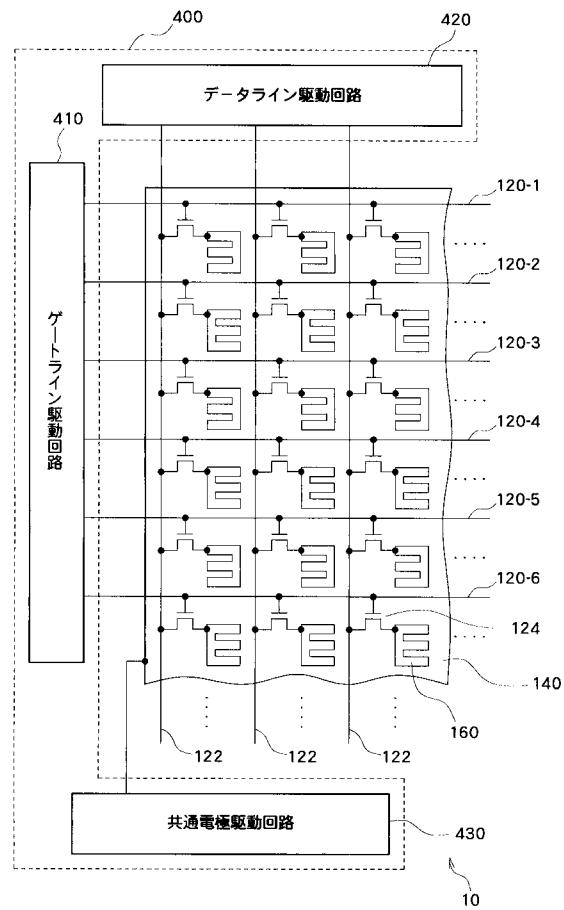

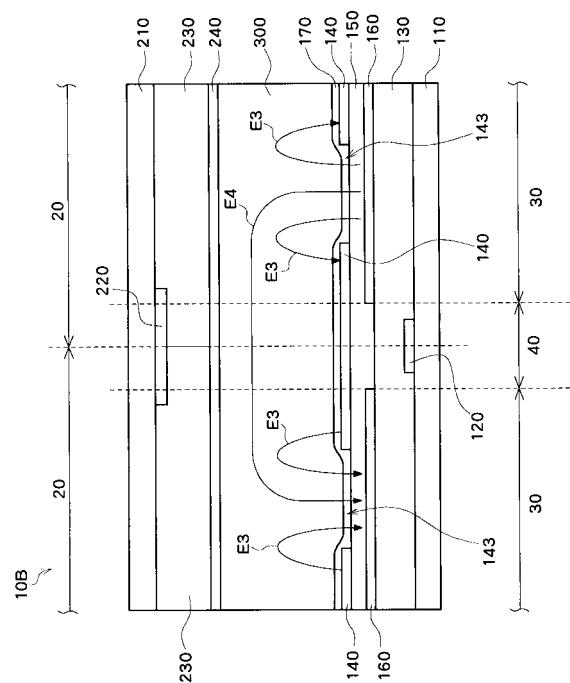

図 1 および図 2 に本発明の実施の形態に係る液晶表示装置 10 の表示領域の一部について断面図および平面図を示す。図 1 は、図 2 中の 1 - 1 線における断面図に相当する。図 2 には、2 行 3 列にマトリクス配列された画素 20 を例示しており、図面の煩雑化を避けるため 2 個の画素 20 についてのみ太い破線で例示している。なお、図 2 では図 1 中に図示した要素の一部を省略している。また、図 3 に液晶表示装置 10 の模式図を示す。

50

## 【0019】

液晶表示装置10は、対向配置された2枚の支持基板110, 210と、当該2枚の支持基板110, 210間に挟持された液晶層300とを含んでいる。支持基板110, 210は、例えばガラス板等の透光性基板で構成可能である。液晶層300の厚さは、セルギャップに対応し、例えば2~4μmである。

## 【0020】

液晶表示装置10は、支持基板110の液晶層300側に、ゲートライン120と、データライン122と、スイッチング素子124と、絶縁膜130と、共通電極140と、絶縁膜150と、画素電極160と、配向膜170とを含んでいる。

## 【0021】

ゲートライン120とデータライン122とは互いに平面視上、交差するように配置されており、図3では直交する場合を例示している。ゲートライン120とデータライン122とは絶縁膜130によって互いに絶縁されている。なお、図3に図示された6本のゲートライン120を区別する場合、表示画面の上側から順番に、1番目のゲートライン120-1、2番目のゲートライン120-2のように呼ぶことにする。

## 【0022】

ゲートライン120とデータライン122との各交差点付近にスイッチング素子124が配置されている。ここではスイッチング素子124としてトランジスタを例示するが、例えばダイオード等を用いることも可能である。各トランジスタ124は、ゲートが近接のゲートライン120に接続され、ドレイン(またはソース)が近接のデータライン122に接続されている。各トランジスタ124に対してそれぞれ画素電極160が設けられており、トランジスタ124のソース(またはドレイン)に画素電極160が接続されている。これにより、画素電極160には、データライン122からトランジスタ124を介して、その画素電極160に対応する画素20の表示データ電位が供給される。

## 【0023】

共通電極140は、絶縁膜130上に配置されている。共通電極140は、例えばITO(Indium Tin Oxide)等の透光性導電膜で構成可能である。共通電極140によって各画素20に共通の電位が供給される。ここでは、共通電極140が、全ての画素20にわたって配置された導電膜で構成される場合を例示するが、例えば、共通電極140を画素20ごとに分割し、これら複数の分割電極を配線で接続してもよい。また、例えば、全画素20を複数のグループに分け、当該グループごとに共通電極140を分割配置することも可能である。

## 【0024】

画素電極160は、絶縁膜150を介して共通電極140上に積層されている。画素電極160は、例えばITO等の透光性導電膜で構成可能である。画素電極160は、各画素20にそれぞれ設けられている。

## 【0025】

画素電極160は、1本の幹部(または背部)161と、複数の枝部(または歯部)162とを含んでいる。枝部162は、スリット部(または溝部)163を挟んで配列されており、スリット部163とともにライン・アンド・スペースのパターンを構成している。なお、枝部162とスリット部163の数は図示の例示に限られるものではない。複数の枝部162は、一端において、幹部161で繋がれている。すなわち、画素電極160は、くし歯形状をしている。なお、枝部162の幅は例えば2.5~3.5μmであり、枝部162間の間隔すなわちスリット部163の幅は例えば4.0~5.0μmである。なお、画素電極160の輪郭線の角部(コーナー部)は、角張っていてもよいし、丸まつた形状でもよい。

## 【0026】

ここでは、枝部162およびスリット部163がゲートライン120と平行に延伸する場合を例示する。なお、説明のため、この形態を図2および図3に図示した態様に合わせて「横スリット型」と呼ぶことにする。また、ここでは、データライン122に平行に並

ぶ画素電極 160 は、くし歯形状の開放端の向き、換言すれば幹部 161 の位置を交互にして配列されている場合を例示する。

【0027】

共通電極 140 は画素電極 160 のスリット部 163 だけでなく幹部 161 および枝部 162 にも対向しており、両電極 140, 160 は絶縁膜 150 を介して保持容量を構成している。

【0028】

配向膜 170 は、画素電極 160 を覆って積層されている。配向膜 170 の液晶層 300 に接する表面は、枝部 162 およびスリット部 163 の長手方向に略平行に、例えば当該長手方向に対して約 5° ~ 10° 傾いた方向にラビングされている。図 2 にはラビング方向 R の一例を矢印によって模式的に図示している。

10

【0029】

液晶表示装置 10 は、支持基板 110 の液晶層 300 とは反対側に不図示の偏光板を含んでいる。

【0030】

液晶表示装置 10 は、支持基板 210 の液晶層 300 側に、遮光膜 220 と、カラーフィルタ 230 とを含んでいる。遮光膜 220 は、例えば黒色顔料を含有した各種樹脂で構成可能である。遮光膜 220 には画素 20 ごとに、画素電極 160 に対向して開口部が形成されている。各開口部には、その画素 20 の表示色に応じた色相のカラーフィルタ 230 が配置されている。図 1 では遮光膜 220 およびカラーフィルタ 230 が支持基板 210 上に配置されている場合を例示している。

20

【0031】

液晶表示装置 10 は、カラーフィルタ 230 を覆って積層された不図示のオーバーコート層と配向膜 240 とを含んでいる。配向膜 240 の液晶層 300 に接する表面は所定方向にラビングされている。また、液晶表示装置 10 は、支持基板 210 の液晶層 300 とは反対側に不図示の偏光板を含んでいる。

【0032】

共通電極 140 と画素電極 160 との間の電圧がオフ電圧の場合、電極 140, 160 付近の液晶分子は、ラビング方向 R に配向している（初期配向状態）。オフ電圧よりも高い電圧を電極 140, 160 間に印加すると、電極 140, 160 間にスリット部 163 を通って電界 E3 が発生する。液晶分子は支持基板 110 に平行な平面内で回転する。すなわち、液晶（分子）が駆動される。液晶分子の回転角を制御することによって、透過光量が制御される。共通電極 140 と画素電極 160 とは、各画素 20 において電極対を構成し、上記電界 E3 を各画素 20 において発生する。

30

【0033】

なお、例えば上記 2 つの配向膜 170, 240 のラビング方向と上記 2 つの偏光板の偏光軸方向との関係によって、液晶表示装置 10 をノーマリ・ブラック（Normaly Black）型とノーマリ・ホワイト（Normaly White）型とのいずれにも設計可能である。ここでは、液晶表示装置 10 がノーマリ・ブラック型の場合を例示する。

40

【0034】

上記では画素 20 がマトリクス配列されている場合を例示したが（図 2 参照）、画素 20 をデルタ配列等の他配列にすることも可能である。また、ここでは、画素 20 の境界が、隣接する画素電極 160 の間の領域 40 を二分する位置である場合を例示するが（図 1 および図 2 参照）、例えば、画素電極 160 とスリット部 163 とからなる領域 30（図 1 および図 2 参照）を画素 20 と規定することも可能である。

【0035】

なお、上記の隣接する画素電極 160 の間の領域 40 を「隣接画素電極間領域 40」と呼び、上記領域 30 を「画素電極領域 30」と呼ぶことにする。図 2 では図面の煩雑化を避けるため、1 つの画素電極領域 30 についてのみ太い破線で例示している。

【0036】

50

液晶表示装置 10 は各画素 20 を駆動する駆動回路 400 を含んでおり、ここでは駆動回路 400 が、ゲートライン駆動回路 410 と、データライン駆動回路 420 と、共通電極駆動回路 430 とを含んで構成される場合を例示する（図 3 参照）。各ゲートライン 120 はゲートライン駆動回路 410 に接続され、各データライン 122 はデータライン駆動回路 420 に接続されている。共通電極 140 には共通電極駆動回路 430 が接続されている。

#### 【0037】

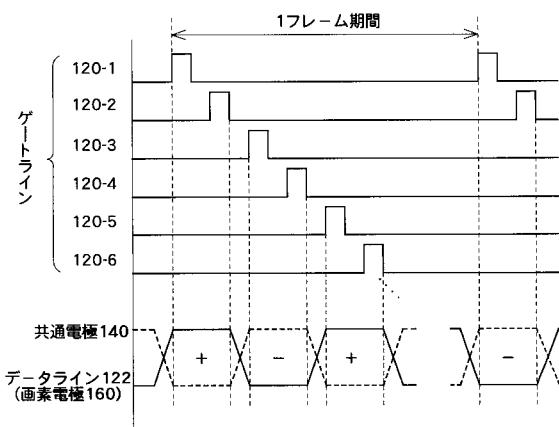

図 4 に、液晶表示装置 10 における駆動方法を説明するタイミングチャートを示す。図 4 には、ゲートライン 120 とデータライン 122 と共通電極 140 との各電位の変化を図示しており、共通電極 140 の波形を破線で図示している。なお、データライン 122 の電位変化は画素電極 160 の電位変化に対応する。

10

#### 【0038】

ゲートライン 120 には、ゲートライン駆動回路 410 によって選択信号が順次、印加される。つまり、複数本のゲートライン 120 がスキャンされる。このとき、同じゲートライン 120 に接続された複数のトランジスタ 124 には同時に選択信号が印加される。なお、上記選択信号を図 4 では矩形パルスで例示している。

#### 【0039】

共通電極 140 には、ここでは、共通電極駆動回路 430 によって 2 つの所定電位が交互に印加される。例示のタイミングチャートの場合、共通電極 140 には、1 番目のゲートライン 120 - 1 への選択信号の印加開始から 2 番目のゲートライン 120 - 2 への選択信号の印加終了までの期間は所定の低電位が印加される。その後、3 番目のゲートライン 120 - 3 への選択信号の印加開始から 4 番目のゲートライン 120 - 4 への選択信号の印加終了までの期間は所定の高電位が共通電極 140 に印加される。その後、5 番目のゲートライン 120 - 5 への選択信号の印加開始から 6 番目のゲートライン 120 - 6 への選択信号の印加終了までの期間は上記低電位が印加される。

20

#### 【0040】

つまり、ゲートライン 120 は連続する 2 本ごとにブロック分けされ、同じブロック内のゲートライン 120 が選択される期間中は共通電極 140 の電位は所定の低電位または高電位に保持され、次のブロックへの移行に合わせて共通電極 140 の電位は低電位から高電位へまたは高電位から低電位へ切り替わる。

30

#### 【0041】

データライン 122 のそれぞれには、データライン駆動回路 420 によって、表示データに応じた電位が印加される。各データライン 122 への表示データ電位の印加は、例えば同時に行われる。表示データ電位は、共通電極 140 が上記低電位である期間中は当該低電位に対して高い電位に設定され、共通電極 140 が上記高電位である期間中は当該高電位に対して低い電位に設定される。つまり、表示データ電位は、共通電極 140 の電位に対する（共通電極 140 の電位を基準にした）極性が変化する。

#### 【0042】

例示のタイミングチャートの場合、データライン 122 には、1 番目のゲートライン 120 - 1 の選択開始から 2 番目のゲートライン 120 - 2 の選択終了までの期間は、共通電極 140 の電位に対して高い電位すなわち正極性の電位が印加される。その後、3 番目のゲートライン 120 - 3 の選択開始から 4 番目のゲートライン 120 - 4 の選択終了までの期間は、共通電極 140 の電位に対して低い電位すなわち負極性の電位がデータライン 122 に印加される。その後、5 番目のゲートライン 120 - 5 の選択開始から 6 番目のゲートライン 120 - 6 の選択終了までの期間は、正極性の電位が印加される。図 4 では、上記の正極性の電位および負極性の電位を“+”および“-”でそれぞれ示している。

40

#### 【0043】

なお、図 4 にはフレーム反転駆動の場合を例示している。

#### 【0044】

50

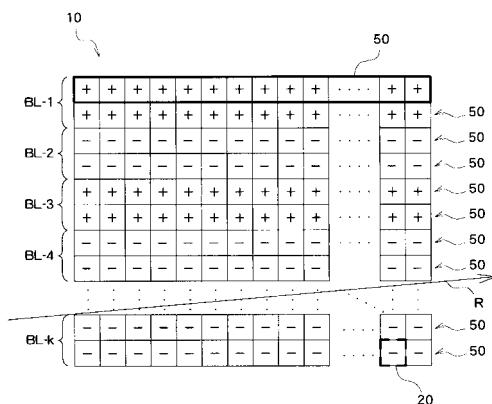

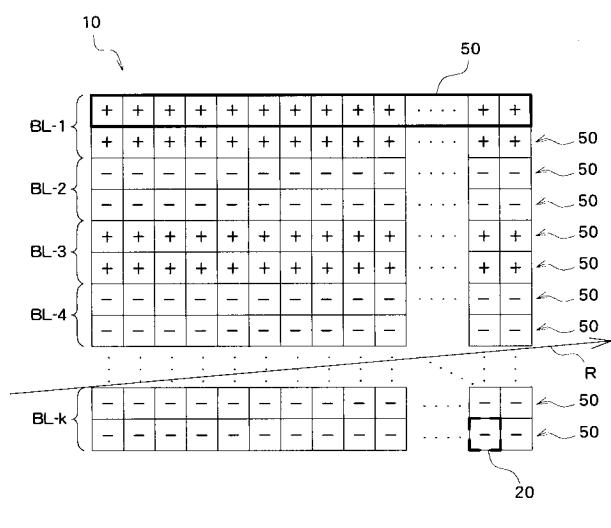

図5に、上記駆動方法による1フレーム分の表示データ電位の極性を説明する模式図を示す。図5では、各画素20を四角形で表し(1つの画素20についてのみ符号20を付している)、当該四角形の中にその画素20の画素電極160(図3参照)の極性を“+”または“-”で示している。

【0045】

上記駆動方法では、ゲートライン120を共有する複数の画素20に対応した画素列50が順次に選択され、選択された画素列50中の各画素20の画素電極160に表示データ電位が印加される。なお、説明のため図5では画素列50の1本を太線で囲んでいる。

【0046】

また、上記駆動方法では、表示画面を構成する複数本の画素列50は連続する2本ごとにブロック分けされて駆動される。図5ではk個のブロックBLに分けられた場合を例示しており、これらを区別するときは表示画面の上側から順番に、1番目のブロックBL-1、2番目のブロックBL-2のように呼ぶことにする。このとき、各ブロックBLでは、そのブロックBLに属する全ての画素電極160(図3参照)に、共通電極140(図3参照)の電位に対して同じ極性の電位が印加される。つまり、同一ブロックBL内の各画素20の共通電極140と画素電極160との間には同極性の電圧が印加される。一方、1番目のブロックBL-1の画素電極160と2番目のブロックBL-2の画素電極160とには共通電極140の電位に対して互いに逆極性の電位が印加される。同様に、2番目のブロックBL-2の画素電極160と3番目のブロックBL-3の画素電極160とには互いに逆極性の電位が印加される。第3番目のブロックBL-3と第4番目のブロックBL-4についても同様である。つまり、隣接するブロックBL間では共通電極140と画素電極160との間の電圧が互いに逆極性になる。

10

20

30

40

【0047】

なお、フレーム反転駆動の場合、次の1フレーム期間では図5の例示とは逆極性の電位が印加される。

【0048】

ここで、上記のように、配向膜170のラビング方向Rはスリット部163に略平行をなし、スリット部163はゲートライン120に平行に延伸している。したがって、ラビング方向Rは、ゲートライン120を共有する複数の画素20に対応した画素列50に略平行をなしている(図5参照)。このため、隣接する画素列50の境界に対応する隣接画素電極間領域40(図1参照)において、隣接する画素電極160間にわたる電界E4によって、光漏れが発生する可能性がある。

30

【0049】

しかし、液晶表示装置10によれば、画素電極160と共通電極140との間の電圧は、同じブロックBL内では同極性であり、隣接するブロックBL間では互いに逆極性である。このため、ライン反転駆動と比べて、互いに逆極性の電圧が印加される隣接画素20の数が減る。したがって、隣接画素電極間領域40で発生する光漏れ等を抑制することができる。その結果、コントラストの低下やちらつき等が低減されて、良好な表示品位が得られる。

【0050】

上記では各ブロックBLが2本の画素列50で構成される場合を例示したが、3本以上の画素列50で構成することも可能である。

【0051】

また、各ブロックBL中の画素列50の本数を異ならせることも可能である。すなわち、m本(mは3以上の整数)の画素列50を2個以上かつ(m-1)個以下のブロックBLに分けてもよい。この場合、少なくとも1個のブロックBLには、連続する2本以上の画素列50が含まれることになるので、上記と同様に、互いに逆極性の電圧が印加される隣接画素20の数を削減することができる。

【0052】

また、各ブロックBL中の画素列50の本数、換言すればブロックBLの個数は、表示

50

動作中に変更してもよい。すなわち、連続する 1 フレーム期間で異ならせててもよい。これによれば、互いに逆極性の電圧が同じ画素 20 に継続的に印加されることが抑制される。このため、同じ位置に継続的に光り漏れ等が発生することが抑制され、良好な表示品位が得られる。表示動作中におけるブロック BL の変更は、例えば、駆動回路 400 の不図示の制御回路が乱数表を利用してブロック BL の個数を設定し、その設定に従ってデータライン駆動回路 420 および共通電極駆動回路 430 が出力電位を制御することによって可能である。

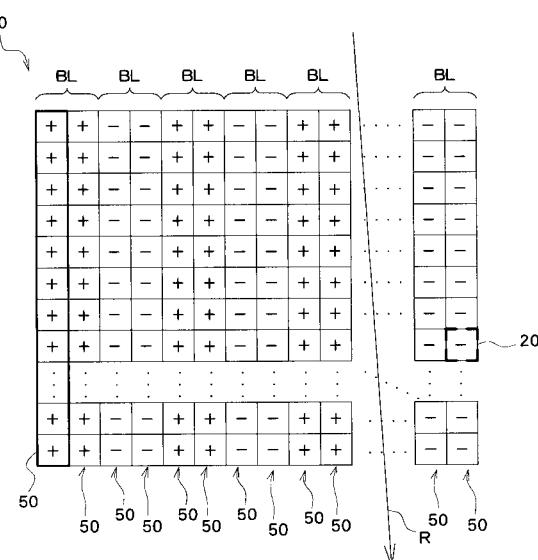

#### 【0053】

また、上記では画素電極 160 が横スリット型の場合を例示した。これに対して、枝部 162 およびスリット部 163 をデータライン 122 に平行に延伸させることも可能である。なお、この形態を「縦スリット型」と呼ぶことにする。縦スリット型においても、画素電極 160 を覆う配向膜 170 は、枝部 162 およびスリット部 163 の長手方向に略平行にラビング処理される。このため、縦スリット型の場合、ラビング方向 R に略平行に並ぶ画素 20 の列 50 は、データライン 122 を共有する複数の画素 20 が対応する（図 6 および図 3 参照）。なお、図 6 には、各ブロック BL が 2 本の画素列 50 で構成される場合を例示しており、ラビング方向 R の一例を矢印によって模式的に図示している。

10

#### 【0054】

また、上記では共通電極 140 に 2 つの所定電位が交互に印加される場合を例示したが、共通電極 140 への印加電位を一定にすることも可能である。

20

#### 【0055】

また、枝部 162 およびスリット部 163 をゲートライン 120 またはデータライン 122 に対して傾いた方向に延伸させることも可能である。この場合、その傾斜角が小さいとき、例えば 10° 以下のときは、実質的に縦スリット型または横スリット型と同一視することが可能である。

30

#### 【0056】

また、上記ではデータライン 122 に平行に並ぶ画素電極 160 が、くし歯形状の開放端の向きを交互にして配列されている場合を例示したが、当該開放端を同じ側に向けて配列することも可能である。また、図 7 の平面図に示す画素電極 160B を適用することも可能である。画素電極 160B は、上記の画素電極 160 において枝部 162 の開放端をもう一つの幹部 161 で繋いだ形状をしている。この場合、各スリット部 163 は画素電極 160B の外縁まで到達していないが、画素電極 160B も枝部 162 とスリット部 163 とによるライン・アンド・スペースのパターンを含んでいる。

30

#### 【0057】

また、上記では画素電極 160 が共通電極 140 よりも液晶層 300 側に配置された場合すなわち画素電極 160 が上電極となる場合を例示した。これに対して、図 8 の断面図に示す液晶表示装置 10B のように、共通電極 140 を上電極にすることも可能である。この場合、共通電極 140 にスリット部 143 が設けられるが、当該スリット部 143 を通って、隣接する画素電極 160 間に電界 E4 が生じる可能性がある。しかし、上記と同様に駆動することによって、液晶表示装置 10B においても良好な表示品位を得ることができる。

40

#### 【図面の簡単な説明】

#### 【0058】

【図 1】本発明の実施の形態に係る液晶表示装置の断面図である。

【図 2】本発明の実施の形態に係る液晶表示装置の平面図である。

【図 3】本発明の実施の形態に係る液晶表示装置の模式図である。

【図 4】本発明の実施の形態に係る液晶表示装置での駆動方法を説明するタイミングチャートである。

【図 5】図 4 の駆動方法を説明する模式図である。

【図 6】本発明の実施の形態に係る液晶表示装置での駆動方法の他の例を説明する模式図である。

50

【図7】本発明の実施の形態に係る画素電極の他の例を説明する平面図である。

【図8】本発明の実施の形態に係る液晶表示装置の他の例を説明する断面図である。

【図9】従来の液晶表示装置における画素電極間の光漏れを説明する図である。

## 【符号の説明】

( 0 0 5 9 )

10, 10B 液晶表示装置、20画素、50画素列、110, 210基板、140共通電極、150絶縁膜、160, 160B画素電極、170配向膜、300液晶層、400駆動回路、BL ブロック、R ラビング方向。

【 図 1 】

〔 図 2 〕

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

|                |                                                        |         |            |

|----------------|--------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2008203675A</a>                          | 公开(公告)日 | 2008-09-04 |

| 申请号            | JP2007041451                                           | 申请日     | 2007-02-21 |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                           |         |            |

| 申请(专利权)人(译)    | 爱普生影像设备公司                                              |         |            |

| [标]发明人         | 矢田竜也<br>山村久仁                                           |         |            |

| 发明人            | 矢田 竜也<br>山村 久仁                                         |         |            |

| IPC分类号         | G02F1/1343                                             |         |            |

| FI分类号          | G02F1/1343                                             |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/JB51 2H092/NA01 2H092/PA02 2H092/PA09 |         |            |

| 代理人(译)         | 吉田健治<br>石田 純                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                              |         |            |

## 摘要(译)

具有这样的结构的液晶显示装置，其中像素电极和公共电极之间插入有绝缘膜，以获得良好的显示质量。其中液晶层夹在一对基板之间的液晶显示装置包括多个像素列50和用于驱动多个像素列50中的每个像素20的驱动电路。每个像素20包括像素电极和公共电极，所述像素电极和公共电极设置在一对基板的一个基板上并且其间插入有绝缘膜，多个像素列50布置在像素电极的液晶层侧和公共电极上并且取向膜与取向膜基本平行地摩擦。驱动电路在每个块BL中具有相同的极性，BL在每个像素20的像素电极和公共电极之间划分为n (n是2或更大的整数)个连续的多个像素列50并且在相邻块之间施加具有相反极性的电压。点域5