(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-317514

(P2006-317514A)

(43) 公開日 平成18年11月24日(2006.11.24)

| (51) Int.CI.                | F 1                          | テーマコード (参考)                                                                                                                                                                                                                                     |

|-----------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36                    | 2 H093                                                                                                                                                                                                                                          |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/20                    | 6 1 1 F 5 C006                                                                                                                                                                                                                                  |

| <b>G02F 1/133 (2006.01)</b> | G09G 3/20                    | 6 2 1 F 5 C080                                                                                                                                                                                                                                  |

|                             | G09G 3/20                    | 6 2 1 M                                                                                                                                                                                                                                         |

|                             | G09G 3/20                    | 6 8 0 G                                                                                                                                                                                                                                         |

|                             |                              | 審査請求 未請求 請求項の数 5 O L (全 15 頁) 最終頁に続く                                                                                                                                                                                                            |

| (21) 出願番号                   | 特願2005-137170 (P2005-137170) | (71) 出願人 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号                                                                                                                                                                                          |

| (22) 出願日                    | 平成17年5月10日 (2005.5.10)       | (74) 代理人 110000028<br>特許業務法人明成国際特許事務所                                                                                                                                                                                                           |

|                             |                              | (72) 発明者 金子 英司<br>長野県諏訪市大和三丁目3番5号 セイコ<br>ーエプソン株式会社内                                                                                                                                                                                             |

|                             |                              | F ターム (参考) 2H093 NA53 NA62 NC13 NC25 NC29<br>NC59 NC65 ND06 ND32 ND58<br>5C006 AA11 AF13 AF45 AF46 AF51<br>AF53 AF61 AF71 BC16 BF02<br>BF08 BF14 BF24 EB04 EB05<br>FA04 FA14 FA18 FA41 FA56<br>5C080 AA10 BB05 DD04 DD22 DD27<br>DD28 EE29 JJ02 |

(54) 【発明の名称】表示特性補正集積回路、液晶制御装置

## (57) 【要約】

【課題】 集積回路であって、低機能版液晶制御装置および高機能版液晶制御装置とで、共通して用いることができ、低機能版液晶制御装置で用いる場合には、VT特性補正を行うことができ、高機能版液晶制御装置で用い場合には、VT特性補正又はVT特性補正に加えて応答速度補正とを行うことができる汎用性が高い集積回路を提供すること。

【解決手段】 液晶パネルのVT特性の補正を行う表示特性補正集積回路であって、画像信号が表わす画像データの変化に応じて、液晶パネルの表示の応答速度を上げるように、VT特性補正に加えて、応答速度の補正を行うか否かを表わす補正判定信号を受け付ける補正判定信号入力端子と、補正判定信号が応答速度補正を行わないことを表わす場合には、画像データに対して、VT特性補正を行い、補正判定信号が応答速度補正を行うことを表わす場合には、画像データに対して、VT特性補正と応答速度補正とを組み合わせた補正を行う。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数の画像データを時系列に液晶パネルに表示させる制御を行う液晶制御装置で用いられ、前記液晶パネルのV T特性の補正を行う表示特性補正集積回路であって、

前記液晶制御装置に入力される画像信号を入力する画像信号入力端子と、

前記画像信号が表わす画像データの変化に応じて、前記液晶パネルにおける表示の応答速度を上げるように、前記V T特性補正に加えて、前記応答速度の補正を行うか否かを表わす補正判定信号を受け付ける補正判定信号入力端子と、

受け付けた前記補正判定信号が前記応答速度補正を行わないことを表わす場合には、前記画像データに対して、前記V T特性補正を行い、受け付けた前記補正判定信号が前記応答速度補正を行うことを表わす場合には、前記画像データに対して、前記V T特性補正と前記応答速度補正とを組み合わせた補正を行う補正部と、

補正後の前記画像データを画像信号として出力するための画像信号出力端子と、

を備えることを特徴とする表示特性補正集積回路。

**【請求項 2】**

請求項 1 に記載の表示特性補正集積回路において、

前記補正部は、

前記画像データに対して、前記補正信号入力端子が受け付けた前記補正判定信号が前記応答速度補正を行わないことを表わす場合には、V T特性補正用ルックアップテーブルを用いて前記V T特性補正を行い、受け付けた前記補正判定信号が前記応答速度補正を行うことを表わす場合には、応答速度補正用ルックアップテーブルを用いて、前記V T特性補正と前記応答速度補正とを組み合わせた補正を行うことを特徴とする表示特性補正集積回路。

**【請求項 3】**

請求項 1 または請求項 2 に記載の表示特性補正集積回路において、

前記補正判定信号入力端子が受け付ける前記補正判定信号は、

前記画像データの各画素データに対して、前記応答速度補正を行うか否かを表わし、前記補正部は、

受け付けた前記補正判定信号が前記応答速度補正を行わないことを表わす場合には、前記画像データの各画素データに対して、前記V T特性補正を行い、受け付けた前記補正判定信号が前記応答速度補正を行うことを表わす場合には、前記画像データの各画素データに対して、前記V T特性補正と前記応答速度補正と組み合わせた前記補正を行うことを特徴とする表示特性補正集積回路。

**【請求項 4】**

請求項 1 ないし請求項 3 のいずれかに記載の表示特性補正集積回路を備える液晶制御装置。

**【請求項 5】**

複数の画像データを時系列に液晶パネルに表示させ、該液晶パネルのV T特性の補正を行う液晶制御装置であって、

応答速度制御用集積回路と、

前記応答速度制御用集積回路とは異なる集積回路である表示特性補正集積回路とを備え、

前記応答速度制御用集積回路は、

前記液晶制御装置に入力される画像信号が表わす画像データの変化に応じて、前記液晶パネルにおける表示の応答速度を上げるように、前記V T特性補正に加えて、前記応答速度の補正を行うか否か判定する応答速度補正判定部と、

前記応答速度補正判定部の判定に基づいて、前記画像データに対して前記応答速度補正を行うか否かを表わす補正判定信号を生成する信号生成部と、

生成した前記補正判定信号を出力するための補正判定信号出力端子と、

を備え、

10

20

30

40

50

前記表示特性補正集積回路は、

前記画像信号を入力する画像信号入力端子と、

前記補正判定信号出力端子から出力される前記補正判定信号を受け付ける補正信号入力端子と、

受け付けた前記補正判定信号が前記応答速度補正を行わないことを表わす場合には、前記画像データに対して、前記V-T特性補正を行い、受け付けた前記補正判定信号が前記応答速度補正を行うことを表わす場合には、前記画像データに対して、前記V-T特性補正と前記応答速度補正とを組み合わせた補正を行う補正部と、

補正後の前記画像データを画像信号として出力するための画像信号出力端子と、

を備えることを特徴とする液晶制御装置。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶パネルの液晶制御装置において、液晶パネルに表示する画像に対して応答速度補正を行う技術に関する。

##### 【背景技術】

##### 【0002】

従来、液晶制御装置は、液晶パネルの各液晶セル（以下、画素と呼ぶ。）に印加させる印加電圧Vを変化させることで、各画素の光透過率Tを変化させて、液晶パネルに画像を表示する。この場合、液晶制御装置は、液晶パネルの表示特性等に起因する印加電圧V - 光透過率T特性（V-T特性）を補正するV-T特性補正を行う必要があった。

20

##### 【0003】

また、この液晶表示装置において、例えば、液晶パネルに時系列な複数の画像から成る動画像を表示する場合に、液晶パネルに表示した画像（以下、現表示画像と呼ぶ。）に、現表示画像の一つ前の画像（以下、前表示画像と呼ぶ。）の一部が重なって見えるなどの動画ぼやけが発生する場合がある。そこで、液晶制御装置は、動画ぼやけを解消するためには、V-T特性補正に加えて、例えば、下記特許文献1に記載の技術のように、現表示画像を表わす画像データに対して応答速度の補正（以下、応答速度補正と呼ぶ。）を行う必要があった。ここで、応答速度とは、現表示画像を表わす画像データの変化に対する液晶パネルの表示の変化速度のことである。そして、応答速度補正とは、液晶パネルの表示の変化速度（応答速度）を上げるように、画像データの表わす印加電圧を調整することである。

30

##### 【0004】

##### 【特許文献1】特開2003-241721号公報

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0005】

ところで、廉価版として、上述したV-T特性補正を行う機能（以下では、V-T特性補正機能と呼ぶ。）のみを備えた低機能な液晶制御装置（以下では、低機能版液晶制御装置と呼ぶ。）と、V-T特性補正機能と、V-T特性補正と応答速度補正とを組み合わせた補正を行う機能（以下では、V-T応答速度補正機能と呼ぶ。）とを備え、これらを使い分けて実施する高機能な液晶制御装置（以下では、高機能版液晶制御装置と呼ぶ。）とがある。これら低機能版液晶制御装置または高機能版液晶制御装置は、例えば、V-T特性補正機能、または、V-T特性補正機能とV-T応答速度補正機能とを、それぞれ一つの集積回路に搭載していた。しかしながら、この場合、低機能版液晶制御装置および高機能版液晶制御装置のそれぞれで、異なる集積回路を新たに開発する必要があった。

40

##### 【0006】

本発明は、上記課題に鑑みてなされたもので、集積回路であって、低機能版液晶制御装置および高機能版液晶制御装置とで、共通して用いることが可能であり、低機能版液晶制御装置で用いる場合には、少なくともV-T特性補正を行うことができ、高機能版液晶制御

50

装置で用いる場合は、少なくとも VT 特性補正または VT 特性補正と応答速度補正とを組み合わせた補正とを行うことができる汎用性が高い集積回路を提供することを目的とする。

#### 【課題を解決するための手段】

##### 【0007】

上記目的の少なくとも一部を達成するために、本発明の表示特性補正集積回路は、複数の画像データを時系列に液晶パネルに表示させる制御を行う液晶制御装置で用いられ、前記液晶パネルの VT 特性の補正を行う表示特性補正集積回路であって、

前記液晶制御装置に入力される画像信号を入力する画像信号入力端子と、

前記画像信号が表わす画像データの変化に応じて、前記液晶パネルにおける表示の応答速度を上げるように、前記 VT 特性補正に加えて、前記応答速度の補正を行うか否かを表わす補正判定信号を受け付ける補正判定信号入力端子と、

受け付けた前記補正判定信号が前記応答速度補正を行わないことを表わす場合には、前記画像データに対して、前記 VT 特性補正を行い、受け付けた前記補正判定信号が前記応答速度補正を行うことを表わす場合には、前記画像データに対して、前記 VT 特性補正と前記応答速度補正と組み合わせた補正を行う補正部と、

補正後の前記画像データを画像信号として出力するための画像信号出力端子と、

を備えることを要旨とする。

##### 【0008】

上記構成の表示特性補正集積回路によれば、補正判定信号に基づいて、 VT 特性補正、若しくは、 VT 特性補正と応答速度補正とを組み合わせた補正を行うことができる。従って、上記構成の表示特性補正集積回路を、高機能版液晶制御装置に用いれば、画像信号が表わす画像データに対して、 VT 特性補正か、若しくは、 VT 特性補正と応答速度補正とを組み合わせた補正を行うことができる。また、上記構成の表示特性補正集積回路を、低機能版液晶制御装置に用いれば、画像信号が表わす画像データに対して、 VT 特性補正のみを実施することができる。従って、上記構成の表示特性補正集積回路は、高機能版液晶制御装置と、低機能版液晶制御装置との両方に用いることができ、すなわち、汎用性が高い集積回路である。

##### 【0009】

上記表示特性補正集積回路において、

前記補正部は、

前記画像データに対して、前記補正信号入力端子が受け付けた前記補正判定信号が前記応答速度補正を行わないことを表わす場合には、 VT 特性補正用ルックアップテーブルを用いて前記 VT 特性補正を行い、受け付けた前記補正判定信号が前記応答速度補正を行うことを表わす場合には、応答速度補正用ルックアップテーブルを用いて、前記応答速度補正を行うようにしてもよい。

##### 【0010】

このようにはすれば、画像データに対して、 VT 特性補正を、 VT 特性補正用ルックアップテーブルを用いることにより実施することができ、また、画像データに対して、 VT 特性補正と応答速度補正とを組み合わせた補正を、応答速度補正用ルックアップテーブルを用いて実施することができる。

##### 【0011】

上記表示特性補正集積回路において、

前記補正判定信号入力端子が受け付ける前記補正判定信号は、

前記画像データの各画素データに対して、前記応答速度補正を行うか否かを表わし、前記補正部は、

受け付けた前記補正判定信号が前記応答速度補正を行わないことを表わす場合には、前記画像データの各画素データに対して、前記 VT 特性補正を行い、受け付けた前記補正判定信号が前記応答速度補正を行うことを表わす場合には、前記画像データの各画素データに対して、前記 VT 特性補正と前記応答速度補正とを組み合わせた前記補正を行うように

10

20

30

40

50

してもよい。

【0012】

このようにすれば、画像信号が表わす画像データの各画素データ単位で、V T特性補正か、若しくは、V T特性補正と応答速度補正とを組み合わせた補正を実施することができる。その結果、液晶パネル上において、画像データの表わす画像を好適に表示することができる。

【0013】

上記表示特性補正集積回路を液晶制御装置に用いるようにしてもよい。

【0014】

上記目的の少なくとも一部を達成するために、本発明の液晶制御装置は、

複数の画像データを時系列に液晶パネルに表示させ、該液晶パネルのV T特性の補正を行う液晶制御装置であって、

応答速度制御用集積回路と、

前記応答速度制御用集積回路とは異なる集積回路である表示特性補正集積回路とを備え、

前記応答速度制御用集積回路は、

前記液晶制御装置に入力される画像信号が表わす画像データの変化に応じて、前記液晶パネルにおける表示の応答速度を上げるように、前記V T特性補正に加えて、前記応答速度の補正を行うか否か判定する応答速度補正判定部と、

前記応答速度補正判定部の判定に基づいて、前記画像データに対して前記応答速度補正を行うか否かを表わす補正判定信号を生成する信号生成部と、

生成した前記補正判定信号を出力するための補正判定信号出力端子と、

を備え、

前記表示特性補正集積回路は、

前記画像信号を入力する画像信号入力端子と、

前記補正判定信号出力端子から出力される前記補正判定信号を受け付ける補正信号入力端子と、

受け付けた前記補正判定信号が前記応答速度補正を行わないことを表わす場合には、前記画像データに対して、前記V T特性補正を行い、受け付けた前記補正判定信号が前記応答速度補正を行うことを表わす場合には、前記画像データに対して、前記V T特性補正と前記応答速度補正とを組み合わせた補正を行う補正部と、

補正後の前記画像データを画像信号として出力するための画像信号出力端子と、

を備えることを要旨とする。

【0015】

上記構成の液晶制御装置は、補正判定信号に基づいて、V T特性補正、若しくは、V T特性補正と応答速度補正とを組み合わせた補正を行うことができる汎用性の高い表示特性補正集積回路を用いている。従って、上記構成の液晶制御装置の開発コストを抑制することができる。

【0016】

なお、本発明は、上記した表示特性補正集積回路や液晶制御装置などの装置発明の態様に限ることなく、表示特性補正集積回路や液晶制御装置の制御方法などの方法発明としての態様で実現することも可能である。さらには、それら方法や装置を構築するためのコンピュータプログラムとしての態様や、そのようなコンピュータプログラムを記録した記録媒体としての態様や、上記コンピュータプログラムを含み搬送波内に具現化されたデータ信号など、種々の態様で実現することも可能である。

【0017】

また、本発明をコンピュータプログラムまたはそのプログラムを記録した記録媒体等として構成する場合には、上記装置の動作を制御するプログラム全体として構成するものとしてもよいし、本発明の機能を果たす部分のみを構成するものとしてもよい。

【発明を実施するための最良の形態】

10

20

30

40

50

## 【0018】

以下、本発明の実施の形態について、実施例に基づき次の順序で説明する。

## A. 実施例：

A 1. 表示特性補正集積回路Yの構成：

A 2. 液晶表示装置100の構成：

A 3. 高機能版液晶制御部300Aの構成：

A 4. 高機能版液晶制御部300Aの動作処理：

A 5. 低機能版液晶制御部300Bの構成：

A 6. 低機能版液晶制御部300Bの動作処理：

## B. 変形例：

10

## 【0019】

## A. 実施例：

A 1. 表示特性補正集積回路Yの構成：

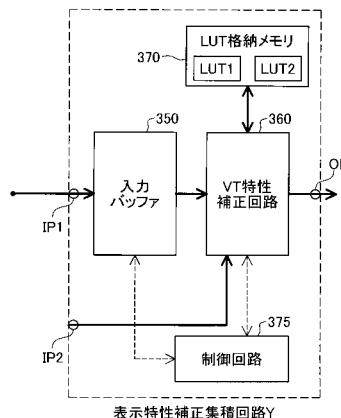

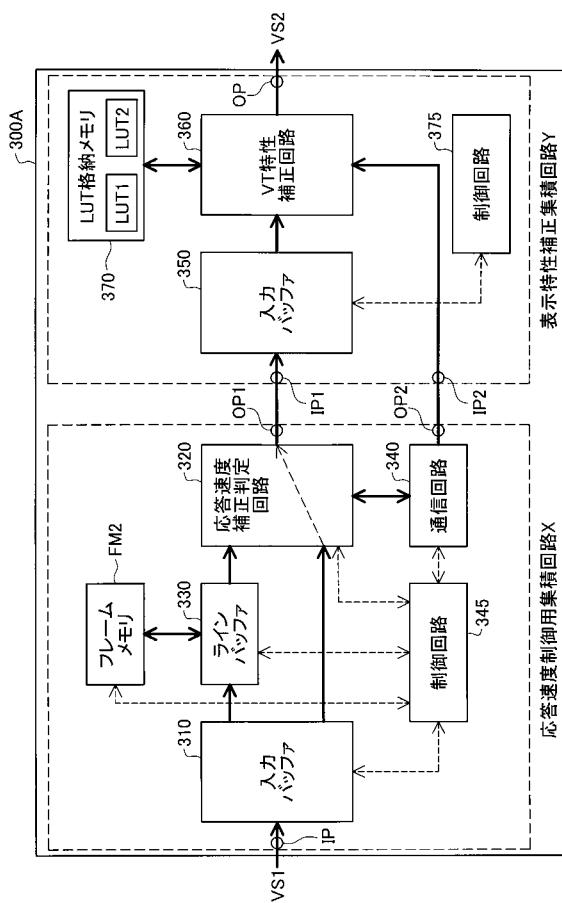

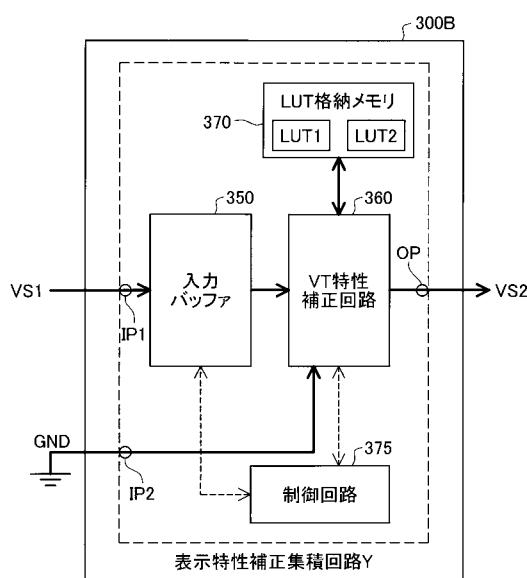

図1は、本発明の一実施例としての表示特性補正集積回路Yの概略構成を示す説明図である。この表示特性補正集積回路Yは、入力バッファ350と、VT特性補正回路360と、LUT格納メモリ370と、制御回路375と、画像信号入力端子IP1と、ODEN信号入力端子IP2と、画像信号出力端子OPとを備える。

## 【0020】

画像信号入力端子IP1は、所定の画像信号（または画像データ）を入力するための端子である。ODEN信号入力端子IP2は、後述するODEN信号を入力するための端子である。なお、ODEN信号入力端子IP2は、請求項における補正判定信号入力端子に該当する。また、ODEN信号は、請求項における補正判定信号に該当する。

20

## 【0021】

本実施例でいう画像信号は、R（レッド）信号、G（グリーン）信号、および、B（ブルー）信号から構成され、画像信号が表す画像データとは、R信号が表すR画像データ、G信号が表すG画像データ、および、B信号が表すB画像データの総称である。また、画像データの画素データは、階調値（画素値）で表され、すなわち、R, G, B画像データの各画素データもこの階調値（画素値）で表わされる。

## 【0022】

入力バッファ350は、画像信号入力端子IP1を介して入力される画像信号が表わす画像データの1画素分の画素データを入力し、バッファリングするバッファである。

30

## 【0023】

制御回路375は、入力バッファ350と、VT特性補正回路360とを制御する。

LUT格納メモリ370は、画像信号が表わす画像データ（R, G, B画像データ）の各画素データに対し、後述する液晶パネル500の表示特性等に起因する印加電圧V-光透過率T特性（VT特性）を補正するVT特性補正を行うためのルックアップテーブルLUT1と、画像データの各画素データに対し、VT特性補正と、応答速度補正とを組み合わせた補正を行うためのルックアップテーブルLUT2とを備える。このLUT格納メモリ370は、例えば、SRAM（Static Random Access Memory）としてもよい。

40

## 【0024】

VT特性補正回路360は、ODEN信号入力端子IP2から入力されるODEN信号に基づき、ルックアップテーブルLUT1またはルックアップテーブルLUT2を用いて、画像データの各画素データに対して、階調値の補正を行う。なお、VT特性補正回路360は、請求項における補正部に該当する。

## 【0025】

画像信号出力端子OPは、VT特性補正回路360で補正された画像データを表わす画像信号を出力するための端子である。

## 【0026】

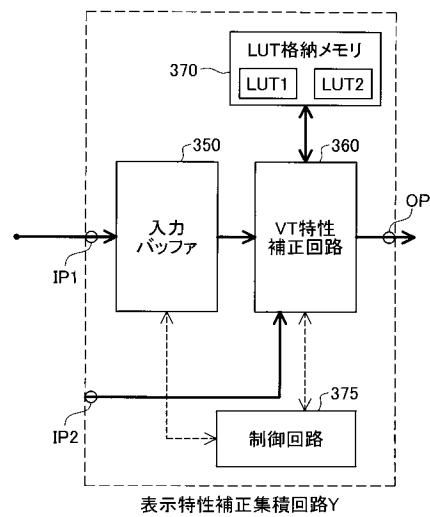

A 2. 液晶表示装置100の構成：

図2は、本実施例としての表示特性補正集積回路Yを用いた液晶制御部300を備えた

50

液晶表示装置100の概略構成を示す説明図である。液晶表示装置100は、主に、信号処理部200と、フレームメモリFM1と、液晶制御部300と、液晶パネル駆動部400と、光変調装置としての液晶パネル500とを備えている。液晶表示装置100は、この他、所定のインターフェイス等の種々の周辺装置等を備えているが、本実施例では、説明を省略する。

#### 【0027】

信号処理部200は、入力される画像信号VSを、フレームメモリFM1に書き込み、スケーリング処理（拡大または縮小処理）やコントラスト補正等の所定の画像処理を行い、垂直同期信号（Vsync）、水平同期信号（Hsync）、クロック信号などのタイミングに基づいて、画像信号VS1として、出力する。10

#### 【0028】

液晶制御部300は、画像信号VS1を入力し、所定の処理を行い、画像信号VS2として出力する。この液晶制御部300は、本発明の特徴部分である表示特性補正集積回路Yを用いて、VT特性補正と応答速度補正とを組み合わせた補正を実施可能である高機能な液晶制御部300A（以下、高機能版液晶制御部300Aと呼ぶ。）と、廉価版として応答速度補正を行わずVT特性補正のみを実施可能である低機能な液晶制御部300B（以下、低機能版液晶制御部300Bと呼ぶ。）とを実現している。これらの詳細についての説明は、後述する。

#### 【0029】

液晶パネル駆動部400は、画像信号VS2を入力し、画像信号VS2に従って、液晶パネル500を駆動する。液晶パネル500に備えられるバックライト（図示せず）より発せられた光は、駆動された液晶パネル500によって変調されて、液晶パネル500に画像を表示する。20

#### 【0030】

A3. 高機能版液晶制御部300Aの構成：

図3は、本実施例の高機能版液晶制御部300Aの概略構成を示す説明図である。この高機能版液晶制御部300Aは、本発明の特徴部分である表示特性補正集積回路Yに加えて、応答速度制御用集積回路Xを備え、入力される画像信号VS1の表わす画像データ（厳密に言えば、画像データの各画素データ）に対して、応答速度補正を行うか否かを判定し、その判定の結果に基づいて、画像データ（の各画素データ）に対して、VT特性補正のみを行うか、若しくは、VT特性補正に加えて、応答速度補正を行い、画像信号VS2として出力する。なお、画像信号VS1が表す画像データにおいて、液晶パネル500にこれから表示される画像を表す画像データを、以下では、表示画像データとも呼ぶ。従って、応答速度補正を行うか否かの判定を行う画像データは、表示画像データである。また、表示画像データが表す画像を表示画像とも呼ぶ。30

#### 【0031】

応答速度制御用集積回路Xは、入力バッファ310と、ラインバッファ330と、フレームメモリFM2と、応答速度補正判定回路320と、通信回路340と、制御回路345と、画像信号出力端子OP1と、ODEN信号出力端子OP2と、画像信号入力端子IPとを備える。なお、ODEN信号出力端子OP2は、請求項における補正判定信号出力端子に該当する。40

#### 【0032】

画像信号入力端子IPは、画像信号VS1を入力するための端子である。

制御回路345は、入力バッファ310と、応答速度補正判定回路320と、ラインバッファ330と、フレームメモリFM2と、通信回路340とを制御する。

#### 【0033】

フレームメモリFM2は、画像信号VS1において、表示画像データの一つ前の画像データである画像データ（以下では、過去画像データと呼ぶ。）を記憶しておくためのメモリである。

#### 【0034】

10

20

30

40

50

入力バッファ310は、画像信号入力端子IPを介して、画像信号VS1が表す表示画像データの1画素分の画素データを入力し、バッファリングするバッファである。

#### 【0035】

ラインバッファ330は、画像データの1ライン分の画素データと、1画素分の画素データとをバッファリング可能なバッファで(図示せず)ある。1ライン分のバッファは、入力バッファ310から送られてくる表示画像データの画素データを順次バッファリングし、1画素のバッファは、フレームメモリFM2に書き込まれていた過去画像データの画素データをバッファリングする。

#### 【0036】

応答速度補正判定回路320は、表示画像データの各画素データに対して、応答速度補正を行うか否かを判定する。また、応答速度補正判定回路320は、画像信号出力端子OP1を介して、応答速度補正を行った表示画像データの画素データを表示特性補正集積回路Yに出力する。なお、応答速度補正判定回路320は、請求項における応答速度補正判定部に該当する。

#### 【0037】

通信回路340は、応答速度補正判定回路320の判定結果に基づいて、所定の信号(以下では、ODEN信号と呼ぶ。)を生成し、そのODEN信号をODEN信号出力端子OP2を介して表示特性補正集積回路Yに出力する。この通信回路340は、請求項における信号生成部に該当する。以下では、液晶制御部300Aの応答速度制御用集積回路Xおよび表示特性補正集積回路Yにおける各機能ブロックの動作処理について、具体的に説明する。

#### 【0038】

A4. 高機能版液晶制御部300Aの動作処理：

前提条件として、フレームメモリFM2には、上述したように、過去画像データが記憶されている。また、表示画像データおよび過去画像データにおいて、各画像データが表わす画像における各画素の座標を(m, n)(mは、画像のライン番号を表わし、nは、番号mのラインにおいて、何番目の画素かを表わす。m: 1 ~ kまでの整数、n: 1 ~ 1までの整数。)とする。以下では、各画像データが表わす画像において、座標(m, n)の画素を表わす画素データを、(m, n)画素データとも呼ぶ。さらに、入力バッファ310には、表示画像データにおいて、最初に(1, 1)画素データが入力され、次に、そのライン(m = 1)の画素データが、n = 2, 3, 4...1の順番で入力され、それ以降同様に、各ライン(m = 2, 3, 4...k)において、n = 1, 2, 3...1の順番で画素データが入力されるようになっている。

#### 【0039】

<第1A工程>

まず、制御回路345は、入力バッファ310に画像信号VS1が表わす表示画像データの先頭の画素データ(すなわち、表示画像データの(1, 1)画素データ。)が入力されると、表示画像データの(1, 1)画素データをラインバッファ330へ読み出す。

#### 【0040】

<第2A工程>

続いて、制御回路345は、フレームメモリFM2から、表示画像データの(1, 1)画素データに対応する、過去画像データの画素データ(すなわち、過去画像データの(1, 1)画素データ。)をラインバッファ330に読み出して、応答速度補正判定回路320へ送信させ、また、それに同期させて、入力バッファ310に入力された表示画像データの(1, 1)画素データを応答速度補正判定回路320へ送信させる。

#### 【0041】

<第3A工程>

応答速度補正判定回路320は、送信されてきた表示画像データの(1, 1)画素データが表わす階調値と、過去画像データの(1, 1)画素データが表わす階調値との差の絶対値(以下、階調差絶対値と呼ぶ。)を求め、所定の閾値Rと比較する。応答速度補正判

10

20

30

40

50

定回路 320 は、階調差絶対値が閾値 R 以上の場合には、応答速度補正を行うと判定し、階調差絶対値が閾値 R より小さい場合には、応答速度補正を行わないと判定し、その判定結果を通信回路 340 に伝える。

#### 【0042】

< 第 4 A 工程 >

通信回路 340 は、判定結果を受け付け、判定結果が、応答速度補正を行うと判定された場合には、ODEN 信号を「High」として生成し、制御回路 345 の指示により、ODEN 信号出力端子 OP2 を介して表示特性補正集積回路 Y に出力する。通信回路 340 は、判定結果が、応答速度補正を行わないと判定された場合には、ODEN 信号を「Low」として生成し、制御回路 345 の指示により、ODEN 信号出力端子 OP2 を介して表示特性補正集積回路 Y に出力する。10

#### 【0043】

< 第 5 A 工程 >

また、応答速度補正判定回路 320 は、表示画像データの(1, 1)画素データを、制御回路 345 の指示により、通信回路 340 による ODEN 信号の出力に同期させて、画像信号出力端子 OP1 を介して、表示特性補正集積回路 Y に出力する。

#### 【0044】

< 第 6 A 工程 >

一方、表示特性補正集積回路 Y において、制御回路 375 は、入力バッファ 350 に、画像信号入力端子 IP1 を介して、応答速度制御用集積回路 X から表示画像データの(1, 1)画素データが入力されると、表示画像データの(1, 1)画素データを VT 特性補正回路 360 に読み出す。20

#### 【0045】

< 第 7 A 工程 >

VT 特性補正回路 360 は、通信回路 340 から出力される ODEN 信号を ODEN 信号入力端子 IP2 を介して入力する。VT 特性補正回路 360 は、制御回路 375 の指示により、入力した ODEN 信号が「Low」の場合には、LUT 格納メモリ 370 からルックアップテーブル LUT1 を読み出し、それを用いて表示画像データの(1, 1)画素データに VT 特性補正を行う。VT 特性補正回路 360 は、入力した ODEN 信号が「High」の場合には、LUT 格納メモリ 370 からルックアップテーブル LUT2 を読み出し、それを用いて表示画像データの(1, 1)画素データに対して、VT 特性補正と応答速度補正とを組み合わせた補正を行う。30

#### 【0046】

< 第 8 A 工程 >

続いて、VT 特性補正回路 360 は、制御回路 375 の指示により、補正後の画素データを画像信号出力端子 OP を介して画像信号 VS2 (1 画素分) として液晶パネル駆動部 400 に出力する。

#### 【0047】

そして、入力バッファ 310 に表示画像データの(1, 1)画素データの次の画素データである表示画像データの(1, 2)画素データ、その次の画素データある(1, 3)画素データ、...、(1, 1)画素データが、順番に入力される度に、高機能版液晶制御部 300A (応答速度制御用集積回路 X および表示特性補正集積回路 Y) の各機能ブロックは、上述した第 1 A 工程～第 8 A 工程の処理を行う。この場合、上述の第 2 A 工程において、制御回路 345 が、フレームメモリ FM2 から読み出す過去画像データの画素データは、第 1 A 工程において制御回路 345 がラインバッファ 330 へ読み出した表示画像の画素データに対応する座標の画素データである。例えば、第 1 A 工程において、表示画像データの(1, 2)画素データが入力バッファ 310 に入力され、制御回路 345 が、それをラインバッファ 330 に読み出した場合には、第 2 A 工程において、制御回路 345 が、フレームメモリ FM2 から読み出す過去画像データの画素データは、過去画像データにおける(1, 2)画素データである。また、この場合、ラインバッファ 330 には、入4050

力バッファ 310 に表示画像データの画素データが入力される度に、制御回路 345 によって入力バッファ 310 から読み出された表示画像データの各画素データ（ここでは、表示画像データの(1, 1)～(1, k)画素データ。）が順次バッファリングされていく。

#### 【0048】

制御回路 345 は、表示画像データにおける(1, 1)画素データについて、上述の第 1A 工程～第 8A 工程までの処理を終了した場合、すなわち、表示画像データにおける先頭ラインのすべての画素データに対して、上述の第 1A 工程～第 8A 工程までの処理を終了した場合には、ラインバッファ 330 にバッファリングされている表示画像データの各画素データ（1ライン分の画素データ）を、フレームメモリ FM2 に書き込む。10

#### 【0049】

同様に、高機能版液晶制御部 300A の各機能ブロックは、表示画像データにおける 2 ライン以降 ( $m = 2 \sim k$ ) の各ラインにおいて、そのラインの画素データに対して、上述した第 1A 工程～第 8A 工程の処理を行い、制御回路 345 は、そのラインについて、第 1A 工程～第 8A 工程までの処理を終了した場合には、ラインバッファ 330 にバッファリングされている表示画像データの各画素データ（1ライン分の画素データ）を、フレームメモリ FM2 に書き込む。

#### 【0050】

以上のようにして、高機能版液晶制御部 300A は、表示画像データの全てのラインの全ての画素データについて、VT 特性補正、若しくは、VT 特性補正と応答速度補正とを組み合わせた補正を行う。20

#### 【0051】

また、以上のように、入力バッファ 310 に入力された表示画像データの各画素データは、ラインバッファ 330 に一端バッファリングされた後、フレームメモリ FM2 に書き込まれ、最終的に、フレームメモリ FM2 には、表示画像データが書き込まれることになる。そして、次に、画像信号 VS1 において、表示画像データの次の画像データを、新たな表示画像データとし、今回フレームメモリ FM2 に書き込んだ表示画像データを新たな過去画像データとして、上述した処理を繰り返し行い、画像信号 VS1 の表わす任意の画像データに対して、VT 特性補正、若しくは、VT 特性補正と応答速度補正とを組み合わせた補正を行うことができる。30

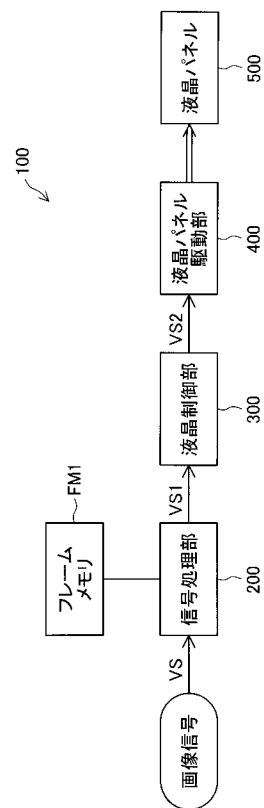

#### 【0052】

##### A5. 低機能版液晶制御部 300B の構成：

図 4 は、本実施例の低機能版液晶制御部 300B の概略構成を示す説明図である。この低機能版液晶制御部 300B は、本発明の特徴部分である表示特性補正集積回路 Y のみを備え、入力される画像信号 VS1 の表わす画像データ（厳密に言えば、画像データの各画素データ）に対して、応答速度補正を行わず VT 特性補正のみを行い、画像信号 VS2 として出力する。なお、表示特性補正集積回路 Y は、この低機能版液晶制御部 300B で用いられる場合において、ODEN 信号入力端子 IP2 がグランド (GND) されており、常に、ODEN 信号が「Low」の状態で入力されたのと同様の状態になっている。以下では、低機能版液晶制御部 300B の各機能ブロックの動作処理について、具体的に説明する。40

#### 【0053】

##### A6. 低機能版液晶制御部 300B の動作処理：

###### < 第 1B 工程 >

まず、制御回路 375 は、入力バッファ 350 に、画像信号入力端子 IP1 を介して、画像信号 VS1 が表わす表示画像データの先頭の画素データ（すなわち、表示画像データの(1, 1)画素データ。）が入力されると、表示画像データの(1, 1)画素データを VT 特性補正回路 360 へ読み出す。

#### 【0054】

###### < 第 2B 工程 >

10

20

30

40

50

V T 特性補正回路 3 6 0 は、常に O D E N 信号が「 L o w 」の状態で入力されているので、L U T 格納メモリ 3 7 0 からルックアップテーブル L U T 1 を読み出し、それを用いて表示画像データの(1, 1)画素データに V T 特性補正のみを行う。

#### 【 0 0 5 5 】

< 第 3 B 工程 >

続いて、V T 特性補正回路 3 6 0 は、補正後の画素データを画像信号出力端子 O P を介して画像信号 V S 2 (1 画素分) として液晶パネル駆動部 4 0 0 に出力する。

#### 【 0 0 5 6 】

そして、低機能版液晶制御部 3 0 0 B における表示特性補正集積回路 Y の各機能ブロックは、入力バッファ 3 5 0 に表示画像データの(1, 1)画素データの次の画素データである表示画像データの(1, 2)画素データ、その次の画素データある(1, 3)画素データ、...、(1, 1)画素データが、順番に入力される度に、上述した第 1 B 工程～第 3 B 工程の処理を行い、表示画像データの全てのラインの全ての画素データについて、V T 特性補正を行う。

10

#### 【 0 0 5 7 】

以上のように本実施例の表示特性補正集積回路 Y を、高機能版液晶制御部 3 0 0 A に用いることにより、応答速度制御用集積回路 X における応答速度補正判定回路 3 2 0 の判定結果に基づき、画像信号 V S 1 が表わす画像データ(各画素データ)に対して、V T 特性補正か、若しくは、V T 特性補正と応答速度補正とを組み合わせた補正を行うことができる。一方、表示特性補正集積回路 Y を、低機能版液晶制御部 3 0 0 B に用いることにより、画像信号 V S 1 が表わす画像データ(各画素データ)に対して、V T 特性補正のみを実施することができる。すなわち、この表示特性補正集積回路 Y は、液晶制御部 3 0 0 において、高機能版液晶制御部 3 0 0 A と、低機能版液晶制御部 3 0 0 B との両方に用いることができる汎用性が高い集積回路である。

20

#### 【 0 0 5 8 】

また、以上のように本実施例の表示特性補正集積回路 Y では、画像信号 V S 1 が表わす画像データの各画素データ単位で、V T 特性補正か、若しくは、V T 特性補正と応答速度補正とを組み合わせた補正を実施することができる。その結果、液晶パネル 5 0 0 上において、画像データの表わす画像を好適に表示することができる。

30

#### 【 0 0 5 9 】

B . 变形例 :

なお、本発明では、上記した実施の形態に限られるものではなく、その要旨を逸脱しない範囲において種々の態様にて実施することが可能である。

#### 【 0 0 6 0 】

B 1 . 变形例 1 :

上記実施例の表示特性補正集積回路 Y において、L U T 格納メモリ 3 7 0 は、表示特性補正集積回路 Y の内部に備えられているが、本発明はこれに限られるものではない。例えば、L U T 格納メモリ 3 7 0 は、表示特性補正集積回路 Y の外部に設置されていてもよい。この場合、V T 特性補正回路 3 6 0 は、上述の高機能版液晶制御部 3 0 0 A の動作処理または低機能版液晶制御部 3 0 0 B の動作処理において、V T 特性補正回路 3 6 0 は、外部に設置された L U T 格納メモリ 3 7 0 からルックアップテーブル L U T 1 またはルックアップテーブル L U T 2 を読み出す。なお、本変形例のように、L U T 格納メモリ 3 7 0 をシリアル R O M として用いることが好ましい。このようにすれば、L U T 格納メモリ 3 7 0 が表示特性補正集積回路 Y の外部に設置されている場合であっても、ルックアップテーブル L U T 1 またはルックアップテーブル L U T 2 を素早く読み出すことができる。

40

#### 【 0 0 6 1 】

B 2 . 变形例 2 :

上記実施例の表示特性補正集積回路 Y において、画像データの各画素データに対して、V T 特性補正を行う場合には、ルックアップテーブル L U T 1 を用いて、V T 特性補正を

50

行うようにしているが、本発明はこれに限られるものではない。例えば、表示特性補正集積回路Yは、所定のメモリにVT特性補正を行うための計算式を有しており、画像データの各画素データに対して、VT特性補正を行う場合には、その計算式を用いて、VT特性補正を行うようにしてもよい。また、上記実施例の表示特性補正集積回路Yにおいて、画像データの各画素データに対して、VT特性補正と応答速度補正とを組み合わせた補正を行う場合には、ルックアップテーブルLUT2を用いて、VT特性補正と応答速度補正とを組み合わせた補正を行っているが、本発明はこれに限られるものではない。例えば、表示特性補正集積回路Yは、所定のメモリにVT特性補正と応答速度補正とを組み合わせた補正を行うための計算式を有しており、画像データの各画素データに対して、VT特性補正に加えて応答速度補正を行う場合には、その計算式を用いて、VT特性補正と応答速度補正とを組み合わせた補正を行っているが、本発明はこれに限られるものではない。以上のようにしても、上記実施例と同様の効果を奏することができる。

10

20

30

40

## 【0062】

## B3. 变形例3：

上記実施例の高機能版液晶制御部300Aの動作処理において、VT特性補正回路360は、ODEN信号が「High」の場合には、LUT格納メモリ370からルックアップテーブルLUT1を読み出し、表示画像データの各画素データにVT特性補正を行い、ODEN信号が「Low」の場合には、ルックアップテーブルLUT2を読み出し、VT特性補正と応答速度補正とを組み合わせた補正を実行するようにしているが、本発明は、これに限られるものではない。例えば、VT特性補正回路360は、表示画像データの各画素データが入力されると、まず、LUT格納メモリ370からルックアップテーブルLUT1およびルックアップテーブルLUT2とを読み出し、ルックアップテーブルLUT1を用いて表示画像データの各画素データにVT特性補正を行いVT特性補正後画素データを作成し、また、ルックアップテーブルLUT2を用いて表示画像データの各画素データにVT特性補正と応答速度補正とを組み合わせた補正を行い、応答速度補正後画素データを作成する。そして、VT特性補正回路360は、ODEN信号入力端子IP2を介して入力されるODEN信号が「Low」の場合には、作成した画素データのうち、VT特性補正後画素データを選択し、そのVT特性補正後画素データを画像信号出力端子OPを介して画像信号VS2(1画素分)として液晶パネル駆動部400に出力するようにしてもよい。また、VT特性補正回路360は、ODEN信号入力端子IP2を介して入力されるODEN信号が「High」の場合には、作成した画素データのうち、応答速度補正後画素データを選択し、その応答速度補正後画素データを画像信号出力端子OPを介して画像信号VS2(1画素分)として液晶パネル駆動部400に出力するようにしてもよい。このようにしても本実施例の効果を奏することができる。

## 【0063】

## B4. 变形例4：

上記実施例の表示特性補正集積回路Yは、画像データの各画素データ単位で、VT特性補正、または、VT特性補正と応答速度補正とを組み合わせた補正を行うようにしているが、本発明は、これに限られるものではない。例えば、表示特性補正集積回路Yは、高機能版液晶制御部300Aの動作処理において、画像データ単位で、VT特性補正、または、VT特性補正と応答速度補正とを組み合わせた補正を行うようにしてもよい。また、表示特性補正集積回路Yは、低機能版液晶制御部300Bの動作処理において、画像データ単位で、VT特性補正を行うようにしてもよい。

## 【0064】

## B5. 变形例5：

上記実施例において、応答速度制御用集積回路Xまたは表示特性補正集積回路Yの各部は、ハードウェア的に構成されているものを、ソフトウェア的に構成するようにしてもよい。

## 【図面の簡単な説明】

## 【0065】

50

【図1】本発明の実施例としての表示特性補正集積回路Yの概略構成を示す説明図である。

【図2】本実施例としての表示特性補正集積回路Yを用いた液晶制御部300を備えた液晶表示装置100の概略構成を示す説明図である。

【図3】本実施例の高機能版液晶制御部300Aの概略構成を示す説明図である。

【図4】本実施例の低機能版液晶制御部300Bの概略構成を示す説明図である。

【符号の説明】

【0066】

100...液晶表示装置

200...信号処理部

300...液晶制御部

300A...高機能版液晶制御部

300B...低機能版液晶制御部

310...入力バッファ

320...応答速度補正判定回路

330...ラインバッファ

340...通信回路

345...制御回路

350...入力バッファ

360...V-T特性補正回路

370...LUT格納メモリ

375...制御回路

400...液晶パネル駆動部

500...液晶パネル

X...応答速度制御用集積回路

Y...表示特性補正集積回路

10

20

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 4 1 Q |

|             | G 0 9 G | 3/20 6 3 1 V |

|             | G 0 9 G | 3/20 6 5 0 A |

|             | G 0 2 F | 1/133 5 7 0  |

|             | G 0 2 F | 1/133 5 7 5  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示特性补正集成电路、液晶制御装置                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2006317514A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2006-11-24 |

| 申请号            | JP2005137170                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2005-05-10 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 金子英司                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 金子 英司                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/36 G09G3/20.611.F G09G3/20.621.F G09G3/20.621.M G09G3/20.680.G G09G3/20.641.Q<br>G09G3/20.631.V G09G3/20.650.A G02F1/133.570 G02F1/133.575                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H093/NA53 2H093/NA62 2H093/NC13 2H093/NC25 2H093/NC29 2H093/NC59 2H093/NC65 2H093/<br>/ND06 2H093/ND32 2H093/ND58 5C006/AA11 5C006/AF13 5C006/AF45 5C006/AF46 5C006/AF51<br>5C006/AF53 5C006/AF61 5C006/AF71 5C006/BC16 5C006/BF02 5C006/BF08 5C006/BF14 5C006/<br>/BF24 5C006/EB04 5C006/EB05 5C006/FA04 5C006/FA14 5C006/FA18 5C006/FA41 5C006/FA56<br>5C080/AA10 5C080/BB05 5C080/DD04 5C080/DD22 5C080/DD27 5C080/DD28 5C080/EE29 5C080<br>/JJ02 2H193/ZD23 2H193/ZH40 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

### 摘要(译)

低功能液晶控制装置和高功能液晶控制装置可以共同使用的集成电路，当被低功能液晶控制装置使用时，进行VT特性校正。提供一种高度通用的集成电路，当在高性能液晶控制装置中使用时，除了VT特性校正外，还可以执行VT特性校正或响应速度校正。一种用于校正液晶面板的VT特性的显示特性校正集成电路，其用于校正VT特性，从而根据由图像信号表示的图像数据的变化来提高液晶面板的显示的响应速度。另外，校正确定信号输入端子接收指示是否校正响应速度的校正确定信号，并且如果该校正确定信号指示响应速度没有被校正，当执行特性校正并且校正确定信号指示执行了响应速度校正时，通过组合VT特性校正和响应速度校正来校正图像数据。[选型图]图1