## (19) **日本国特許庁(JP)**

# (12)公開特許公報(A)

(11)特許出願公開番号

特開2006-209027 (P2006-209027A)

(43) 公開日 平成18年8月10日(2006.8.10)

| (51) Int.C1. |        |            | F I  |        |     | テーマコード (参考) |

|--------------|--------|------------|------|--------|-----|-------------|

| G02F         | 1/1368 | (2006.01)  | GO2F | 1/1368 |     | 2G036       |

| GO 1 R       | 31/00  | (2006.01)  | GO1R | 31/00  |     | 2H088       |

| G02F         | 1/13   | (2006, 01) | GO2F | 1/13   | 101 | 2HO92       |

|                                                                         | 審査請求 未請求 請求項の数 4 OL (全 9 頁) |

|-------------------------------------------------------------------------|-----------------------------|

| (21) 出願番号 特願2005-24501 (P2005-24501)<br>(22) 出願日 平成17年1月31日 (2005.1.31) | (71) 出願人 000103747          |

#### (54) 【発明の名称】液晶パネルの検査方法

## (57)【要約】

#### 【課題】

簡便に高効率に液晶パネルの欠陥を検出できる液晶パネルの検査方法を提供することである。

## 【解決手段】

本発明の実施の形態にかかる液晶パネルの検査方法は、ゲート線101と、ゲート線101と絶縁膜を介して互いに交差するように設けられたソース線102と、ゲート線101とソース線102と、ゲート線101とソース線102との交差点近傍に設けられたTFT103と、TFT103を介してソース線102と接続された画素電極104と、画素電極104と対向配置する対向電極106とを有する液晶パネルの検査方法であって、ソース線102に0.6msec以下のパルス幅のソース信号を供給し、ソース信号のパルス幅の0.2倍以下のパルス幅でTFT103をオン状態とするゲート信号をソース信号のパルスの後半で重複するようにゲート線101に供給し、欠陥部と正常部との透過率の差に基づいて不良となる液晶パネルを判別する

【選択図】 図2

#### 【特許請求の範囲】

## 【請求項1】

複数のゲート線と、

前記複数のゲート線と絶縁膜を介して互いに交差するように設けられた複数のソース線と、

前記複数のゲート線と前記複数のソース線との交差点近傍に設けられたスイッチング素子と、

前 記 ス イ ッ チ ン グ 素 子 を 介 し て 前 記 ソ ー ス 線 と 接 続 さ れ た 画 素 電 極 と 、

前記画素電極と対向配置する対向電極とを有する液晶パネルの検査方法であって、

前 記 複 数 の ソ ー ス 線 に 0 . 6 m s e c 以 下 の パ ル ス 幅 の ソ ー ス 信 号 を 供 給 し 、

前記ソース信号のパルス幅の 0 . 2 倍以下のパルス幅で前記スイッチング素子をオン状態とするゲート信号を前記ソース信号のパルスの後半で重複するように前記複数のゲート線に供給 し、

欠陥部と正常部との透過率の差に基づいて不良となる液晶パネルを判別する液晶パネルの検査方法。

#### 【請求項2】

前記ゲート信号と重複する前記ソース信号のパルスにおいて、前記ソース信号のパルスが前記重複するソース信号のパルスに切り替わるタイミングから、前記ゲート信号が立ち上がるタイミングまでの時間間隔が前記ソース信号のパルス幅の 0 . 5 ~ 0 . 7 倍の時間間隔である請求項 1 に記載の液晶パネルの検査方法。

## 【請求項3】

前記ゲート信号と重複する前記ソース信号のパルスにおいて、前記ゲート信号の立ち下がるタイミングから、前記重複するソース信号のパルスより前記ソース信号に切り替わるタイミングまでの時間間隔が、前記ソース信号のパルス幅の 0 . 1 ~ 0 . 3 倍の時間間隔である請求項 1 又は 2 に記載の液晶パネルの検査方法。

## 【請求項4】

前記ゲート信号は、周期が3.6msec以下である請求項1、2または3に記載の液晶パネルの検査方法。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、液晶パネルの検査方法に関する。

## 【背景技術】

## [0002]

近年、高度な映像・情報化社会の本格的な進展やマルチメディアシステムの急速な普及に伴い、液晶表示装置の重要性はますます増大している。液晶表示装置は、低消費電力・薄型・軽量などの利点を有することから、携帯端末機器などの表示装置として幅広く応用されている。このような液晶表示装置に用いられる液晶パネルは、例えば、格子状に形成された複数のソース線及び複数のゲート線と、マトリクス状に配列した画素電極と、ソース線及び画素電極に接続されたスイッチング素子であるTFT(Thin film transistor)とが形成されたTFTアレイ基板と、画素電極に対向する対向電極が形成された対向基板と、これら両基板の間に挟持された液晶とを有する。

## [0003]

液晶表示装置において表示を行う場合、ゲート線を介して、TFTを導通状態とするONレベルの走査信号を印加する。そして、TFTを導通状態にした状態で、ソース線を介して画素電極に階調に応じた表示信号を印加する。このようにして、画素電極と対向電極との間に、表示信号に応じた電荷を蓄積する。電荷蓄積後は、走査信号をOFFレベルとしTFTを非導通状態にしても、各電極における電荷の蓄積状態は、液晶容量や補助容量などによって保持される。

## [0004]

50

10

20

30

ところで、液晶表示装置は、その製造工程において高度な薄膜形成技術や微細加工技術が必要である。このため、TFTの特性不良やソース線と画素電極とのリーク、ソース線、ゲート線の欠損などの欠陥に起因する、液晶表示装置の表示不良を完全に抑制することは困難である。したがって、上述のような欠陥を製造工程の早い段階に発見し、製造損失を小さくすることが求められている。

#### [00005]

そこで、従来、液晶表示装置を駆動させる駆動ドライバを実装する前の、液晶パネルの 段階において点灯検査を行い、上述の欠陥を有する液晶パネルを後の工程に流すことを防 止していた(例えば、特許文献 1 参照。)。

【特許文献 1 】特開平 9 - 3 1 1 3 0 6 号公報

【発明の開示】

【発明が解決しようとする課題】

#### [0006]

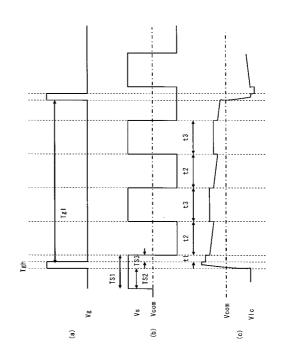

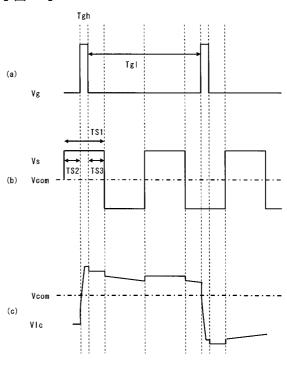

従来の液晶パネルの点灯検査について、図4を参照して説明する。図4は、液晶パネルのソース線及びゲート線に入力される検査信号の波形を示す図である。図4(a)では、ゲート信号によりゲート線に印加されるゲート電圧Vgについて図示している。また、同図(b)では、ソース信号によりソース線に印加されるソース電圧Vsについて図示している。同図(c)は、実際に液晶にかかる電圧V1cを示している。なお、液晶パネルの対向基板に形成された対向電極に供給される対向電圧Vcomについては直流電圧を用いている。

[0007]

図4(a)に示すように、複数のゲート線に供給されるゲート信号は、TFTを導通状態とするONレベルの信号と非導通状態とするOFFレベルの信号から成り、一定周期ごとにONレベルの信号が供給される矩形波である。また、図4(b)に示すように、複数のソース線に供給されるソース信号は、10 Vの電圧と0 Vの電圧から成り、Duty比50%で一定周期ごとに切り替わる矩形波である。また、対向電極に供給される対向電圧Vcomは、5 Vに固定されている。液晶には、対向電極を基準とするため、ゲート信号の周期に応じて±5 Vの電圧V1 cが交互に印加される。

[0008]

ソース信号の周波数は、例えば、120Hzであり、ゲート信号の周波数は75Hzである。また、図4に示すように、ソース信号のパルス幅TS1を1とすると、ゲート信号のパルス幅Tghは0.2である。また、ソース信号が立ち上がってからゲート信号が立ち上がるまでの期間TS2の比率は0.4であり、ゲート信号が立ち下がってからソース信号が立ち下がるまでの期間TS3は0.4である。すなわち、ソース信号のパルスの中央付近でゲート信号がONレベルの信号となる。

[0009]

このようにソース信号が所望の電圧となった期間において、ゲート線にゲート信号を供給し、TFTが導通状態となっている状態で、ソース線にソース信号を供給すると、画素電極には所望の電荷が蓄積され、画素電極と対向電極との間の液晶に図4(c)に示すような電圧が印加される。このような信号を入力すると、ソース線の断線、TFTの不良などの欠陥部においては、画素電極に所望の電荷が蓄積しないため、正常部との間に生じる透過率の差が生じる。したがって、このような欠陥を目視により検出し、不良パネルとして判別していた。

[0010]

また、ゲート線に供給されるゲート信号において、画素電極に電荷を蓄積しTFTを非導通状態としてから、次にTFTを導通状態とするオンレベルのゲート信号の立ち上がるまでの時間の間隔Tg1(以下、保持期間Tg1とする。)を長くして、TFTにとって厳しい条件下で欠陥検出を行うことによって、TFTの保持特性などによる電圧降下の影響を大きくし、不良パネルの検出を発見しやすくしていた。

[0011]

10

20

30

40

しかしながら、必要以上に保持期間Tg1を長くすることによって、オーバーキル(過剰検査)になる可能性があり、保持期間の決定は難しかった。また、この従来の液晶パネルの検査方法においては、液晶パネルの駆動条件が駆動ドライバを実装したモジュール状態における駆動条件とは異なる。このため、モジュール状態の検査において発見される欠陥を、液晶パネル状態の検査時点で見つけることができないという問題点があった。

#### [0012]

本発明は上記のような事情を背景になされたものであって、本発明の目的は、簡便に高効率に液晶パネルの欠陥を検出できる液晶パネルの検査方法を提供することである。

【課題を解決するための手段】

#### [0013]

本発明の第1の態様にかかる液晶パネルの検査方法は、複数のゲート線と、前記複数のゲート線と絶縁膜を介して互いに交差するように設けられた複数のソース線と、前記複数のゲート線と前記複数のソース線との交差点近傍に設けられたスイッチング素子と、前記スイッチング素子を介して前記ソース線と接続された画素電極と、前記画素電極と対向配置する対向電極とを有する液晶パネルの検査方法であって、前記複数のソース線に0.6msec以下のパルス幅のソース信号を供給し、前記ソース信号のパルス幅の0.2倍以下のパルス幅で前記スイッチング素子をオン状態とするゲート信号を前記ソース信号のパルスの後半で重複するように前記複数のゲート線に供給し、欠陥部と正常部との透過率の差に基づいて不良となる液晶パネルを判別する。これによって、簡便に高効率に欠陥を検出することが可能である。

[0014]

本発明の第2の態様にかかる液晶パネルの検査方法は、上記の検査方法において、前記ゲート信号と重複する前記ソース信号のパルスにおいて、前記ソース信号のパルスが前記重複するソース信号のパルスに切り替わるタイミングから、前記ゲート信号が立ち上がるタイミングまでの時間間隔が前記ソース信号のパルス幅の0.5~0.7倍の時間間隔である。これによって、欠陥を顕著にし、容易に欠陥を検出することができる。

[0015]

本発明の第3の態様にかかる液晶パネルの検査方法は、上記の検査方法において、前記ゲート信号と重複する前記ソース信号のパルスにおいて、前記ゲート信号の立ち下がるタイミングから、前記重複するソース信号のパルスより前記ソース信号に切り替わるタイミングまでの時間間隔が、前記ソース信号のパルス幅の0.1~0.3倍の時間間隔である。これによって、さらに欠陥を顕著にし、容易に欠陥を検出することができる。

[0016]

本発明の第4の態様にかかる液晶パネルの検査方法は、上記の検査方法において、前記 ゲート信号は、周期が3.6msec以下である。これによって、さらに欠陥を顕著にし 、容易に欠陥を検出することができる。

【発明の効果】

[0017]

本発明によって、簡便に高効率に液晶パネルの欠陥を検出できる液晶パネルの欠陥検査方法を提供できる。

【発明を実施するための最良の形態】

[0018]

以下に、本発明を適用可能な実施の形態について図を用いて説明する。以下の説明は、本発明の実施形態を説明するものであり、本発明が以下の実施形態に限定されるものではない。説明の明確化のため、以下の記載及び図面は、適宜、省略及び簡略化がなされている。また、当業者であれば、以下の実施形態の各要素を、本発明の範囲において容易に変更、追加、変換することが可能である。

[0019]

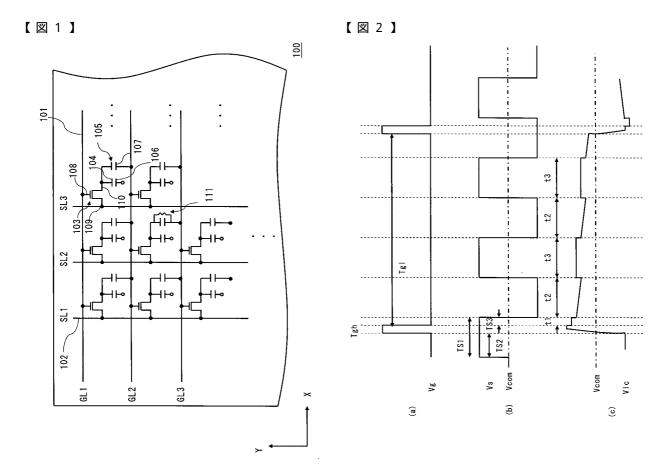

本発明の実施の形態にかかる液晶パネルの検査方法について、図1及び図2を参照して 説明する。図1は、本実施形態にかかる検査方法を適用する、一般的な液晶パネル100 10

20

30

40

の等価回路の一例を示す図である。以下の説明では、電圧印加状態で黒表示となるノーマリーホワイトの液晶パネルについて説明するが、電圧印加状態において白表示となるノーマリーブラックの液晶パネルについても、表示状態が反転するだけであり、本発明の検査方法を適用することが可能である。

## [0020]

液晶パネル100を形成する一方の基板であるTFTアレイ基板(不図示)上には、ゲート線GL101、ソース線SL102、TFT(Thin Film Transistor)103、画素電極104及び補助容量105などが形成されている。一方、液晶パネル100を形成する他方の基板である対向基板(不図示)上には、対向電極106及びカラーフィルタ(不図示)が形成されている。

[0021]

TFTアレイ基板上において、ゲート線GL101とソース線SL102とは、絶縁膜を介して、格子状に形成されている。また、ゲート線GL101とソース線SL102との交差点近傍には、TFT103が形成されている。TFT103のゲート端子108にはゲート線GL101が、ソース端子109にはソース線SL102が、TFT103のドレイン端子110には画素電極104がそれぞれ接続されている。また、ゲート線GL101の一部には補助容量105を形成するための補助容量電極107が形成されている。なお、ゲート線GL101とは独立に補助容量電極107を形成することもできる。

[0022]

一方、対向基板上には対向電極 1 0 6 及び R (赤)、 G (緑) B (青)のカラーフィルタが形成されている。対向電極 1 0 6 は、実際には画素電極 1 0 4 と対向するように対向基板の略全面に形成される透明電極である。なお、モノクロ表示の場合は、カラーフィルタを設けなくてもよい。

[0023]

図1において、111は高抵抗のITO残渣部を示しており、本実施の形態にかかる検査方法を用いて検出しようとする欠陥部である。ITO残渣は、画素電極104とゲート端子108、ドレイン端子110あるいは補助容量電極107などとの間でのショートの原因となり易い。ここでは、画素電極104と補助容量電極107との間に高抵抗の導通性異物であるITO残渣部111が存在する場合について図示している。

[0024]

ITO残渣部111は高い抵抗値を示すため、ITO残渣による画素電極104・補助容量電極107間のリークは小さい。このため、従来の液晶パネルの欠陥検査では、ITO残渣による欠陥を検出することが困難であった。すなわち、従来の液晶パネルの検査方法では、TFT自体のリーク及びソース線SL102の断線などの他の欠陥が検出されない場合は、ITO残渣部111が存在する液晶パネルであっても、良品と判別する場合があった。しかし、このようなITO残渣部111は、駆動ドライバを実装した後のモジュール状態で点灯検査を行った際に点欠陥として検出される。本発明においては、液晶パネル100に存在する欠陥がITO残渣部111であっても、駆動ドライバを実装する前の液晶パネル100の状態で検出することが可能である。

[0025]

本実施の形態にかかる欠陥の検出検査では、従来から広く知られているように、ゲート線 G L 1 0 1 及びソース線 S L 1 0 2 にそれぞれ検査信号を供給し、目視により欠陥の検出を行う。本発明において、従来と異なる点は検査信号の波形である。この検査信号については後に詳述する。検査信号の供給は、従来から広く知られているように、例えば、各ゲート線 G L 1 0 1、各ソース線 S L 1 0 2 それぞれをショートリングで短絡し、全ての配線に一括して供給することができる。また、各ゲート線 G L 1 0 1、各ソース線 S L 1 0 2 それぞれを短絡する大きな検査用電極を設けて、検査信号を供給する方法などを用いることも可能である。なお、液晶パネルの対向基板に形成された対向電極に供給される対向電圧については図示しない直流電圧を用いることができる。

[0026]

10

20

30

20

30

40

50

ONレベルのゲート信号がゲート線GL101を介して、TFTのゲート端子109に供給されると、TFT103は導通状態となる。そして、TFT103が導通状態である間にソース線SL102を介して、画素電極104にソース信号に応じた電荷が蓄積される。ゲート信号をOFFレベルとしTFTを非導通状態にしても、各画素電極104に蓄積された電荷は、液晶容量や補助容量105などによって保持される。欠陥が存在する部分では、黒表示のときには電位差が小さくなって黒表示より明るい中間調もしくは、白表示となる。このような表示不良を有する液晶パネルを不良品として目視によって判別することができる。

#### [0027]

ここで、図2を参照して、本実施の形態にかかる検査信号について説明する。図2は、図1に示すゲート線GL101及びソース線SL102に供給する検査信号の波形を示す図である。図2(a)では、ゲート信号によりゲート線GL101に印加されるゲート電圧Vgについて図示している。また、同図(b)では、ソース信号によりソース線SL102に印加されるソース電圧Vsについて図示している。また、同図(c)は、実際に液晶にかかる電圧V1cを示している。なお、液晶パネルの対向基板に形成された対向電極に供給される対向電圧Vcomについては直流電圧を用いている。

#### [0028]

図2(a)において、ゲート線GL101に供給するゲート信号は、例えば、周期が3.0msecの矩形波であり、TFT103を導通状態とするONレベルとするパルス(以下、ゲートパルスとする)の幅は0.12msecである。また、ゲートパルス間は、TFT103を非導通状態とするOFFレベルの信号である。ゲート信号のONレベルの期間が、画素電極104に電荷の蓄積を行う充電期間Tghである。すなわち、本実施の形態においては、充電期間Tghは0.12msecである。また、ゲート信号のOFFレベルの期間は、後述するように液晶にかかる電圧を保持する保持期間Tg1である。本実施の形態においては、保持期間Tg1は2.88msecである。

## [0029]

一方、図2(b)において、ソース線SL102に供給するソース信号は、例えば、周期が1.2msecで、10V(Highレベル)と0V(Lowレベル)の電圧がDuty比50%で繰り返し供給される矩形波の信号である。すなわち、ソース線SL102には、10Vの電圧が0.6msecの間供給され、その後0Vの電圧が0.6msecの間供給され、これを1周期として繰り返し供給される。また、対向電極に供給される対向電圧Vcomは、5Vに固定されている。液晶には、対向電極を基準とするため、ゲート信号の周期に応じて理想的には±5Vの電圧が交互に印加される。

## [ 0 0 3 0 ]

+ 1 0 V を画素電極 1 0 4 に書き込んでからソース信号が切り替わる直前までの期間(図 2 中、 t 1 の期間)では、ソース線 S L 1 0 2 と画素電極 1 0 4 との電圧差が小さいために、TFTのリーク、ソース線 S L 1 0 2 ・画素電極 1 0 4 間のリークは小さい。その後、ゲート信号が O F F レベルの信号になってから、ソース信号が L o w レベルに切り替わると、ソース・ドレイン間の結合容量によって、液晶にかかる電圧は降下する。

#### [0031]

そして、ゲート信号がOFFレベルで、ソース信号が0Vの間(図2中、t2の期間)においては、ソース線SL102と画素電極104との電圧差が大きくなる。このため、TFTの保持特性、ソース・画素間のリークによる電圧降下の影響が大きくなり、液晶にかかる電圧が小さくなる。また、ゲート信号がOFFレベルである間に、ソース信号が10Vに切り替わると、ソース・ドレイン間の結合容量によって、液晶にかかる電圧は上昇する。ソース信号が10Vの間(図2中、t3期間)においては、ソース線SL102と画素電極104との電圧差が小さいため、ソース線SL102・画素電極104間のリークによる電圧降下はほとんど生じない。

#### [0032]

従来は、この保持期間の電圧降下によって、ITO残渣部111以外のTFT保持特性

10

20

30

40

50

不良などのリークが大きい画素の透過率が変化する欠陥を有する液晶パネルを不良として 判別していた。本実施の形態においては、ITO残渣部111が存在する画素の書き込み 不足によって、欠陥を検出することを特徴としている。

[0033]

ここで、図2(b)を参照して、ゲートパルスのタイミングについて詳細に説明する。ここでは、ゲートパルスと重複するHighレベルのソース信号の1パルスについて説明するが、ソース信号がLowレベルあっても同様である。ソース信号の1/2周期、すなわちHighレベルの期間をTS1とし、ソース信号が立ち上がった後にゲート信号が立ち上がるまでの期間をTS2とし、ゲート信号が立ち下がった後にソース信号が立ち下がるまでの期間をTS3とする。ゲート信号の立ち上がりのタイミングは、ソース信号の立ち上がりのタイミングよりも後である。また、ゲート信号の立ち下がりのタイミングは、ソース信号の立ち下がりのタイミングよりも先である。

[0034]

TS1は、0.6msecより短いことが好ましい。すなわち、ソース信号の周期は1.2msec以下でDuty比が50%であることが好ましい。TS1を1とすると、充電期間TghはTS1の0.2倍以下であることが好ましい。また、TS2は0.5~0.7倍であり、TS3は0.1~0.3倍であることが好ましい。すなわち、ソース信号の周期をモジュール駆動時の周期に近づけ、ゲート信号のONレベルの期間(充電期間Tgh)を短くし、ゲートパルスの入力タイミングをソース信号のHighレベルのパルスのうちの後半とする。

[0035]

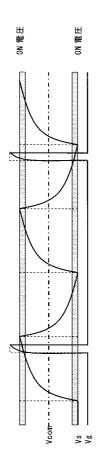

ゲート信号のONレベルの期間(充電期間Tgh)を短くすることによって、画素電極104に蓄積される電荷は減少する。また、ソース信号及びゲート信号の周期を短るでによって画素が顕著によって画素の書き換え速度を上げると、リークにより充電されない画素が顕著にいる。このとき、駆動波形にはなまりが生じる。図3は、図2におけるゲート信号及びソース信号の実際の波形を示す図である。本実施の形態においては、周波数を高くしてりるため、ゲート線GL101及びソース線SL102にパルス間隔を短くしているため、ゲート線GL101及びソース線SL102にパルスの入力をソース信号のHighレベルのパルスの後半とすることによって、画素電極104に蓄積される電荷を安定させることができる。このため、通常の画素電極104には、所望の電荷が蓄積されず、所望の電圧が液晶に印加されない。したがって、点灯の画素が明るい輝点として視認され、この液晶パネル100を不良として判別することができる。

[0036]

また、 TS3 は TS1 の 0 . 1 ~ 0 . 3 倍 であることが好ましい。 すなわち、ソース信号が切り替わる前に、ゲート信号を立ち下げるようにする。

[0037]

また、本実施の形態においては、ゲート信号がOFFレベルの保持期間Tg1において、ソース信号が5回切り替わるようにしたが、これに限定されるものではない。ソース信号が3回切り替わるようしてもよい。ゲート信号がONレベルとなるパルスの立ち上がるタイミングで、画素電極に10V(Highレベル)と0V(Lowレベル)のソース信号が交互に供給されるようにすればよい。ソース・ドレイン間の結合容量により、液晶にかかる電圧はソース信号が立ち上がるときには増加し、ソース信号が立ち下がるときには減少するが、保持期間Tg1の間のソース信号の切り替わり回数によって、電圧降下の実効値が変化するものではないためである。

【図面の簡単な説明】

[0038]

【図1】本実施の形態における検査方法を適用する液晶パネルの一例を示す等価回路である。

10

- 【図2】本実施の形態における検査信号波形及びタイミングの一例を示す図である。

- 【図3】本実施の形態における検査信号波形及びタイミングの一例を示す図である。

- 【図4】従来の検査信号波形およびタイミングを示す図である。

## 【符号の説明】

## [0039]

- 100 液晶パネル

- 101 ゲート線GL

- 102 ソース線SL

- 103 TFT

- 104 画素電極

- 1 0 5 補助容量

- 106 対向電極

- 1 0 7 補助容量電極

- 108 ゲート端子

- 109 ソース端子

- 1 1 0 ドレイン端子

- 111 ITO残渣部

【図3】

【図4】

| 专利名称(译)     | 检查液晶面板的方法                                                                                                                                                                        |         |            |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号     | JP2006209027A                                                                                                                                                                    | 公开(公告)日 | 2006-08-10 |  |  |  |

| 申请号         | JP2005024501                                                                                                                                                                     | 申请日     | 2005-01-31 |  |  |  |

| 申请(专利权)人(译) | 光王公司                                                                                                                                                                             |         |            |  |  |  |

| [标]发明人      | 平石昭一                                                                                                                                                                             |         |            |  |  |  |

| 发明人         | 平石 昭一                                                                                                                                                                            |         |            |  |  |  |

| IPC分类号      | G02F1/1368 G01R31/00 G02F1/13                                                                                                                                                    |         |            |  |  |  |

| FI分类号       | G02F1/1368 G01R31/00 G02F1/13.101                                                                                                                                                |         |            |  |  |  |

| F-TERM分类号   | 2G036/AA25 2G036/BA33 2G036/CA12 2H088/FA13 2H088/HA06 2H088/HA08 2H088/MA20 2H092 /JA24 2H092/MA58 2H092/NA30 2H092/PA06 2H192/AA24 2H192/DA02 2H192/EA43 2H192/HB03 2H192/HB23 |         |            |  |  |  |

| 外部链接        | Espacenet                                                                                                                                                                        |         |            |  |  |  |

|             |                                                                                                                                                                                  |         |            |  |  |  |

## 摘要(译)

[问题] 本发明的目的是提供一种用于检查液晶面板的方法,其可以容易且有效地检测液晶面板中的缺陷。[解决方案] 根据本发明实施例的液晶面板检查方法包括栅极线101,设置成通过绝缘膜与栅极线101相交的源极线102,栅极线101和源极线102。 像素电极104通过TFT 103连接到源极线102,并且对电极106被布置为面对像素电极104。 脉冲宽度为0.6毫秒以下的源信号被提供给102,并且以脉冲宽度为源信号的脉冲宽度的0.2倍以下的宽度导通TFT 103的栅极信号在源信号脉冲的后半部分重叠。 将有缺陷的液晶面板供应到101,并且基于有缺陷的部分与正常部分之间的透射率的差来确定有缺陷的液晶面板。 [选择图]图2