## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-76731 (P2008-76731A)

(43) 公開日 平成20年4月3日(2008.4.3)

プソンイメージングデバイス株式会社内

ND49 ND52 NE07 5C006 AA16 BB16 BC20 BF01 BF04 BF26 BF27 FA43

NC15 NC24 NC34 ND06 ND39

最終頁に続く

F ターム (参考) 2H093 NA16 NA43 NA53 NC09 NC13

| (51) Int.Cl. |       |               | F I            |          |             | テーマコー     | ド(参考)  |

|--------------|-------|---------------|----------------|----------|-------------|-----------|--------|

| G09G         | 3/36  | (2006.01)     | GO9G           | 3/36     |             | 2H093     |        |

| G02F         | 1/133 | (2006.01)     | GO2F           | 1/133    | 505         | 5C006     |        |

| G09G         | 3/20  | (2006.01)     | GO9G           | 3/20     | 621L        | 5C080     |        |

|              |       |               | GO9G           | 3/20     | 623F        |           |        |

|              |       |               | GO9G           | 3/20     | 623G        |           |        |

|              |       |               | 審査請求 未         | 請求請求     | ド項の数 7 OL   | (全 19 頁)  | 最終頁に続く |

| (21) 出願番号    |       | 特願2006-255611 | (P2006-255611) | (71) 出願丿 | √ 304053854 |           |        |

| (22) 出願日     |       | 平成18年9月21日    | (2006. 9. 21)  |          | エプソンイメ      | ージングデバイ   | ス株式会社  |

|              |       |               |                |          | 長野県安曇野      | 市豊科田沢69   | 25     |

|              |       |               |                | (74)代理/  | 人 100095728 |           |        |

|              |       |               |                |          | 弁理士 上柳      | T 雅誉      |        |

|              |       |               |                | (74)代理力  | 人 100127661 |           |        |

|              |       |               |                |          | 弁理士 宮坂      | <b>一彦</b> |        |

|              |       |               |                | (72) 発明者 | 皆 小橋 裕      |           |        |

|              |       |               |                |          | 東京都港区海      | 松町二丁目4番   | 1号 三洋エ |

(54) 【発明の名称】データ線駆動回路、液晶表示装置およびこれを搭載した電子機器

## (57)【要約】

【課題】高精細で低消費電力なDAC内蔵データ線駆動 回路を実現する。

【解決手段】順次選択回路の第1出力端子が選択されたタイミングでメモリ回路内に基準電位を書き込み、第2出力端子が選択されたタイミングで信号をメモリ回路に書き込む。さらにメモリ回路をダイナミック型で構成することで素子数を低減して高精細化を実現する。

## 【選択図】図4

#### 【特許請求の範囲】

#### 【請求項1】

順次選択される複数の出力端子を有した順次選択回路と、

複数の単位メモリ回路を有したメモリ回路と、

映像信号配線と、

を備えたデータ線駆動回路であって、

前記複数の単位メモリ回路のそれぞれは、前記順次選択回路の前記複数の出力端子のうちの2つであるそれぞれの第1出力端子と第2出力端子とに接続されていて、

前記複数の単位メモリ回路のそれぞれについて、

前記第1出力端子が選択されたタイミングで第1の基準電位が前記単位メモリ回路内の第1ノードへ書き込まれ、

前記第2出力端子が選択されたタイミングで前記単位メモリ回路に前記映像信号配線のデータがレベルシフトされて書き込まれる

ことを特徴としたデータ線駆動回路。

## 【請求項2】

前記複数の単位メモリ回路のそれぞれは、蓄積容量にデータを書き込むことでメモリを 行ういわゆるダイナミック型のメモリであるとともに、前記第2出力端子が選択されたタ イミングで前記蓄積容量に書き込むことでメモリ動作を行うように構成されている ことを特徴とした請求項1に記載のデータ線駆動回路。

## 【請求項3】

前記複数の単位メモリ回路のそれぞれは、前記順次選択回路の前記複数の出力端子の更に別なる一つである第3出力端子に接続されているとともに、前記第3出力端子が選択されたタイミングで前記単位メモリ回路の一部への電源供給を停めるように構成されていることを特徴とした請求項1または2に記載のデータ線駆動回路。

#### 【請求項4】

前記第1の基準電位は前記複数の単位メモリ回路のそれぞれの出力信号の高電位時の電圧値VHと低電位時の電圧値VLの間の電圧値であって、

前記複数の単位メモリ回路のそれぞれは昇圧用容量を有していて、

前記昇圧用容量の一端に前記第1ノードが接続されてなり、前記昇圧用容量の他端に第2ノードが接続されてなり、

前記第1出力端子が選択されるタイミングで第2の基準電位が前記第2ノードへ書き込まれ、

前記第2出力端子が選択されるタイミングで前記映像信号配線と前記第2ノードが電気的に接続される

ことを特徴とした請求項1から3のいずれか一つに記載のデータ線駆動回路。

#### 【請求項5】

前記データ線駆動回路を構成する能動素子はガラス基板上に形成された薄膜トランジスターであることを特徴とした請求項1から4のいずれか一つに記載のデータ線駆動回路。

#### 【請求項6】

請 求 項 1 か ら 5 の い ず れ か 一 つ に 記 載 の デ ー タ 線 駆 動 回 路 を 備 え た 液 晶 表 示 装 置 。

【請求項7】

請求項6に記載の液晶表示装置を備えた電子機器。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は例えば、データ線駆動回路、液晶表示装置およびこれを搭載した電子機器に関する。

## 【背景技術】

## [0002]

近 年 、 低 温 ポ リ シ リ コ ン 薄 膜 形 成 技 術 を 用 い て ガ ラ ス 基 板 上 に 薄 膜 ト ラ ン ジ ス タ ー ( T

20

10

30

40

FT)回路を形成する、いわゆるSystem On G1ass(SOG)技術があれた開発されており、液晶ディスプレイのガラス基板上にドライバー回路を内蔵置の開発するいはモノシリックドライバーと呼ばれる表示装置のの開発を開発した。なり、特にDAC(Digita1 Ana1ogue Convert セスクロ路を含むデータ線駆動回路をガラス基板上に形成することでドライバーエスの両のの構成で安価になることが期待されている。このようなDAC回路であるいは水平駆動回路(あるいは水平駆動回路、H‐DRIVERなどと称される)をガララ路に構成する場合、順次選択回路(あるいはシフトレジスタ回路)、第1メモリ回路の方のははサングラッチ回路)、第2メモリ回路によっての場になり、部のメモリの路によってで送信されるデジタル映像信号を順次選択回路によってで送信されるデジタルで取り込むためのメモリであって、第2メモリ回路は点順次である。このような液晶表示装置の詳細な構成例としては特許文献1などが提案されている。

[00003]

ここで第1メモリ回路に入力される映像デジタルデータの信号振幅は消費電力の低減およびドライバーICのコスト低減の両面からなるべく低いことが要請され、2.5~5.0 V程度であることが望ましい。一方、低温ポリシリコン薄膜形成技術で製造したTFTの閾値電圧はMOS-ICのトランジスターに比べて高いことから、DAC回路が精度よく動作するために第2メモリ回路からの出力電位振幅は6~12 V程度であることが要求される。この両者の要求から、第1メモリ回路もしくは第2メモリ回路で電位のレベルシフトを行う必要がある。これを実現する回路構成として、特許文献2、特許文献3などが提案されている。これらはいずれも第1メモリ回路及び第2メモリ回路の構成としてS-RAM(Static Random Access Memory)回路を応用したものである。

[0004]

【特許文献1】特開2000-242209号公報

【特許文献2】特開2000-221926号公報

【特許文献3】特開2000-221929号公報

【発明の開示】

【発明が解決しようとする課題】

[0005]

駆動回路一体型液晶表示装置においては複雑な回路をICに比べ10倍程度大きなデザインルールで形成する必要があるため、精細度が低いものしかできないと言う課題がある。そこで、第1メモリ回路および第2メモリ回路についてもD-RAM(DynamicRandom Access Memory)を用いて回路構成を簡略化すればより高精細な駆動回路一体型液晶表示装置を製造できる。しかしながら、D-RAM構成ではレベルシフトを行うことが難しいため、従来はS-RAM回路の構成が提案されてきた。本発明は上記の問題点に鑑み、その目的の一つは、D-RAM構成によるレベルシフト可能なデータ線駆動回路を提案することである。

【課題を解決するための手段】

[0006]

本発明のある態様によれば、データ線駆動回路が、順次選択される複数の出力端子を有した順次選択回路と、複数の単位メモリ回路を有したメモリ回路と、映像信号配線と、を備えている。そして、前記複数の単位メモリ回路のそれぞれは、前記順次選択回路の前記複数の出力端子のうちの2つであるそれぞれの第1出力端子と第2出力端子とに接続されている。さらに、前記複数の単位メモリ回路のそれぞれについて、前記第1出力端子が選択されたタイミングで前記単位メモリ回路内の第1ノードへ書き込まれ、前記第2出力端子が選択されたタイミングで前記単位メモリ回路に前記映像信号配線のデータがレベルシフトされて書き込まれる。

10

20

30

### [0007]

本回路構成により、素子数の多いS-RAM回路の構成を用いずとも映像信号のレベルシフトが可能になり、高精細化対応が可能でかつ低消費電力なデータ線駆動回路が構成できるようになる。

## [00008]

本発明の他の態様によれば、前記複数の単位メモリ回路のそれぞれは、蓄積容量にデータを書き込むことでメモリを行ういわゆるダイナミック型のメモリであるとともに、前記第2出力端子が選択されたタイミングで前記蓄積容量に書き込むことでメモリ動作を行うように構成されている。

## [0009]

前記の構成をとればレベルシフトがS-RAM構成でなくても可能であるから、より素子数の少ないダイナミック型のメモリを用いることができ、かつレベルシフトと同一タイミングで書き込みを行うことで映像信号より高い電圧を書き込み、出力電圧を高くすることが可能である。

### [0010]

本発明のさらに他の態様によれば、前記複数の単位メモリ回路のそれぞれは、前記順次選択回路の前記複数の出力端子の更に別なる一つである第3出力端子に接続されているとともに、前記第3出力端子が選択されたタイミングで前記単位メモリ回路の一部への電源供給を停めるように構成されている。

## [0011]

このような動作によってメモリ回路内のレベルシフタのリーク電流を停めることで消費 電流を低減できる。

#### [0012]

本発明のさらに他の態様によれば、前記第1の基準電位は前記複数の単位メモリ回路のそれぞれの出力信号の高電位時の電圧値VHと低電位時の電圧値VLの間の電圧値である。そして、前記複数の単位メモリ回路のそれぞれは昇圧用容量を有していて、前記昇圧用容量の一端に前記第1ノードが接続されてなり、前記昇圧用容量の他端に第2ノードが接続されてなり、前記第1出力端子が選択されるタイミングで第2の基準電位が前記第2ノードへ書き込まれ、前記第2出力端子が選択されるタイミングで前記映像信号配線と前記第2ノードが電気的に接続される。

### [0013]

このような回路構成により、 D - R A M 型メモリと組み合わせてもレベルシフタ回路として動作し、かつリーク電流が生じないため消費電流が少ない。

### [0014]

本発明のさらに他の態様によれば、前記データ線駆動回路を構成する能動素子はガラス 基板上に形成された薄膜トランジスターである。

## [0015]

ガラス基板上に形成された閾値電圧が高い薄膜トランジスターでDAC回路を構成するとDAC回路に入力するデジタル信号は高い電位振幅を必要とするが、本回路構成によって映像信号は低い電位振幅のままにおさえることができるから、ガラス基板上に形成された薄膜トランジスターで駆動回路を一体形成する際にも低消費電力な回路とすることが出来るため、DAC回路をガラス基板上に形成することでコストを安価に出来る。

## [0016]

また、上記のデータ線駆動回路を備えた液晶表示装置、およびその液晶表示装置を備えた電子機器も提案する。上述のデータ線駆動回路を内蔵した液晶表示装置は従来のものにくらべ高精細で低消費電力であり、ガラス基板上に形成することができるからコストが低くなる。電子機器に応用すれば安価でバッテリー駆動時間が長く、表示品位の高い電子機器を実現できる。

## [0017]

上記のような構成によれば、メモリ回路に素子数の多いS-RAMでなくD-RAMを

10

20

30

40

20

30

40

50

用いることができ、かつ映像信号からの入力信号振幅は低いままDAC回路への出力データ振幅を大きくすることができるため、高精細で低消費電力なデータ線駆動回路を低温ポリシリコンTFT回路で構成できる。

【発明を実施するための最良の形態】

## [0018]

(実施例1)

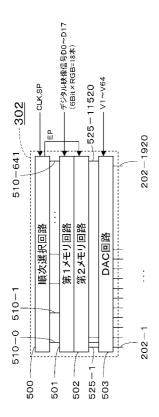

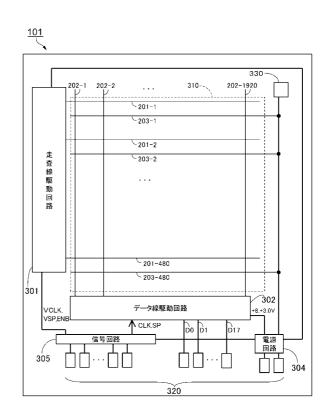

図1は本発明の第1の実施例を実現するための6BitDAC内蔵VGA液晶用データ線駆動回路302のブロック図である。

## [0019]

データ線駆動回路 3 0 2 は順次選択回路 5 0 0 、第 1 メモリ回路 5 0 1、第 2 メモリ回路 5 0 2、 D A C 回路 5 0 3 よりなる。順次選択回路 5 0 0 は 6 4 2 個の出力端子 5 1 0 - 0 ~ 6 4 1 を有し、適切なクロック信号 C L K、スタートパルス信号 S P を供給されることにより出力端子 5 1 0 - 0 ~ 6 4 1 に順次選択信号を供給し、出力端子 5 1 0 - 6 4 1 を選択した後に終端信号 E P を第 2 メモリ回路 5 0 2 へ出力する。

### [0020]

第1メモリ回路501は11520個の単位メモリ回路520-1~11520よりなるメモリ回路であって、18本のデジタル映像信号D0~D17が入力される。デジタル映像信号D0~D17の電位は0/3Vの信号である。順次選択回路500から出力端子510-kに選択信号が出力されると、各デジタル映像信号D0~D17に接続された18個の単位メモリ回路520-k \* 18-17~k \* 18に0/3Vの信号が書き込まれる。次のタイミングで出力端子510-k + 1が選択されると、単位メモリ回路520-a \* 18-17~a \* 18の信号はメモリ内容を保持したまま0/8Vの信号にレベルシフトされる。同時に、単位メモリ回路520-(a + 1) \* 18-17~(a + 1) \* 18117~(a + 1) \* 18117~(a + 1) \* 18にデジタル映像信号D0~D17より0/3Vの信号が書き込まれている。なお、aは1以上639以下の整数である。

## [0021]

また、第2メモリ回路502は11520個の単位メモリ521-1~11520よりなるメモリ回路であって、順次選択回路500からの終端信号EPが選択されたタイミングで第1メモリ回路501の単位メモリ回路520-nの内容をコピーし、次のEP信号が選択されるまでの間、その内容を保持したまま出力端子525-nに出力しつづける。これによってDAC回路503は線順次書き込みが可能になるのである。

## [0022]

DAC回路503は第2メモリ回路502からの出力端子525 1~11520を元にデジタル・アナログ変換を行い、データ線202-1~1920ヘアナログ電位を書き込む。ここでDAC回路503は6Bitのデジタル・アナログ変換であって、出力端子525-p\*6までの6Bitのデータをもとにデータ線202-pへのアナログ電位に変換する。なお、pは1以上1920以下の整数である。【0023】

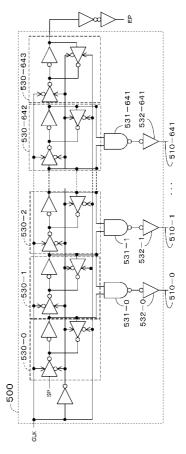

図2は順次選択回路500の回路図である。644段のD-FF回路530-0~643が直列に接続されてなり、D-FF回路530-nとD-FF回路530-n+1の出力端子がNAND回路531-nの入力段に接続され、NAND回路531-nの出力が出力がコンバーター回路532-nに接続され、インバーター回路532-nの出力が出力端子510-kに繋がる。初段のD-FF回路530-0の入力端子はスタートパルス信号SPに接続され、る。これらの構成回路は全て+8Vと0Vの電源に接続される。これらの構成回路は全て+8Vと0Vの電源に接続される。スタートパルス信号SPは35μ秒周期でパルス長54n秒の矩形かの矩形クロック信号であって+8V/0Vのレベルの信号である。このように構成することで、出力端子510-0 出力端子510-2...と各出力端子が順次54n秒ずつ選択され、出力端子510-641が選択された後、EP信号が108

n 秒選択される。なお、順次選択回路としては本実施例であげたような D - F F 回路を用いた構成の他、 S - R A M ラッチや R S - フリップフロップを用いた構成など、既知のいかなる順次選択回路を用いても差し支えない。また、反転表示を実現するため、双方向転送回路を組み込んでもよい。

## [0024]

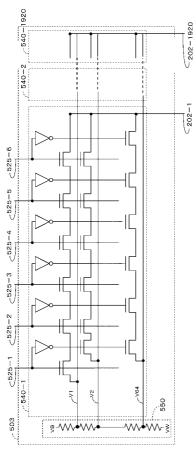

図3はDAC回路503の回路図である。DAC回路503は6Bitのデジタル・アナログ変換回路であり、1920個のDACユニット回路540・1~1920と基準電位発生源550は反転する2つの電位VBとVWを表ったが、これを適当な抵抗で分割することで64個の基準電位V1~V64を発生する。これに不分割することで64個の基準電位V1~V64を発生する。これに反転する。これによって0月期は70回路503から出力される信号は1H期間毎に反転する。これに反転動が実現される。DACロであり、同期は70回路503から出力される信号は1H期間毎に反転する。1H反転駆動が実現される。DACコニット回路540・pは第2メモリ回路502からの出力端子525・p\*66・5~p\*6に接続され、その信号に応じてV1~V64の中から一つの電位を選択(デコータ路1にでデータ線202・pに出力する。これによって6Bitのデジタル・アナログでカウでである。なお、本実施例では基準電位発生源550の出力を直接データ線202・pにおされる。なお、本実施例では基準電位発生源550の出力を直接データ線202・pにおされる。なお、本実施例では基準電位発生源550の出力を直接データ線202・同にいる構成にしても差し支えない。また、DAC回路として本実施例であげた構成の他方式の構成にしても差し支えない。また、DAC回路として本実施例であらゆる他方式の日本にはみ合わせて構わない。なお、pは1以上1920以下の整数である。

#### [0025]

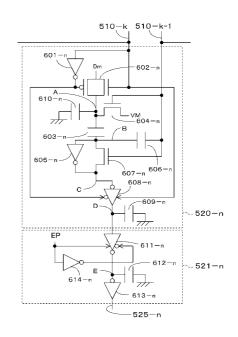

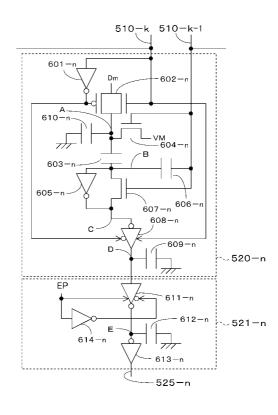

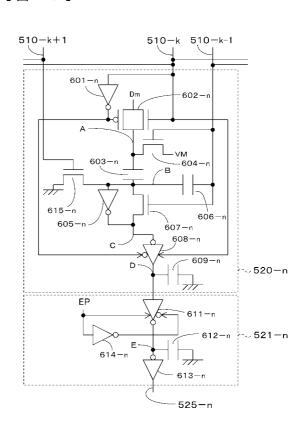

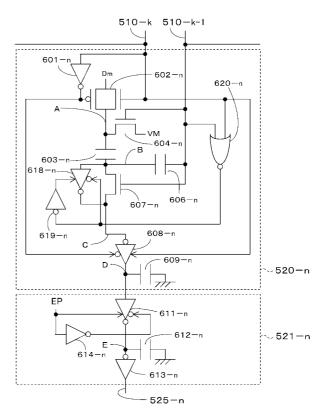

図 4 は第 1 メモリ回路 5 0 1 の単位メモリ回路 5 2 0 - n および第 2 メモリ回路 5 0 2 の単位メモリ回路 5 2 1 - n の回路構成である。

#### [0026]

単位メモリ回路 5 2 0 - n は、第 1 インバーター回路 6 0 1 - n と、第 1 伝送ゲート 6 0 2 - n と、第 1 蓄積容量 6 0 3 - n と、第 1 トランジスター 6 0 4 - n と、第 2 インバーター回路 6 0 5 - n と、第 2 蓄積容量 6 0 6 - n と、第 2 トランジスター 6 0 7 - n と、第 1 クロックド・インバーター 6 0 8 - n と、第 3 蓄積容量 6 0 9 - n と、第 4 蓄積容量 6 1 0 - n と、を備えている。

### [0027]

第1インバーター回路601-nには、出力端子510-kが入力されていて、出力端子510-kに現れる信号を反転し、反転によって得た信号を出力する。第1伝送ゲートの2つのゲート入力には、出力端子510-kと、第1インバーター回路601-nの出力と、が接続されている。そして、第1伝送ゲート602-nは、出力端子510-kの選択/非選択に応じて、映像信号配線上に現れるデジタル映像信号Dmを、ノードAへ伝送するように構成されている。なお、ノードAは、本実施例では、第1伝送ゲート602-nの出力と、第1トランジスター604-nのソースと、第1蓄積容量603-nの一端と、第4蓄積容量610-nの一端と、が接続された部分である。

## [0028]

ここで、第4蓄積容量610-nの他端は、本実施例では接地されている。また、第1トランジスター604-nのドレインは、基準電位VMに接続されている。そして、第1トランジスター604-nのゲート入力には、出力端子510-k-1が接続されている。なお、出力端子510-k-1は、出力端子510-kの直前に選択される出力端子である。

## [0029]

第1蓄積容量603-nの他端は、ノードBに接続されている。ノードBは、本実施例では、第1蓄積容量603-nの他端と、第2蓄積容量606-nの一端と、第2インバーター回路605-nの入力と、第2トランジスター607-nのソースと、が接続された部分である。なお、第2蓄積容量606-nの他端は、出力端子510-k-1が接続されている。また、後の説明から明らかになるように、第1蓄積容量603-nは、「昇

10

20

30

40

圧用容量」として機能する。

#### [0030]

第2トランジスター607-nのゲート入力は出力端子510-k-1に接続されていて、第2トランジスター607-nのドレインは第2インバーター回路605-nの出力に接続されている。つまり、この構成によれば、出力端子510-k-1が選択される場合に、第2トランジスター607-nは第2インバーター回路605 nの入力と出力とを短絡することになる。

## [0031]

なお、第2インバーター回路605-nと、第2トランジスター607-nのドレインと、が互いに接続された部分は、さらに第1クロックド・インバーター608-nの入力に接続されている。そして本実施例では、これら第2インバーター回路605-nの出力と、第2トランジスター607-nのドレインと、第1クロックド・インバーター608-nと、が接続された部分がノードCである。

## [ 0 0 3 2 ]

第1クロックド・インバーター608-nは、出力端子510-kの選択/非選択に応じて、第2インバーター回路605-nの出力に現れる信号を反転し、その反転によって得た信号をノードDに供給する。ここで、ノードDは、本実施例では、第1クロックド・インバーター608-nの出力と、第3蓄積容量609-nの一端と、単位メモリ回路521-nにおける第2クロックド・インバーター611-nの入力と、が接続された部分である。なお、第3蓄積容量609-nの他端は本実施例では接地されている。

#### [0033]

単位メモリ521-nは、第3インバーター回路614-nと、第2クロックド・インバーター611-nと、第5蓄積容量612-nと、第4インバーター回路613-nと、を備えている。

## [ 0 0 3 4 ]

第2クロックド・インバーター611-nは、終端信号EPに応じて、ノードD上に現れた信号を反転し、その反転によって得た信号をノードEに供給するように構成されている。ここで、ノードEは、本実施例では、第2クロックド・インバーター611-nの出力と、第5蓄積容量612-nの一端と、第4インバーター回路613-nの入力と、が接続された部分である。なお、第5蓄積容量の他端は本実施例では接地されている。

### [0035]

ここで、第3インバーター回路614-n は、終端信号EPを反転し、その反転によって得た信号を第2クロックド・インバーター611-n の負のクロック端子(ゲート入力の一つ)に供給する。なお、第2クロックド・インバーター611-n の正のクロック端子には、終端信号EPが供給されている。

#### [0036]

第4インバーター回路613 - nは、ノードEに現れた信号を反転して、反転した信号を出力端子525 - nに供給するように構成されている。

#### [0037]

このような構成を有する単位メモリ回路 5 2 0 - n と単位メモリ回路 5 2 1 - n とは、 以下のように動作する。

#### [0038]

まず、出力端子 5 1 0 - k - 1 (第1出力端子)が選択される(= High電位となる)と、第1トランジスター604 - n及び第2トランジスター607 - nがONし、ノードA (第2のノード)には電位 V M (第2基準電位)が充電される。なお、ここで k = 1 ~ 6 4 0 であって、n = (k - 1) \* 1 8 + m + 1、m = 0 ~ 1 7 であり、一つの出力端子 5 1 0 - kに対して 1 8 個の単位メモリが同時に動作する。m = 0 ~ 1 7 は外部から入力される 1 8 本のデジタル映像信号 D m (0 ~ 1 7)に対応しており、同時に選択される各単位メモリはそれぞれ接続されるデジタル映像信号が異なる。ここで電位 V M は映像信号 D 0 ~ D 1 7 のデータ H i g h 時の電位 (= 3 V)とデータ L o w 時の電位 (= 0 V)

10

20

30

40

20

30

40

50

の間のいずれかの電位が充電される。本実施例ではVM=0Vとする。また、第2インバーター回路605-nの入力端子と出力端子が第2トランジスター607-nによって短絡されるから、ノードB(第1のノード)には第2インバーター回路605-nの反転閾電圧(Vt、第1基準電位)が充電される。ここで反転閾電圧(Vt)はインバーターの入力端子と出力端子を短絡させた時の出力電圧であって、Vtより低い電圧を入力すればインバーターはLow電位を出力する閾値電圧である。本実施例では第2インバーター回路605-n、第1クロックド・インバーター608-nの電源電圧は+8V、0Vであって反転閾電圧Vt=4Vとする。なお、この時、隣接する単位メモリ回路520-n-1では後述する書き込み動作が同時に行われている。

[0039]

次にCLK信号が反転して順次選択回路500が動作し、出力端子510- k (第2出 力端子)が選択され(=HIGH、+8V)、出力端子510-k-1は非選択(=LO W、 0 V ) となって第 1 トランジスター 6 0 4 - n 及び第 2 トランジスター 6 0 7 - n が OFFする。ここで順次選択回路500及び第1インバーター回路601 - nの電源は+ 8 V と 0 V であって、ゆえに出力端子 5 1 0 - k は + 8 V 、第 1 インバーター回路 6 0 1 - n の出力は 0 V である。このとき、第 2 蓄積容量 6 0 6 - n の容量結合と第 2 トランジ スター 6 0 7 - n のゲート・ドレイン間フィードスルーによってノード B の電位は電位 V tから下がることになる。本実施例では第2蓄積容量606-nの容量を120fF、第 2 トランジスター 6 07-nのゲート・ドレイン間フィードスルー実効容量を 1 0fF、 第 1 蓄積容量 6 0 3 - n の容量を 8 9 0 f F 、第 2 インバーター回路 6 0 5 - n の入力容 量を20fFとするので、ノードBの電位は電位Vtから1V下がり、3.0Vとなる。 このとき、出力端子510-kが+8V、第1インバーター回路601-nの出力が0V であるので第1伝送ゲート602-nはゲート開となり、この結果、映像信号配線と、ノ ード A とが電気的に接続されるので、映像信号配線上のデジタル映像信号 D m ( m = 0 ~ 1 7)の電位が第1蓄積容量603-nの一端であるノードAに充電される。すなわちノ ー ド A は + 3 V または 0 V となる。ノード A が 3 V になった場合はノード B は第 1 蓄積容 量 6 0 3 - n (容量は 1 p F とする)との容量結合によって電位が 2 . 6 V 上昇し、 5 . 6 V となる。ここで第 2 インバーター回路 6 0 5 - n の反転 閾電圧 V t は 4 V であるから 、入力電位は十分これより大きく、従って第2インバーター回路605-nはほぼ0Vを ノードCに出力し、第1クロックド・インバーター608-nによって第3蓄積容量60 9- n の一端に接続されたノードDには8Vが出力される。一方、デジタル映像信号Dm からノードAに充電された電位が0Vとなった場合はノードAの電位は変動していないか らノードBの電位は3.0Vのままであって、反転闘電圧Vt(4V)より小さいから第 2 インバーター回路 6 0 5 - n は約 8 V をノード C に出力し、第 1 クロックド・インバー ター 6 0 8 - n によってノード D には 0 V が出力される。このようにして、出力端子 5 1 0-kが選択されたタイミングで第3蓄積容量609-nには0-3V電位のデジタル映 像信号Dmが0-8Vに増幅して書き込まれることになるのである。

[0040]

次にさらに C L K 信号が反転して順次選択回路 5 0 0 が動作し、出力端子 5 1 0 - k 及び出力端子 5 1 0 - k - 1 がともに非選択(= L O W)となると、第 1 伝送ゲート 6 0 2 - n はゲート閉となるが、ノード A の電位は第 4 蓄積容量 6 1 0 - n (容量は 1 0 0 f F )によって次に出力端子 5 1 0 - k - 1 が選択される約 3 0 μ 秒後まで保持され、ノード B / ノード C / ノード D の電位変動もほとんどなく保持される。すなわち、第 1 メモリ回路 5 0 1 として動作するのである。

[0041]

順次選択回路 5 0 0 が動作を続け、出力端子 5 1 0 - 6 4 1 まで選択を終えると、次に E P 信号が選択 ( 8 V ) される。すると第 3 インバーター回路 6 1 4 - n は L o w ( 0 V ) を出力し、第 2 クロックド・インバーター 6 1 1 - n が出力を開始する。このとき、第 2 メモリ回路の単位メモリ回路 5 2 1 - 1 ~ 1 1 5 2 2 0 全ての第 2 クロックド・インバ

20

30

40

50

- タ - 6 1 1 - 1 ~ 1 1 5 2 2 0 が同時に動作する。

## [0042]

ここで第3インバーター回路614 - nおよび第2クロックド・インバーター611 nの電源電圧は+8Vと0Vである。すなわち、ノードDが電位0Vなら+8Vを、ノー ドDが電位 + 8Vなら0Vをそれぞれ第5蓄積容量612-nの一端に接続されている丿 ードEへ出力する。第5蓄積容量612-nの他端は0V電源に接続される。約100n 秒後にEP信号が非選択になると第2クロックド・インバーター611-nは非動作とな る。 第 2 クロックド・インバーター 6 1 1 - n のリーク電流が 1 n A 以下、 第 5 蓄積容量 6 1 2 - nの容量を 1 p F とすればノード E の電位変動は次に E P 信号が選択するまでの 期間ではせいぜい35mVであるから、次のEP信号選択期間までの間、ノードEの電位 は保持されることになる。この間、第4インバーター回路613-n(電源電位は8V/ 0 V)によってノードEが + 8 Vなら 0 V、ノードEが 0 Vなら + 8 Vをそれぞれ出力端 子525-nに出力している。すなわち、第2メモリ回路502として動作するのである 。 出力端子 5 2 5 - n の電位はそのまま D A C 回路 5 0 3 へ接続されるので、 D A C 回路 5 0 3 では E P 信号選択から次選択の間、すなわち走査線選択期間の間、入力電位が 0 / 8 V で保持される。この間に全てのデータ線 2 0 2 - 1 ~ 1 9 2 0 へ単位メモリ回路 5 2 n の出力( = 出力端子 5 2 5 - n 電位)に従ってデジタル・アナログ変換した結果を 同時に書き込めばよい(線順次書き込み)。

## [0043]

本実施例のようにデータ線駆動回路302を構成することで素子数の多いスタティック型RAM構成では無く、ダイナミック型RAM構成でメモリ回路を構成できるため、より高精細な液晶表示装置を実現可能である。また、デジタル映像信号Dmの電位振幅を低く(0~3V)できるので消費電力を低減できる一方、第2メモリ回路502からの出力電位振幅は高い(0~8V)ので閾値の高いポリシリコン薄膜トランジスターを用いて構成したDAC回路503の精度が低下することが無い。

#### [0044]

なお、本実施例では第1インバーター回路601-n、第3インバーター回路614-nを各単位メモリ回路520-n、521-n内に配置しているが、2個以上の単位メモリ回路に1つの配置としても良い。第1インバーター回路601-nでは最大6個の単位メモリ回路、第3インバーター回路614-nでは全ての単位メモリ回路で一つのインバーターに統合可能である。

## [0045]

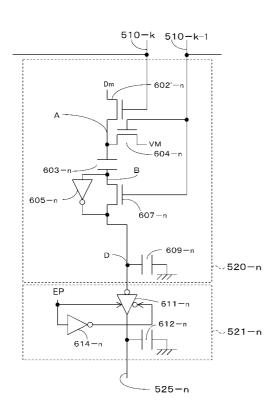

また、別の構成例として、図5に示す例を説明する。図5の単位メモリ回路520-nは、第1伝送ゲート602-nに代えて、トランジスター602'-nを備えている。一方で、第1インバーター回路601-nと、第2蓄積容量606-nと、第4蓄積容量610-nと、第1クロックド・インバーター608-nとは、本変形例の単位メモリ回路520-nから省かれている。さらに、本変形例では、第1トランジスター604-nのソースに接続されたVMの電位は、1.5Vに設定されている。

## [0046]

トランジスター602′-nのゲート入力には、出力端子510-kが接続されている。また、トランジスター602′-nのソースには映像信号配線が接続されている。そして、トランジスター602′-nは、出力端子510-kの選択/非選択に応じて、映像信号配線上のデジタル映像信号Dmをドレインへ出力するように構成されている。

## [0047]

本変形例のノードAは、トランジスター602 ' - nのドレインと、第1トランジスター604 - nのドレインと、第1蓄積容量603 - nの一端と、が接続された部分である。また本変形例のノードBは、第1蓄積容量603 - nの他端と、第1インバーター回路605 - nの入力と、第2トランジスター607 - nのソースと、が接続された部分である。また、本変形例のノードDは、第1インバーター回路605 - nの出力と、第2トランジスター607 - nのドレインと、第3蓄積容量609 - nの一端と、第2クロックド

20

30

40

50

・インバーター 6 1 1 - n の入力と、が接続された部分である。実施例 1 におけるノード C は、本変形例では定義しない。

## [0048]

このような構成を有する単位メモリ回路520-nの動作は以下の通りである。

## [0049]

出力端子510・k・1が選択(=High)でノードBにまず4.0 Vが書き込まれた後、出力端子510・k・1が非選択(=LOW)となったタイミングでノードBの電位は第2インバーター回路605・nのフィードスルーによって3.9 Vと0.1 Vドロップする。ノードAに3 Vが充電されるとノードBの電位は容量結合によって1.4 V上昇して5.3 Vに、ノードAに0 Vが充電されるとノードBの電位は1.4 V下降して2.5 Vになる。前者の場合は反転閾電圧 V t (4 V)より高いので第2インバーター回路605・nは約0 VをノードCに出力するので第1クロックド・インバーター608・nは8 VをノードDに出力し、後者の場合は反転閾電圧 V t (4 V)より低いので第2インバーター回路605・nは約8 VをノードCに出力するので第1クロックド・インバーター608・nは0 VをノードDに出力する。すなわち、ノードAに3 Vが充電されるとノードDは8 V、ノードAに0 Vが充電されるとノードDは0 Vとなり、同様に第1メモリ回路として動作する。

## [0050]

このような構成をとると第2蓄積容量606-nがなくなる分、素子数を削減できる一方で1.5Vの電源配線が1本増えることになる。どちらを選択するかは回路面積等を勘案して決めればよい。また、ノードAに繋がる第4蓄積容量610-nは伝送ゲート602-nのリーク電流及び各種配線交差・平行容量によるノイズによって誤動作を起こすことを防止するものであって、リークや交差・平行容量が少ない場合は不要である。同様に第1クロックド・インバーター608-nは必ずしも必須ではなく、伝送ゲート602-n、第1トランジスター604-n及び第2トランジスター607-nのリーク電流が十分に小さければ削除しても構わない。また、クロックド・インバーターではなく、通常のインバーターで構成しても良い。このようにして回路を簡素化した構成例を図5にのせる

## [0051]

図 6 は図 1 のデータ線駆動回路 3 0 2 を用いたアクティブマトリクス基板 1 0 1 の構成図である。アクティブマトリクス基板 1 0 1 上には 4 8 0 本の走査線(2 0 1 - 1 ~ 4 8 0)と1920本のデータ線(2 0 2 - 1 ~ 1 9 2 0)が直交して形成されており、4 8 0 本の容量線(2 0 3 1 ~ 4 8 0)は走査線(2 0 1 - 1 ~ 4 8 0)と並行に配置されている。容量線(2 0 3 1 ~ 4 8 0)は相互に短絡され、対向導通部(3 3 0)に接続され、電源回路 3 0 4 から適切な共通電位を与えられる。

## [ 0 0 5 2 ]

走査線(201-1~480)は走査線駆動回路301に接続されて駆動信号を与えられる。また、データ線(202-1~1920)はデータ線駆動回路302に接続されて映像信号を与えられる。走査線駆動回路301、データ線駆動回路302は電源回路304および信号回路305に接続され、必要な信号(例えばSP,CLK信号)と必要な電位(例えば+8、+3、0VDC電源)を供給される。データ線駆動回路302は信号入力端子320からデジタル映像信号D0~D17を与えられる。また信号回路305および電源回路304も必要な信号(マスタークロック、SYNC信号など)および電源電位(例えば+2V)を与えられる。

#### [0053]

走査線駆動回路301、データ線駆動回路302、電源回路304、信号回路305はアクティブマトリクス基板の一部を構成するガラス基板上に能動素子としてのポリシリコン薄膜トランジスターを集積することで形成されており、後述する画素スイッチング素子(401-n-m)と同一工程で製造される、いわゆる駆動回路内蔵型の液晶表示装置となっている。

20

30

40

50

### [0054]

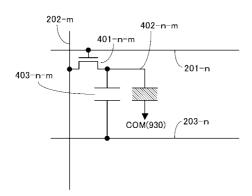

図7は図6の点線310部で示す画素表示領域中のm番目のデータ線(202-m)と n番目の走査線(201-n)の交差部付近の回路図である。走査線(201-n)とデータ線(202-m)の各交点にはNチャネル型電界効果ポリシリコン薄膜トランジスターよりなる画素スイッチング素子(401-n-m)が形成されており、そのゲート電極は走査線(201-n)に、ソース・ドレイン電極はそれぞれデータ線(202-m)と画素電極(402-n-m)に接続されている。画素電極(402-n-m)及び同一電位に短絡される電極は容量線(203-n)と補助容量コンデンサー(403-n-m)を形成し、また液晶表示装置として組み立てられた際には液晶素子をはさんで対向基板電極930(コモン電極)とやはリコンデンサーを形成する。

[0055]

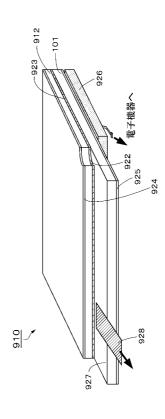

図8は図6のアクティブマトリクス基板を用いた第1の実施例における6BitDAC 内蔵透過型VGA解像度液晶表示装置の斜視構成図(一部断面図)である。液晶表示装置 9 1 0 は、アクティブマトリクス基板 1 0 1 (第 1 の基板)と対向基板 9 1 2 (第 2 の基 板 )とをシール材 9 2 3 により一定の間隔で貼り合わせ、ネマティック相液晶材料 9 2 2 を挟持してなる。アクティブマトリクス基板101上には図示しないがポリイミドなどか らなる配向材料が塗布されラビング処理されて配向膜が形成されている。また、対向基板 912は、図示しないが画素に対応したカラーフィルタと、光抜けを防止し、コントラス トを向上させるためのブラックマトリクスと、アクティブマトリクス基板101上の対向 導 通 部 3 3 0 と 短 絡 さ れ る コ モ ン 電 位 が 供 給 さ れ る I T O 膜 で な る 対 向 基 板 電 極 9 3 0 が 形成される。液晶材料922と接触する面にはポリイミドなどからなる配向材料が塗布さ れ、 ア ク テ ィ ブ マ ト リ ク ス 基 板 1 0 1 の 配 向 膜 の ラ ビ ン グ 処 理 の 方 向 と は 直 交 す る 方 向 に ラビング処理されている。さらに対向基板912の外側には、上偏光板924を、アクテ ィブマトリクス基板101の外側には、下偏光板925を各々配置し、互いの偏光方向が 直交するよう(クロスニコル状)に配置する。さらに下偏光板925下には、面光源を成 すバックライトユニット926が配置される。バックライトユニット926は、冷陰極管 やLEDに導光板や散乱板をとりつけたものでも良いし、EL素子によって全面発光する ユニットでもよい。図示しないが、さらに必要に応じて、周囲を外殻で覆っても良いし、 あるいは上偏光板924のさらに上に保護用のガラスやアクリル板を取り付けても良いし 、視野角改善のため光学補償フィルムを貼っても良い。

[0056]

また、アクティブマトリクス基板101は、対向基板912から張り出す張り出し部927が設けられ、その張り出し部927にある信号入力端子320には、FPC(可撓性基板)928が実装され電気的に接続されている。

[0057]

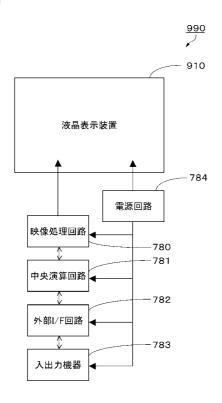

図9は本実施例での電子機器990の具体的な構成を示すブロック図である。液晶表示装置910は図8で説明した6BitDAC内蔵VGA解像度液晶表示装置であって、電源回路784、映像処理回路780がFPC(可撓性基板)928および信号入力端子320を通じて必要な信号と電源を液晶表示装置910に供給する。中央演算回路781は外部I/F回路782を介して入出力機器783からの入力データを取得する。ここで入出力機器783とは例えばキーボード、マウス、トラックボール、LED、スピーカー、アンテナなどである。中央演算回路781は外部からのデータをもとに各種演算処理を行い、結果をコマンドとして映像処理回路780あるいは外部I/F回路782へ転送する。映像処理回路780は中央演算回路781からのコマンドに基づき映像情報を更新し、液晶表示装置910の表示映像が変化する。

[0058]

このように構成された電子機器 9 9 0 は表示装置が高精細であって、駆動回路や信号回路がアクティブマトリクス基板 1 0 1 上に一体形成されているゆえにコストが安い上に信頼性が高い。このため、表示品位の良好で高信頼性の電子機器を安価に提供できるのであ

る。ここで「電子機器」とは具体的にはモニター、TV、ノートパソコン、PDA、デジタルカメラ、ビデオカメラ、携帯電話、携帯フォトビューワー、携帯ビデオプレイヤー、携帯DVDプレイヤー、携帯オーディオプレイヤーなどである。

## [ 0 0 5 9 ]

(実施例2)

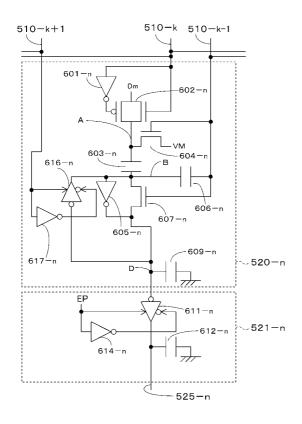

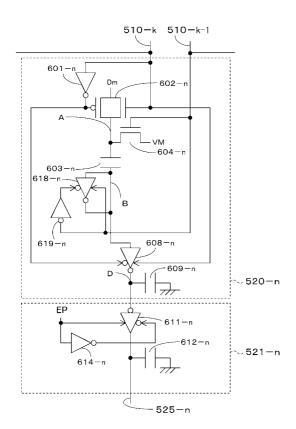

図10は第2の実施例を実現するための第1メモリ回路501の単位メモリ回路520-nおよび第2メモリ回路502の単位メモリ回路521-nの回路構成であり、第1の実施例の図4に代わるものである。なお、データ線駆動回路302の構成、DAC回路503の回路構成、順次選択回路500の回路構成は第1の実施例となんら変わりないので説明を省略する。また、図10中、図4と構成・動作が変わらない部分については同じ記号を用いることで詳細な説明は省略する。

[0060]

[0061]

図 1 0 に示すように、本実施例の単位メモリ回路 5 2 0 - n には、出力端子 5 1 0 - k - 1 と、出力端子 5 1 0 - k とに加えて、出力端子 5 1 0 - k + 1 が接続されている。なお、出力端子 5 1 0 - k の次に選択される出力端子である。

そして、図10の単位メモリ回路520- n からは、第4蓄積容量610- n が省略されている。その代わり、単位メモリ回路520- n は、第3トランジスター615- n を備えている。第3トランジスター615- n のゲート入力は、出力端子510- k + 1 に接続されている。そして、第3トランジスター615- n のソースは、本実施例では接地されている。さらに、第3トランジスター615 n のドレインは、実施例1のノードBに接続されている。

[0062]

図10の構成は第1の実施例における消費電力の問題を解決した回路構成である。すなわち、第1の実施例の構成では出力端子510-kにおいてノードBの電位が5.6Vもしくは3.0Vのまま次に出力端子510-k・1が選択されるまでの期間、保持Bの電位が5.6Vの時、第2インバーター回路605-nの電源電圧は8V及び0Vであるから、ノードBの電位が5.6Vの時、第2インバーター回路605-nを構成するpチャネル型トランである。すなわち、第2インバーター回路605-nを構成するpチャネル型トランである。すなわち、第2インバーター回路605-nを構成するpチャネル型トランが第2インバーター回路605-nを構成するmチャネル型トランバーターの闘値Vthが・2.4Vよりも十分大きい場合、定常的な貫通リーク電流が第2インバーター回路605-nを構成するmチャネル型トランバーター回路605-nを流れることになる。この貫通電流は動作中の、すなわち選択中の回路605-nを流れることになる。この貫通電流は動作中の、すなわち選択中の回路605-nの接続された段を除いて全ての段で流れるから、一つの第2インバーター回路605-nのりつ電流を100nAとしても全体では約1.1mAとなって無視し得ないち

[0063]

そこで本実施例では第3トランジスター615-nを追加し、ソース電極に0V電源、ドレイン電極をノードBに接続し、さらに出力端子510-k+1をゲート電極に接続する。第3トランジスター615-nはnチャネル型のトランジスターである。このような構成により、順次選択回路500により出力端子510-kが選択され、ノードDに0-8Vの電位を書き込んだ後、CLK信号が反転して順次選択回路500が動作し出力端子510-k・1が選択(8V)、出力端子510-kが非選択(0V)となった時にノードBに0Vを第3トランジスター615-nによって書き込み、第2インバーター回路605-nにリーク電流が流れないようにするのである。このとき、ノードCは8Vとなるが、第1クロックド・インバーター608-nは非動作になっているので、ノードDの電位は変化しないので第1メモリ回路としての動作に支障は無い。

[0064]

50

10

20

30

20

30

40

50

その他の回路構成等については第1の実施例と基本的に同じである。本実施例のデータ線駆動回路302を用いたアクティブマトリクス基板101、液晶表示装置910、電子機器990の構成も第1の実施例と同様であるので省略する。

### [0065]

なお、図10のような構成であると、第1クロックド・インバーター608-nを省略することは不可能である。そこで別の実施例として図11の構成を示す。図11では第3トランジスター615-nに代わり、第3クロックド・インバーター616-nを配置し、入力をノードD(本変形例では第3蓄積容量609-nの一端)に、出力をノードBに、直クロック端子に出力端子510-k+1に、負クロック端子に第5インバーター608-n、第4インバーターの317-nの出力につなぎ、第1クロックド・インバーター608-n、第4インバーター回路613-nを省略した構成としている。なお、第5インバーター回路617-nの日の入力は出力端子510-k+1に接続され、第5インバーター回路617-nのまであればノードBに0Vとする。このような構成により、出力端子510-k+1が選択された時、ノードDの電位が0VであればノードBに18Vを、ノードDの電位が18VであればノードBに18Vを、バーター616-nの貫通リーク電流も抑制される。

#### [0066]

#### (実施例3)

図12は第3の実施例を実現するための第1メモリ回路501の単位メモリ回路520-nおよび第2メモリ回路502の単位メモリ回路521-nの回路構成であり、第1の実施例の図4に代わるものである。なお、データ線駆動回路302のブロック図、順次選択回路500の回路図は第1の実施例と基本的に同じなので説明を省略する。また、図12中、図4と構成・動作が変わらない部分については同じ記号を用いることで詳細な説明は省略する。

## [0067]

図12の構成は第1の実施例における消費電力の問題について、第2の実施例とは別の解決法を示したものである。第2の実施例で示した解決方法では新規に出力端子510-k+1からの引き回しが生じるため、配線が複雑になりやすい。そこで本実施例では第2インバーター回路605・nを第4クロックド・インバーター618・nに置き換え620・nに接続している。第4クロックド・インバーター618・n、第6インバーター回路619・n、負クロック第1NOR回路620・nはそれぞれ電源電位として+8Vとのとに接続されており、第6インバーター回路619・nの入力は第1NOR回路620・nの出力に接続されており、第6インバーター回路619・nの入力は出力端子510・kおよび出力端子510・k・1にそれぞれ接続される。このような構成をとることで、第4クロックド・インバーター618・nは出力端子510・kの選択期間および出力端子510・k・1の選択期間のみ動作し、それ以外の期間では動作せず、貫通電流も抑制される。

#### [0068]

その他の回路構成等については第1の実施例と基本的に同じである。本実施例のデータ線駆動回路302を用いたアクティブマトリクス基板101、液晶表示装置910、電子機器990の構成も第1の実施例と同様であるので省略する。

## [0069]

図13の構成は第3の実施例の別構成例を示すための第1メモリ回路501の単位メモリ回路520-nおよび第2メモリ回路502の単位メモリ回路521-nの回路構成である。本構成では、第2蓄積容量606-nと、第2トランジスター607-nと、を廃している。そのうえで、第4クロックド・インバーター618-nの入力・出力をともにノードB(または第1蓄積容量603-nの他端)へ接続するとともに、正クロック端子を出力端子510-k-1、負クロック端子を第6インバーター回路619-nの出力へ

20

30

40

50

接続している。第6インバーター回路619 - nの入力は出力端子510 - k - 1へ接続している。ここで第6インバーター回路619 - nの電源電圧は8V/0Vである。なお、本変形例でのノードBは、第1蓄積容量603 - nの他端と、第1クロックド・インバーター608 - nの入力と、第4クロックド・インバーター618 - nの入力と、が接続された部分である。

#### [0070]

本構成では第4クロックド・インバーター618-nによって反転閾値電圧Vt(第1基準電位)を書き込み、増幅は第1クロックド・インバーター608-nで行うようにしている。第4クロックド・インバーター618-nの反転閾値電圧Vtと第1クロックド・インバーター608-nの反転閾値電圧Vt 'を電源電位VMに応じて微妙に調整することで容量606-nを省略できるようにしている。ここでは電源電位VM=0、Vt=4V、Vt'=4.5Vとなるように調整している。第4クロックド・インバーター618-nは出力端子510-k-1が選択されている期間だけ、第1クロックド・インバーター608-nは出力端子510-k-1が選択されている期間だけ、それぞれ動作しているので貫通電流は抑制される。一方で、|Vt Vt'|のプロセスばらつきについては比較的シビアであって他実施例よりマージンが少ない。どちらの回路構成を選択するかはこれらの点を勘案して決めればよい。

## [0071]

なお、実施例3では第1インバーター回路601-n、第3インバーター回路614-n、第6インバーター回路619-n、第1NOR回路620-nを各単位メモリ回路520-n、521-n内に配置しているが、2個以上の単位メモリに1つの配置としても良い。第1インバーター回路601-n、第6インバーター回路619-n、第1NOR回路620-nでは最大6個の単位メモリ、第3インバーター回路614-nでは全ての単位メモリを一つのインバーターに統合可能である。

## 【産業上の利用可能性】

## [0072]

本発明は実施例の形態に限定されるものではなく、TNモードではなく垂直配向モード(VAモード)、横電界を利用したIPSモード、フリンジ電界を利用したFFSモードなどの液晶表示装置に利用しても構わない。また、全透過型のみならず全反射型、反射透過兼用型であっても構わない。

### 【図面の簡単な説明】

## [0073]

- 【 図 1 】 本 発 明 の 第 1 か ら 第 3 実 施 例 に 係 る デ ー タ 線 駆 動 回 路 の ブ ロ ッ ク 図 。

- 【図2】本発明の第1から第3実施例に係る順次選択回路の回路図。

- 【図3】本発明の第1から第3実施例に係るDAC回路の回路図。

- 【図4】本発明の第1実施例に係る第1メモリ回路の単位メモリ回路および第2メモリ回路の単位メモリ回路の回路図。

- 【図5】本発明の第1実施例の別実施形態に係る第1メモリ回路の単位メモリ回路および第2メモリ回路の単位メモリ回路の回路図。

- 【図6】本発明の実施例に係るアクティブマトリクス基板の構成図。

- 【図7】本発明の実施例に係るアクティブマトリクス基板の画素回路図。

- 【図8】本発明の実施例に係る液晶表示装置の斜視図。

- 【図9】本発明の電子機器の構成を示すブロック図。

- 【図10】本発明の第2実施例に係る第1メモリ回路の単位メモリ回路および第2メモリ 回路の単位メモリ回路の回路図。

- 【図11】本発明の第2実施例の別実施形態に係る第1メモリ回路の単位メモリ回路および第2メモリ回路の単位メモリ回路の回路図。

- 【図12】本発明の第3実施例に係る第1メモリ回路の単位メモリ回路および第2メモリ 回路の単位メモリ回路の回路図。

- 【図13】本発明の第3実施例の別実施形態に係る第1メモリ回路の単位メモリ回路およ

び第2メモリ回路の単位メモリ回路の回路図。

## 【符号の説明】

## [0074]

101…アクティブマトリクス基板、201…走査線、202…データ線、302…データ線駆動回路、501…第1メモリ回路、502…第2メモリ回路、503…DAC回路、520-1~1520…第2メモリ回路の単位メモリ回路の単位メモリ回路の単位メモリ回路の出力端子、401…画素スイッチング素子、402…画素電極、910…液晶表示装置。

## 【図1】

## 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図10】

## 【図11】

## 【図13】

## フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 8 0 G G 0 9 G 3/20 6 2 1 M

F ターム(参考) 5C080 AA10 BB05 DD25 EE29 FF11 JJ02 JJ03 JJ06

| 专利名称(译)        | 数据线驱动电路,液晶显示设备和带SAM的电子设备                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号        | <u>JP2008076731A</u>                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2008-04-03 |  |  |  |

| 申请号            | JP2006255611                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2006-09-21 |  |  |  |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |

| 申请(专利权)人(译)    | 爱普生影像设备公司                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| [标]发明人         | 小橋裕                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |

| 发明人            | 小橋 裕                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |  |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                       |         |            |  |  |  |

| FI分类号          | G09G3/36 G02F1/133.505 G09G3/20.621.L G09G3/20.623.F G09G3/20.623.G G09G3/20.680.G G09G3/20.621.M                                                                                                                                                                                                                                                                 |         |            |  |  |  |

| F-TERM分类号      | 2H093/NA16 2H093/NA43 2H093/NA53 2H093/NC09 2H093/NC13 2H093/NC15 2H093/NC24 2H093 /NC34 2H093/ND06 2H093/ND39 2H093/ND49 2H093/ND52 2H093/NE07 5C006/AA16 5C006/BB16 5C006/BC20 5C006/BF01 5C006/BF04 5C006/BF26 5C006/BF27 5C006/FA43 5C080/AA10 5C080 /BB05 5C080/DD25 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ06 2H193/ZA04 2H193/ZD23 2H193/ZF34 |         |            |  |  |  |

| 代理人(译)         | 宫坂和彦                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |

## 摘要(译)

要解决的问题:提供高清晰度和低功耗的DAC内置数据线驱动电路。解决方案:在选择顺序选择电路的第一输出端子的定时将参考电位写入存储电路,并且在选择第二输出端子的定时将信号写入存储电路。此外,通过组成动态类型的存储电路来减少元件的数量,以获得高清晰度。 Ž