## (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第3666662号 (P3666662)

(45) 発行日 平成17年6月29日(2005.6.29)

(24) 登録日 平成17年4月15日 (2005.4.15)

| (51) Int.C1. <sup>7</sup> | F 1                           |           |                         |

|---------------------------|-------------------------------|-----------|-------------------------|

| GO2F 1/133                | GO2F                          | 1/133 5   | 550                     |

| GO2F 1/1345               | GO2F                          | 1/1345    |                         |

| GO9G 3/20                 | G09G                          | 3/20 €    | S 1 2 L                 |

| GO9G 3/36                 | G09G                          | 3/20 €    | S 2 1 M                 |

|                           | G09G                          | 3/20 €    | S 2 2 A                 |

|                           |                               |           | 請求項の数 9 (全 19 頁) 最終頁に続く |

| (21) 出願番号                 | 特願2002-363037 (P2002-363037)  | (73) 特許権者 | 皆 000005049             |

| (22) 出願日                  | 平成14年12月13日 (2002.12.13)      |           | シャープ株式会社                |

| (65) 公開番号                 | 特開2004-191888 (P2004-191888A) |           | 大阪府大阪市阿倍野区長池町22番22号     |

| (43) 公開日                  | 平成16年7月8日 (2004.7.8)          | (74) 代理人  | 100080034               |

| 審査請求日                     | 平成16年12月20日 (2004.12.20)      |           | 弁理士 原 謙三                |

|                           |                               | (74) 代理人  | 100113701               |

|                           |                               |           | 弁理士 木島 隆一               |

|                           |                               | (74) 代理人  | 100116241               |

|                           |                               |           | 弁理士 金子 一郎               |

|                           |                               | (72) 発明者  | 鷲尾 一                    |

|                           |                               |           | 大阪府大阪市阿倍野区長池町22番22号     |

|                           |                               |           | シャープ株式会社内               |

|                           |                               | (72) 発明者  | 前田和宏                    |

|                           |                               |           | 大阪府大阪市阿倍野区長池町22番22号     |

|                           |                               |           | シャープ株式会社内               |

|                           |                               |           | 最終頁に続く                  |

### (54) 【発明の名称】表示装置

## (57)【特許請求の範囲】

#### 【請求項1】

走査信号線を駆動する走査信号線駆動回路と、上記走査信号線に交差するように配された データ信号線を駆動するデータ信号線駆動回路とを備えた表示装置において、

上記走査信号線駆動回路或いはデータ信号線駆動回路の少なくとも一方の駆動回路に、少なくとも第1,第2の信号が入力され、他の回路に第1の信号が共通して入力されるように構成されており、上記駆動回路に入力される第2の信号の配線負荷と、上記他の回路にも共通に入力される第1の信号の配線負荷とを揃える配線負荷調整手段が設けられていることを特徴とする表示装置

### 【請求項2】

10

上記他の回路は、上記走査信号線又はデータ信号線を駆動する駆動回路であることを特徴とする請求項1に記載の表示装置。

## 【請求項3】

上記第1の信号は、共通の入力端より信号線を共用して、上記駆動回路及び上記他の回路 に入力されることを特徴とする請求項1に記載の表示装置。

### 【請求項4】

上記第1,第2の信号が、複数系統のクロック信号であることを特徴とする請求項1に記載の表示装置。

### 【請求項5】

上記第1,第2の信号が、複数のビットで構成されるデジタル映像信号であって、少なく

とも 2 つのビット群に分けられているデジタル映像信号であることを特徴する請求項 1 に記載の表示装置。

#### 【請求項6】

上記配線負荷調整手段が、各配線の時定数を揃えるようになっていることを特徴とする請求項1~5の何れかに記載の表示装置。

#### 【請求項7】

上記走査信号線と上記データ信号線とは基板上に形成されると共に、該基板と対向電極が 形成された基板との間に液晶層を挟持しており、

上記配線負荷調整手段は、上記液晶層を誘電体として用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、該ダミー配線上の上記液晶層と、上記対向電極とを備えていることを特徴とする請求項1~6の何れかに記載の表示装置。

#### 【請求項8】

上記走査信号線と上記データ信号線とは基板上に形成されると共に、該基板上にはさらに 層間絶縁膜と導電膜とが形成されており、

上記配線負荷調整手段は、上記層間絶縁膜を誘電体として用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、上記層間絶縁膜と、上記導電膜とを備えていることを特徴とする請求項1~6の何れかに記載の表示装置。

#### 【請求項9】

上記走査信号線と上記データ信号線との各交点には薄膜トランジスタが設けられており、 上記配線負荷調整手段は、薄膜トランジスタのゲート絶縁膜を構成する層を誘電体として 用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、該ダミー 配線に積層して配された上記薄膜トランジスタのゲート絶縁膜及び半導体層を構成する各層とを備えていることを特徴とする請求項1~6の何れかに記載の表示装置。

#### 【発明の詳細な説明】

### [0001]

### 【発明の属する技術分野】

本発明は、アクティブマトリックス型の液晶表示装置などに好適な、複数の走査信号線を駆動する走査信号線駆動回路と、上記走査信号線に交差するように配された複数のデータ信号線を駆動するデータ信号線駆動回路とを備えた表示装置に関する。

## [0002]

### 【従来の技術】

従来、表示装置の一つとして、アクティブマトリックス駆動方式の液晶表示装置が知られている。なお、本明細書では、本発明の対象技術である表示装置例として、液晶表示装置について述べるが、本発明はこれに限定されることなく、他の表示装置についても有効なものである。

### [0003]

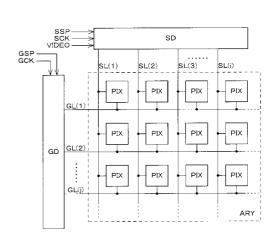

アクティブマトリックス型の液晶表示装置は、図 1 0 に示すように、画素アレイ A R Y と、走査信号線駆動回路 G D と、データ信号線駆動回路 S D とを備えている。

#### [0004]

画素アレイARYは、互いに交差する複数の走査信号線GL(1)~GL(j)及び、データ信号線SL(1)~SL(i)を備えており、隣接する2つの走査信号線GL・GL(以下、総称するとき及び任意のものを指すとき、参照符号GLとする)と、隣接する2つのデータ信号線SL・SL(以下、総称するとき及び任意のものを指すとき、参照符号SLとする)とで区画された部分毎に、画素PIXが1つずつ配されている。画素PIX … は、マトリックス状に配設されている。

## [0005]

データ信号線駆動回路SDは、主にシフトレジスタとサンプリング回路とからなり、図示しない外部回路より、映像信号VIDEOと共に、制御信号としてのスタートパルス信号SSP及びクロック信号SCKが入力されるようになっている。データ信号線駆動回路SDは、スタートパルス信号SSPのパルスが入力されると、クロック信号SCKのタイミ

10

20

30

40

ング信号に同期して、入力された映像信号 VIDEOをサンプリングし、必要に応じて増幅して、データ信号線 SL(1)~SL(i)に書き込む。

#### [0006]

走査信号線駆動回路GDは、主にシフトレジスタからなり、図示しない外部回路より、制御信号としてのスタートパルス信号GSP及びクロック信号GCKが入力されるようになっている。走査信号線駆動回路GDは、スタートパルス信号GSPのパルスが入力されると、クロック信号GCKのタイミング信号に同期して、走査信号線GL(1)~GL(j)を順次選択して駆動する。これにより、画素PIX内にある後述するスイッチング素子の開閉が制御され、データ信号線SLに書き込まれた映像信号(データ)を画素PIXに書き込むと共に、画素PIXに書き込まれたデータは保持される。

[0007]

そして、本願出願人は、このような表示装置において、上記データ信号線駆動回路SD及び走査信号線駆動回路GDのうちの少なくとも一方の駆動回路を、複数の駆動回路より構成しておき、画素アレイに対して複数の駆動回路を、互いに独立して或いは連動して駆動することを提案している(特許文献1参照)。

[0008]

これにおいては、入力される映像の種類や使用環境に応じて、画素アレイを駆動する駆動 回路を適宜切り換えることによって、最適な表示フォーマットでの表示が可能となり、ま た、省電力化を図ることもできる。

[0009]

例えば、白黒表示とカラー表示とを1つの表示装置にて実現するにあたり、白黒データをカラー表示用の駆動回路で処理することで、白黒表示を行うことはできる。しかしながら、白黒表示であるのにカラー表示と同等の電力が駆動回路で消費される結果、白黒表示を行う上でのメリットがなくなってしまう。そこで、駆動回路を複数個とする構成を採用し、白黒表示用の駆動回路をカラー表示用の駆動回路とは別に搭載させておくことで、白黒表示に見合う消費電力に抑えることができる。

[0010]

また、複数の駆動回路を用いて時間差をつけてデータ信号線に映像信号を書き込むことにより、画像の上書きをすることができるので、映像信号を外部で信号処理することなく、スーパーインポーズ表示が可能となる。

[0011]

【特許文献1】

特開2002-32048号公報(2002年1月31日公開)

[0012]

【発明が解決しようとする課題】

上記したように、本願出願人は、データ信号線駆動回路、或いは走査信号線駆動回路を、 互いに独立して或いは連動して駆動する複数個の構成とすることを既に提案している。

[0013]

ところで、このような構成では、例えば、複数個備えられたうちのある駆動回路には、2 系統のクロック信号が使用されるのに対し、他の駆動回路には、そのうちの1系統のクロック信号のみが使用されるといった構成が考えられる。

[0014]

より具体的に説明すると、例えば、データ信号線の両側に2つのデータ信号線駆動回路が、データ信号線を介して互いが接続されるように設けられている構成があり、これにおいて、一方のデータ信号線駆動回路は、シフトレジスタを2系列備えており、個々のシフトレジスタに対応して2系統のクロック信号を使用するのに対し、もう一方のデータ信号線駆動回路は、シフトレジスタを1系列のみ備えており、2系統のクロック信号のうちの一方しか使用しないといった構成である。

[0015]

このような場合、外部インターフェースの構造の簡略化から、2つのデータ信号線駆動回

20

10

30

40

路にて共用されるクロック信号は、2つのデータ信号線駆動回路に共通して入力されることとなるが、ここで、2系統のクロック信号を使用するデータ信号線駆動回路においては、映像信号のサンプリングタイミングがずれてしまい、画面品位が低下するといった問題は起こる。

### [0016]

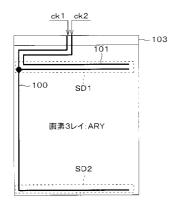

これは、2系統のクロック信号を供給する配線の引き回しの違いによる、配線負荷の違いに起因する。つまり、図11に示すように、信号入力部103側に設けられた第1のデータ信号線駆動回路SD1と共に、信号入力部103側とは反対側の端辺に配設された第2のデータ信号線駆動回路SD2にも共通して入力される第1のクロック信号ck1の配線100は、第1のデータ信号線駆動回路SD1のみに入力される第2のクロック信号ck2の配線101よりも、配線長が長くなる。そのため、当然に配線負荷が大きくなり、配線100と配線101とでは配線負荷が異なってくる。

#### [0017]

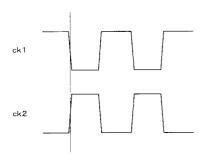

このような配線負荷が異なった配線100・101に、例えば、図12に示すように、互いに逆相の関係にある第1及び第2の各クロック信号 c k 1 ・ c k 2 を入力すると、配線負荷の大きい配線100にて供給される第1のクロック信号 c k 1 が、第2のクロック信号 c k 2 よりも遅れてしまう。その結果、たとえ信号入力側103よりほぼ等しい距離位置であっても、配線100にて供給される第1のクロック信号 c k 1 と、配線101にて供給される第2のクロック信号 c k 2 とでは、位相関係がずれてしまう。データ信号線駆動回路SD1の場合、このようなクロック信号間の位相ずれは、映像信号のサンプリングタイミングのずれとして現れる。

### [0018]

一方、配線100と配線101との配線負荷の違いにて発生する、第1及び第2のクロック信号 c k 1・ c k 2 間の上記した位相差を考慮して、第1及び第2のクロック信号 c k 1・ c k 2 を該位相差を解消し得るように予め補正しておくといったことも考えられる。

## [0019]

しかしながら、例えば、その補正値が 2 5 n s の時間であるとすると、外部回路の源クロック(システムクロック)としては、 2 0 M h z 以上のものが必要となり、消費電力をアップさせてしまう。近年、このような表示装置は、モバイル機器の表示装置に利用されること多く、低消費電力化の観点から、源クロックは低減される傾向にある。したがって、このような位相差の補正を外部回路で行う手法を採用することは困難である。

#### [0020]

さらに、表示装置が上記したような液晶表示装置である場合、配線負荷は、該配線と、対向電極と、これらの間に挟持された誘電体である液晶層とで構成される容量によるところが大きい。そのため、液晶層に用いる液晶材料や液晶層の厚みによっても変化してしまい、外部回路で対応するには、表示パネル毎に補正量を調整する必要があり、コストアップは否めない。

## [0021]

本発明は、上記課題に鑑みなされたもので、その目的は、複数系統のクロック信号等の互いに関わりのある複数の信号が駆動回路に入力される場合において、外部インターフェースの構造の簡略化を図るべく、一部は単独で入力され、一部は他の回路と共通して入力されるといった、関わりのある複数の信号間で異なる配線の引き回しで入力されたとしても、消費電力をアップさせることなく、引き回しの違いによる影響を受けることなく良好な表示を行い得る表示装置を提供することにある。

## [0022]

#### 【課題を解決するための手段】

本発明の表示装置は、上記課題を解決するために、走査信号線を駆動する走査信号線駆動回路と、上記走査信号線に交差するように配されたデータ信号線を駆動するデータ信号線駆動回路とを備えた表示装置において、上記走査信号線駆動回路或いはデータ信号線駆動

20

30

40

回路の少なくとも一方の駆動回路に、少なくとも第1,第2の信号が入力され、他の回路に第1の信号が共通して入力されるように構成されており、上記駆動回路に入力される第2の信号の配線負荷と、上記他の回路にも共通に入力される第1の信号の配線負荷とを揃える配線負荷調整手段が設けられていることを特徴としている。

#### [0023]

上記他の回路としては、上記走査信号線又はデータ信号線を駆動する駆動回路等がある。 また、上記第1,第2の信号としては、複数系統のクロック信号や、複数のビットで構成 されるデジタル映像信号であって、少なくとも2つのビット群に分けられているデジタル 映像信号等がある。

## [0024]

例えば、データ信号線の両側に2つのデータ信号線駆動回路が、データ信号線を介して互いが接続されるように設けられている構成においては、一方のデータ信号線駆動回路は2系統のクロック信号を使用し、もう一方のデータ信号線駆動回路は、そのうちの1系統のクロック信号のみを使用するといった構成が考えられる。

#### [0025]

このような場合、外部インターフェースの構造の簡略化から、2つのデータ信号線駆動回路にて共に使用される第1のクロック信号は、2つのデータ信号線駆動回路に共通して入力されることが多い。しかしながら、このように、2つのデータ信号線駆動回路で使用される第1のクロック信号を共通して入力させると、第1のクロック信号(第1の信号)と、単独で入力される第2のクロック信号(第2の信号)とを共に使用するデータ信号線駆動回路において、第1及び第2のクロック信号における配線負荷の違いにより信号遅延量に差が発生してしまう。このような信号遅延量に差が発生すると、第1及び第2のクロック信号間で位相関係が信号設計時の最適な関係よりずれてしまうため、データ信号線駆動回路の場合、映像信号のサンプリングタイミングのずれとして現れ、画面品位が低下する

#### [0026]

なお、配線負荷の違いにて発生する第1及び第2のクロック信号間の上記した位相差を考慮して、これらクロック信号を作成する外部回路にて、第1及び第2のクロック信号を該位相差を解消し得るように予め補正しておくことも可能であるが、前述したように、外部回路の源クロック(システムクロック)として、非常に高い周波数のものが必要となり、消費電力が高くなってしまう。モバイル機器の表示装置として利用する場合、消費電力のアップは、非常に問題である。

#### [0027]

そこで、本発明では、上記のように、他の回路にも共通に入力される第1の信号の配線負荷と、駆動回路に単独で入力される第2の信号の配線負荷を揃える配線負荷調整手段を設けている。

#### [0028]

これにより、外部回路において第1及び第2のクロック信号に補正を施して、消費電力のアップを伴うようなことなく、データ信号線駆動回路にのみ単独で入力される第2のクロック信号(第2の信号)の配線負荷と、もう一方のデータ信号線駆動回路にも共通して入力される第1のクロック信号(第2の信号)の配線負荷とを揃えて、両クロック信号間での信号遅延量の差を許容な範囲とできる。その結果、第1及び第2のクロック信号を両方用いるデータ信号線駆動回路における映像信号のサンプリングが正確に行われ、画面品位を良好に保つことが可能となる。

#### [0029]

なお、ここでは、データ信号線駆動回路を例に挙げて説明したが、走査信号線駆動回路においても、複数系統のクロック信号を1つの走査信号線駆動回路で用いる場合、各系統のクロック信号間の上記した位相差は、走査信号線の選択タイミングのずれを招来する。但し、走査信号線駆動回路におけるクロック信号の周波数は、データ信号線駆動回路のクロック信号の周波数に比べて低いので、上記した位相差による影響は小さいため、データ信

10

20

30

40

号線駆動回路において用いることが、より効果的である。

#### [0030]

また、上述したように、本発明は、上記第1の信号が、共通の入力端より信号線を共用して、上記駆動回路及び上記他の回路に入力される構成との組み合わせが適している。第1の信号が、共通の入力端より信号線を共用して入力させる構成とすることで、例えば、入力信号の入力端の数を減らすことができ、基板面積を有効活用することができる。

#### [0031]

本発明の表示装置は、さらに、上記配線負荷調整手段が、各配線の時定数を揃えるようになっていることを特徴とすることもできる。

#### [0032]

配線負荷を調整するにあたり、時定数、つまり、配線容量値 C、配線抵抗値 R によって算出することが可能となる。配線容量値 C は、容量を構成するための配線の幅や長さと配線間に挟持される誘電体の比誘電率により算出される。このとき容量値を調整するためにたとえば配線幅や長さを変更すればよく、また、負荷を構成する配線抵抗値も配線長、配線幅を変更することによって調整が可能となる。よって、時定数 = 容量 C \* 抵抗 R ( = C R ) にて近似される各配線の時定数を揃えるよう設計することで、配線負荷の調整を容易に行うことができる。

## [0033]

本発明の表示装置は、さらに、上記走査信号線と上記データ信号線とは基板上に形成されると共に、該基板と対向電極が形成された基板との間に液晶層を挟持しており、上記配線負荷調整手段は、上記液晶層を誘電体として用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、該ダミー配線上の上記液晶層と、上記対向電極とを備えていることを特徴とすることもできる。

#### [0034]

上記の構成によれば、配線負荷の小さい、駆動回路に単独で入力される第2の信号の配線にダミー配線を設け、該ダミー配線と、対向電極と、液晶層とで、配線負荷調整のための容量を構成している。

### [0035]

このような配線負荷調整手段は、表示装置としてそもそも備えている部材を利用して構成 し得るので、配線負荷調整手段を具備したことによるコスト上昇を最小限に抑えることが できる。

## [0036]

また、液晶層を有する液晶表示装置の場合、駆動回路に単独で入力される第2の信号の配線負荷と、他の回路にも共通に入力される第1の信号の配線負荷とが違ってくる最大の原因は、第1の信号における他の回路へと引き回される配線部分が、液晶層と対向電極との間で容量を形成し、これが、無視できない程度に大きいためである。

## [0037]

したがって、このような構成とすることで、ダミー配線を、第 1 の信号の上記した他の回路へと引き回される配線部分と条件的に等しく設けることで、簡単に配線負荷を調整することができる。

## [0038]

本発明の表示装置は、さらに、上記走査信号線と上記データ信号線とは基板上に形成されると共に、該基板上にはさらに層間絶縁膜と導電膜とが形成されており、上記配線負荷調整手段は、上記層間絶縁膜を誘電体として用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、上記層間絶縁膜と、上記導電膜とを備えていることを特徴とすることもできる。

#### [0039]

上記の構成によれば、配線負荷の小さい、駆動回路に単独で入力される第2の信号の配線にダミー配線を設け、該ダミー配線上に形成された層間絶縁膜と導電膜とで、配線負荷調整のための容量を構成している。

10

20

30

#### [0040]

上記走査信号線と上記データ信号線との上には、層間絶縁膜を介して透明導電膜等からなる画素電極が形成されたり、或いは、配線の交差を実現するための金属層が層間絶縁膜を介して設けられたりする。したがって、層間絶縁膜を誘電体として用い、その上に形成されている導電膜を他方の電極として容量を構成することができる。

#### [0041]

つまり、このような配線負荷調整手段においても、表示装置としてそもそも備えている部材を利用して構成し得るので、配線負荷調整手段を具備したことによるコスト上昇を最小限に抑えることができる。

#### [0042]

本発明の表示装置は、さらに、上記走査信号線と上記データ信号線との各交点には薄膜トランジスタが設けられており、上記配線負荷調整手段は、薄膜トランジスタのゲート絶縁膜を構成する層を誘電体として用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、該ダミー配線に積層して配置された上記薄膜トランジスタのゲート絶縁膜層及び半導体層をそれぞれ構成する各層を備えていることを特徴とすることもできる。

### [0043]

上記の構成によれば、配線負荷の小さい、駆動回路に単独で入力される第2の信号の配線にダミー配線を設け、該ダミー配線と、薄膜トランジスタのゲート絶縁膜を構成する層と、薄膜トランジスタの半導体層を構成する層とで、配線負荷調整のための容量を構成している。

### [0044]

上記走査信号線と上記データ信号線との交点にはアクティブ素子として薄膜トランジスタが設けられている構成が多く、このような構成においては、薄膜トランジスタの構成材料であるゲート絶縁膜の構成層を誘電体とし、半導体層に不純物を添加するなどして、高抵抗の金属のような特性を持たせて電極として機能させることで、容量を構成することができる。

#### [0045]

つまり、このような配線負荷調整手段においても、表示装置としてそもそも備えている部材を利用して構成し得るので、配線負荷調整手段を具備したことによるコスト上昇を最小限に抑えることができる。

## [0046]

#### 【発明の実施の形態】

本発明に係る実施の一形態について、図1~図9を用いて以下に説明する。

#### [0047]

本実施の形態では、表示装置として、アクティブマトリックス型の液晶表示装置を例示する。

### [0048]

本実施の形態におけるアクティブマトリックス型の液晶表示装置は、図2に示すように、 画素アレイARYと、走査信号線駆動回路GD1と、画素アレイARYの上下に配された 40 第1及び第2の2つのデータ信号線駆動回路SD1・SD2とを備えている。

#### [0049]

画素アレイARYは、互いに交差する複数の走査信号線GL(1)~GL(j)及び、データ信号線SL(1)~SL(i)を備えており、隣接する2つの走査信号線GL・GLと、隣接する2つのデータ信号線SL・SLとで区画された部分に、画素PIXが1つずつ配されている。画素PIX…は、マトリックス状に配設されている。

#### [0050]

第1及び第2のデータ信号線駆動回路SD1・SD2は、何れも、主にシフトレジスタとサンプリング回路とから構成されている。このうち、第1のデータ信号線駆動回路SD1には、図示しない外部回路より、映像信号VIDEOと共に、制御信号としてのスタート

10

20

30

パルス信号SSP1及び2系統の第1及び第2のクロック信号SCK1・SCK2が入力されるようになっている。また、第2のデータ信号線駆動回路SD2には、図示しない外部回路より、映像信号VIDEOと共に、制御信号としてのスタートパルス信号SSP2及び第1のデータ信号線駆動回路SD1に入力される第1のクロック信号SCK1が共通して入力されるようになっている。

#### [0051]

これら第1及び第2のデータ信号線駆動回路SD1・SD2の詳細な構成や動作については、図4~図7を用いて後述するが、2つのデータ信号線駆動回路SD1・SD2は、データ信号線SL(1)~SL(i)をその両端側より挟むように設けられており、データ信号線駆動回路SD1・SD2の両方がデータ信号線SL(1)~SL(i)を駆動し得るようになっている。

#### [0052]

走査信号線駆動回路GDは、主にシフトレジスタからなり、図示しない外部回路より、制御信号としてのスタートパルス信号GSP及びクロック信号GCKが入力されるようになっている。走査信号線駆動回路GDは、スタートパルス信号GSPのパルスが入力されると、クロック信号GCKのタイミング信号に同期して、走査信号線GL(1)~GL(j)を順次選択して駆動する。これにより、画素PIX内にある後述するスイッチング素子の開閉が制御され、データ信号線SLに書き込まれた映像信号(データ)を画素PIXに書き込むと共に、画素PIXに書き込まれたデータは保持される。

#### [0053]

画素PIXは、図3に示すように、アクティブ素子である電界効果型の薄膜トランジスタSWと、画素容量CPとによって構成される。画素容量CPは、液晶容量CL、および必要によって付加される補助容量CSより形成される。アクティブ素子である薄膜トランジスタSWのドレイン及びソースを介してデータ信号線SLと画素容量CPを構成する液晶容量CLおよび補助容量CSの各一方の電極とが接続される。また、薄膜トランジスタSWのゲートは走査信号線GLに接続されている。液晶容量CLの他方の電極は、全画素に共通に設けられた対向電極COMに接続され、補助容量の他方の電極も、全画素に共通に設けられた共通電極線を介して対向電極COMに接続されている。そして、各液晶容量CLに印加される電圧により、液晶の透過率または反射率が変調され、表示に供する。

#### [0054]

次に、図4~図7を用いて、上記第1及び第2のデータ信号線駆動回路SD1・SD2における構成及び動作の一例を説明する。ここでは、2つのデータ信号線駆動回路SD1・SD2は互いに独立して駆動する高解像度用のデータ信号線駆動回路と、低解像度用のデータ信号線駆動回路である場合を説明する。

### [0055]

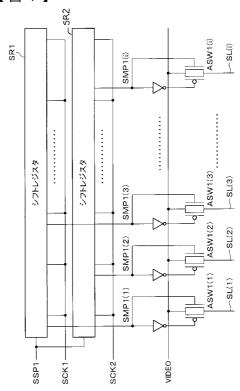

図4に、図2において上方に配置された第1のデータ信号線駆動回路SD1の回路構成を示す。高解像度用である第1のデータ信号線駆動回路SD1は、2系列のシフトレジスタSR1・SR2からの各出力が入力されることで、別途入力される映像信号VIDEOをサンプリングするアナログスイッチASW1(1)~ASW1(1) (1) を備えている。これらアナログスイッチASW1(1)~ASW1(i) にて、サンプリング回路が構成される。

#### [0056]

シフトレジスタSR1には、スタートパルス信号SSP1と、第1のクロック信号SCK 1 とが入力されるようになっており、シフトレジスタSR1から順次出力されるサンプリング信号SMP1(1),SMP1(3)・・・SMP1(i-1)は、アナログスイッチASW1(1),ASW1(3)~ASW1(i-1)へと供給され、アナログスイッチASW1(1),ASW1(3)~ASW1(i-1)を順次ONしていく。アナログスイッチASW1(1),ASW1(3)~ASW1(i-1)がONしている期間、別途入力されている映像信号VIDEOがサンプリングされ、対応するデータ信号線SL(1),SL(3),~SL(i-1)へと出力される。

20

10

30

50

### [0057]

一方、シフトレジスタSR2には、スタートパルス信号SSP1と、第2のクロック信号SCK2とが入力されるようになっており、シフトレジスタSR2から順次出力されるサンプリング信号SMP1(2),SMP1(4)・・・SMP1(i)は、アナログスイッチASW1(2),ASW1(4)~ASW1(i)へと供給され、アナログスイッチASW1(2),ASW1(4)~ASW1(i)を順次ONしていく。アナログスイッチASW1(2),ASW1(4)~ASW1(i)がONしている期間、映像信号VIDEOがサンプリングされ、対応するデータ信号線SL(2),SL(4),~SL(i)へと出力される。

### [0058]

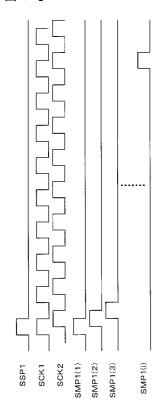

このような第1のデータ信号線駆動回路SD1に関わる各信号のタイミングチャートを図5に示す。第1のクロック信号SCK1と第2のクロック信号SCK2とは、位相が1/4周期ずれている関係にあり、スタートパルス信号SSP1が、シフトレジスタSR1とシフトレジスタSR2とに供給されると、各シフトレジスタSR1・SR2は、供給されている第1のクロック信号SCK1或いは第2のクロック信号SCK2に同期して、サンプリング信号SMP1(1),SMP1(2)・・・SMP1(i)を順次出力する。

#### [0059]

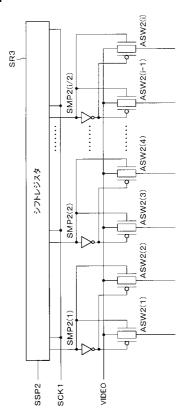

一方、図 6 に、図 2 において下方に配置された第 2 のデータ信号線駆動回路 S D 2 の回路 構成を示す。第 2 のデータ信号線駆動回路 S D 2 は、低解像度用のデータ信号線駆動回路 であって、シフトレジスタ S R 3 のみを 1 つ備えている。シフトレジスタ S R 3 には、ス タートパルス信号 S S P 2 と第 1 のクロック信号 S C K 1 とが入力される。

### [0060]

シフトレジスタSR3から順次出力されるSMP2(1),SMP2(2)・・・SMP2(i/2)は、アナログスイッチASW2(1),ASW2(2)~ASW2(i)へと供給され、アナログスイッチASW2(1),ASW2(2)~ASW2(i)を2個同時に順次ONしていく。アナログスイッチASW2(1),ASW2(2)~ASW2(1)がONしている期間、映像信号VIDEOが、対応するデータ信号線SL(1),SL(2),~SL(i)へと2本ずつ出力される。

## [0061]

このような第 2 のデータ信号線駆動回路 S D 2 に関わる各信号のタイミングチャートを図7 に示す。スタートパルス信号 S S P 2 が、上記シフトレジスタ S R 3 に供給されると、シフトレジスタ S R 3 は、供給されている第 1 のクロック信号 S C K 1 に同期して、サンプリング信号 S M P 2 ( 1 / 2 ) を順次出力する

## [0062]

このように、第2のデータ信号線駆動回路SD2では、2つのアナログスイッチが同時に制御され、映像信号VIDEOが2本のデータ信号線SL・SLに同時に供給されるようになっている。したがって、第1のデータ信号線駆動回路SD1を用いて画素アレイARYに表示を行った場合と比べて、表示上の解像度が半分となる。

#### [0063]

ところで、第1及び第2の2つのデータ信号線駆動回路SD1・SD2を備えた上記構成においては、2つのデータ信号線駆動回路SD1・SD2で共用される第1のクロック信号(第1の信号)SCK1は、2つのデータ信号線駆動回路SD1・SD2に共通して入力させている。これにより、第1のクロック信号SCK1を第2のデータ信号線駆動回路SD2に別途入力させる構成に比べて、外部インターフェースの構造の簡略化できる。

## [0064]

なお、第1のクロック信号SCK1を、2つのデータ信号線駆動回路SD1・SD2に共通して入力させる構成とした場合、第1のデータ信号線駆動回路SD1が駆動される場合、第2のデータ信号線駆動回路SD2へも供給されるが、第2のデータ信号線駆動回路SD2には、スタートパルス信号SSP2が入力されていないため、第2のデータ信号線駆

10

20

30

40

動回路SD2が動作することはない。

#### [0065]

しかしながら、第1のクロック信号SCK1を単に共通して入力させると、前述したように、第1のクロック信号SCK1と、単独で入力される第2のクロック信号SCK2(第2の信号)における配線負荷の違いに起因して、第1のクロック信号SCK1及び第2のクロック信号SCK2の両方を用いる第1のデータ信号線駆動回路SD1において、第1及び第2のクロック信号SCK1・SCK2間で信号遅延量に差が生じてしまい、位相関係がずれてしまう。第1及び第2のクロック信号SCK1・SCK2の位相関係がずれると、第1のデータ信号線駆動回路SD1での映像信号VIDEOのサンプリングタイミングに微妙なずれが出てしまい、画面品位が低下する。また、該位相関係のずれを、外部回路においてクロック信号を補正することで対処しようとすると、消費電力のアップを伴ってしまう。

#### [0066]

そこで、本実施の形態では、図1に示すように、単独で入力される第2のクロック信号SCK2用の配線2にダミー配線3を設けて、共通して入力される第1のクロック信号SCK1用の配線1と単独で入力される第2のクロック信号SCK2用の配線2との配線負荷を揃えるようになっている。ここでは、配線負荷の調整は、各配線1・2の時定数、つまり、前述したように時定数 = 容量C\*抵抗R( = CR)を調整するようになっている。配線2の配線負荷が配線1の配線負荷と揃うように調整するにあたり、時定数にて近似される各配線の時定数を揃えることで、配線負荷の調整を容易に行うことができる。

#### [0067]

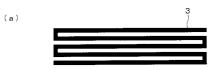

詳細には、図1に示すように、ダミー配線3は、データ信号線駆動回路SD1よりも基板端部側の信号入力部5に近い空き領域であって、表示に寄与する表示部とはならないが、対向電極COMを有する対向基板との間に液晶層を挟持している領域に、九十九折状に形成されている(図8(a)参照)。このような領域にダミー配線3を設けることで、図8(b)に示すように、該ダミー配線3を一方の電極、対向電極COMを他の電極4とし、液晶層を誘電体5として付加容量部7が形成され、これが配線負荷調整手段として機能するようになる。

## [0068]

このようなダミー配線3を設けて配線2の配線負荷を配線1の配線負荷と揃えることで、第1及び第2のクロック信号SCK1・SCK2の配線負荷が揃い、第1のデータ信号線駆動回路SD1における第1及び第2のクロック信号SCK1・SCK2間での信号遅延量の差を許容な範囲とでき、位相関係を正しく保持することができる。その結果、第1のデータ信号線駆動回路SD1において、映像信号VIDEOのサンプリングが正確に実施でき、画面品位が向上する。

### [0069]

また、この場合、表示装置としてそもそも備えている部材を利用して配線負荷調整手段としての付加容量部7を構成しているので、配線負荷調整手段を具備したことによるコスト 上昇を最小限に抑えることができる。

### [0070]

しかも、本実施の形態のような液晶層を備えた液晶表示装置の場合、配線1と配線2とで配線負荷が違ってくる最大の原因は、第2のデータ信号線駆動回路SD2にまで引き回される配線部分1 aが、液晶層と対向電極COMとの間で容量を形成するためである(図1参照)。したがって、特に、液晶表示装置の場合、このように、ダミー配線3と液晶層と対向電極COMとで容量を形成して付加容量部7とすることで、配線2に設けるダミー配線3を上記した引き回し配線部分1 aと同じ材質を用い、配線1と配線2とで各配線自身がもつ抵抗Rを等しくしておくことで、配線1・2間で容易に時定数を揃えることができる。簡単に配線負荷を調整することができる。

#### [0071]

なお、ここではダミー配線3を、信号入力部5近傍の空き領域に九十九折状に形成したが

20

30

40

10

20

30

40

50

、対向電極 C O M と平行平板を成すようにダミー配線を平板状としてもよい。また、図 9 (a)(b)に示すように、表示部の周囲にダミー配線 3 (太線で記載)を形成して付加容量部 7 としてもよい。このように、ダミー配線 3 を、第 2 のデータ信号線駆動回路 S D 2 にまで引き回される配線部分 1 a に沿わせる、或いは、配線部分 1 a と対称を成すように画素アレイ A R Y の反対側に設けることで、材質、配線幅を等しくした場合、配線長を同じにするだけで、配線 1 ・ 2 間で容易に時定数を揃えることができる。

#### [0072]

また、付加容量部 7 としては、ダミー配線 3 と液晶層と対向電極 C O M とで容量を形成する構成以外に、例えば、図 8 (b)に示すダミー配線 3 とで容量を形成する他の電極 4 として、液晶容量 C L の図示しない画素電極を形成すると同じ透明導電膜や、コンタクトホールを用いて配線の交差を実現するために別途設けられる別の金属層を用い、これら透明導電膜や金属層である導電膜と、ダミー配線 3 との間に介在する層間絶縁膜を誘電体 5 として容量を形成して、付加容量部 7 としてもよい。

### [0073]

または、画素アレイARYに形成されるアクティブ素子である薄膜トランジスタSWを構成する層を利用し、図8(c)に示すように、他の電極4としては薄膜トランジスタSWの半導体層9に不純物を添加するなどして、高抵抗の金属のような特性を持たせて電極として機能させ、金属のような特性をもつ該半導体層9と、ダミー配線3との間に介在するゲート絶縁膜8を誘電体5として容量を形成して、付加容量部7としてもよい。

#### [0074]

何れの付加容量部7においても、表示装置としてそもそも備えている部材を利用して構成し得るので、付加容量部7として配線負荷調整手段を具備したことによるコスト上昇を最小限に抑えることができる。なお、このように、液晶層と対向電極COMとを利用しない構成は、時定数を揃えて配線負荷を調整するにおいては、液晶層を利用したもの程に容易ではないが、液晶層や対向電極COMが積層していない部分にも設けることができ、レイアウト上の自由度が高い。

## [0075]

以上のように、本実施の形態のアクティブマトリックス型の液晶表示装置では、第1のデータ信号線駆動回路SD1で使用される第1及び第2のクロック信号SCK1・SCK2のうちの第1のクロック信号SCK1のみが第2のデータ信号線駆動回路SD2にも共通して入力されるといった構成においても、第1及び第2のクロック信号SCK1・SCK2の配線負荷(正確には、第1及び第2のクロック信号SCK1・SCK2を供給する各配線1・2の配線負荷)を揃える付加容量部7が設けられているので、外部回路側で第1及び第2のクロック信号SCK1・SCK2の加工を施して消費電力をアップさせるようなことなく、配線引き回しの違いによる影響を受けることなく良好な表示を行い得る。

## [0076]

なお、本実施の形態では、第1のクロック信号SCK1が共通して入力される回路をデータ信号線駆動回路SD2としたが、次にフレームにおけるデータ信号線SL(1)~SL(1)~SL(1)~SL(1)~SL(1)~SL(1)~SL(1)~SL(1)~SL(1)~SL(1)~SL(1)を帰線期間に予備充電させる予備充電回路であってもよい。また、ここでは、2つのデータ信号線駆動回路SD1・SD2は、対応解像度が異なるものとしたが、カラー表示用と白黒表示用のデータ信号線駆動回路であってもよく、また、2つのデータ信号線駆動回路SD1・SD2が連動して駆動して、スーパーインポーズ表示等を可能にする構成などであってもよく、さらには、配線負荷調整手段が走査信号線駆動回路に設けられている構成であってもよい。

## [0077]

要するに、少なくとも1つの駆動回路(データ信号線駆動回路には限らない)に、互いに関わりのある複数の信号(2種類とは限らない)が入力され、そのうちの少なくとも1つの信号が他の回路(駆動回路でなくてもよい)へも引き回されて共通して入力される構成において、このようなダミー配線(平板状も含む)3を設けて容量を形成させ、関わりの

ある信号間の配線負荷を揃えればよい。

#### [0078]

なお、本発明では、互いに関わりのある複数の信号として、第1及び第2の信号間の配線 負荷を揃えるといった表現を用いているが、これは、例えば上記した配線1・2の配線負 荷を等しく揃える場合をもちろん含むが、要は、第1及び第2の信号が共に使用される駆 動回路内において、単独で入力する第2の信号と他の回路にも共通して入力される第1の 信号との間で、各配線負荷にてそれぞれの量遅延した各信号の位相関係が、信号設計時と 同じであればよく、極端に言えば一方の信号を大きく遅延させて位相を1周期分遅らせる ことで、位相を合わせてもよい。

#### [0079]

また、ここでは、互いに関わりのある複数の信号である第1及び第2の信号として、クロック信号を例示したが、例えば、複数のビットで構成されるデジタル映像信号であって、少なくとも2つのビット群に分けられているデジタル映像信号である場合もある。つまり、6 ビットのデジタル映像信号を、第1のデータ信号線駆動回路SD1へ入力させる一方、前記6 ビットのデジタル映像信号のうち、上位3 bitだけを第2のデータ信号線駆動回路SD2に入力して、データ信号線駆動回路SD1とSD2とで、異なる諧調に対応するといった場合が考えられる。

### [0080]

このような場合も、外部インターフェースの簡略化から、映像信号VIDEOを上位3ットと下位3ビットに分け、上位3ビットのみを他の回路へも入力させる構成がとられる。 【 0 0 8 1 】

このような場合に、上記した配線負荷に起因して、第1のデータ信号線駆動回路SD1へ入力される6ビットのデジタル映像信号のうち、上位3ビットの信号の配線負荷が下位3ビットの信号の配線負荷とが異なった場合、第1のデータ信号線駆動回路SD1において、デジタル映像信号をサンプリングする際に、位相差が発生し、サンプリングミスが起きる可能性があるが、本発明を用いて位相差を揃えることにより、上記サンプリングミスを起こすことなく。回路は正常に機能することが可能となる。

#### [0082]

## 【発明の効果】

本発明の表示装置は、以上のように、走査信号線を駆動する走査信号線駆動回路と、上記走査信号線に交差するように配されたデータ信号線を駆動するデータ信号線駆動回路とを備えた表示装置において、上記走査信号線駆動回路或いはデータ信号線駆動回路の少なくとも一方の駆動回路に、少なくとも第1,第2の信号が入力され、他の回路に第1の信号が共通して入力されるように構成されており、上記駆動回路に入力される第2の信号の配線負荷と、上記他の回路にも共通に入力される第1の信号の配線負荷とを揃える配線負荷調整手段が設けられていることを特徴としている。

## [0083]

データ信号線駆動回路や走査信号線駆動回路が、複数個設けられる構成では、外部インターフェースの構造の簡略化から、例えば、ある駆動回路で使用される2系統の第1及び第2のクロック信号のうちの1系統の第1のクロック信号(第1の信号)のみが他の駆動回路にも共通して入力されるといった構成となる場合がある。このような場合、第1及び第2のクロック信号を使用する駆動回路において、単独で入力される第2のクロック信号(第2の信号)との配線負荷の違いにより信号遅延量に差が発生してしまう結果、両クロック信号の位相関係にずれが生じて、画面品位が低下することとなる。また、該位相関係のずれを、外部回路においてクロック信号を補正することで対処しようとすると、消費電力のアップを伴ってしまう。

#### [0084]

しかしながら、このように、駆動回路に単独で入力される第2の信号の配線負荷と、他の回路にも共通に入力される第1の信号の配線負荷とを揃える配線負荷調整手段を設けることで、外部回路においてクロック信号に補正を施して、消費電力のアップを伴うようなこ

10

20

30

40

となく、上記した両クロック信号間での信号遅延量の差による位相関係の差を許容な範囲 として、画面品位を良好に保つことが可能となる。

#### [0085]

つまり、上記の構成により、複数系統のクロック信号等の互いに関わりのある複数の信号が駆動回路に入力されるにおいて、外部インターフェースの構造の簡略化を図るべく、一部は単独で入力され(第2の信号)、一部は他の回路と共通して入力される(第1の信号)といった、関わりのある複数の信号間で異なる配線の引き回しで入力されたとしても、消費電力をアップさせることなく、引き回しの違いによる影響を受けることなく良好な表示を行い得る表示装置を提供することができるという効果を奏する。

#### [0086]

また、上述したように、本発明は、上記第1の信号が、共通の入力端より信号線を共用して、上記駆動回路及び上記他の回路に入力される構成との組み合わせが適している。第1の信号が、共通の入力端より信号線を共用して入力させる構成とすることで、例えば、入力信号の入力端の数を減らすことができ、基板面積を有効活用することができるという効果を奏する。

#### [0087]

本発明の表示装置は、さらに、上記配線負荷調整手段が、各配線の時定数を揃えるようになっていることを特徴とすることもできる。

#### [0088]

配線負荷を調整するにあたり、時定数 = 容量 C \* 抵抗 R ( = C R ) にて近似される時定数を揃えるよう設計することで、配線負荷の調整を容易に行うことができるという効果を奏する。

### [0089]

本発明の表示装置は、さらに、上記走査信号線と上記データ信号線とは基板上に形成されると共に、該基板と対向電極が形成された基板との間に液晶層を挟持しており、上記配線負荷調整手段は、上記液晶層を誘電体として用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、該ダミー配線上の上記液晶層と、上記対向電極とを備えていることを特徴とすることもできる。

## [0090]

上記の構成によれば、配線負荷の小さい、駆動回路に単独で入力される第2の信号の配線にダミー配線を設け、該ダミー配線と対向電極と液晶層とで、配線負荷調整のための容量を構成しているので、表示装置としてそもそも備えている部材を利用して構成することができ、配線負荷調整手段を具備したことによるコスト上昇を最小限に抑えることができるという効果を併せて奏する。

## [0091]

また、液晶層を有する液晶表示装置の場合、駆動回路に単独で入力される第2の信号の配線負荷と、他の回路にも共通に入力される第1の信号の配線負荷とが違ってくる最大の原因は、他の回路にも入力される第1の信号における他の回路へと引き回される配線部分が、液晶層と対向電極との間で容量を形成し、これが、無視できない程度に大きいためである。

## [0092]

したがって、このような構成とすることで、ダミー配線を、上記した他の回路へと引き回される配線部分と条件的に等しく設けることで、簡単に配線負荷を調整することができるという効果も奏する。

#### [0093]

本発明の表示装置は、さらに、上記走査信号線と上記データ信号線とは基板上に形成されると共に、該基板上にはさらに層間絶縁膜と導電膜とが形成されており、上記配線負荷調整手段は、上記層間絶縁膜を誘電体として用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、上記層間絶縁膜と、上記導電膜とを備えていることを特徴とすることもできる。

10

20

30

40

#### [0094]

上記の構成によれば、配線負荷の小さい、駆動回路に単独で入力される第2の信号の配線にダミー配線を設け、該ダミー配線上に形成された層間絶縁膜と導電膜とで、配線負荷調整のための容量を構成しているので、これによっても、表示装置としてそもそも備えている部材を利用して構成することができ、配線負荷調整手段を具備したことによるコスト上昇を最小限に抑えることができるという効果を併せて奏する。

#### [0095]

本発明の表示装置は、さらに、上記走査信号線と上記データ信号線との各交点には薄膜トランジスタが設けられており、上記配線負荷調整手段は、薄膜トランジスタのゲート絶縁膜を構成する層を誘電体として用い、上記駆動回路に入力される第2の信号の配線に接続されたダミー配線と、該ダミー配線に積層して配置された上記薄膜トランジスタのゲート絶縁膜及び半導体層をそれぞれ構成する各層とを備えていることを特徴とすることもできる。

## [0096]

上記の構成によれば、配線負荷の小さい、駆動回路に単独で入力される第2の信号の配線にダミー配線を設け、ダミー配線と、これに積層して配されている薄膜トランジスタのゲート絶縁膜の構成層及び半導体層の構成層とで、配線負荷調整のための容量を構成しているので、これによっても、表示装置としてそもそも備えている部材を利用して構成することができ、配線負荷調整手段を具備したことによるコスト上昇を最小限に抑えることができるという効果を併せて奏する。

【図面の簡単な説明】

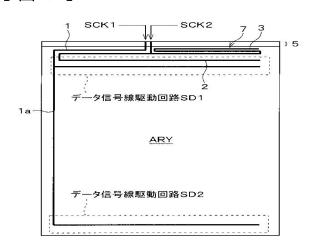

- 【図1】本発明の実施の一形態を示すもので、ダミー配線が設けられた液晶表示装置の配線要部を概略的に示す平面図である。

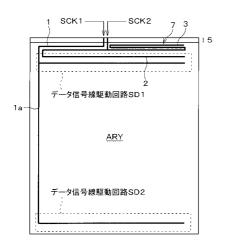

- 【図2】上記液晶表示装置の構成の概略を示すブロック図である。

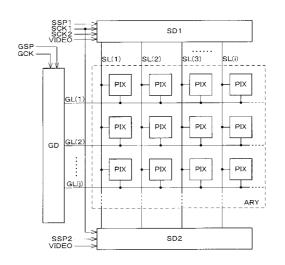

- 【図3】上記液晶表示装置における画素の構成を示す等価回路図である。

- 【図4】上記液晶表示装置における第1のデータ信号線駆動回路の一構成例を示す回路ブロック図である。

- 【図5】図4の第1のデータ信号線駆動回路に関わる各信号のタイミングチャートである

- 【図6】上記液晶表示装置における第2のデータ信号線駆動回路の一構成例を示す回路ブ 30 ロック図である。

- 【図7】図6の第2のデータ信号線駆動回路に関わる各信号のタイミングチャートである

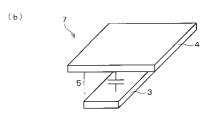

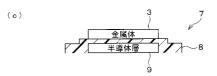

- 【図8】図8(a)は、ダミー配線の一例を拡大して示す図面であり、図8(b)は、配線負荷調整手段を構成する容量部の構成を示す図面であり、図8(c)は、薄膜トランジスタの半導体層を用いて構成される配線負荷調整手段を示す図面である。

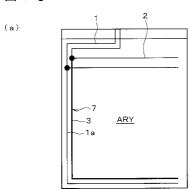

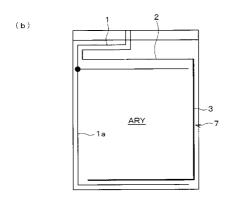

- 【図9】(a)(b)ともに、ダミー配線を形成して配線負荷調整手段を構成する容量を設ける位置の例を示す平面図である。

- 【図10】従来の一般的な液晶表示装置の構成の概略を示すプロック図である。

- 【図11】データ信号線駆動回路を2つ備えた液晶表示装置において、2つのデータ信号 40線駆動回路間で1つのクロック信号ck1・ck2を共通して入力させている構成を示す 平面図である。

- 【図12】上記2つのデータ信号線駆動回路に入力されるクロック信号 c k 1 ・ c k 2 の 波形図である。

#### 【符号の説明】

- 1 配線(第1の信号の配線)

- 2 配線(第2の信号の配線)

- 3 ダミー配線

- 5 信号入力部

- 7 付加容量部(配線負荷調整手段)

20

ARY 画素アレイ

CL 液晶容量

SW 薄膜トランジスタ

SD1 データ信号線駆動回路

S D 2 データ信号線駆動回路 G D 走査信号線駆動回路

## 【図1】

## 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

# 【図11】

# 【図12】

## フロントページの続き

(51) Int.CI.<sup>7</sup>

G 0 9 G 3/20 6 2 3 A G 0 9 G 3/20 6 8 0 G G 0 9 G 3/36

(72)発明者 恩田 衛

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

FΙ

審査官 井口 猶二

(56)参考文献 特開昭 6 1 - 1 1 4 2 2 6 ( J P , A )

特開平03-135597(JP,A)

特開平04-271322(JP,A)

特開平08-015713(JP,A)

特開平08-022028(JP,A)

特開平10-239655(JP,A)

特開平10-268350(JP,A)

特開2000-155338(JP,A)

(58)調査した分野(Int.CI.<sup>7</sup>, DB名)

G02F 1/133 550

G02F 1/1345

G09G 3/20

G09G 3/36

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | JP3666662B2                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2005-06-29 |  |  |

| 申请号            | JP2002363037                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2002-12-13 |  |  |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |  |  |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |  |  |

| [标]发明人         | 鷲尾一<br>前田和宏<br>恩田衛                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |

| 发明人            | 鷲尾 一<br>前田 和宏<br>恩田 衛                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |

| IPC分类号         | G02F1/1345 G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |

| CPC分类号         | G09G3/3688 G09G3/3607 G09G3/3677 G09G2300/043 G09G2310/0248 G09G2320/0223 G09G2330 /021                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |

| FI分类号          | G02F1/133.550 G02F1/1345 G09G3/20.612.L G09G3/20.621.M G09G3/20.622.A G09G3/20.623.A G09G3/20.680.G G09G3/36 G11C19/00 G11C19/00.J                                                                                                                                                                                                                                                                                                              |         |            |  |  |

| F-TERM分类号      | 2H092/GA59 2H092/GA61 2H092/JB22 2H092/JB31 2H092/NA01 2H092/PA06 2H093/NA16 2H093 /NC16 2H093/NC22 2H093/NC26 2H093/NC27 2H093/ND32 2H093/ND39 2H093/ND54 2H193/ZA04 2H193/ZA07 2H193/ZF37 5C006/AF50 5C006/AF52 5C006/BB16 5C006/BB27 5C006/BC03 5C006 /BC06 5C006/BC11 5C006/BC20 5C006/BC22 5C006/BC23 5C006/EB05 5C006/FA18 5C080/AA06 5C080/AA10 5C080/BB05 5C080/DD03 5C080/DD26 5C080/DD28 5C080/FF11 5C080/JJ02 5C080 /JJ03 5C080/JJ06 |         |            |  |  |

| 代理人(译)         | 木岛隆一<br>金子 一郎                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |

| 其他公开文献         | JP2004191888A                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |  |  |

## 摘要(译)

要解决的问题:为了提供将彼此相关的多个信号输入到驱动电路的配置,其中至少一个信号被路由到其他电路并且共同输入,布线负载在不处理信号本身的情况下抑制由它们之间的差异引起的相移,这导致功耗增加。 种类代码:A1第一和第二时钟信号SCK1和SCK2被输入到第一数据信号线驱动电路SD1。其中,第一时钟信号SCK1也共同输入到第二数据信号线驱动电路SD2。在布线2中设置虚设布线3,以便由于布线1和布线2之间的布线的不同而使布线负载相等,并且通过虚设布线3,液晶层和对电极形成附加电容部分7。它有。 点域1

## 【図1】