(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-64856

(P2008-64856A)

(43) 公開日 平成20年3月21日(2008.3.21)

(51) Int.Cl.

G02F 1/1343 (2006.01)

C23C 14/04 (2006.01)

F 1

G02F 1/1343

C23C 14/04

テーマコード(参考)

2 H 0 9 2

B 4 K 0 2 9

審査請求 未請求 請求項の数 5 O L (全 14 頁)

(21) 出願番号

(22) 出願日特願2006-240258 (P2006-240258)

平成18年9月5日 (2006.9.5)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100065385

弁理士 山下 橿平

(74) 代理人 100122921

弁理士 志村 博

(74) 代理人 100130029

弁理士 永井 道雄

(72) 発明者 原田 武彦

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 橋本 栄

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】反射型液晶表示パネルの製造方法

## (57) 【要約】

【課題】特別な工程を追加することなしに、対向電極と同じ仕事関数を有するITO膜を電極上に形成する反射型液晶表示パネルの製造方法を提供することを目的とする。

【解決手段】反射型の画素電極113を有する画素電極基板と透明電極117を有する対向基板との間に液晶層116が設けられ、透明電極117に対する仕事関数の差が、画素電極113と透明電極117の仕事関数差よりも小さい導電性薄膜が、画素電極の表面に形成された反射型液晶表示パネルの製造方法において、画素電極となる層の表面にある、画素を分離する領域である画素分離領域上にレジストを形成する工程と、レジストが形成された後、導電性薄膜を形成する工程と、レジストリフトオフ法によって、画素分離領域上に形成された導電性薄膜を除去する工程と、を含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

反射型の画素電極を有する画素電極基板と、透明電極を有する対向基板とが対向して設けられ、前記画素電極基板と前記対向基板との間に液晶層が設けられ、

前記透明電極に対する仕事関数の差が、前記画素電極と前記透明電極の仕事関数差よりも小さい導電性薄膜が、前記画素電極の表面に形成された反射型液晶表示パネルの製造方法において、

前記画素電極となる層の表面にある、画素を分離する領域である画素分離領域上にレジストを形成する工程と、

当該レジストが形成された後、前記導電性薄膜を形成する工程と、

レジストリフトオフ法によって、前記画素分離領域上に形成された前記導電性薄膜を除去する工程と、を含むことを特徴とする反射型液晶表示パネルの製造方法。

**【請求項 2】**

前記画素分離領域上の前記導電性薄膜が除去された後、当該導電性薄膜をマスクとして、前記画素電極となる層をエッチングして前記画素電極とする工程を含むことを特徴とする請求項 1 記載の反射型液晶表示パネルの製造方法。

**【請求項 3】**

反射型の画素電極を有する画素電極基板と、透明電極を有する対向基板とが対向して設けられ、前記画素電極基板と前記対向基板との間に液晶層が設けられ、

前記透明電極に対する仕事関数の差が、前記画素電極と前記透明電極の仕事関数差よりも小さい導電性薄膜が、前記画素電極の表面に形成された反射型液晶表示パネルの製造方法において、

前記画素を分離する領域である画素分離領域にレジストを形成する工程と、

当該レジストが形成された後、前記画素電極となる層と前記導電性薄膜とを形成する工程と、

レジストリフトオフ法によって、前記画素分離領域上の、前記画素電極となる層及び前記導電性薄膜を除去する工程と、を含むことを特徴とする反射型液晶表示パネルの製造方法。

**【請求項 4】**

前記画素電極上に形成された導電性薄膜は透明であることを特徴とする請求項 1 から 3 のいずれか 1 項記載の反射型液晶表示パネルの製造方法。

**【請求項 5】**

前記画素電極は、アルミニウム又はアルミニウムを主成分とする材料が用いられる特徴とする請求項 1 記載の反射型液晶表示パネルの製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、反射型液晶表示パネルの製造方法に関し、特に、透明電極に対する仕事関数の差が、画素電極と透明電極の仕事関数差よりも小さい導電性薄膜が画素電極上に形成された反射型液晶表示パネルの製造方法に関する。

**【背景技術】****【0002】**

近年、プロジェクションディスプレイの高精細化、小型化及び高輝度化が進展している。それについて、そのプロジェクションディスプレイのデバイスとして、小型、高精細であり、高い光利用効率が期待される反射型の液晶表示パネルが注目され、一部実用化もされてきている。

**【0003】**

反射型の液晶表示パネルは、通常、画素電極基板と対向基板と液晶層とから構成される。対向基板としては、通常、ガラス基板の表面に透明電極を形成したものが使用されており、代表的な透明電極としては、ITO (Indium Tin Oxide ; インジウム

10

20

30

40

50

ムすず酸化膜)が用いられている。

【0004】

ITOを対向基板側の透明電極に用いた反射型液晶表示パネルでは、特許文献1にも記載されているように、フリッカーや焼きつき防止のために対向電極との仕事関数差を小さくすることが重要である。

【0005】

その目的で、対向電極と同じ仕事関数を有するITO膜を画素電極上に形成する方法が提案されている。

【0006】

ITOは対向電極との仕事関数差をなくす効果がある以外に、材料としての光透過率が高いため、画素電極層の上に形成しても反射率の低下を抑制できる利点がある。 10

【0007】

しかし、導電性があるために反射層と同一パターンで形成する必要がある。

【特許文献1】特開2004-170604号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、ITOは化学種を用いたドライエッティングでのパターンの形成が困難である。

【0009】

アルゴン等を用いた逆スパッタリングによるエッティングでは、エッティングマスクであるレジストと選択比がとれず、また反射層の下層の酸化膜との選択性がないため、加工上の安定性が低くなっていた。そのため、この構造を実現することは困難であった。 20

【0010】

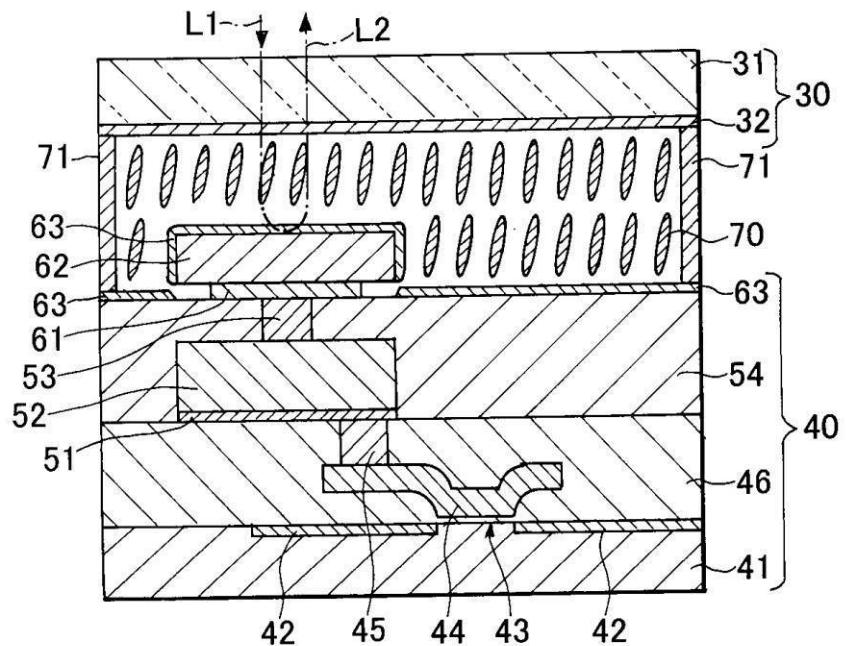

図13に示す特許文献1に記載される技術では、これを解決するために、画素電極基板の製造工程において画素電極を画素間で絶縁分離することを可能としている。

【0011】

しかしながら、図13に示した技術では、画素電極を画素間で絶縁分離するために、画素電極の下層に幅方向の断面積が画素電極の下面の面積よりも小さくなるような段差部分を形成する必要があるので、工程が増えていた。 30

【0012】

さらに、画素電極の下層に横方向に凹んだ領域を形成するため、その後の成膜工程や液晶層注入工程で空隙(ボイド)を形成する可能性が高く、液晶表示パネルの均質性や吸湿性等の問題から信頼性を損ねる可能性もあった。

【0013】

そこで、本発明は、特別な工程を追加することなしに、対向電極と同じ仕事関数を有するITO膜を電極上に形成する反射型液晶表示パネルの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0014】

本発明は、上記課題を解決するための手段として、反射型の画素電極を有する画素電極基板と、透明電極を有する対向基板とが対向して設けられ、前記画素電極基板と前記対向基板との間に液晶層が設けられ、前記透明電極に対する仕事関数の差が、前記画素電極と前記透明電極の仕事関数差よりも小さい導電性薄膜が、前記画素電極の表面に形成された反射型液晶表示パネルの製造方法において、前記画素電極となる層の表面にある、画素を分離する領域である画素分離領域上にレジストを形成する工程と、当該レジストが形成された後、前記導電性薄膜を形成する工程と、レジストリフトオフ法によって、前記画素分離領域上に形成された前記導電性薄膜を除去する工程と、を含むことを特徴とする。 40

【0015】

また、本発明は、反射型の画素電極を有する画素電極基板と、透明電極を有する対向基

10

20

30

40

50

板とが対向して設けられ、前記画素電極基板と前記対向基板との間に液晶層が設けられ、前記透明電極に対する仕事関数の差が、前記画素電極と前記透明電極の仕事関数差よりも小さい導電性薄膜が、前記画素電極の表面に形成された反射型液晶表示パネルの製造方法において、前記画素を分離する領域である画素分離領域にレジストを形成する工程と、当該レジストが形成された後、前記画素電極となる層と前記導電性薄膜とを形成する工程と、レジストリフトオフ法によって、前記画素分離領域上の、前記画素電極となる層及び前記導電性薄膜を除去する工程と、を含むことを特徴とする。

#### 【発明の効果】

#### 【0016】

本発明によれば、特別な工程を追加することなしに、対向電極と同じ仕事関数を有するITO膜を画素電極上に形成する反射型液晶表示パネルの製造方法を提供することが可能となつた。

10

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、添付図面を参照して本発明を実施するための最良の実施の形態を説明する。

#### 【0018】

##### [第1の実施の形態]

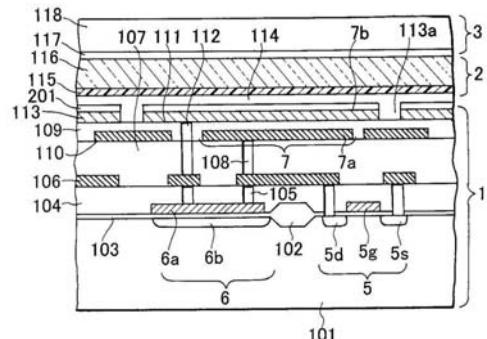

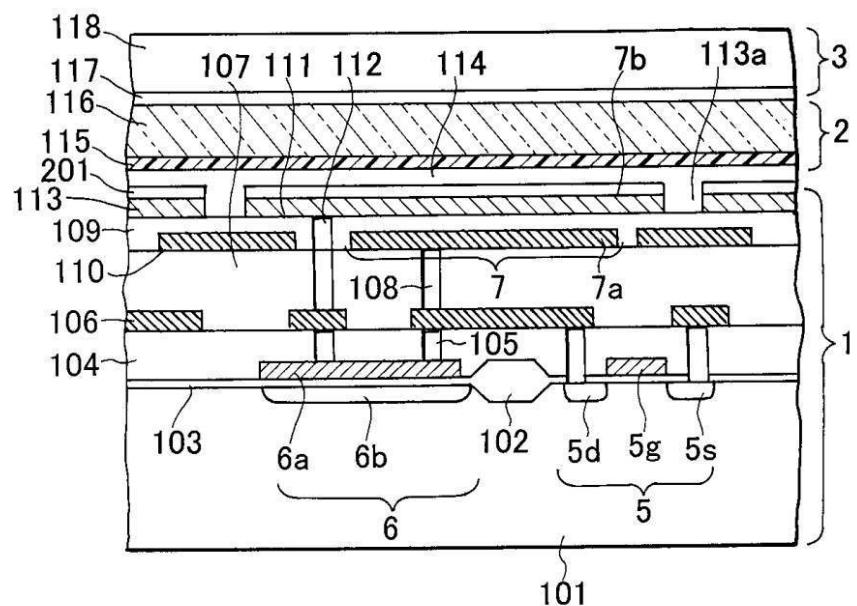

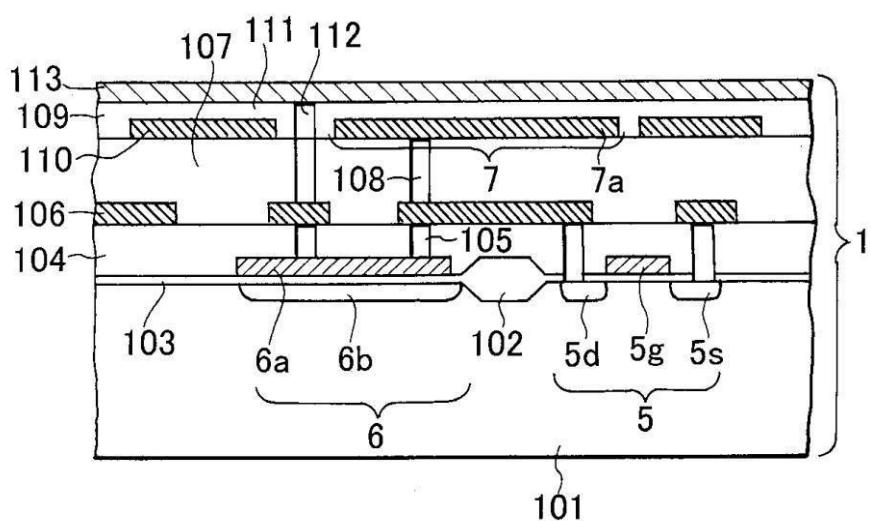

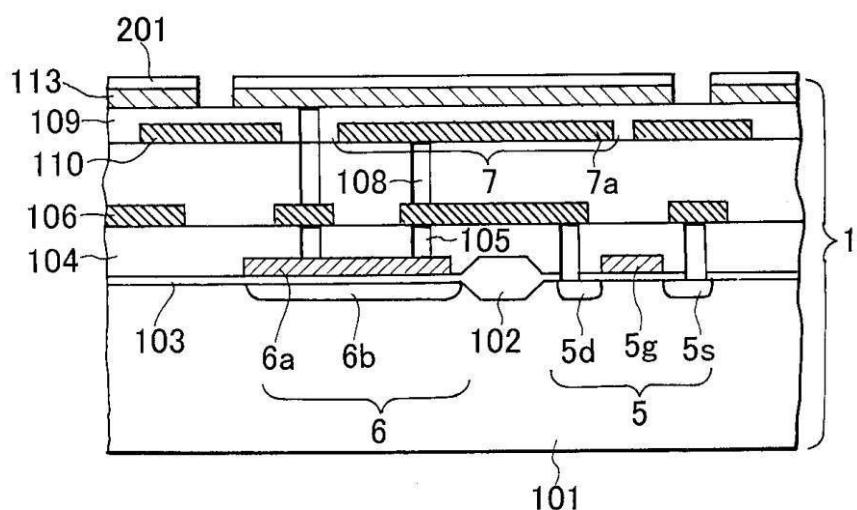

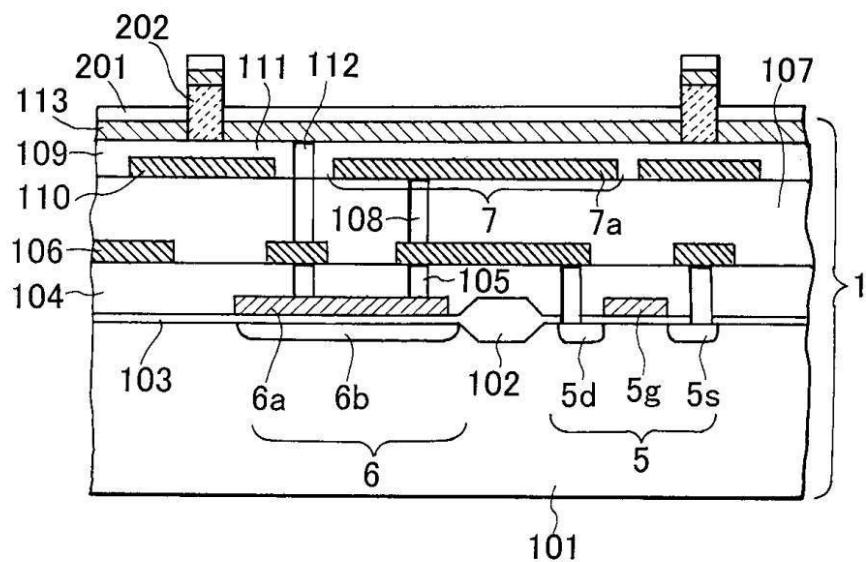

図1は、本発明の第1の実施形態としての反射型液晶表示パネルの画素表示部の基本構造を示す断面図である。

20

#### 【0019】

本実施の形態では、Si基板101上に、ゲート電極5g、ソース電極5s、ドレイン電極5dからなるMOS-FET5及び上部電極6a、下部電極6bからなる補助容量部6が形成されている。

20

#### 【0020】

MOS-FET5のドレイン電極5dは、第1接続部105及び信号線106を介して補助容量部6に接続されている。

#### 【0021】

そして、補助容量部6の上部電極6aは、第1接続部105、信号線106、第2接続部108及び第3接続部112を介して画素電極113に接続している。

30

#### 【0022】

画素電極113は、対向基板118側からの入射光を反射するとともに、液晶層116に対して選択的に駆動電圧を印加する。

#### 【0023】

画素電極113は、反射率が可視光域で90%以上と高く、一般にLSIの金属配線材として用いられているシリコン又は銅を数重量%以下添加したアルミニウム金属膜が用いられている。

#### 【0024】

ただし、反射率が可視光域で90%以上と高い金属膜であれば、アルミニウム以外の物を用いても構わない。

40

#### 【0025】

また、画素電極113の上部にはITO層201が設けられている。

#### 【0026】

さらに、画素電極113の画素間領域113a下部には、画素間領域113aより侵入した入射光がMOS-FET5に到達するのを防止するために遮光層110が形成されている。

#### 【0027】

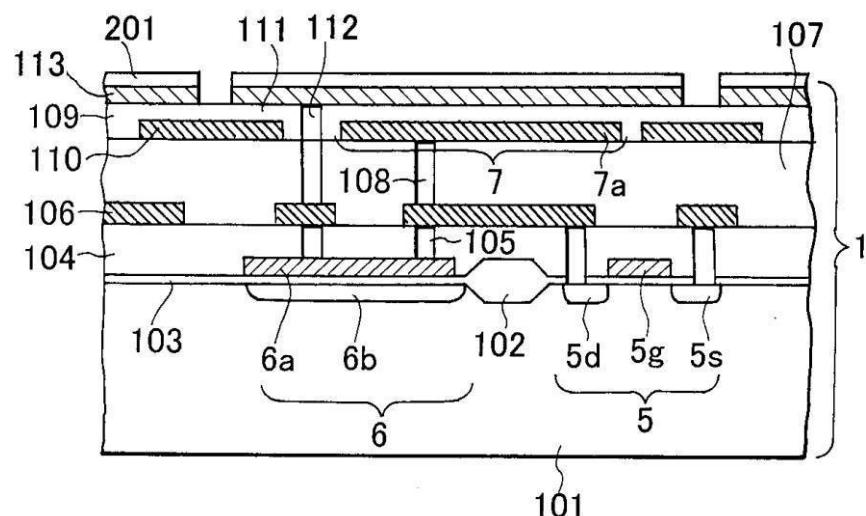

次に、図2～図8を用いて、図1に示した反射型液晶素子の製造方法を示す。以下の図において、図1で用いた符号と同一符号で示される各構成要素は同一の要素に相当する。

#### 【0028】

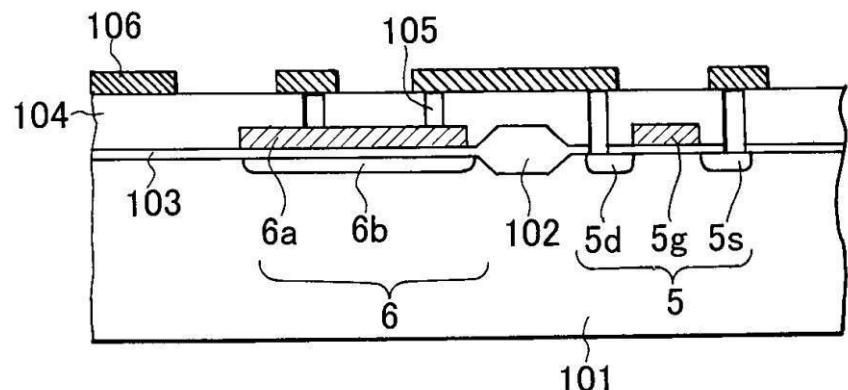

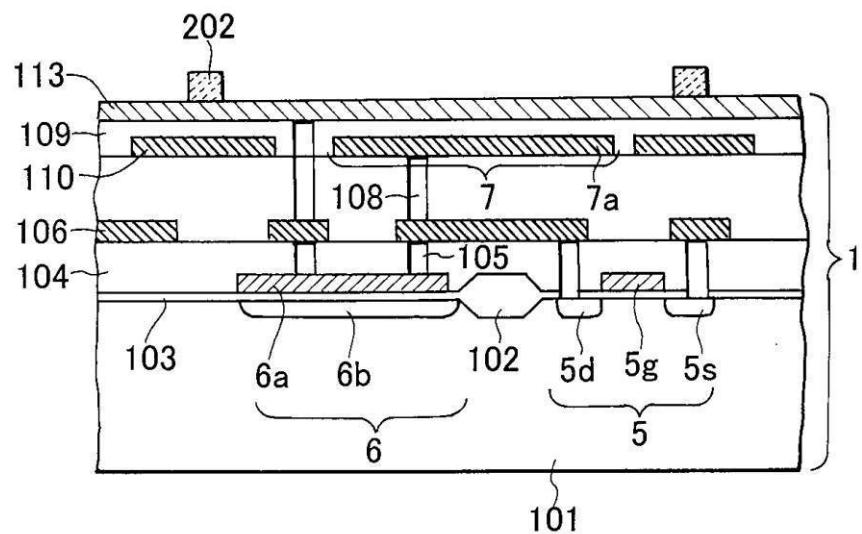

図2に示すように、Si基板101の上に、絶縁膜103を介してゲート電極5gを形

50

成し、ゲート電極 5 g の両側にイオン注入法等によりソース 5 s 及びドレイン 5 d を形成する。

【0029】

次に、NSG (Nondoped Silica Glass)、BPSG (Boron doped Phospho Silicate Glass) 等の材料からなる第1の絶縁膜 104 を減圧 CVD 法、常圧 CVD 法によって成膜する。それから、CMP (Chemical Mechanical Polishing) 法やレジストエッチバック法によって平坦化する。

【0030】

さらに、フォトリソグラフィとドライエッティングによって第1の接続孔 105 となる箇所を開口する。そして、Ti (チタン)、TiN (窒化チタン) 等からなるバリアメタルと W (タンクスチン) を成膜し、Wエッチバック又はW-CMP により第1の接続孔 105 を形成した。

【0031】

次いで、第1の金属配線層 106 をスパッタリング法等により、アルミニウム、若しくはシリコン又は銅を数重量 % 添加したアルミニウムを形成し、フォトリソグラフィとドライエッティングによって第1の金属配線層 106 を形成した。

【0032】

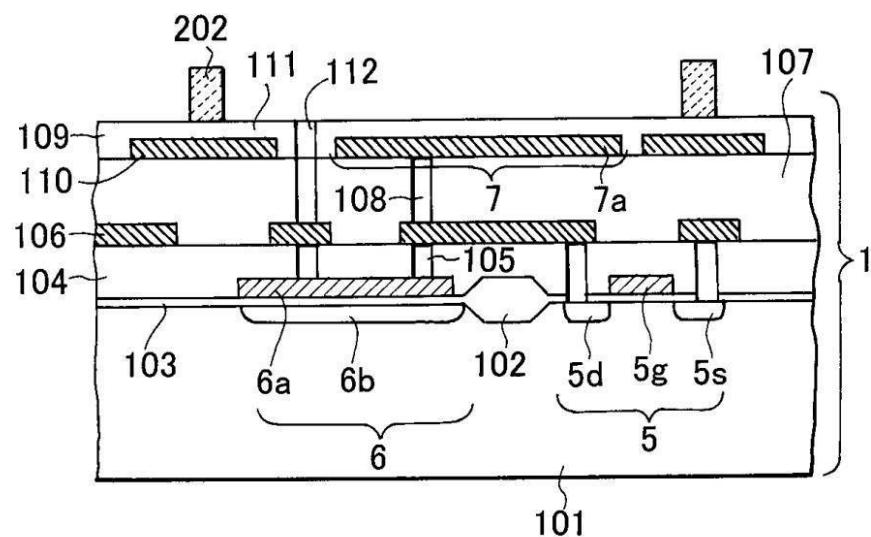

次いで、図3に示すように、第2の層間絶縁膜 107 をプラズマ CVD 法等で形成する。

【0033】

そして、フォトリソグラフィとドライエッティングによって第2の接続孔 108 となる箇所を開口する。それから、Ti (チタン)、TiN (窒化チタン) 等からなるバリアメタルと W (タンクスチン) を成膜し、Wエッチバック又はW-CMP により第2の接続孔 108 を形成した。

【0034】

次いで、遮光層 110 をスパッタリング法等により、アルミニウム、もしくは、シリコンまたは銅を数重量 % 添加したアルミニウムを形成し、フォトリソグラフィとドライエッティングとにより第2の接続孔 108 を形成した。

【0035】

次いで、第3の層間絶縁膜 109 をプラズマ CVD 法等で形成する。それから、フォトリソグラフィとドライエッティングによって第3の接続孔 112 となる箇所を開口する。そして、Ti (チタン)、TiN (窒化チタン) 等からなるバリアメタルと W (タンクスチン) を成膜し、Wエッチバック又はW-CMP により第3の接続孔 112 を形成した。

【0036】

次いで、画素電極 113 を AlSi 又は AlCu 層のスパッタリング法により成膜した。

【0037】

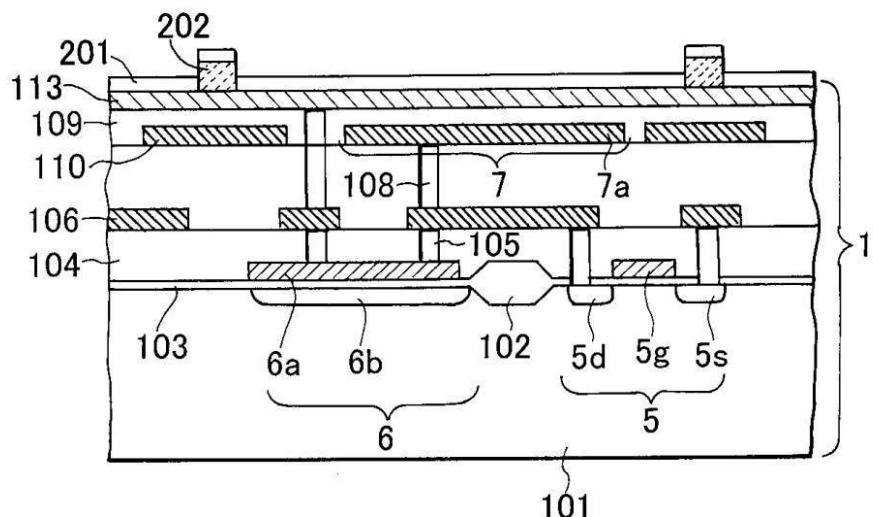

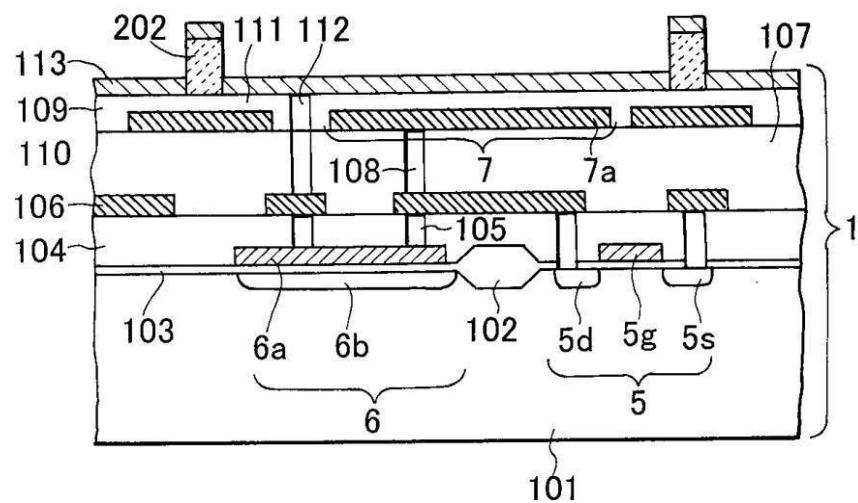

次いで、図4に示すように、画素分離領域にレジストパターン 202 を形成する。このとき、レジストパターンは、側壁が垂直又は逆メサ(台形)状が望ましい。

【0038】

次いで、図5に示すように、ITO 層 201 を蒸着法又はスパッタリング法で形成する。

【0039】

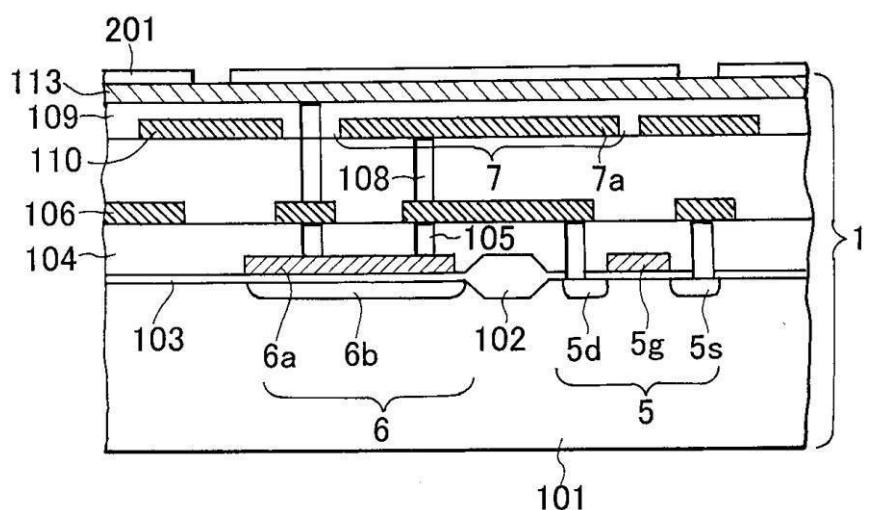

次いで、図6に示すように、レジストリフトオフ法で画素分離領域のITOをレジストパターン 202 とともに除去する。

【0040】

一般に、レジストリフトオフ法は、有機溶媒でレジストパターンを膨潤させてレジスト側壁に薄く被膜した材料を断片化して、レジストパターン上の材料を浮き上がらせる。しかし、ITO層を安定的に除去するために、超音波洗浄や高压ジェットによるリンスを適宜入れると良い。

10

20

30

40

50

## 【0041】

次いで、図7に示すように、ITOをマスクとして、画素電極113をドライエッチングによりパターン形成する。

## 【0042】

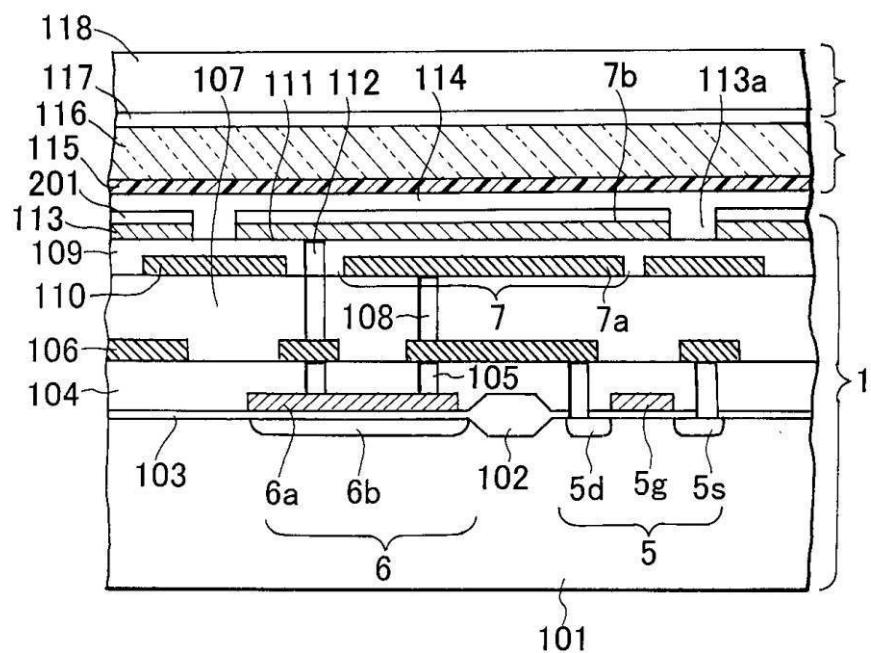

その後、図8に示すように、パッシベーション層114をプラズマCVD法と、必要に応じてCMP法やレジストエッチバック法による平坦化工程で平坦化膜114を形成する。

## 【0043】

次いで、液晶層116に配向性を持たせるための配向膜115を形成する。そして、別途作成したITO(インジウム錫酸化膜)などの透明導電性材料からなる対向電極117が形成された対向基板118とをシール材を介して対向させ、液晶注入口から液晶を注入して、液晶層2を形成する。10

## 【0044】

最後に、液晶注入口を封止することで図1に示した反射型液晶素子が製造される。

## 【0045】

## [第2の実施の形態]

次に、本発明の第2の実施の形態について説明する。

## 【0046】

本実施の形態の反射型液晶表示パネルが第1の実施の形態と異なるのは、図3から図7を用いて説明した画素電極層113及びITO層201付近の製造方法のみである。20

## 【0047】

第1の実施形態では、図3で示したように、第3の接続孔を形成した後に画素電極113を、スパッタリング法等によりアルミニウム、もしくは、シリコンまたは銅を数重量%添加したアルミニウムを成膜し、フォトリソグラフィとドライエッチングして形成した。

## 【0048】

一方、本実施形態では、図9に示したように、第3の接続孔を形成した後にレジストパターン202を形成する。

## 【0049】

このとき、レジストパターンは、側壁が垂直又は逆メサ(台形)状が望ましい。

## 【0050】

次いで、図10に示したように、画素電極113をスパッタリング法等により、アルミニウム、若しくはシリコン又は銅を数重量%添加したアルミニウムを成膜し、フォトリソグラフィとドライエッチングして形成した。30

## 【0051】

次いで、図11に示すように、ITO層201を蒸着法又はスパッタリング法で形成する。

## 【0052】

次いで、図12に示すように、レジストリフトオフ法で画素分離領域のITO層及び画素電極層をレジストパターン202とともに除去する。

## 【0053】

第1の実施の形態と同様、一般に、レジストリフトオフ法は、有機溶媒でレジストパターンを膨潤させてレジスト側壁に薄く被膜した材料を断片化して、レジストパターン上の材料を浮き上がらせる。しかし、ITO層及び画素電極層を安定的に除去するために、超音波洗浄や高压ジェットによる rinsing を適宜入れると良い。40

## 【0054】

この後の工程及び構造については、第1の実施形態の図8を用いて説明したものと同様なので省略する。

## 【0055】

本実施形態では、図11と図12で示したように、ITO層と画素電極パターンを1回のリフトオフで一括形成できるので、第1の実施形態よりも、更に工程を簡略化できる。50

**【0056】**

なお、本発明は、上記各実施の形態に限定されず種々の変形実施が可能である。

**【0057】**

例えば、本発明の反射型液晶表示パネルは、液晶プロジェクタに限らず、その他の表示装置、各種携帯型電子機器及び各種情報処理端末などにおける映像表示部に広く適用することが可能である。

**【産業上の利用可能性】****【0058】**

本発明は、液晶プロジェクタなどに利用される反射型液晶表示パネルの製造に利用可能である。

10

**【図面の簡単な説明】****【0059】**

【図1】本発明の第1の実施形態としての反射型液晶表示パネルの画素構成を示す断面図である。

10

【図2】本発明の第1の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図3】本発明の第1の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図4】本発明の第1の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図5】本発明の第1の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図6】本発明の第1の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図7】本発明の第1の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図8】本発明の第1の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図9】本発明の第2の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図10】本発明の第2の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図11】本発明の第2の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図12】本発明の第2の実施形態としての反射型液晶表示パネルの製造方法を示す断面図である。

10

【図13】従来の反射型液晶表示パネルの構成を示す断面図である。

**【符号の説明】****【0060】**

- 1 アクティブマトリクス基板

- 2 液晶層

- 3 透明基板

- 5 MOS-FET

- 5s ソース(入力端子)

- 5d ドレイン(出力端子)

- 5g ゲート電極(制御端子)

- 6 補助容量部

- 6a 上部電極

- 6b 下部電極

- 101 シリコン基板

40

50

- 102 分離絶縁部

104、107、109、111、114 絶縁体層

105 コンタクトホール

106 信号線

108、112 ヴィアホール

109 遮光層

113 画素電極層

113a 画素分離領域

114 パッシベーション層

115 配向層

116 液晶層

117 対向電極

118 対向基板

201 ITO層

202 レジスト

10

【図1】

【図2】

【図3】

【図4】

【図 5】

【図 6】

【図 7】

【図8】

【図9】

【図 10】

【図 11】

【図 12】

【図13】

---

フロントページの続き

F ターム(参考) 2H092 GA17 HA04 HA05 JA21 JB07 JB13 KB14 MA13 MA17 NA25

NA27

4K029 AA06 AA24 BA45 BB03 BD02 CA01 CA05 HA07

|                |                                                                                                                                                                                                                  |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 制造反射型液晶显示板的方法                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2008064856A</a>                                                                                                                                                                                    | 公开(公告)日 | 2008-03-21 |

| 申请号            | JP2006240258                                                                                                                                                                                                     | 申请日     | 2006-09-05 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                             |         |            |

| [标]发明人         | 原田 武彦<br>橋本 栄                                                                                                                                                                                                    |         |            |

| 发明人            | 原田 武彦<br>橋本 栄                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1343 C23C14/04                                                                                                                                                                                             |         |            |

| F1分类号          | G02F1/1343 C23C14/04.B                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H092/GA17 2H092/HA04 2H092/HA05 2H092/JA21 2H092/JB07 2H092/JB13 2H092/KB14 2H092/MA13 2H092/MA17 2H092/NA25 2H092/NA27 4K029/AA06 4K029/AA24 4K029/BA45 4K029/BB03 4K029/BD02 4K029/CA01 4K029/CA05 4K029/HA07 |         |            |

| 代理人(译)         | 永井道雄                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                        |         |            |

### 摘要(译)

解决的问题：提供一种制造反射型液晶显示面板的方法，其中在电极上形成具有与对电极相同的功函数的ITO膜，而无需增加特别的步骤。液晶层116设置在具有反射像素电极113的像素电极基板与具有透明电极117的相对基板之间，并且相对于透明电极117的功函数差在像素电极113与透明电极之间不同。在制造反射型液晶显示面板的方法中，在像素电极的表面上形成功函数差小于117的导电薄膜。在该区域上形成抗蚀剂的步骤，在形成抗蚀剂之后形成导电薄膜的步骤以及通过抗蚀剂剥离方法去除形成在像素隔离区域上的导电薄膜的步骤。.. [选型图]图1