# (19)日本国特許庁(JP) (12) **公開特許公報**(A) (11)特許出願公開番号

特開2001 - 42842

(P2001 - 42842A)

(43)公開日 平成13年2月16日(2001.2.16)

| (51) Int | .CI | 7 |   |   |       | 識別記号 | 庁内整理番号 | F | I |   |   |       |     |   | 技術表示箇所 |

|----------|-----|---|---|---|-------|------|--------|---|---|---|---|-------|-----|---|--------|

|          | G   | 0 | 9 | G | 3/36  |      |        | G | 0 | 9 | G | 3/36  |     |   |        |

|          | G   | 0 | 2 | F | 1/133 | 550  |        | G | 0 | 2 | F | 1/133 | 550 |   |        |

|          | G   | 0 | 9 | G | 3/20  | 623  |        | G | 0 | 9 | G | 3/20  | 623 | G |        |

|          |     |   |   |   |       |      |        |   |   |   |   |       | 623 | W |        |

審査請求 有 請求項の数 40 L (全 22数)

| (21)出願番号              | 特願2000 - 167947(P2000 - 167947) | (71)出願人 | 500261592                                         |  |  |

|-----------------------|---------------------------------|---------|---------------------------------------------------|--|--|

| (22)出願日               | 平成12年6月5日(2000.6.5)             |         | 權 五敬<br>大韓民国ソウル市松波區新川洞(番地なし)<br>ジャンミアパート14 - 1102 |  |  |

| (31)優先権主張番号           |                                 | (72)発明者 | 權 五敬                                              |  |  |

| (32)優先日<br>(33)優先権主張国 | 平成11年6月4日(1999.6.4)<br>韓国(KR)   |         | 大韓民国ソウル市松波區新川洞(番地なし)<br>ジャンミアパート14 - 1102         |  |  |

|                       |                                 | (74)代理人 | 100095957                                         |  |  |

|                       |                                 |         | 弁理士 亀谷 美明 (外3名)                                   |  |  |

|                       |                                 |         |                                                   |  |  |

# (54)【発明の名称】 液晶表示装置のソースドライバ

## (57)【要約】

【課題】 データラインの数を従来の半分の水準に減少 させながら同一な画像表現が可能になるようにしてコス トの低減を可能にする液晶表示装置及びその駆動回路を 提供すること。

【解決手段】 液晶表示装置のデータラインの左右の画 素領域に画像信号を伝達できるようにしてデータライン 数を半分に減少し,対応するソースドライバの数も半分 にできる構成にする。水平同期信号の1周期を2区間に 分け,前半,後半それぞれ,奇数,偶数番目のカラムラ インに該当する画像信号をサンプリング及びラッチさせ る。

1

#### 【特許請求の範囲】

【請求項1】 第1基板と第2基板また,その間に封入 された液晶を含む液晶表示装置のデータラインに画像信 号を与えるソースドライバにおいて,水平同期信号のパ ルスをシフトさせてラッチクロックを出力するnクロッ クシフトージスタ部;前記シフトレジスタ部から出力さ れるラッチクロックによって2 n 個のカラムラインのう ち, 奇数番目のカラムラインに該当するデジタル画像信 号をサンプリングしてラッチさせる第1サンプリングラ ッチ部;前記シフトレジスタ部から出力されるラッチク 10 ロックによって2n個のカラムラインのうち,偶数番目 のカラムラインに該当するデジタル画像信号をサンプリ ングしてラッチさせる第2サンプリングラッチ部;第1 ロード信号によって前記第1サンプリングラッチ部に貯 蔵されたデータが伝えられてラッチされ,第2ロード信 号によって前記第2サンプリングラッチ部に貯蔵された データが伝えられてラッチされるホールディングラッチ 部:前記ホールディングラッチ部に貯蔵された奇数番目 のカラムラインに該当するディジタル画像信号または偶 数番目のカラムラインに該当するディジタル画像信号を 20 m transistor)と画素電極とが構成され アナログデータに切り換える D / A コンバータ部;前記 D / A コンバータ部から出力される奇数番目のカラムラ インに該当するアナログ画像信号または偶数番目のカラ ムラインに該当するアナログ画像信号を一定幅で増幅さ せる増幅部を含めて構成することを特徴とする液晶表示 装置のソースドライバ。

【請求項2】 前記第1サンプリングラッチ部及び第2 サンプリングラッチ部のセル数はデータラインの数によ って決められることを特徴とする請求項1記載の液晶表 示装置のソースドライバ。

【請求項3】 第1基板と第2基板また,その間に封入 された液晶を含める液晶表示装置のデータラインに画像 信号を与えるソースドライバにおいて, 水平同期信号の パルスをシフトさせてラッチクロックを出力するn出力 シフトレジスタ部;前記シフトレジスタ部から出力され るラッチクロックによって2n個のカラムラインを,偶 数番目のカラムラインと奇数番目のカラムラインとに各 々サンプリングしてラッチさせる第1,第2サンプリン グラッチ部:ロード信号によって前記第1,第2サンプ リングラッチ部に貯蔵されたデータが伝えられて各々ラ 40 その間に封入された液晶から成り画像をディスプレイす ッチされる第1,第2ホールディング部:前記第1,第 2 ホールディングラッチ部に貯蔵されたディジタル画像 信号を各々アナログ画像信号で切り換える第1,第2D / Aコンバータ部;前記第1,第2D/Aコンバータ部 から出力されるアナログ画像データを各々一定幅で増幅 される第1,第2増幅部;前記第1,第2増幅部の出力 を選択的に前記データラインと連結させるスイッチング 部を含めて構成されることを特徴とする液晶表示装置の ソースドライバ。

【請求項4】 前記スイッチング部は1水平周期の間, 50 ライン(G1,G2,・・・,Gn?1,Gn)などが

前記第1増幅部の出力と前記第2増幅部の出力を順次前 記データラインと連結させることを特徴とする請求項1 記載の液晶表示装置のソースドライバ。

#### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】本発明は、液晶表示装置のソ ースドライバに係り,特に高解像度を保持しながら生産 コストが低減できるようにした液晶表示装置のソースド ライバに関する。

#### [0002]

【従来の技術】一般的な液晶ディスプレイ素子(liq uid crystal display:LCD)は 大きく上板と下板,また上板と下板の間に封入された液 晶からなる。上板にはブラックマトリックス,共通電 極,色相を表現するためのR(赤),G(緑),B (青)のカラーフィルタ層が配設される。下板にはデー タラインとゲートラインとが交差しながら配設されてマ トリックス形態の画素領域を有する。また各画素領域に は一つの薄膜トランジスタ(TFT:thin fil る。

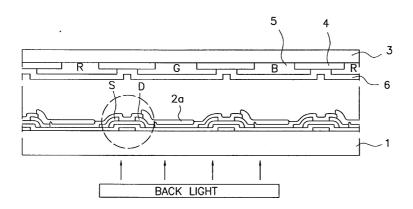

【0003】図24は一般的な液晶ディスプレイ素子の の断面構造図である。図24に示したように,下板1に は走査ライン (ゲートライン)から延伸されるゲート電 極(Gate)と、データラインから延伸されるソース 電極S及びドレーン電極Dから構成される薄膜トランジ スタが,一定な間隔を置きマトリックスの形態で形成さ れる。

【0004】各画素領域には各薄膜トランジスタ2のド 30 レーン電極 D に連結される画素電極 2 a が形成される。 【0005】上板3には下板1に形成された画素電極2 a を除外した部分で光の透過を遮断するためにブラック マトリックス層4がメッシュ形態で形成される。各ブラ ックマトリックス層4の間には色を表現するためのR, G , Bカラーフィルタ層 5 が形成される。また , カラー フィルタ層 5 とブラックマトリックス層 4 とに亘って共 通電極6が形成される。

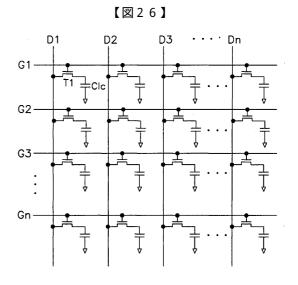

【0006】図25は一般的な液晶ディスプレイ素子の 構成図である。図25に示したように下板及び上板また るパネル部21と,前記パネル部21のロー方向へ駆動 信号を与えるゲートドライバGDから成るゲートドライ バ22と,前記パネル部21のカラム方向へ駆動信号を 与えるソースドライバS Dから成るソースドライバ23 とから構成される。

【0007】以下,添付の図面を参照して従来液晶表示 装置及びその駆動回路を説明する。図26は従来技術に よる液晶表示装置の構成図である。図26に示したよう に,ロー方向に沿って互いに一定間隔を置き複数の走査 3

形成され、各走査ラインなどを横ぎる方向へ複数のデー タライン(D1,D2,・・・,Dn?1,Dn)など が形成される。

【0008】また、走査ラインとデータラインが交差す る地点ごとに薄膜トランジスタT1などが構成され,各 薄膜トランジスタごとに画素電極てしが連結される。

【0009】従って,走査ラインに順次駆動電圧が供給 されて薄膜トランジスタがターンオンされ、ターンオン された薄膜トランジスタを介して該当データラインの信 号電圧が画素電極へ充電される。

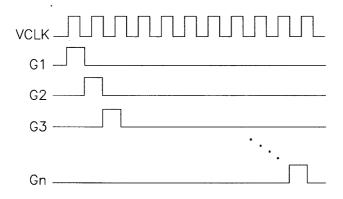

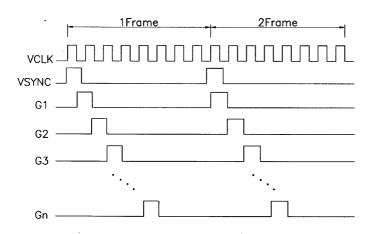

【0010】図27は従来液晶表示装置の走査ラインに 与える駆動信号波形図である。図27に示したように1 水平周期の間,1番目の走査ラインG1からn番目の走査 Gnまで順次駆動信号が与えられるので,該当走査ライ ンによってターンオンされた薄膜トランジスタを介して 該当データラインの信号電圧が画素電極へ伝えられて画 像を表示する。

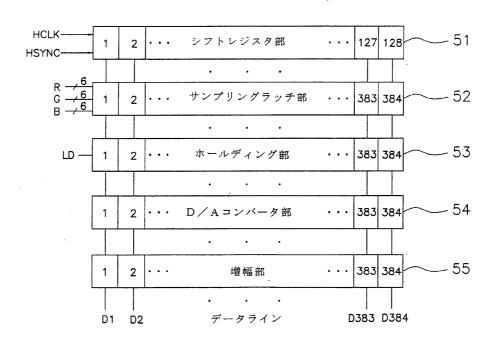

【0011】図28は従来液晶表示装置によるソースド ライバの構成図であり、図29はソースドライバの動作 波形図である。参考に図28に示したソースドライバは20 384チャンネル6ビットドライバを示した。即ち, R , G , B データが各々 6 ビットで成され , カラムライ ン(データライン)は384ラインから構成されたソー スドライバである。

【0012】図28に示したように、シフトレジスタ部 51と,サンプリングラッチ部52と,ホールディング ラッチ部3と,デジタル/アナログコンバータ部54, また増幅部から構成される。

【0013】シフトレジスタ部51は水平同期信号パル ス(HSYNC)をソースパルスクロックによってシフ 30 ケージングのみならず,ドライバとパネルとの間の接続 トさせてラッチクロックをサンプリングラッチ部52に 出力する。

【 0 0 1 4 】サンプリングラッチ部 5 2 はシフトレジス 夕部51から出力されるラッチクロックによってディジ タルR,G,Bデータをカラムライン別にサンプリング してラッチさせる。

【0015】ホールディングラッチ部53はサンプリン グラッチ部52にラッチされたR,G,Bデータをロー ド信号(LD:Load)によって同時に伝達されてラ ッチされる。

【0016】デジタル/アナログコンバータ部54はホ ールディングラッチ部53に貯蔵されたR,G,Bデー タをロード信号(LD:Load)によって同時に伝え られラッチさせる。デジタル/アナログコンバータ部5 4 はホールディングラッチ部53 に貯蔵されたデジタル R , G , B にデータをアナログ R G B データで変換す る。

【0017】増幅部55はアナログ信号で変換された R,G,Bデータを一定幅で増幅してパネルのデータラ

G , B データをサンプルアンドホールディングの後にア ナログRGBデータで変換し,これを電流増幅して出力 するが,前記ホールディングラッチ部53がn番目のカ ラムラインに該当するR,G,Bデータをホールデドし ていたらサンプリングラッチ部52はn+1番目のカラ ムラインに該当するR,G,Bデータをサンプリングす

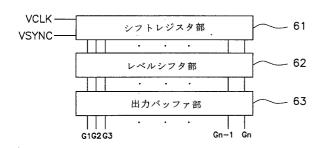

【0018】次に図30は従来液晶表示装置によるゲー トドライバの構成図であり、図31はそれによる入力波 10 形図である。図30に示したように,シフトレジスタ部 61,レベルシフト部62,また出力バッファ部63か ら構成される。

【0019】シフトレジスタ部61は垂直同期信号パル ス(VSYNC)をゲートパルスクロックによってシフ トさせて走査ラインを順次インエーブルさせる。

【0020】レベルシフタ部62は走査ラインに与えら れる信号を順次的にレベルシフトさせて出力バッファ部 63で出力する。従って、出力バッファ部63と連結さ れた複数の走査ラインは順次的にインエーブルされる。

【0021】以上のように、従来液晶表示装置は各々の データラインごとに薄膜トランジスタを備えて,走査ラ インに順次駆動電圧を供給して薄膜トランジスタをオン / オフさせ, そのうち, ターンオンされた薄膜トランジ スタを介して該当データラインの信号電圧を画素領域に 伝えて画像を表示する。

【0022】しかしながら、前記のような従来の液晶表 示装置は,高解像度及び大型化を満たすためにさらに多 い画素を構成しようとする場合、ドライバの数及びサイ ズが増加してコストが上昇することになり,これはパッ などの新しい問題を生じた。

## [0023]

【発明が解決しようとする課題】本発明は,このような 問題点に鑑みてなされたもので、その目的とするところ は、データラインの数を従来の半分の水準に減少させな がら同一な画像表現が可能になるようにしてコストの低 減を可能にする液晶表示装置及びその駆動回路を提供す ることである。

#### [0024]

【課題を解決するための手段】前述した課題をを達成す るために本発明は、第1基板と第2基板また、その間に 封入された液晶を含む液晶表示装置のデータラインに画 像信号を与えるソースドライバにおいて,水平同期信号 のパルスをシフトさせてラッチクロックを出力するnク ロックシフトレジスタ部、シフトレジスタ部から出力さ れるラッチクロックによって2 n 個のカラムラインのう ち、奇数番目のカラムラインに該当するデジタル画像信 号をサンプリングしてラッチさせる第1サンプリングラ ッチ部,シフトレジスタ部から出力されるラッチクロッ インで出力する。即ち,1水平周期の間,デジタルR, 50 クによって2n個のカラムラインのうち,偶数番目のカ

ラムラインに該当するデジタル画像信号をサンプリング してラッチさせる第2サンプリングラッチ部,第1ロー ド信号によって第1サンプリングラッチ部に貯蔵された データが伝えられてラッチされ,第2ロード信号によっ て第2サンプリングラッチ部に貯蔵されたデータが伝え られてラッチされるホールディングラッチ部,ホールデ ィングラッチ部に貯蔵された奇数番目のカラムラインに 該当するディジタル画像信号または偶数番目のカラムラ インに該当するディジタル画像信号をアナログデータに 切り換えるD/ Aコンバータ部, D/ Aコンバータ部か 10 ら出力される奇数番目のカラムラインに該当するアナロ グ画像信号または偶数番目のカラムラインに該当するア ナログ画像信号を一定幅で増幅させる増幅部を含めて構 成することを特徴とする液晶表示装置のソースドライバ である。

【0025】第1サンプリングラッチ部及び第2サンプ リングラッチ部のセル数はデータラインの数によって決 められる。

【0026】第1基板と第2基板また,その間に封入さ れた液晶を含める液晶表示装置のデータラインに画像信 20 号を与えるソースドライバにおいて、水平同期信号のパ ルスをシフトさせてラッチクロックを出力するn出力シ フトレジスタ部,シフトレジスタ部から出力されるラッ チクロックによって2n個のカラムラインを,偶数番目 のカラムラインと奇数番目のカラムラインとに各々サン プリングしてラッチさせる第1,第2サンプリングラッ チ部,ロード信号によって第1,第2サンプリングラッ チ部に貯蔵されたデータが伝えられて各々ラッチされる 第1,第2ホールディング部,第1,第2ホールディン グラッチ部に貯蔵されたディジタル画像信号を各々アナ 30 結された第1薄膜トランジスタ71aと,前記第1薄膜 ログ画像信号で切り換える第1,第2D/Aコンバータ 部,第1,第2D/Aコンバータ部から出力されるアナ 口グ画像データを各々一定幅で増幅される第1,第2増 幅部,第1,第2増幅部の出力を選択的にデータライン と連結させるスイッチング部を含めて構成されることを 特徴とする液晶表示装置のソースドライバである。

【0027】また,スイッチング部は1水平周期の間, 第1増幅部の出力と第2増幅部の出力を順次データライ ンと連結させることを特徴とする液晶表示装置のソース ドライバである。

【0028】また,ゲートドライバは第1基板と第2基 板、またその間に封入された液晶を含む液晶表示装置の 走査ラインに駆動信号を与えるゲートドライバにおい て,スタートパルスをゲートパルスクロックによってシ フトさせるシフトレジスタ部,前記シフトレジスタ部の 出力信号のうち選択的に複数個入力して論理演算の後出 力するロジック回路部,前記ロジック回路部の出力を一 定レベルでシフトさせて順次的に出力するレベルシフタ 部、レベルシフトされた信号を順次走査ラインに与える [0029]

【発明の実施の形態】以下,図面に基づいて,本発明の 実施の形態を詳細に説明する。まず,本発明の一実施の 形態による液晶表示装置は隣接した二つの走査ラインに 与える駆動信号を制御して一つのデータラインへその両 側の画素領域に画像信号を伝えられるようにしてデータ ラインの数を半分で減少させるのにその特徴がある。

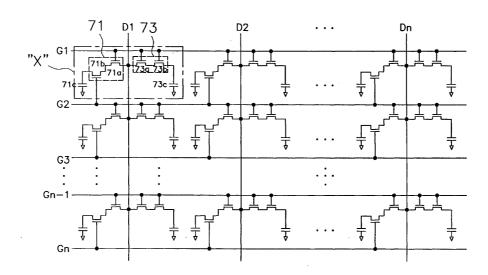

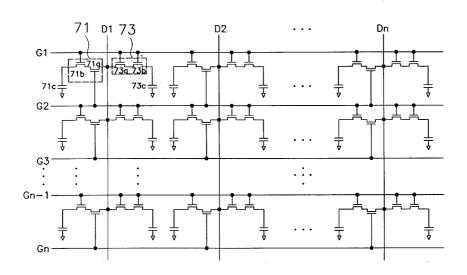

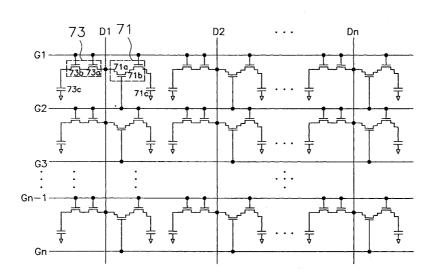

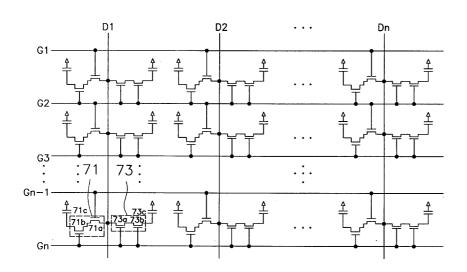

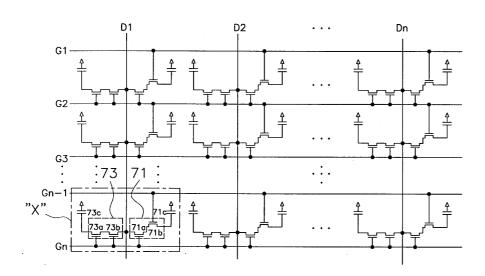

【0030】図1は本発明の第1実施例による液晶表示 装置の構成図である。図1に示したようにロー方向へ走 查ライン(G1,G2,···,Gn?1,Gn)など が形成され, 走査ライン(G1, G2, ・・・, Gn? 1,Gn)などを横きるカラム方向へデータライン(D 1,D2,・・・,Dn?1,Dn)が交差する地点で データライン(D1,D2,・・・,Dn?1,Dn) を中心に左側の画素領域に画像信号を伝える第1スイッ チング部71が形成され、データラインを中心に右側の 画素領域に画像信号を伝える第2スイッチング部73が 形成される。

【0031】また, 第1スイッチング部71には第1画 素電極71cが連結され,第2スイッチング73には第 2 画素電極 7 3 c が連結される。ここで,前記第 1 スイ ッチング部71と,第2スッイチング部73は薄膜トラ ンジスタから構成し、前記薄膜トランジスタはNタイプ の薄膜トランジスタまたはPタイプの薄膜トランジスタ から構成する。

【 0 0 3 2 】また,図1の"X"部分を中心により詳細 に説明する。データラインD1の左側に構成される第1 スイッチング部71は,ソースまたはドレーンがデータ ラインD1に連結されゲートが該当走査ラインG1に連 トランジスタ71aと直列で連結され,ゲートが次の走 査ラインG2に連結される第2薄膜トランジスタ71b から構成される。

【0033】前記第2薄膜トランジスタ71bには第1 画素電極71cが連結されて前記第1,第2薄膜トラン ジスタ 7 1 a , 7 1 b などのオン / オフ動作によって選 択的に画像信号が伝えられる。

【0034】前記データラインD1の右側に構成される 第2スイッチング部73はゲートが該当走査ラインG1 40 に連結され,ソースまたはドレーンがデータラインD1 に連結される第3薄膜トランジスタ73aと,前記第3 薄膜トランジスタ73aと直列で連結され,ゲートが該 当走査ラインG1に連結される第4薄膜トランジスター から構成される。ここで,前記第2スイッチング部73 は第3薄膜トランジスタ73aのみを構成することもで

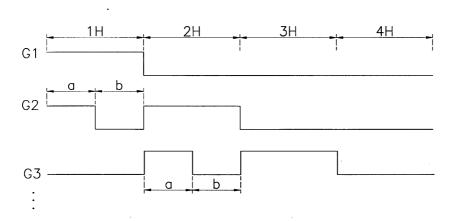

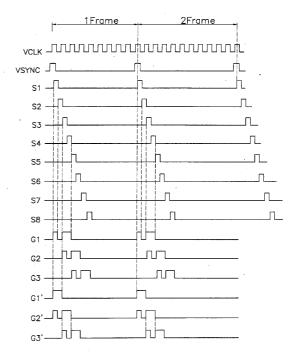

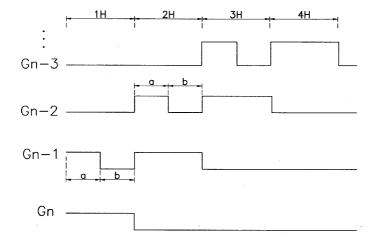

【0035】このように構成された本発明の第1実施例 による液晶表示装置において,第1画素電極と第2画素 電極に画像信号を伝える過程を図2に示した波形図を参 出力バッファ部を含めて構成されることを特徴とする。 50 照して説明する。図2は本発明の第1実施例による液晶

表示装置の走査ラインに与える駆動信号の波形を示すも のである。

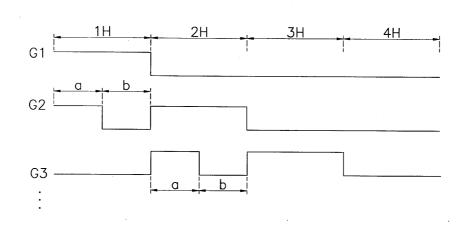

【0036】図2に示したように1水平周期を2区間に 分けて第1区間aではデータライン(D1,D2,・・ ・, Dn?1, Dn)を中心に左側と右側の画素領域に 画像信号を与え,第2区間bでは右側の画素領域だけに 画像信号を与える。即ち,1番目の走査ラインG1では 1水平周期の間にハイ信号を与え,2番目の走査ライン G 2 に 1 / 2 水平周期の間 (正確に 1 / 2 ではなくても 構わない),即ち,a区間の間だけハイ信号を与え,余10 第1スイチング部71をデータライン(D1,D2,・ 分の1/2水平周期の間にはロー信号を与える。

【0037】従って,1番目の走査ラインG!と,2番 目の走査ラインG2が全てのハイの間には第1スイッチ ング部71を構成している第1,第2薄膜トランジスタ 7 1 a , 7 1bと第 2 スイチング部 7 3 を構成している 第3,第4薄膜トランジスタ73a,73bが全てター ンオンの状態となって第1画素電極71cと第2画素電 極73 c に画像信号が伝えられる。

【0038】その後,2番目の走査ラインG2にロー信 号を与えると,第2薄膜とトランジスター71bがター20 ンオフ状態となって第1画素電極71cには画像信号が 伝えられず第2画素電極73cだけに画像信号が伝えら れる。

【0039】このように1水平周期を2区間a,bに分 けて一つのデータラインに格納された画像信号を左側及 び右側の画素電極に選択的に伝えられる。結果的に走査 ラインに与えられる駆動信号を制御して一つのデータラ インが左側と右側の画素領域に画像信号を伝えるのでデ ータラインの数を従来に比べて半分に減少させることが でき,これによってソースドライバの数も半分に減少さ30 せることができる。

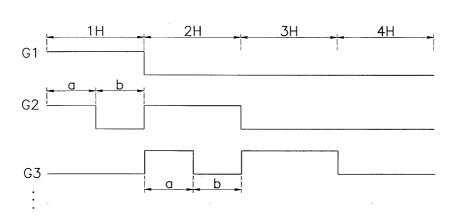

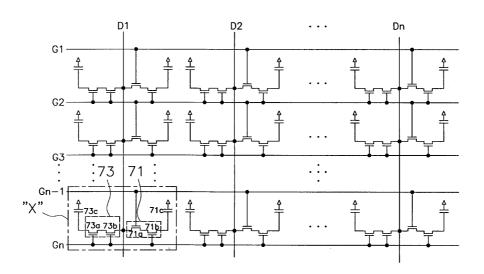

【0040】続いて,図3は本発明第2実施例による液 晶表示装置の構成図である。図3に示したように,前記 の第1実施例と比較して第1スイッチング部71を構成 している第1薄膜トランジスタ71aと第2薄膜トラン ジスタ71bのゲート接続部位が相異することがわか る。

【0041】即ち,本発明の第2実施例による第1スイ チング部71はソースまたはドレーンがデータラインD 1に連結され、ゲートが次回の走査ラインG2に連結さ 40 ンD1に連結され、ゲートが該当走査ラインG1に連結 れる第1薄膜トランジスター71aと前記第1薄膜トラ ンジスタ71aと直列で連結され,ゲートは該当走査ラ インG1に連結される第1薄膜トランジスタ71bから 構成される。このとき,第2スイチング部73は第1実 施例による構成と同一である。

【0042】このような本発明の第2実施例による液晶 表示装置において走査ライン図4のような波形を与える と,液晶パネルの上端から下端へ移動しながら画像が表 示され,一つのデータラインが左側と右側の画素領域に 画像信号を伝えてデータラインの数を減少することがで 50 インG2にa区間の間だけハイ信号を与え, b区間の間

きる。

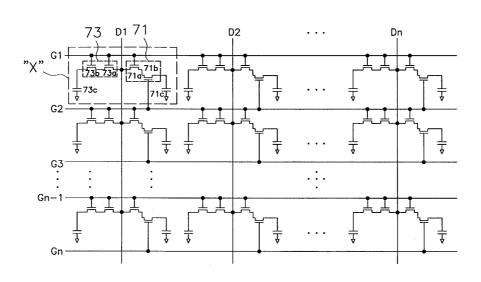

【0043】なお、図5は本発明の第3実施例による液 晶表示装置の構成図であり、図6は走査ラインに与えら れる駆動信号の波形図である。図5に示したように,本 発明の第3実施例は第1スイッチング部71を前記デー タライン(D1,D2,・・・,Dn?1,Dn)の右 側に構成し,第2スイッチング部73を右側に構成し

【0044】即ち,本発明の第1,第2実施例では前記 ・・, Dn?1, Dn)の左側に構成したが, 本発明の 第3実施例では右側に構成した。このような本発明の第 3 実施例による液晶表示装置はロー方向へ形成された複 数の走査ライン(G1,G2,・・・,Gn?1,G n) などと, 前記走査ラインと交差する方向へ形成され たデータライン(D1,D2,・・・,Dn?1,D n)と,各走査ラインと交差するデータライン(D1, D2, · · · , Dn? 1, Dn) の左側に形成される第 1スイチング部71と,前記データライン(D1,D 2, · · · , D n ? 1, D n ) の左側に形成される第2 スイチング部73と,前記第1スイチング部73に連結 された第2画素電極73cから構成される。

【 0 0 4 5 】これを図 5 の " X " 部分を中心に,より詳 細に説明する。第1スイッチング部71は走査ラインG 1とデータライン D 1 が交差する地点でデータラインの 右側に形成され、第1スイッチング部71を構成する第 1薄膜トランジスタ71aと第2薄膜トランジスタ71 bのうち,第2薄膜トランジスタ71bのゲートが次回 の走査ラインG2に連結される。

【0046】即ち,ソースまたはドレーンがデータライ ンD1に連結され,ゲートが該当走査ラインG1に連結 される第1薄膜トランジスタ71aと,第1薄膜トラン ジスタ 7 1 a と直列で連結され,ゲートが次回の走査ラ インG2に連結される第2薄膜トランジスタ71bから

【0047】また、第2スイッチング部73はデータラ イン D 1 を中心に左側に形成され,二つの薄膜トランジ スタから構成される。

【0048】即ち、ソースまたはドレーンがデータライ される第3薄膜トランジスタ73aと,第3薄膜トラン ジスター73aと直列で連結されゲートが該当走査ライ ンG1に連結される第4薄膜トランジスタ73bから構 成される。ここで、第2スイッチング部73は一つの薄 膜トランジスタから構成することができる。

【0049】このように構成された本発明の第3実施例 に液晶表示装置は走査ラインに図6のような駆動信号を 与える。図6に示したように,1水平周期の間に1番目 の走査ラインG1にはハイ信号を与え,2番目の走査ラ にはロー信号を与える。

【 0 0 5 0 】従って, 1番目の走査ラインG1と2番目 の走査ライン G 2 に全てハイ信号が与える場合には第1 スイッチング部71及び第2スイッチング部73を構成 している薄膜トランジスタが全てターンオンされて第1 画素電極71cと第2画素電極73cに画像信号が伝え られる。

9

【0051】この後,1番目の走査ラインG1にはハイ 信号が与えられ,2番目の走査ラインG2にロー信号が 与えられる場合には第1スイチング部71を構成してい10極が形成される。 る第2薄膜トランジスター71bがターンオフ状態とな るので第1画素電極71cには画像信号が伝えられず第 2 画素電極 7 3 c だけに画像信号が伝えられる。このよ うな過程を介して液晶パネルの上端から下端へ移動しな がら画像が表示される。

【0052】なお,図7は本発明の第4実施例による液 晶表示装置の構成図であり、図8は図7による波形図で ある。図7に示したように,本発明のの第4実施例には 第3実施例と比較して第1スイッチング部71を構成し ている第1,第2薄膜トランジスタ71a,71bのゲ20 ート接続部位を異にして構成したものである。

【0053】即ち,第3実施例には第1スイッチング部 71を構成している第1薄膜トランジスタ71aと第2 薄膜トランジスタ71bのうち,第2薄膜トランジスタ 7 1 b のゲートが次回の走査ライン G 2 に連結されてい るが,本発明の第4実施例では第1薄膜トランジスタ7 1 aのゲートが次回の走査ラインG2に連結されるよう に構成した。

【0054】即ち,本発明第4実施例による第1スイッ チング部71はソースまたはドレーンがデータラインD30側には第1スイッチング部71が構成され,右側には第 1に連結され、ゲートが次回走査ラインG2に連結され る第1薄膜トランジスタ71aと直列で連結され,ゲー トが該当走査ラインG2に連結される第2薄膜トランジ スタ71bで構成される。

【0055】従って、図8のように走査ラインに駆動信 号を与えるとデータライン D 1 を中心に左側と右側に選 択的に画像信号を与えることができる。また,画像は液 晶パネルの上端から下端へ移動しながらディスプレイさ れる。

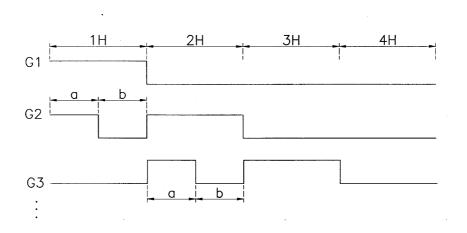

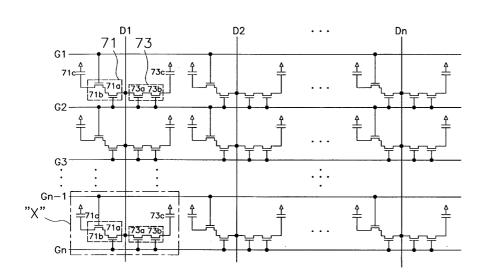

【0056】続いて,図9は本発明の第5実施例による40 インGnに連結される。 液晶表示装置の構成図であり、図10は走査ラインに与 える駆動信号の波形を示した。第5実施例には第1,第 2 スイッチング部を構成している薄膜トランジスタが形 成される位置において,第1実施例ないし第4実施例の 構成と差がある。

【0057】即ち,本発明の第1実施例ないし第4実施 例にはデータライン(D1,D2,···,Dn?1, Dn)と走査ライン(G1,G2,・・・,Gn?1, Gn)とが交差する地点に薄膜トランジスタ及び画素電 極が形成されるが,前記データラインに対して1番目の50当走査ラインにはハイ信号を与え,以前走査ラインGn

走査ラインとの交差点から順次2番目,3番目,,,n ? 1番目の走査ラインと交差点に形成される。また,デ ータラインと n 番目の走査ラインが交差する地点では薄 膜トランジスター及び画素電極が形成されない。

【0058】しかしながら、本発明の第5実施例ではデ ータラインに対して1番目の走査ラインが交差する地点 には薄膜トランジスタ及び画素電極が形成されず,2番 目の走査ラインから3番目,4番目,・・・,n番目走 査ラインが交差する地点に薄膜トランジスタ及び画素電

【0059】本発明の第1実施例ないし第4実施例では 走査ラインとデータラインが交差する地点に形成される 4個の薄膜トランジスタなどのうち,いずれかの一つが 次回の走査ラインに連結されたが,第5実施例では4個 の薄膜トランジスタのうち,いずれかの一つが以前走査 ラインに連結される構造を有する。

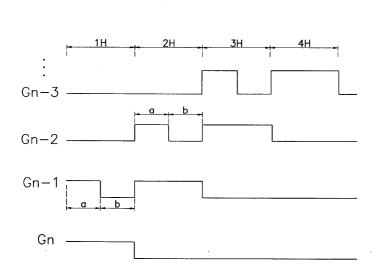

【0060】このような本発明の第5実施例の場合,図 10のように走査ラインに駆動信号を与えると液晶パネ ルの下端から上端へ移動しながら画像が表示される。図 10に示したように,1水平周期を2区間a,bに分け て走査ラインに駆動信号を与えることによってデータラ インを中心に左側と右側の画素領域に選択的に画像信号 を与えることができる。

【0061】これをより詳細に説明すると次のようであ る。図9に示したように一方向へ複数の走査ライン(G 1,G2,···,Gn?1,Gn)が形成され,各々 走査ラインなどと交差する方向へデータライン(D1, D2, ···, Dn?1, Dn) が形成される。各デー タライン(D1,D2,・・・,Dn?1,Dn)の左 2スイッチング部73が構成される。

【0062】第1スイッチング部71及び第2スイッチ ング部73は薄膜トランジスタから構成され前記薄膜ト ランジスタはNタイプの薄膜トランジスタまたはPタイ プの薄膜トランジスタから構成される。

【0063】前記データラインD1の左側には構成され る第1スイッチング部71のうち,第2薄膜トランジス タ71bのゲートは以前走査ライン(Gn?1)に連結 され第1薄膜トランジスタ71aのゲートは該当走査ラ

【0064】各々データライン(D1,D2,··· Dn?1,Dn)の右側に形成される第2スイッチング 部73は二つの薄膜トランジスタから構成され,前記二 つの薄膜トランジスタ (第3,第4薄膜トランジス タ)のゲートは全て該当走査ラインGnに連結される。 ここで,前記第2スイッチング部73を一つの薄膜トラ ンジスタから構成することもできる。

【0065】これを図9の"X"部分を中心により詳細 に説明する。図10に示したように1水平周期の間に該 (7)

? 1は第1区間aの時だけハイ信号を与える。従って, 該当走査ラインGnと以前走査ラインGn?1が全てハ イである区間では第1,第2スイッチング部70,73 を構成している薄膜トランジスタなどが全てターンオン 状態となって第1,第2画素電極71c,73cに画像 信号が伝えられる。

11

【0066】次に第2区間bの時には以前走査ライン (Gn?1)にロー信号を与えると前記第1スイッチン グ部71を構成している第2薄膜トランジスタ71bが ターンオフ状態となって第1画素電極71cには画像信 10 ートが該当走査ラインGnに連結される第1薄膜トラン 号が伝えられない。代わりに,データラインの右側の第 2スイチング部73は相変わらずターンオン状態を保持 することになって前記第2画素電極73cだけに画像信 号が伝えられる。

【0067】このようにデータラインを中心に左側と右 側に選択的に画像信号を伝えることができ、データライ ンの数を半分に減少することができる。

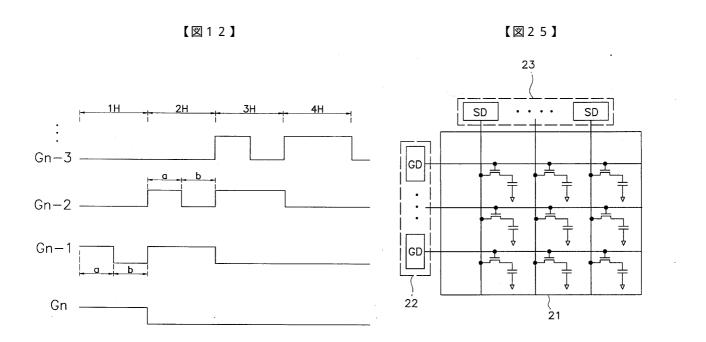

【0068】図11は本発明の第6実施例による液晶表 示装置の構成図であり、図12は本発明の第6実施例に よる液晶表示装置の走査ラインに与えられる駆動信号を 20 波形図を示したものである。本発明の第6実施例による 液晶表示装置は本発明の第5実施例と比較して第1スイ ッチング部71を構成している第1薄膜トランジスタ7 1 a と第 2 薄膜トランジスタ 7 1 b のゲート接続部位が 相異することがわかる。

【0069】即ち,本発明の第5実施例では第1薄膜ト ランジスタ71aのゲートが該当走査ラインGnに連結 され,第2薄膜トランジスタ71bのゲートは以前走査 ラインGn?1に連結されたが,本発明の第6実施例で は第1薄膜トランジスタ71aのゲートが以前走査ライ 30 ンGn?1に連結され,第2薄膜トランジスタ71bの ゲートが該当走査ライン Gnに連結される。このとき, 第2スイッチング部73は第5実施例の構成と同一であ る。

【0070】このように走査ラインに図12のように駆 動信号を与えると一つのデータラインを中心に左側と右 側に選択的に画像信号を伝えられる。また,第5実施例 と同じく液晶パネルの下端から上端へ移動しながら画像 が表示される。

【0071】次に,図13は本発明の第7実施例による40 液晶表示装置の構成図であり、図14は走査ラインに与 える駆動信号の波形図である。図13に示したように, 本発明の第7実施例による液晶表示装置はデータライン を中心に右側に第1スイチング部を構成し左側に第2ス イチング部を構成した。

【0072】図13のように一方向へ形成された走査ラ インなど(G1,G2,・・・,Gn?1,Gn),前 記走査ラインと交差する方向へ形成されたデータライン (D1,D2,···,Dn?1,Dn)と,前記走査 ラインとデータラインが交差する地点でデータラインの 50 タラインの数を半分に減らすことができる。

両側に形成され,前記該当走査ラインと以前走査ライン によって制御される第1スイッチング71及び第2スイ ッチング部73と,前記第1スイッチング部71と連結 される第1画素電極71cと,前記第2スイッチング部 73と連結される第2画素電極73cを含めて構成され る。

【0073】これを図13の"X"部分をより詳細に説 明すると次のようである。第1スイッチング部71はソ ースまたはドレーンがデータラインD1に連結され,ゲ ジスタ71aと前記第1薄膜トランジスタ71aと直列 で連結され,ゲートが以前走査ラインGn?1に連結さ れる第2薄膜トランジスタ71bから構成される。

【0074】また、第2スイッチング部73はソースま たはドレーンがデータラインD1に連結されゲートが該 当走査ラインGnに連結される第3薄膜トランジスタ7 3 a と , 前記第3薄膜トランジスタ73 a と直列で連結 されゲートが該当走査ラインGnに連結される第4薄膜 トランジスタ73bから構成される。

【0075】前記第2スイッチング部73は第3薄膜ト ランジスタ73aだけを構成することができる。

【0076】このように構成された液晶表示装置の走査 ラインに図14のように駆動信号を与えると,液晶パネ ルの下端から上端の方へ移動しながら画像が表示され る。これは前記で説明した第5,第6の実施例と同じで ある。

【0077】なお,図15は本発明の第8実施例による 液晶表示装置の構成図であり、図16は走査ラインに与 えられる駆動信号の波形図である。本発明の第8実施例 では第7実施例と比較して第1スイッチング部を構成し ている第1薄膜トランジスタ71aのゲートと第2薄膜 トランジスタ71bのゲートの接続部位が相異する。

【0078】即ち,本発明の第8実施例による第1スイ ッチング部71はソースまたはドレーンがデータライン D1に連結され,ゲートが以前走査ライン(Gn?1) に連結される第1薄膜トランジスタ71aと,前記第1 薄膜トランジスタ71aと直列で連結されゲートが該当 走査ライン(Gn)だけに連結される第2薄膜トランジ スタ71bから構成される。

【 0 0 7 9 】ここで前記第 2 スイッチング部 7 3 は第 7 実施例による第2スイッチング部73と同一な構成を有 する。

【0080】このような本発明の第8実施例による液晶 表示装置の走査ラインに図16のように駆動信号を与え ると液晶パネルの下端から上端の方へ移動しながら画像 が表示される。

【0081】以上のように,本発明の一実施の形態によ る液晶表示装置は,一つのデータラインがその左側と右 側の画素領域に画像信号を伝えられるようにして、デー

【0082】このようにデータラインの数を半分で減ら すことができるのでデータラインに駆動信号を与えるソ ースドライバの数も半分に減らすことができる。

【0083】以下,本発明の一実施の形態による液晶表 示装置を駆動するための駆動回路について説明する。前 記の本発明の一実施の形態による液晶表示装置はデータ ラインの数を半分に減少することができるが,これを満 足させるためにはソースドライバの構成が変わらなけれ ばならない。

【0084】即ち,本発明の一実施の形態による液晶表 10 る。 示装置を駆動するためのソースドライバはデータライン が384ラインであれば総768ラインに相応する画像 信号をハンドリングしなければならない。

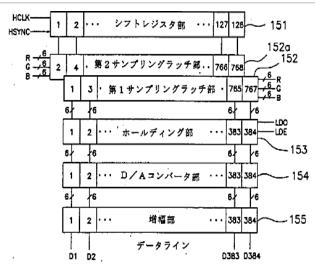

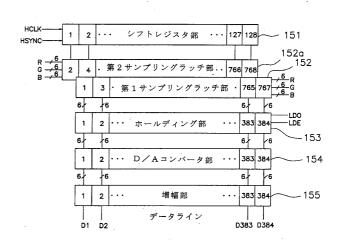

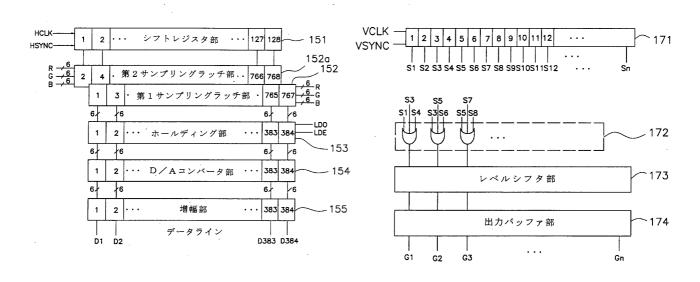

【0085】このためにソースドライバを図17のよう に構成することができる。図17は本発明の一実施の形 態によるソースドライバの第1実施例を示している。図 17に示したソースドライバは従来のソースドライバと 比較してサンプリングラッチ部のセル数を 2 倍に増加さ せた。これは本発明の一実施の形態によるソースドライ バは384個のデータラインを駆動するが,実質的に720 8 4 ラインの画像データをハンドリングをしなければな らないからである。

【0086】図17に示したように,水平同期信号のパ ルスをソースパルスクロックによってシフトさせてラッ チクロックを出力する384クロックシフトレジスタ部 100と,シフトレジスタ部151から出力されるラッ チクロックによって768個のカラムラインのうち,奇 数番目のカラムラインに該当するデジタルR,G,Bデ ータをサンプリングしてラッチさせる第1サンプリング ラッチ152と,偶数番目のカラムラインに該当するデ30ラムラインに該当するR,G,Bデータがパネルに与え ジタルR,G,Bデータをサンプリングしてラッチさせ る第2サンプリングラッチ部152aと,第1ロード信 号によって第1サンプリングラッチ部152に貯蔵され たデータが伝えられてラッチされ,第2ロード信号によ って第2サンプリングラッチ部152aに貯蔵されたデ ータが伝えられてラッチされるホールディングラッチ 1 53と,ホールディングラッチ部153に貯蔵された奇 数番目のカラムに該当するディジタルR, G, Bデータ または偶数番目のカラムに該当するディジタル R , G , Bデータをアナログデータで変換するD/Aコンバータ 40 の実施例を示した。図19に示したソースドライバは1 部154と,D/Aコンバータ154から出力される奇 数番目のカラムに該当するアナログR,G,Bデータま たは偶数番目のカラムに該当するアナログR,G,Bデ ータの電流を一定幅で増幅させる増幅部155から構成 される。

【0087】このように本発明の第1実施例によるソー スドライバは総768個のカラムラインのうち,奇数番 目のカラムラインに該当する画像データをサンプリング してラッチさせる第1サンプリングラッチ部152と,

リングしてラッチさせる第2サンプリングラッチ部15 2 a とから構成される。

14

【0088】即ち,1水平周期を2区間に分けて1/2 水平周期の間(正確に1/2ではなくても構わない)に は奇数番目のカラムラインに該当するR,G,Bデータ を第1サンプリングラッチ部152でサンプリング及び ラッチさせ,余分の1/2水平周期の間には偶数番目の カラムラインに該当するR,G,Bデータを第2サンプ リングラッチ部 1 5 2 a でサンプリング及びラッチさせ

【0089】従って、総768個のカラムラインに該当 するR,G,Bデータをサンプリングすることができ

【0090】このように第1サンプリングラッチ部15 2と,第2サンプリングラッチ部152aに分けてラッ チされたデジタル画像信号は順次ホールディングラッチ 153へ伝えられる。

【0091】即ち、第1ロード信号によって第1サンプ リングラッチ部152に貯蔵された画像データがホール ディングラッチ部153にロードされ,第2ロード信号 によって第2サンプリングラッチ部152aに貯蔵され た画像データがホールディングラッチ部153にロード される。

【0092】ホールディングラッチ部153にロードさ れたR,G,BディジタルデータはD/Aコンバータ部 154でアナログ信号に変換され,アナログ信号に変換 されたR,G,Bデータは増幅部155で電流が増幅さ れる。

【0093】また,1/2水平周期の間に奇数番目のカ られて表示され,余分の1/2水平周期の間には偶数番 目のカラムラインに該当するR,G,Bデータがパネル に与えられて表示される。

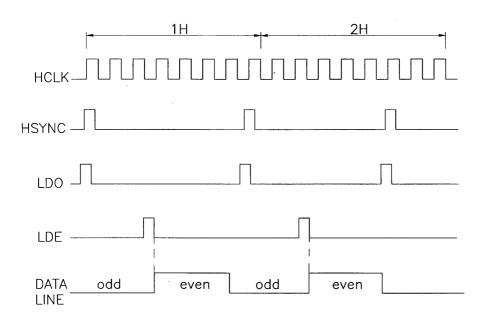

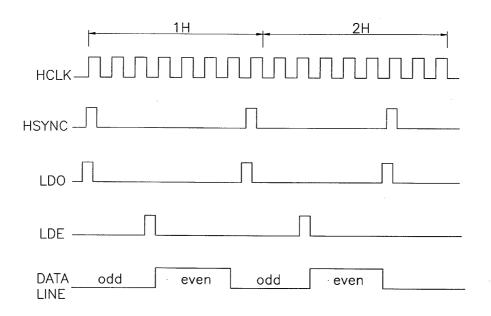

【0094】図18は図17によるソースドライバの動 作波形図を示したもので1水平周期の間に奇数番目のカ ラムラインをサンプリングしたデジタルデータと偶数番 目のカラムラインをサンプリングしたデジタルデータが ホールディング部153でロードされることがわかる。

【0095】図19は本発明によるソースドライバの他 水平周期の間に奇数番目のカラムラインと偶数番目まカ ラムラインに分けて液晶パネルに与えるために,サンプ リングラッチ部162,162a,ホールディングラッ チ部163,162a,DAC部164,164a,増 幅部165,165aを各々二つずつ構成したものであ

【0096】また,二つの増幅部165,165aの出 力を選択的ににデータラインに伝達するためにはスイッ チング部166がさらに構成される。

偶数番目のカラムラインに該当する画像データをサンプ 50 【 0 0 9 7 】従って,第1サンプリングラッチ部162

(9)

16

は奇数番目のカラムラインに該当する画像信号をサンプ リングし,第2サンプリングラッチ部162aは偶数番 目のカラムラインに該当する画像信号をサンプリングす る。

15

【0098】また,第1サンプリングラッチ部162に ラッチされた奇数番目のカラムラインに該当する画像信 号は,ロード信号LDによって奇数番目のカラムライン に該当する画像信号を貯蔵する第1ホールディングラッ チ部163にロードされる。

【0099】第2サンプリングラッチ部162aにラッ 10 チされた偶数番目のカラムラインに該当する画像信号 は,ロード信号 L D によって偶数番目のカラムラインに 該当する画像信号を貯蔵する第2ホールディングラッチ 部163aにロードされる。

【0100】その後,第1ホールディングラッチ部16 3に貯蔵されたデジタル画像信号は第1DAC部164 でアナログ信号に変換され,第2ホールディングラッチ 部163aに貯蔵された画像信号を第2DAC部164 a でアナログ信号に変換される。

【0101】ここで,第1DAC部164は奇数番目の20 れた複数の走査ラインなどは順次インエーブルされる。 カラムに該当するデジタル画像信号をアナログ信号に変 換し,第2DAC部164aは偶数番目のカラムに該当 するデジタル画像信号をアナログ信号に変換する。

【0102】アナログ信号に変換された奇数番目及び偶 数番めのカラムに該当する画像信号をさらに一定幅で増 幅させるが、前記増幅部また奇遇番目のカラムに該当す るアナログ信号を増幅する第1増幅部165と偶数番目 のカラムに該当するアナログ信号を増幅する第2増幅部 165aで構成される。

【0103】従って,1/2水平周期の間には前記スイ30 ッチング166の動作によって奇数番目のカラムライン に該当するアナログ画像信号がデータラインに与えら れ,余分の1/2水平周期の間には偶数番目のカラムラ インに該当するアナログ画像信号がデータラインに与え

【 0 1 0 4 】ここで,前記スイッチング部166は1/ 2水平周期の間には第1増幅部165の出力とデータラ イン(D1,D2,・・・,Dn?1,Dn)を電気的 に連結し,余分の1/2水平周期の間には第2増幅部1 65aの出力とデータライン(D1,D2,・・・,D40 る。 n?1,Dn)を電気的に連結する。

【0105】このように本発明の他の実施例によるソー スドライバはサンプリングラッチ部,ホールディング, D / A コンバータ部, また増幅部を各々2個ずつ構成す るので, n 個のカラムラインで2 n 個のカラムラインに 当たる画像信号を液晶パネルに与えることができる。

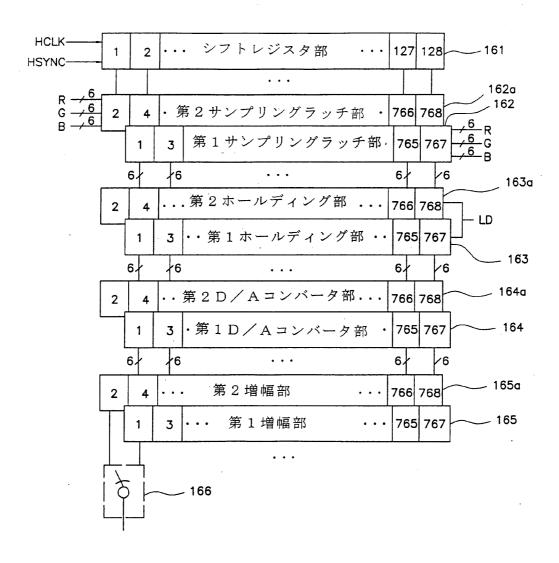

【0106】以下,本発明の一実施の形態による液晶表 示装置によるゲートドライバを説明する。図21は本発 明の一実施の形態によるゲートドライバの第1実施例を 示した。図21に示したように,大きくシフトレジスタ50【0116】 ここで,1水平周期の間に2個の画素領

部171,ロジック回路部172,レベルシフタ部17 3,また出力バッファ部174から構成される。

【 0 1 0 7 】シフトレジスタ部 1 7 1 は垂直同期信号パ ルスVSYNCをゲートパルスクロックによってシフト

【0108】ロジック回路部172は3入力オアゲート (OR1,OR2,・・・,ORn)などで構成され, 各々のオアゲートはシフトレジスタ部171の出力を選 択的に3個ずつ入力して論理演算する。

【0109】本発明の実施例によると,3入力オアゲー トのうち、1番目のオアゲートOR1が前記シフトレジ スタ部171の出力S1?Snのうち,S1,S3,S 4を入力する。また、2番目のオアゲートOR2はS 3, S5, S6を入力し, 3番目のオアゲートOR3は S5,S7,S8を入力する。続いて,4番目,5番 目,,,終わり番目まで続ける。

【0110】レベルシフタ部173は走査ラインに与え られる信号を順次レベルシフトさせて出力バッファ 1 7 4へ出力する。従って、出力バッファ部174と連結さ 【0111】このような本発明の第1実施例によるゲー トドライバの動作を図22に示した波形図を参照して説 明する。図22に示したように,前記1番目の走査ライ ンG1には前記1番目のオアゲートOR1の出力波形が 与えられ,2番目の走査ラインG2には2番目のオアゲ ートOR2の出力波形が与えられる。このように,1番 目の走査ラインから終わり番目の走査ラインまで順次イ ンエーブルされる。

【0112】ここで,前記走査ライン(G1,G2,・ ・・, Gn?1, Gn)などに与えられる信号は1水平 周期の間にハイ状態とロー状態を繰り返し,これは図2 - 8 に示したいずれかの一つの走査ラインに与えられる 駆動信号の波形と同じであることがわかる。

【0113】なお、図21に示した前記オアゲートの入 力を異にすることもできるが、その例として1番目のオ アゲート〇R1にS1,S2を入力し,2番目のオアゲ ートOR2にはS1,S2,S4を入力し,3番目のオ アゲートOR3にはS3、S5、S6を入力するなど終 わり番目のオアゲートまで規則的に入力することもでき

【0114】 前記のようにオアゲートの入力を異にす る場合には走査ラインに与えられる駆動信号は図22の 下端部に示したG1′,G2′,G3′のような波形を 有する。

【0115】 以上説明のように,ゲートドライバ及び ソースドライバを構成して1水平周期の間に2個の画素 領域に画像信号を伝える本発明の液晶表示装置によると データラインの数を減少することができ,これによって ソースドライバの数も減少することができる。

域に画像信号を伝えなければならないので各々画素領域 に伝えるラインタイムが減少し、これによってアナログ 回路の動作速度を2倍に速めなければならない問題が発 生する。

17

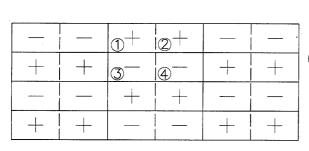

【0117】 かかる問題はドットインバージョンで著 しく表れるので図23のような方式で画素電極に画像信 号を書き込む。 画像信号を書き込む順序は図23に示 した番号順である。 と が全て(+)の極性信号であ るので が書き込まれるとたん はプレチャージされる ので1水平周期の半周期の間だけにも充電時間には大き 10 成図。 い問題はない。

【0118】 また と では画像信号の極性が変わる ので充電及び放電に長い時間が所要される。従って,

, から , へ移る間のブランキングの間,データ ライン、プレチャージまたはデータライン間のチャージ シャーリング(charge sharing)で充 電,放電時間を減少させる。

【0119】 なお, は が書き込まれる間,プレチ ャージされるので書き込み時間には問題がないが, の 書き込み時間には問題となり得るので、1水平周期の20 与えられる駆動信号の波形図。 間,走査ラインに与える駆動信号のハイ区間aとロー区 間bの値を調整して の書き込み時間を確保することが できる。

【0120】 以上,添付図面を参照しながら本発明に かかる液晶表示装置のソースドライバの好適な実施形態 について説明したが,本発明はかかる例に限定されな い。当業者であれば,特許請求の範囲に記載された技術 的思想の範疇内において各種の変更例または修正例に想 到し得ることは明らかでありそれについても当然に本発 明の技術的範囲に属するものと了解される。

#### [0121]

【発明の効果】 以上のように本発明の液晶表示装置の ソースドライバは,次の効果がある。 第1,一つのデ ータラインがその左側と右側の二つの画素領域に選択的 に画像信号を伝えることができるのでデータラインの数 を半分に減少することができる。第2,データラインの 数が半分に減少されるのでソースドライバの数も半分に 減少させ得る。従って,素子のサイズを減少させること ができ、同時にコストを低減することができる。第3、 同一サイズでさらに多い画像をディスプレイすることが 40 【図26】 従来技術による液晶表示装置の構成図。 できるので高解像度を実現することができる。

# 【図面の簡単な説明】

【図1】 本発明の第1実施例による液晶表示装置の構 成図。

【図2】 図1による液晶表示装置の走査ラインに与え られる駆動信号の波形図。

【図3】 本発明の第2実施例による液晶表示装置の構 成図。

【図4】 図3による液晶表示装置の走査ラインに与え られる駆動信号の波形図。

【図5】 本発明の第3実施例による液晶表示装置の構 成図。

【図6】 図5による液晶表示装置の走査ラインに与え られる駆動信号の波形図。

【図7】 本発明の第4実施例による液晶表示装置の構 成図。

【図8】 図7による液晶表示装置の走査ラインに与え られる駆動信号の波形図。

【図9】 本発明の第5実施例による液晶表示装置の構

【図10】 図9による液晶表示装置の走査ラインに与 えられる駆動信号の波形図。

【図11】 本発明の第6実施例による液晶表示装置の 構成図。

【図12】 図11による液晶表示装置の走査ラインに 与えられる駆動信号の波形図。

【図13】 本発明の第7実施例による液晶表示装置の 構成図。

【図14】 図13による液晶表示装置の走査ラインに

【図15】 本発明の第8実施例による液晶表示装置の 構成図。

【図16】 図15による液晶表示装置の走査ラインに 与えられる駆動信号の波形図。

【図17】 本発明の一実施の形態による液晶表示装置 のソースドライバの構成図。

【図18】 図17による動作波形図。

【図19】 本発明の一実施の形態による液晶表示装置 のソースドライバの他の実施例を示した図。

30 【図20】 図19による動作波形図。

【図21】 本発明の一実施の形態による液晶表示装置 のゲートドライバの構成図。

【図22】 図21による動作波形図。

【図23】 本発明の一実施の形態による液晶表示装置 による画像信号の書き込み順序を示した図

【図24】 一般的な液晶ディスプレイ素子の断面構造

【図25】 一般的な液晶ディスプレイ素子の概略的構 成図。

【図27】 従来液晶表示装置の走査ラインに与える駆 動信号の波形図。

【図28】 従来液晶表示装置によるソースドライバの 構成図。

【図29】 従来液晶表示装置によるソースドライバの 動作波形図。

【図30】 従来の液晶表示装置によるゲートドライバ の構成図。

【図31】 従来液晶表示装置によるゲートドライバの 50 動作波形図。

19

【符号の説明】

71:第1スイッチング部

71a,71b:第1,第2薄膜トランジスタ

\*73:第2スイッチング部

7 3 a , 7 3 b : 第 3 , 第 4 薄膜トランジスタ

20

\* 73c:第2画素電極

# 【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図23】

【図11】

【図13】

【図30】

【図15】

【図16】

【図17】

【図21】

【図18】

【図19】

【図27】

【図20】

【図24】

【図28】

【図31】

| 专利名称(译)        | 液晶显示装置的源极驱动器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |            |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|--|--|--|--|

| 公开(公告)号        | <u>JP2001042842A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日                   | 2001-02-16 |  |  |  |  |

| 申请号            | JP2000167947                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日                       | 2000-06-05 |  |  |  |  |

| [标]申请(专利权)人(译) | <br>权五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |            |  |  |  |  |

| 申请(专利权)人(译)    | 权 五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |            |  |  |  |  |

| [标]发明人         | 權五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           |            |  |  |  |  |

| 发明人            | 權五敬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           |            |  |  |  |  |

| IPC分类号         | G02F1/133 G09F9/30 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |            |  |  |  |  |

| CPC分类号         | G09G3/3677 G09G3/3614 G09G3/3648 G09G3/3659 G09G3/3688 G09G2300/0814 G09G2310/0251 G09G2310/027 G09G2310/0297 G09G2310/06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |            |  |  |  |  |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3/20.623.G G09G3/20.623.W |            |  |  |  |  |

| F-TERM分类号      | -TERM分类号 2H093/NA16 2H093/NA34 2H093/NA45 2H093/NA53 2H093/NA80 2H093/NB11 2H093/NC13 2H093 /NC15 2H093/NC16 2H093/NC22 2H093/NC23 2H093/NC26 2H093/NC34 2H093/NC40 2H093/NC67 2H093/ND49 2H093/ND52 2H093/ND54 2H093/NF05 2H193/ZA04 2H193/ZA08 2H193/ZB02 2H193 /ZC20 2H193/ZC26 2H193/ZC34 2H193/ZD23 2H193/ZE31 2H193/ZH40 2H193/ZH45 2H193/ZQ06 5C006/AA16 5C006/AC11 5C006/AC21 5C006/AF43 5C006/AF83 5C006/BB16 5C006/BC12 5C006 /BC23 5C006/BF03 5C006/BF04 5C006/FA42 5C006/FA43 5C080/AA10 5C080/BB06 5C080/CC03 5C080/DD22 5C080/EE29 5C080/EE30 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080 /JJ06 |                           |            |  |  |  |  |

| 优先权            | 1999P20721 1999-06-04 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |            |  |  |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |            |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |            |  |  |  |  |

#### 摘要(译)

解决的问题:提供一种液晶显示装置及其驱动电路,该液晶显示装置及其驱动电路通过实现相同的图像表示同时将数据线的数量减少到传统水平的一半来降低成本。 可以将图像信号传输到液晶显示装置的数据线的左右像素区域,以将数据线的数量减少一半,并将相应的源极驱动器的数量减少一半。 将水平同步信号的一个周期划分为两个部分,并且对与上半部分和后半部分中的奇数和偶数列线相对应的图像信号进行采样和锁存。