(19)日本国特許庁( J P )

## (12) 公開特許公報(A)

(11)特許出願公開番号

特開2003 - 75805

(P2003 - 75805A)

(43)公開日 平成15年3月12日(2003.3.12)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テ-マコード <sup>*</sup> (参考) |

|--------------------------|------|---------------|--------------------------|

| G 0 2 F 1/133            | 550  | G 0 2 F 1/133 | 550 2 H 0 9 3            |

| G 0 9 G 3/20             | 611  | G 0 9 G 3/20  | 611 A 5 C 0 0 6          |

|                          | 621  |               | 621 B 5 C 0 8 0          |

|                          | 624  |               | 624 B                    |

|                          | 631  |               | 631 H                    |

審査請求 未請求 請求項の数 60 L (全 9 数) 最終頁に続く

(21)出願番号 特願2001 - 264252(P2001 - 264252)

(22)出願日 平成13年8月31日(2001.8.31)

(71)出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(72)発明者 藤原 久男

埼玉県深谷市幡羅町一丁目9番地2 株式会

社東芝深谷工場内

(74)代理人 100058479

弁理士 鈴江 武彦 (外6名)

最終頁に続く

(54)【発明の名称】 液晶表示素子

## (57)【要約】

【課題】低消費電力で高品位な画像を安定に表示する。

【解決手段】液晶表示素子は液晶表示画素 P X と、外部から供給される表示信号を液晶表示画素 P X に印加するスイッチ素子 Qsig と、液晶表示画素 P X に並列的に接続され液晶表示画素 P X に印加される表示信号によって充放電される補助容量 C sig と、液晶表示画素 P X に印加される表示信号を保持し、スイッチ素子 Qsig が継続的に非導通に維持される低消費電力モードで自身の保持する表示信号を液晶表示画素 P X に印加するスタティック RAM 回路 M R と、液晶表示画素 P X およびスタティック RAM 回路 M R 間に接続されスタティック RAM 回路 M R から液晶表示画素 P X に印加される表示信号が周期的にレベル反転されるように制御する極性制御回路 P C と、低消費電力モードで補助容量 C sig を液晶表示画素 P X から電気的に切り離す分離回路 S P とを備える。

**【特許請求の範囲】**

【請求項1】 液晶表示画素と、

外部から供給される表示信号を前記液晶表示画素に印加するスイッチ素子と、

前記液晶表示画素に並列的に接続され前記液晶表示画素に印加される表示信号によって充放電される容量素子と、

前記液晶表示画素に電気的に接続され、前記液晶表示画素に印加される表示信号を保持するメモリ回路と、

前記メモリ回路からの出力を所定の周期でレベル反転する極性制御回路と、を備えた液晶表示装置において、

前記液晶表示画素と前記容量素子とを選択的に電気的に切り離す分離回路とを備えることを特徴とする液晶表示素子。

【請求項2】 前記分離回路は前記極性制御回路の制御動作に連動するスイッチ回路から構成されることを特徴とする請求項1に記載の液晶表示素子。

【請求項3】 前記スイッチ回路は極性制御回路を制御するために外部から供給される制御信号を参照するよう構成されることを特徴とする請求項2に記載の液晶表示素子。

【請求項4】 前記メモリ回路はスタティックRAMで構成されることを特徴とする請求項1に記載の液晶表示素子。

【請求項5】 前記メモリ回路は、前記分離回路の制御により前記液晶表示画素に電気的に接続される第1モードと、前記分離回路の制御により前記液晶表示画素から電気的に切り離される第2モードとを含み、前記第2モードでは前記スイッチ素子が非導通に維持されることを特徴とする請求項1に記載の液晶表示素子。

【請求項6】 前記極性制御回路は、1フレーム周期で前記メモリ回路からの出力をレベル反転することを特徴とする請求項5に記載の液晶表示素子。

**【発明の詳細な説明】****【0001】**

【発明の属する技術分野】本発明は、表示画素が周期的にレベル反転される表示信号により駆動される液晶表示素子に関し、特に表示画素に供給される表示信号をアナログ的に保持するように充放電される容量素子および表示信号の供給停止時に容量素子に代わって表示信号をデジタル的に保持するメモリ回路を備える液晶表示素子に関する。

**【0002】**

【従来の技術】液晶表示装置は薄型、小型、軽量という特徴から携帯電話やPDA(PortableDigital Assistant e)のような携帯用端末機器の画像モニタとして広く利用されている。こうした携帯用端末機器は一般に充電池を電源として動作するため、電池の消耗率が利用可能時間に大きく影響する。このような理由により、液晶表示装置の低消費電力化が盛んに研究されている。

【0003】最近では、SRAM(Static Random Access Memory)技術が液晶表示パネルを低消費電力化するために用いられている。このSRAM技術では、例えば表示信号の更新を必要としない静止画像を表示する場合に、スタティックRAM回路が外部駆動回路から供給される表示信号を保持して表示画素に印加する。これにより、外部駆動回路の出力動作を停止させても画像表示を継続することが可能になる。

【0004】SRAM技術を用いた従来の液晶表示装置では、スタティックRAM回路が表示画面を構成する複数の表示画素の各々に対して設けられる。表示画素は一对の画素電極および対向電極とこれらの間に挟持される液晶材料とを含む。表示信号は対向電極に設定されるコモン電位に対して逆極性となるよう例えば1フレーム毎にレベル反転させて信号線に供給される。画素電極はこの信号線上の表示信号を画素スイッチとして選択的に出力する薄膜トランジスタに接続される。対向電極は、例えば画素電極に容量結合する補助容量線に接続され、この補助容量線の電位をコモン電位に等しい値に設定する。画素電極および対向電極は液晶材料を介して液晶容量を構成し、画素電極および補助容量線は液晶材料を介さず液晶容量に並列的な補助容量を構成する。画素スイッチは走査線からの走査信号によって駆動されたときに信号線上の表示信号を表示画素に印加する。このとき、表示画素は対向電極と画素電極間の電位差に対応する光透過率に設定される。補助容量は液晶容量に比べて十分大きな容量値を有し、表示画素に印加された表示信号により充放電される。補助容量がこの充放電により表示信号を保持すると、この表示信号は画素スイッチが非導通となったときに補助容量から画素電極に印加される。これにより、画素電極および対向電極間の電位差が維持される。

【0005】さらに、表示画素は極性制御回路を介してスタティックRAM回路に接続される。スタティックRAM回路は走査線からの走査信号の立ち上がりに伴って信号線から薄膜トランジスタを介して表示画素に印加される表示信号を保持し、この走査信号の立ち下がりに伴って自身で保持した表示信号を表示画素に印加する。ここで、極性制御回路はスタティックRAM回路から表示画素に印加される表示信号が1フレーム毎にレベル反転されコモン電位に対して逆極性となるように制御して、液晶材料の偏在化による焼き付き現象を防止する。

**【0006】**

【発明が解決しようとする課題】ところで、上述の液晶表示装置では、低消費電力モードにおいてスタティックRAM回路から表示画素に印加される表示信号を極性反転する際に液晶容量および補助容量の充放電電流が一時的に一对の電源端子の一方からまたは他方へ流れ、これにより電源端子間の電圧を変動させる。この電源変動は50 サタディックRAM回路の動作を不安定にする。さら

に、この電源変動が大きい場合には、スタティックRAM回路の保持内容が変化して表示画像の乱れを招く。

【0007】本発明の目的は、上述のような問題を解消し、低消費電力で高品位な画像を安定に表示できる液晶表示素子を提供することにある。

【0008】

【課題を解決するための手段】本発明によれば、液晶表示画素と、外部から供給される表示信号を液晶表示画素に印加するスイッチ素子と、液晶表示画素に並列的に接続され液晶表示画素に印加される表示信号によって充放電される容量素子と、液晶表示画素に電気的に接続され、液晶表示画素に印加される表示信号を保持するメモリ回路と、メモリ回路からの出力を所定の周期でレベル反転する極性制御回路と、を備えた液晶表示装置において、液晶表示画素と容量素子とを選択的に電気的に切り離す分離回路とを備える液晶表示素子が提供される。

【0009】この液晶表示素子では、分離回路が低消費電力モードで容量素子を液晶表示画素から電気的に切り離すため、メモリ回路から液晶表示画素に印加される表示信号の極性反転に伴って一時的に流れる容量素子の充放電電流のために生じるメモリ回路の電源変動を防止できる。従って、低消費電力で高品位な画像を安定に表示することが可能である。

【0010】

【発明の実施の形態】以下、本発明の一実施形態に係る液晶表示装置について図面を参照して説明する。この液晶表示装置は動画を表示可能な通常モードの他に例えば静止画を表示可能な低消費電力モードを持つ携帯端末機器の画像モニタとして用いられる。

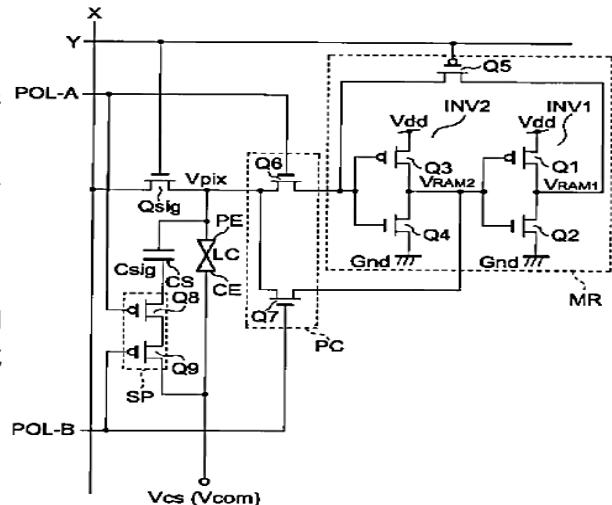

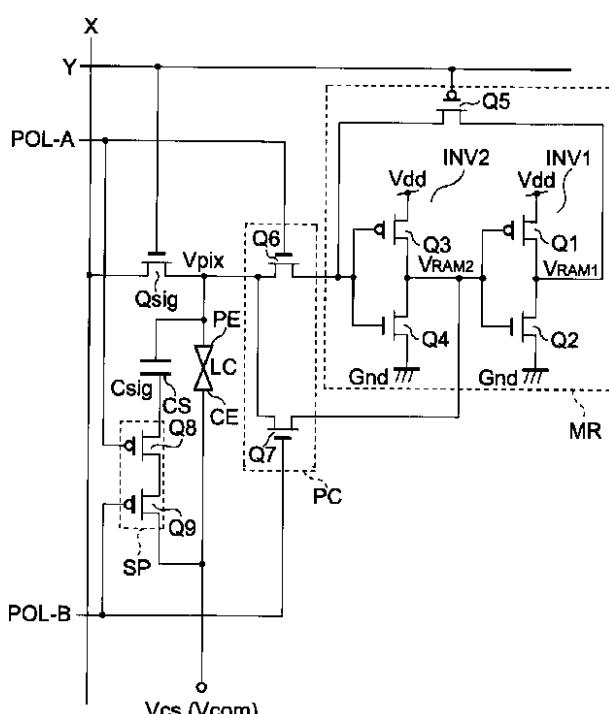

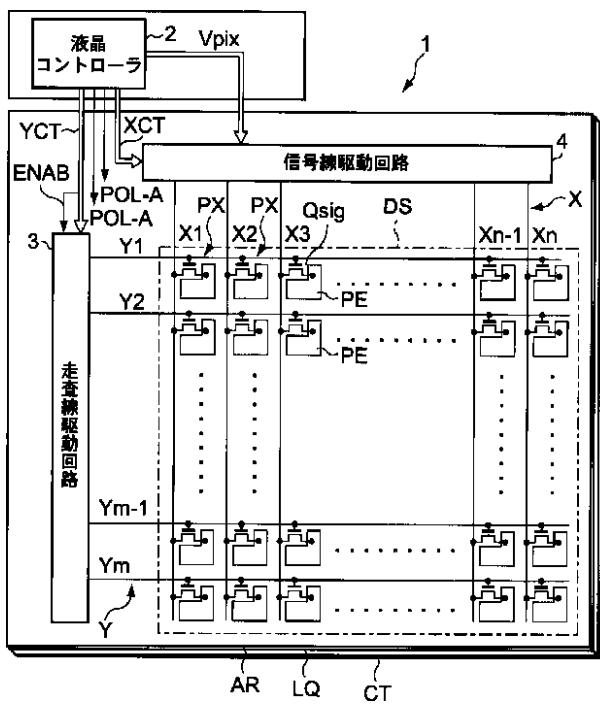

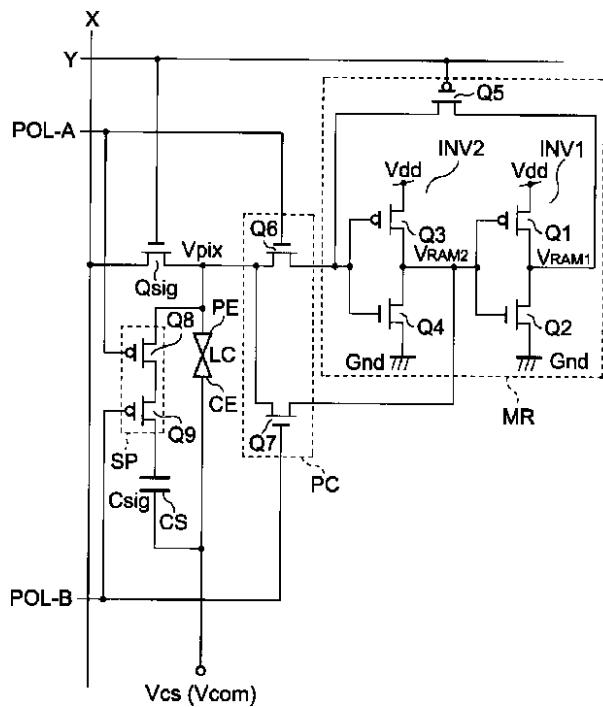

【0011】図1はこの液晶表示装置の概略的な構造を示し、図2はこの液晶表示装置の画素周辺回路を示す。

【0012】この液晶表示装置は、液晶表示パネル1およびこの液晶表示パネル1を制御する液晶コントローラ2を備える。液晶表示パネル1は液晶層LQがアレイ基板ARおよび対向基板CT間に保持される構造を有し、液晶コントローラ2は液晶表示パネル1から独立した外部駆動回路基板上に配置される。

【0013】アレイ基板ARは、マトリクス状に配置される複数の画素電極PE、複数の画素電極PEの行に沿って形成される複数の走査線Y(Y1~Ym)、複数の画素電極PEの列に沿って形成される複数の信号線X(X1~Xn)、信号線X1~Xnおよび走査線Y1~Ymの交差位置にそれぞれ隣接して配置され各々対応走査線Yからの走査信号に応答して対応信号線Xからの表示信号Vpixを対応画素電極に供給するスイッチ素子を構成する複数のNチャネルポリシリコン薄膜トランジスタ(TFT)Qsig、走査線Y1~Ymを駆動する走査線駆動回路3、並びに信号線X1~Xnを駆動する信号線駆動回路4を含む。走査線駆動回路3および信号線駆動回路4は、薄膜トランジスタQsigと同様にアレイ基板AR上に形成さ

れる複数のポリシリコン薄膜トランジスタにより構成される。

【0014】対向基板CTは複数の画素電極PEに対向して配置されコモン電位Vcomに設定される単一の対向電極CEを含む。

【0015】液晶コントローラ2は、例えば外部から供給される6ビットのデジタル映像信号および同期信号を受取り、通常モードで従来と同様に画素表示信号Vpix、垂直走査制御信号YCTおよび水平走査制御信号XCTを発生する。垂直走査制御信号YCTは例えば垂直スタートパルス、垂直クロック信号、出力イネーブル信号ENA等を含み、走査線駆動回路3に供給される。水平走査制御信号XCTは水平スタートパルス、水平クロック信号、極性反転信号等を含み、表示信号Vpixと共に信号線駆動回路4に供給される。

【0016】走査線駆動回路3はシフトレジスタ回路を含み、薄膜トランジスタQsigを導通させる走査信号を1垂直走査(フレーム)期間毎に走査線Y1~Ymに順次供給するよう垂直走査制御信号YCTによって制御される。シフトレジスタ回路は1垂直走査期間毎に供給される垂直スタートパルスを垂直クロック信号に同期してシフトさせることにより複数の走査線Y1~Ymのうちの1本を選択し、出力イネーブル信号を参照して選択走査線に走査信号を出力する。出力イネーブル信号ENAは垂直走査(フレーム)期間のうちの有効走査期間において走査信号の出力を許可するために高レベルに維持され、この垂直走査期間から有効走査期間を除いた垂直ブランкиング期間で走査信号の出力を禁止するために低レベルに維持される。

【0017】信号線駆動回路4はシフトレジスタ回路を有し、各走査線Yが走査信号により駆動される1水平走査期間(1H)において表示信号Vpixを信号線X1~Xnにそれぞれ供給するように水平走査制御信号XCTによって制御される。シフトレジスタ回路は1水平走査期間毎に供給される水平スタートパルスを水平クロック信号に同期してシフトさせることにより複数の信号線X1~Xnの1本を選択し、選択信号線に対して表示信号Vpixを供給する。

【0018】尚、対向電極CEには、図2に示すようにコモン電位Vcomが供給される。コモン電位Vcomは通常モードにおいて1水平走査期間(H)毎に0Vおよび5Vの一方から他方にレベル反転され、低消費電力モードにおいて1フレーム期間(F)毎に0Vおよび5Vの一方から他方にレベル反転される。また、通常モードにおいて、本実施形態のように1水平走査期間(H)毎にコモン電位Vcomをレベル反転させる代わりに、例えば2H毎、あるいは1フレーム期間(F)毎にコモン電位Vcomをレベル反転させてもかまわない。

【0019】極性反転信号はこのコモン電位Vcomのレベル反転に同期して信号線駆動回路4に供給される。そ

して、信号線駆動回路4は、通常モードにおいては0Vから5Vの振幅を持つ表示信号Vpixをコモン電位Vcomに対して逆極性となるように極性反転信号に応答してレベル反転し出力し、低消費電力モードではその動作を停止する。

【0020】本実施形態の液晶表示装置は、液晶層LQが対向電極CEに設定される0Vのコモン電位Vcomに対して5Vの表示信号Vpixを画素電極PEに印加することにより黒表示を行うノーマリホワイトであり、上述したように通常モードでは表示信号Vpixおよびコモン電位Vcomの電位関係が1水平走査期間(H)毎に交互に反転されるHコモン反転駆動が採用され、低消費電力モードでは1フレーム毎に交互に反転されるフレーム反転駆動が採用されている。表示画面DSは各々一対の画素電極PEおよび対向電極CE、並びにこれらの間に挟持された液晶層LQの液晶材料を含む複数の表示画素PXにより構成され、スタティックRAM回路MRがこれら表示画素PXの各々に対して設けられる。図2に示すように、画素電極PEはこの信号線X上の表示信号Vpixを画素スイッチとして選択的に出力する薄膜トランジスタQsigに接続される。対向電極CEは画素電極PEに容量結合する複数の補助容量線Csに接続され、この補助容量線Csの電位Vcsをコモン電位Vcomに等しい値に設定する。画素電極PEおよび対向電極CEは液晶材料を介して液晶容量LCを構成し、画素電極PEおよび補助容量線Csは液晶材料を介さず液晶容量LCに並列的な補助容量Csigを構成する。

【0021】薄膜トランジスタQsigは走査線Yからの走査信号によって駆動されたときに信号線X上の表示信号Vpixを表示画素PXに印加する。このとき、表示画素PXは対向電極CEと画素電極PE間の電位差に対応する光透過率に設定される。補助容量Csigは液晶容量LCに比べて十分大きな容量値を有し、表示画素PXに印加された表示信号Vpixにより充放電される。補助容量Csigがこの充放電により表示信号Vpixを保持すると、この表示信号Vpixは薄膜トランジスタQsigが非導通となったときに液晶容量LCに保持された電位の変動を補償し、これにより画素電極PEおよび対向電極CE間の電位差が維持される。

【0022】さらに、表示画素PXは図2に示すように極性制御回路PCを介してスタティックRAM回路MRに接続される。スタティックRAM回路MRはPチャネル薄膜トランジスタQ1, Q3, Q5およびNチャネル薄膜トランジスタQ2, Q4で構成され、極性制御回路PCはNチャネル薄膜トランジスタQ6およびQ7で構成される。薄膜トランジスタQ1, Q2は電源端子Vdd(=5V)および電源端子Gnd(=0V)間の電源電圧で動作する第1インバータ回路INV1を構成し、薄膜トランジスタQ3, Q4は電源端子Vdd, Gnd間の電源電圧で動作する第2インバータINV2を

構成する。インバータ回路INV1の出力端は走査信号により制御される薄膜トランジスタQ5を介してインバータ回路INV2の入力端に接続され、インバータ回路INV2の出力端はインバータ回路INV1の入力端に接続される。Pチャネル薄膜トランジスタQ5は、Nチャネル薄膜トランジスタQsigが走査線Yからの走査信号の立ち上がりにより導通したときに非導通となり、Nチャネル薄膜トランジスタQsigが走査線Yからの走査信号の立ち下がりにより非導通になったときに導通する。即ち、低消費電力モードで走査線駆動回路3からの走査信号が低レベルに維持される状態にあっては、Pチャネル薄膜トランジスタQ5は導通状態を維持する。極性制御回路PCは少なくとも静止画表示用の低消費電力モードにおいて例えば1フレーム毎に交互に高レベルに設定される極性制御信号POL-AおよびPOL-Bによりそれぞれ制御されるNチャネル薄膜トランジスタQ6, Q7で構成される。薄膜トランジスタQ6は画素電極PEとインバータ回路INV2の入力端並びに薄膜トランジスタQ5を介してインバータ回路INV1の出力端との間に接続され、薄膜トランジスタQ7は画素電極PEとインバータ回路INV1の入力端並びにインバータ回路INV2の出力端との間に接続される。

【0023】通常モードで走査線Yからの走査信号が立ち上ると、薄膜トランジスタQsigが導通し薄膜トランジスタQ5が非導通となる。極性制御信号POL-AおよびPOL-Bは静止画用の低消費電力モードを設定しない場合薄膜トランジスタQ6, Q7を共に非導通に維持するためにいずれも低レベルに設定可能である。

【0024】低消費電力モードを設定する場合には、これら極性制御信号POL-AおよびPOL-Bが少なくとも1フレーム前に薄膜トランジスタQsigを介して画素電極PEに印加される表示信号VpixをスタティックRAM回路MRに供給するために一方において高レベルに設定され、後続フレーム毎に交互に高レベルに設定される。

【0025】例えば極性制御信号POL-Aだけが高レベルに設定されると、薄膜トランジスタQ6が画素電極PEに印加された表示信号Vpixをインバータ回路INV2に供給する。この表示信号Vpixはインバータ回路INV2によってレベル反転され表示信号VRAM2としてインバータ回路INV1に出力され、さらにこのインバータ回路INV1によりレベル反転され表示信号VRAM1として出力される。走査線Yからの走査信号が立ち下がると、薄膜トランジスタQsigが非導通となって画素電極PEを電気的なフローティング状態とする一方で、薄膜トランジスタQ5が導通して表示信号VRAM1をインバータ回路INV2に供給する。表示信号Vpixはコモン電位Vcomに対して表示信号VRAM1と同極性であり、表示信号VRAM1はスタティックRAM回路MRによって表示信号Vpixとしてデジタル的に保持されると共に、薄膜

トランジスタQ 6 を介して画素電極P E に供給される。

【0026】また、逆に極性制御信号POL - B だけが高レベルに設定されると、薄膜トランジスタQ 7 が画素電極P E に印加された表示信号Vpixをインバータ回路INV1 に供給する。この表示信号Vpixはインバータ回路INV1 によってレベル反転され表示信号VRAM1として出力される。走査線Yからの走査信号が立ち下がると、薄膜トランジスタQsigが非導通とて画素電極P E を電気的なフローティング状態とする一方で、薄膜トランジスタQ 5 が導通して表示信号VRAM1をインバータ回路INV2 に供給する。この表示信号VRAM1はインバータ回路INV2 によってレベル反転され表示信号VRAM2としてインバータ回路INV1 に出力される。表示信号Vpixはコモン電位Vcomに対して表示信号VRAM2と同極性であり、この表示信号VRAM2はスタティックRAM回路MR によって表示信号Vpixとしてデジタル的に保持されると共に、薄膜トランジスタQ 6 を介して画素電極P E に供給される。

【0027】極性制御信号POL - A , POL - B が1フレーム毎に交互に高レベルに設定されると、互いに逆の電位関係にある表示信号VRAM2 , VRAM1がスタティックRAM回路MR から交互に画素電極P E に供給され、液晶材料の偏在化による焼き付き現象を防止する。

【0028】液晶表示装置は図2に示すように補助容量Csigと直列に接続され低消費電力モードで補助容量Csigを表示画素PXから電気的に分離する分離回路SPを備える。この分離回路SPは低消費電力モードで交互に高レベルとなる極性制御信号POL - A , POL - B によりそれぞれ制御されるPチャネル薄膜トランジスタQ8 , Q9を含む。薄膜トランジスタQ8 は極性制御信号POL - A が高レベルのときに非導通になり、薄膜トランジスタQ9 は極性制御信号POL - B が高レベルのときに非導通となる。すなわち、薄膜トランジスタQ8 , Q9の一方が低消費電力モードで非導通になるため、分離回路SPが低消費電力モードで継続的に表示画素PXから電気的に分離される。

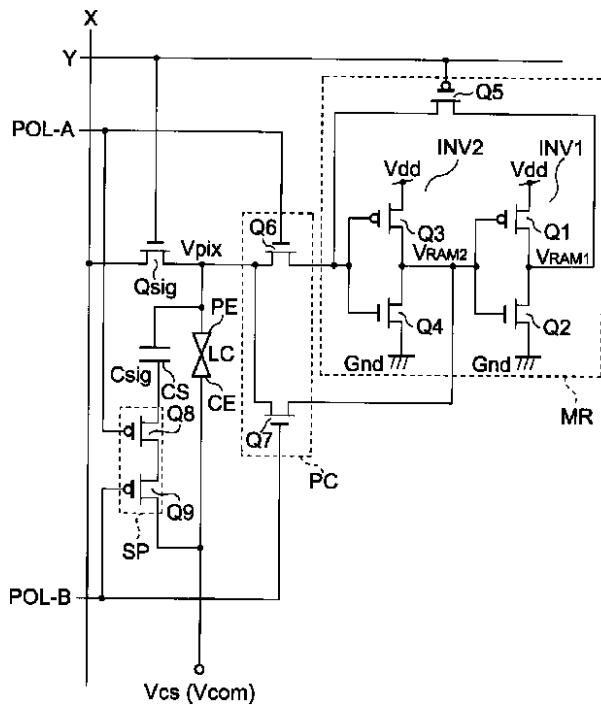

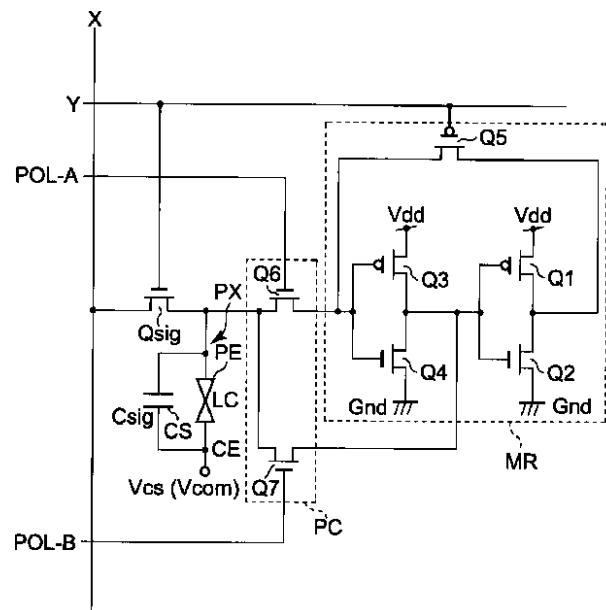

【0029】ここで、分離回路SPが図6に示すように省略された場合に生じるスタティックRAM回路MRの電源変動について説明する。ここでは、低消費電力モードで薄膜トランジスタQ5 が導通した状態にあり、極性制御信号POL - A が高レベルであると仮定する。例えば5Vの表示信号VRAM1が表示信号VpixとしてスタティックRAM回路MRから薄膜トランジスタQ6を介して画素電極P E に供給され、0Vのコモン電位Vcomが対向電極CEに印加された場合、表示画素PXがこれら画素電極P E および対向電極CEから液晶層LQに印加される5Vの電位差により黒表示に設定される。すなわち、薄膜トランジスタQ6の導通時には、液晶容量LCおよび補助容量Csigの充電電流が一時的に電源端子Vddから薄膜トランジスタQ1 , Q5 , Q6を介して画

10

20

30

40

50

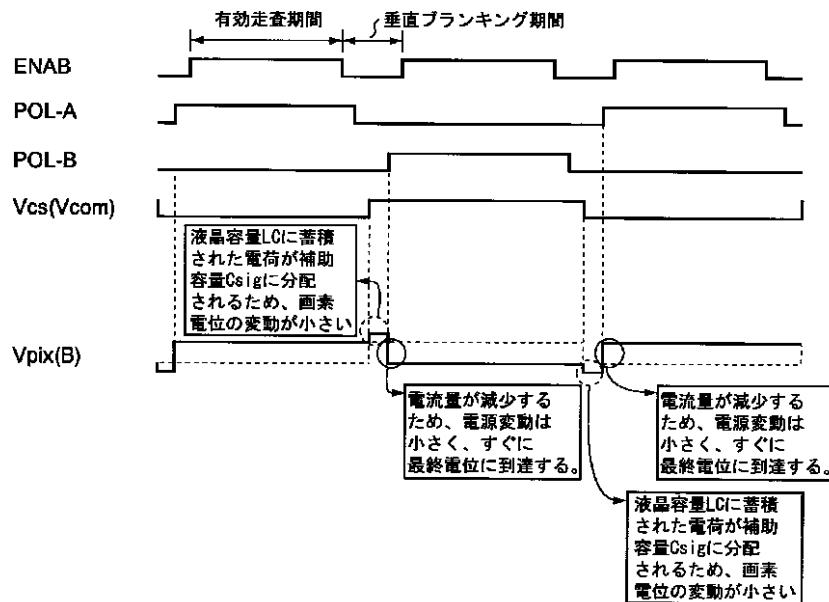

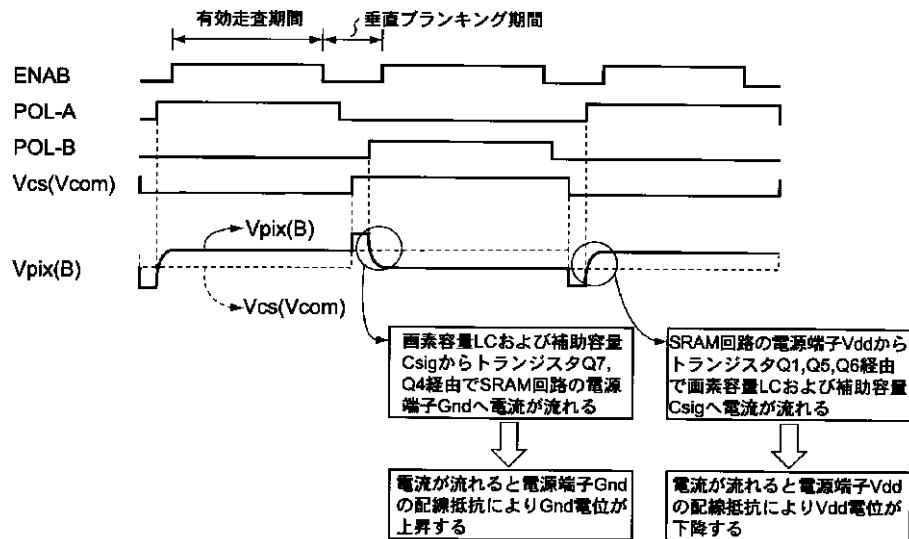

素電極P E に流れる。画素電極P E の電位を5Vに設定する。図7に示す垂直プランギング期間では、極性制御信号POL - A が立ち下がり、しばらくして極性制御信号POL - B が立ち上がる。表示信号VRAM1は極性制御信号POL - A の立ち下がりに伴って非導通となる薄膜トランジスタQ6により遮断される。コモン電位Vcomはこの遮断から極性制御信号POL - B の立ち上がりまでの間に0Vから5Vにレベル反転される。画素電極P E の電位はコモン電位Vcomのレベル反転に伴って5Vから10Vにシフトする。この後、薄膜トランジスタQ7が極性制御信号POL - B の立ち上がりに伴って導通すると、0Vの表示信号VRAM2が表示信号VRAM1に代わる表示信号Vpixとして薄膜トランジスタQ7を介して画素電極P E に供給される。これにより、表示画素PXがこれら画素電極P E および対向電極CEから逆極性で液晶層LQに印加される5Vの電位差により黒表示に設定される。薄膜トランジスタQ7の導通時には、液晶容量LCおよび補助容量Csigの放電電流が一時的に画素電極P E から薄膜トランジスタQ7 , Q4を介して電源端子Gndに流れる。

【0030】通常、スタティックRAM回路MRなどの配線は電源線も含めて導電性薄膜で形成されるため、その配線抵抗が高い。このような導電性薄膜に電流が流れた場合には、この配線抵抗による電圧降下が発生する。補助容量Csigが1pFで液晶容量LCが平均0.2pFであり、これらの電極間電圧を5Vとし、電流が10μsの時間だけ流れたとすると、 $(1\text{ pF} + 0.2\text{ pF}) \times 5\text{ V} \times (1 / 10\text{ } \mu\text{ s}) = 600\text{ nA}$ の充放電電流が各表示画素PXについて流れる。

【0031】さらに、各行の総画素数が200画素×3(赤、緑、青)=600画素であるとすれば、1行当たり1.36mAの電流となり、電源端子Gnd用電源配線の配線抵抗が給電端から走査線Yに沿って最も遠い端まで10kΩ あったとすると、3.6Vの電位差が給電端と最遠端との間に生じる。すなわち、電流が画素電極P E から電源端子Gndに流れる場合に+3.6Vの電位変化が発生し、逆に電流が電源端子Vddから画素電極P E に流れる場合に-3.6Vの電位変化が発生する。

【0032】従って、画素電極P E からの電荷流入出が発生する場合には、スタティックRAM回路MRの電源変動が発生し、電源端子Vddと電源端子Gndの電位差を小さくすることになる。すなわち、スタティックRAM回路MRの電源電圧が低下するため、インバータ回路INV1の薄膜トランジスタQ1 , Q2およびインバータ回路INV2の薄膜トランジスタQ3 , Q4を安定にスイッチングさせることが出来なくなり、スタティックRAM回路MR全体の動作を不安定にする。電源変動が大きい場合には、スタティックRAM回路MRの保持内容が変化し、表示画像の乱れを招く。さらに液晶容量

L C および補助容量 C sig の充放電電流が極性制御回路 P C の動作により不必要に流れるため、これが低消費電力化の妨げとなる。

【0033】これに対して、図2に示す分離回路 S P が設けられる場合、薄膜トランジスタ Q 8 が極性制御信号 P O L - A の立ち上がりに伴って補助容量 C sig を液晶容量 L C から電気的に切り離し、薄膜トランジス Q 9 が極性制御信号 P O L - B の立ち上がりに伴って補助容量 C sig を液晶容量 L C から電気的に切り離す。このため、補助容量 C sig の充放電電流が極性制御信号 P O L - A および極性制御信号 P O L - B の立ち上がり直後に流れなくなる。すなわち、液晶容量 C sig の充放電電流だけが図3に示すように流れる。この補助容量 C sig の充放電電流は図6に示す比較例の構造において流れる充放電電流のうちで大部分を占めることから、スタティック RAM 回路 M R の電源変動を大幅に改善できる。例えば、補助容量 C sig が 1 p F で液晶容量 L C が平均 0.2 p F あるとした場合、表示画素 P X の総容量が 1 / 6 になるため、この表示画素 P X に関する充放電電流も 1 / 6 となる。この結果、図6に示す比較例の構造においてスタティック RAM 回路 M R の電源となる 5 V の電圧で生じていた 3.6 V (72%) の変動を、補助容量 C sig を切り離すことにより 0.6 V (12%) にまで低減できる。この値は、津素性のデジタル回路の電源電圧精度 ( $\pm 10\%$ ) と同等であり、スタティック RAM 回路 M R が安定に動作するようになる。

【0034】本実施形態の液晶表示素子では、分離回路 S P が低消費電力モードで補助容量を表示画素 P X から電気的に切り離すため、スタティック RAM 回路 M R から表示画素 P X に印加される表示信号 Vpix の極性反転に伴って一時的に流れる補助容量 C sig の充放電電流のために生じるスタティック RAM 回路 M R の電源変動を防止できる。従って、低消費電力で高品位な画像を安定に表示することが可能である。

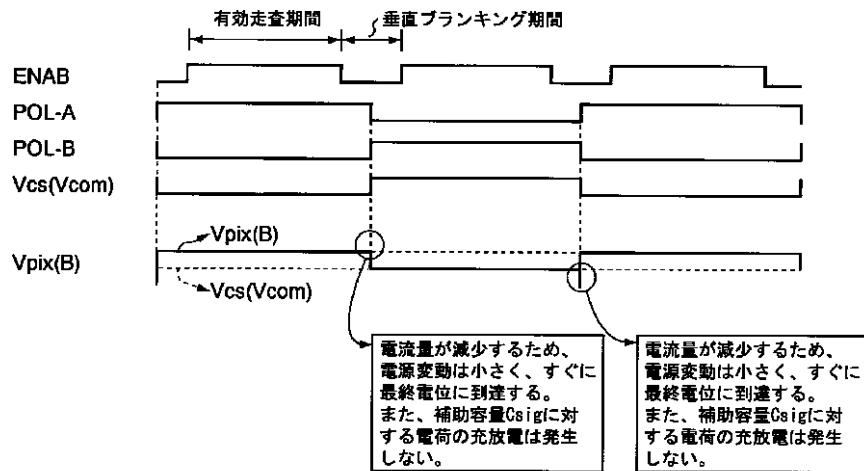

【0035】図4は極性制御信号 P O L - A および P O L - B のレベル反転タイミングを同時にした場合に得られる動作波形を示す。すなわち、先行フレームで極性制御信号 P O L - A が立ち下がるタイミングで極性制御信号 P O L - B が立ち上がり、後続フレームで極性制御信号 P O L - A が立ち上がるタイミングで極性制御信号 P O L - B が立ち下がる。この場合、補助容量 C sig が低消費電力モードで常に液晶容量 L C から切り離された状態となる。従って、表示信号 Vpix をスタティック RAM 回路 M R から表示画素 P X に供給する場合、液晶容量 L C に分配される電荷も含めて補助容量 C sig に対する電荷の流入出が発生しない。このため、極性制御回路 P C の動作により不必要に流れる液晶容量 L C および補助\*

\*容量 C sig の充放電電流をさらに低減して、低消費電力化を図ることができる。

【0036】図5は図2に示す液晶表示装置の画素周辺回路の変形例を示す。この変形例では、分離回路 S P が補助容量 C sig と画素電極 P E との間に配置される。この構成でも、薄膜トランジスタ Q 8 が極性制御信号 P O L - A の立ち上がりに伴って補助容量 C sig を液晶容量 L C から電気的に切り離し、薄膜トランジス Q 9 が極性制御信号 P O L - B の立ち上がりに伴って補助容量 C sig を液晶容量 L C から電気的に切り離す。このため、上述の実施形態と同様の効果が得られる。

【0037】尚、本発明は上述の実施形態に限定されず、その要旨を逸脱しない範囲で様々に変形可能である。例えば、分離回路 S P の薄膜トランジスタ Q 8、Q 9 が補助容量 C sig の両側にそれぞれ配置されても良い。また、分離回路 S P は極性制御信号 P O L - A および P O L - B とは独立な制御信号により低消費電力モードで補助容量 C sig を電気的に表示画素 P X 、すなわち液晶容量 L C から切り離すように構成されても良い。

【0038】

【発明の効果】以上のように本発明によれば、低消費電力で高品位な画像を安定に表示できる液晶表示素子を提供することができる。

【図面の簡単な説明】

【図1】本発明の一実施形態に係る液晶表示装置の概略的な構造を示す図である。

【図2】図1に示す液晶表示装置の画素周辺回路を示す回路図である。

【図3】図2に示す画素周辺回路の動作波形を示すタイムチャートである。

【図4】図2に示す一対の極性制御信号のレベル反転タイミングを同時にした場合に得られる画素周辺回路の動作波形を示すタイムチャートである。

【図5】図2に示す画素周辺回路の変形例を示す回路図である。

【図6】図2に示す分離回路を省略した比較例の回路図である。

【図7】図6に示す比較例の動作波形を示すタイムチャートである。

【符号の説明】

P X … 液晶表示画素

Qsig … 画素スイッチ用薄膜トランジスタ

C sig … 補助容量

M R … スタティック RAM 回路

P C … 極性制御回路

S P … 分離回路

L C … 液晶容量

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

フロントページの続き

(51)Int.Cl.<sup>7</sup>

識別記号

F I

テ-マコ-ド<sup>®</sup> (参考)

G 0 9 G 3/36

G 0 9 G 3/36

F ターム(参考) 2H093 NA16 NA33 NA34 NA45 NC26

NC34 NC35 NC40 ND10 ND35

ND49

5C006 AC28 AF44 BB16 BC03 BC06

BC11 BC20 BF09 FA47

5C080 AA10 BB05 DD26 FF11 GG12

JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示元件                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2003075805A</a>                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2003-03-12 |

| 申请号            | JP2001264252                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2001-08-31 |

| [标]申请(专利权)人(译) | 株式会社东芝                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 东芝公司                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 藤原久男                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 藤原 久男                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G2300/0857                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G02F1/133.550 G09G3/20.611.A G09G3/20.621.B G09G3/20.624.B G09G3/20.631.H G09G3/36                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA33 2H093/NA34 2H093/NA45 2H093/NC26 2H093/NC34 2H093/NC35 2H093/NC40 2H093/ND10 2H093/ND35 2H093/ND49 5C006/AC28 5C006/AF44 5C006/BB16 5C006/BC03 5C006/BC06 5C006/BC11 5C006/BC20 5C006/BF09 5C006/FA47 5C080/AA10 5C080/BB05 5C080/DD26 5C080/FF11 5C080/GG12 5C080/JJ02 5C080/JJ03 5C080/JJ04 2H193/ZA04 2H193/ZA20 2H193/ZC15 2H193/ZC20 2H193/ZC26 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                  |         |            |

#### 摘要(译)

解决的问题：以低功耗稳定显示高质量图像。液晶显示元件包括：液晶显示像素PX；用于将从外部提供的显示信号施加到液晶显示像素PX的开关元件Qsig；以及并联连接并施加到液晶显示像素PX的液晶显示像素PX。保持由显示信号充电和放电的存储电容器Csig和施加到液晶显示像素PX的显示信号，并且开关元件Qsig自身保持在低功耗模式下，在该模式下，开关元件Qsig连续保持非导通状态。将显示信号施加到液晶显示像素PX的静态RAM电路MR和连接在液晶显示像素PX和静态RAM电路MR之间并且从静态RAM电路MR施加到液晶显示像素PX的显示信号被周期性地电平反转。设置用于控制的极性控制电路PC和用于在低功耗模式下将辅助电容Csig与液晶显示像素PX电断开的分离电路SP。