(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2003 - 280608

(P2003 - 280608A)

(43)公開日 平成15年10月2日(2003.10.2)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テ-マコード <sup>*</sup> (参考) |

|--------------------------|------|---------------|--------------------------|

| G 0 9 G 3/36             |      | G 0 9 G 3/36  | 2 H 0 9 3                |

| G 0 2 F 1/133            | 520  | G 0 2 F 1/133 | 5 C 0 0 6                |

|                          | 550  |               | 5 C 0 8 0                |

| G 0 9 G 3/20             | 612  | G 0 9 G 3/20  | 612 D                    |

|                          |      |               | 612 E                    |

審査請求 未請求 請求項の数 4 O L (全 6 数) 最終頁に続く

(21)出願番号 特願2002 - 84643(P2002 - 84643)

(71)出願人 000001960

シチズン時計株式会社

東京都西東京市田無町六丁目1番12号

(22)出願日 平成14年3月26日(2002.3.26)

(72)発明者 矢野 敬和

東京都西東京市田無町六丁目1番12号 シチズン時計株式会社内

(72)発明者 高橋 和壽

東京都西東京市田無町六丁目1番12号 シチズン時計株式会社内

(72)発明者 宮部 光正

東京都西東京市田無町六丁目1番12号 シチズン時計株式会社内

最終頁に続く

(54)【発明の名称】 液晶表示装置

(57)【要約】

【課題】 TFT型液晶表示装置を駆動するためには、種々の電位を持つ電源が必要となる。今までの大型液晶表示装置においては、その面積に起因する電流を必要とするため、上記すべての電位の電源を電源回路から発生していた。この回路をそのまま小型液晶表示装置に適用すれば、簡単で確実に駆動することが可能であるが、実装容積や価格の面で大型液晶表示装置と同じとなる。

【解決手段】 上記課題を解決するため、5ボルトで駆動できるロジック汎用ICをコモン電源に採用し、高電位電源から低電位電源を発生する際のレベルシフトを使い、階調基準のための電位は位相反転の出力間に複数の抵抗を介して異なる電位の信号を簡単に発生する。

## 【特許請求の範囲】

【請求項1】 複数の電源の電位とロジック電源の電位を発生する電源回路と、該ロジック電源で駆動するロジック回路と、データ用ICと、走査用ICを備え、薄膜トランジスタを形成した素子基板と、コモン電極を形成した対向基板からなる液晶表示装置において、前記ロジック回路からの出力信号を中電位の電源で駆動するCMOSトランジスタまたはTTLトランジスタに入力し、該CMOSトランジスタまたは該TTLトランジスタからの第1の出力を、ロジック電源電位とグランドの間の電位または前記複数の電源電位とグランドの間の電位にクランプして、前記コモン電極に接続することを特徴とする液晶表示装置。

【請求項2】 複数の電源の電位とロジック電源の電位を発生する電源回路と、該ロジック電源で駆動するロジック回路と、データ用ICと、走査用ICを備え、薄膜トランジスタを形成した素子基板と、コモン電極を形成した対向基板からなる液晶表示装置において、前記ロジック回路からの出力信号を中電位の電源で駆動するCMOSトランジスタまたはTTLトランジスタに入力し、該CMOSトランジスタまたは該TTLトランジスタからの第2の出力を、高電圧にレベルシフトし、ロジック電源の電位、中電位またはグランドにクランプして整流し、低電位の電源とすることを特徴とする液晶表示装置。

【請求項3】 複数の電源の電位とロジック電源の電位を発生する電源回路と、該ロジック電源で駆動するロジック回路と、データ用ICと、走査用ICを備え、薄膜トランジスタを形成した素子基板と、コモン電極を形成した対向基板からなる液晶表示装置において、前記ロジック回路からの出力信号を中電位の電源で駆動するCMOSトランジスタまたはTTLトランジスタに入力し、該CMOSトランジスタまたは該TTLトランジスタからの第3の出力の出力端と、該第3の出力と逆位相である第4の出力の出力端を複数の抵抗を直列に介して接続し、該第3の出力の出力端の電位、該第4の出力の出力端の電位および該第3の出力と該第4の出力の間の電位を前記データ用ICに入力することを特徴とする液晶表示装置。

【請求項4】 複数の電源の電位とロジック電源の電位を発生する電源回路と、該ロジック電源で駆動するロジック回路と、データ用ICと、走査用ICを備え、薄膜トランジスタを形成した素子基板と、コモン電極を形成した対向基板からなる液晶表示装置において、前記ロジック回路からの出力信号を中電位の電源で駆動する複数個のCMOSトランジスタまたはTTLトランジスタを1個のICに備え、該CMOSトランジスタまたは該TTLトランジスタからの第1の出力を、ロジック電源電位にクランプして前記コモン電極に接続し、該CMOSトランジスタまたは該TTLトランジスタからの第2の

10

20

30

50

出力を高電圧にレベルシフトし、ロジック電源の電位、中電位またはグランドにクランプして整流して低電位の電源とし、該CMOSトランジスタまたは該TTLトランジスタからの第3の出力端と、該第3の出力と逆位相である第4の出力の出力端を複数の抵抗を直列に介して接続し、該第3の出力の出力端の電位、該第4の出力の出力端の電位および該第3の出力と該第4の出力の間の電位を前記データ用ICに入力することを特徴とする液晶表示装置。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は時分割駆動回路を備えた薄膜トランジスタ(TFT)型液晶表示装置に関する。

## 【0002】

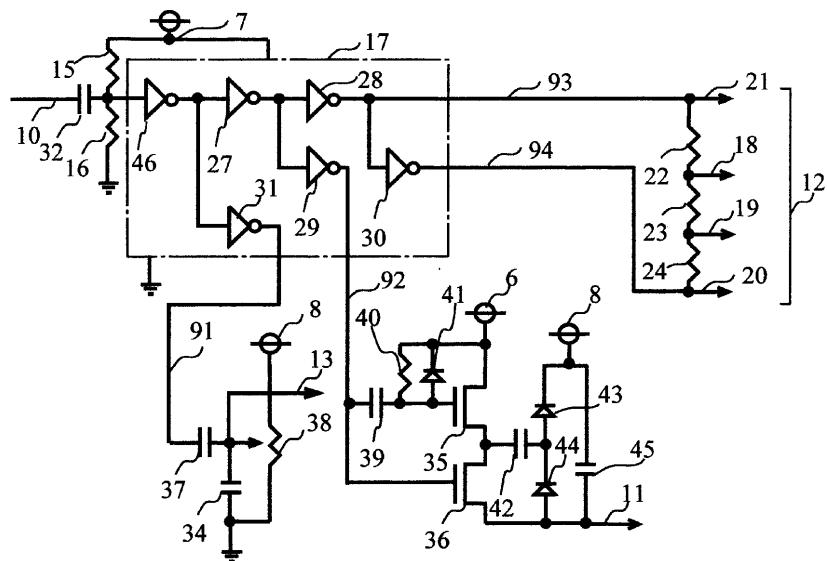

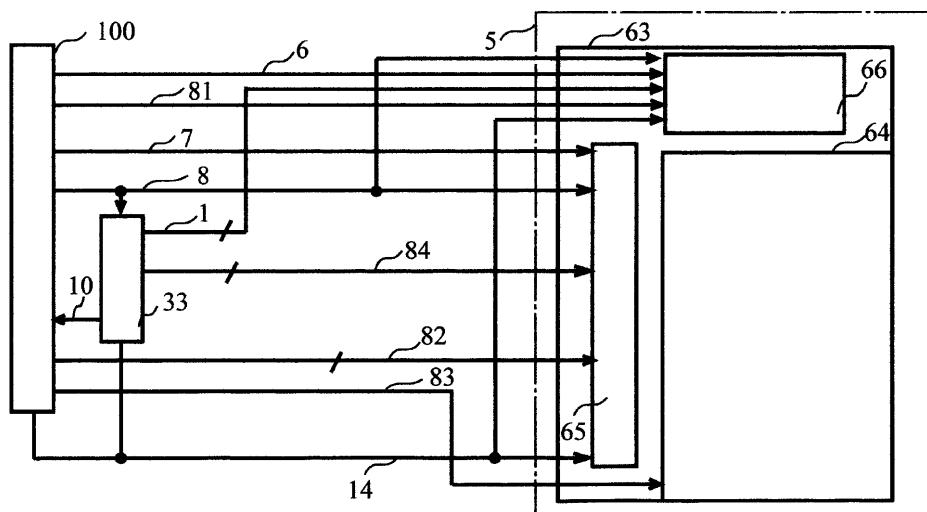

【従来の技術】TFT型液晶表示装置はコントラストや応答性の良さにより、携帯型PCの等に採用されており現在の液晶表示装置の主流である。図4は従来のTFT液晶表示装置の駆動回路ブロック図を示す。図中、電源回路ブロック84は駆動に必要な電源を発生し、電池などの電源、駆動に必要な電位の電源にするためのコイルを用いた昇圧回路および各電源を平滑化するためのオペアンプを用いたレギュレータ回路から構成され、電源回路ブロック100は第1の電源6、第2の電源7および第3の電源8を安定して発生する。ここで、第1の電源6は高電圧電源(約15ボルト)、第4の電源81は低電圧電源(約-10~-15ボルト)、第3の電源8はロジック電源(約3.3ボルト)あり、第2の電源7はデータ側IC出力用の中電圧電源(約5ボルト)である。

【0003】さらに、電源回路ブロック84はコモン信号10を基に、オペアンプで構成される回路を介してコモン電源83および階調電位群82を液晶表示装置5に出力する。ここで、コモン電源83は矩形波であり、階調電位群はグランド(GND)14と第2の電源7およびその間の2種の電位からなる。ロジック回路33は液晶表示装置5を駆動するための同期信号およびデータ信号であるデータロジック信号群84および走査ロジック信号群1を発生し、さらにコモン信号10を発生する。

【0004】液晶表示装置5は薄膜トランジスタ(TFT)を形成した素子基板63と全面電極を形成した対向基板64から構成され、前記素子基板にデータ用IC65と走査用IC66を搭載している。データ用IC65は、GND14、第2の電源7、第3の電源8、データロジック信号群84および階調電位群82を入力し、データを出力する。走査用IC66は、GND14、第1の電源6、第3の電源8、第4の電源81および走査ロジック信号群1を入力して走査する。ここで、データ用IC65の出力はデータロジック用信号群84中の出力反転信号(図示せず。)に応じて反転する。

## 【0005】

【発明が解決しようとする課題】上述の通り TFT 型液晶表示装置を駆動するためには、種々の電位を持つ電源が必要となる。今までの大型液晶表示装置においては、その面積に起因する電流を必要とするため、上記すべての電位の電源を電源回路から発生していた。この回路をそのまま小型液晶表示装置に適用すれば確実に駆動することが可能であるが、実装容積や価格の面で大型液晶表示装置と同じとなる。本発明によれば、電源回路から発生する電源の数を減らす回路を備えた TFT 型小型液晶表示装置が可能となる。

## 【0006】

【課題を解決するための手段】上記目的を達成するため、本発明の液晶表示装置は、下記記載の手段を採用する。すなわち、本発明の液晶表示装置は、複数の電源の電位とロジック電源の電位を発生する電源回路と、該ロジック電源で駆動するロジック回路と、データ用 IC と、走査用 IC を備え、薄膜トランジスタを形成した素子基板と、コモン電極を形成した対向基板からなる液晶表示装置において、前記ロジック回路からの出力信号を中電位の電源で駆動する CMOS トランジスタまたは TTL トランジスタに入力し、該 CMOS トランジスタまたは該 TTL トランジスタからの第 1 の出力を、ロジック電源電位とグランドの間の電位または前記複数の電源電位とグランドの間の電位にクランプして、前記コモン電極に接続することを特徴とする。また、本発明の液晶表示装置は、複数の電源の電位とロジック電源の電位を発生する電源回路と、該ロジック電源で駆動するロジック回路と、データ用 IC と、走査用 IC を備え、薄膜トランジスタを形成した素子基板と、コモン電極を形成した対向基板からなる液晶表示装置において、前記ロジック回路からの出力信号を中電位の電源で駆動する CMOS トランジスタまたは TTL トランジスタに入力し、該 CMOS トランジスタまたは該 TTL トランジスタからの第 2 の出力を、高電圧にレベルシフトし、ロジック電源の電位、中電位またはグランドにクランプして整流し、低電位の電源とすることを特徴とする。さらに、本発明の液晶表示装置は、複数の電源の電位とロジック電源の電位を発生する電源回路と、該ロジック電源で駆動するロジック回路と、データ用 IC と、走査用 IC を備え、薄膜トランジスタを形成した素子基板と、コモン電極を形成した対向基板からなる液晶表示装置において、前記ロジック回路からの出力信号を中電位の電源で駆動する CMOS トランジスタまたは TTL トランジスタに入力し、該 CMOS トランジスタまたは該 TTL トランジスタからの第 3 の出力の出力端と、該第 3 の出力と逆位相である第 4 の出力の出力端を複数の抵抗を直列に介して接続し、該第 3 の出力の出力端の電位、該第 4 の出力の出力端の電位および該第 3 の出力と該第 4 の出力の間の電位を前記データ用 IC に入力することを特徴とす

10

20

20

30

40

50

る。

【0007】[作用] 電源の一部を発生するため、ロジック回路を積極的に採用する。要点は現在のロジック回路は 3.3 ボルト電源であるのに対して、液晶駆動は 5 ボルトで行わなければならないところである。ロジック汎用 IC である 74HC シリーズは 5 ボルト電源駆動であることを利用すれば、小型の TFT 型液晶表示装置を簡素に駆動することは可能である。すなわち、その出力能力をうまく使えばそのままコモン電源に採用でき、高電位電源から低電位電源を発生する際のレベルシフトにおいて、振幅が 5 ボルトであるので多大な電流を摂取することが可能となる。また、データ出力はロジック的に反転するよりも、階調基準のための電位自体を反転させた方が安定した画像が得られることが知られている。本発明においては、反転位相の出力間に複数の抵抗を介して異なる電位の信号を簡単に発生することによって階調基準のための電位自体を反転することが可能である。

## 【0008】

【発明の実施の形態】以下図面を用いて本発明の液晶表示装置における最適な実施形態を説明する。

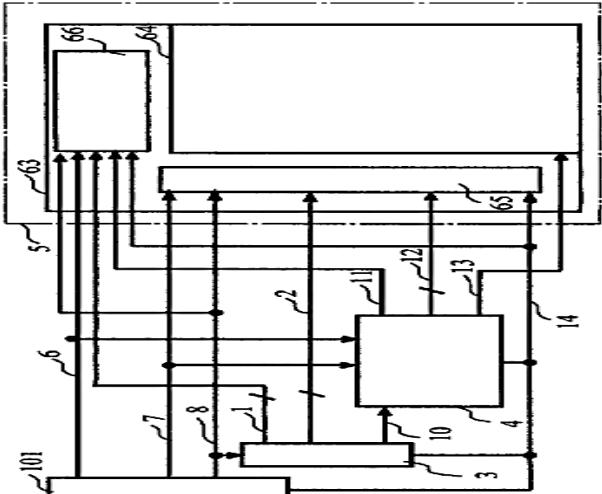

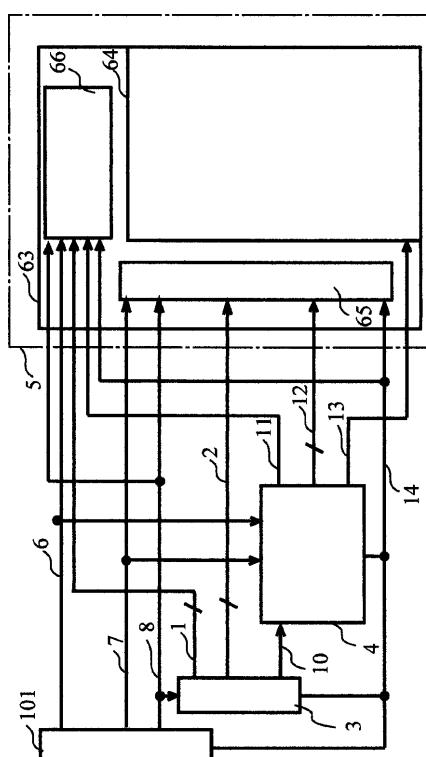

【0009】(実施の形態 1) 図 1 は本発明の実施の形態における液晶表示装置の回路ブロック示す図面である。図中、電源回路ブロック 101 は第 1 の電源 6、第 2 の電源 7 および第 3 の電源 8 を安定して発生する回路である。ロジック回路 3 は液晶表示装置 5 を駆動するための同期信号およびデータ信号であるデータロジック信号群 2 および走査ロジック信号群 1 を発生し、さらにコモン信号 10 を発生する。電位発生回路ブロック 4 は本発明の中心となる回路を含んでおり、コモン信号 10、第 1 の電源 6 および第 2 の電源 7 を入力し、第 4 の電源 11、階調電位群 12 およびコモン電源 13 を液晶表示装置 5 に出力する。

【0010】液晶表示装置 5 は薄膜トランジスタ (TFT) を形成した素子基板 63 と全面電極を形成した対抗基板 64 から構成され、前記素子基板にデータ用 IC 65 と走査用 IC 66 を搭載している。データ用 IC 65 は、GND14、第 2 の電源 7、第 3 の電源 8、データロジック信号群 2 および階調電位 12 を入力し、データを出力する。走査用 IC 66 は、GND14、第 1 の電源 6、第 3 の電源 8、走査ロジック信号群 1 および第 4 の電源 11 およびを入力して走査する。ここで、データ用 IC 65 の出力は階調電位 12 の電位変動に応じて反転する。

【0011】第 1 の電源 6 は 1.5 ボルト電位であり、走査 IC 65 に入力する。第 2 の電源 7 は 5 ボルト電位であり、データ用 IC 65 の出力電源である。第 3 の電源 8 は 3.3 ボルト電位であり、ロジック回路の駆動電源である。コモン電源 13 は対抗基板 64 に形成された全面電極に接続されている。

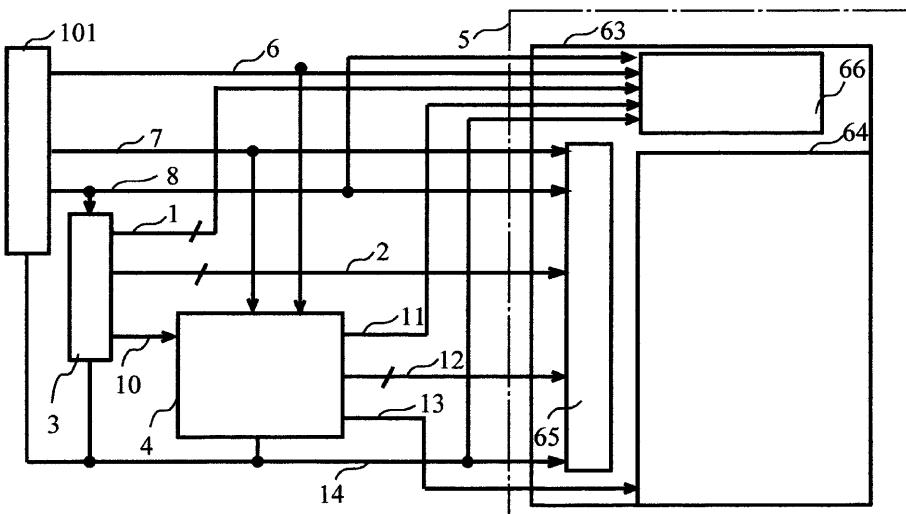

【0012】図 2 は電位発生回路ブロックの中身を示

す。図中コンデンサ32、第1の抵抗15および第2の抵抗16は、中央値1.65ボルトで振幅3.3ボルトのコモン信号10を中央値2.5ボルトで振幅3.3ボルトの信号にする目的で設けられている。第1のインバータ46、第2のインバータ27、第3のインバータ28、第4のインバータ29、第5のインバータ30および第6のインバータ31はロジック回路CMOSインバータ17(74HC04)に内蔵され第2の電源7で駆動される。第1のインバータ46の出力信号は第2のインバータ27および第6のインバータ31に入力される。第2のインバータの出力信号は第3のインバータ28および第4のインバータ29に入力される。第4のインバータの出力信号は第5のインバータ30に入力される。

【0013】次に図1で示した対向基板64に必要なコモン電源13の発生回路について説明する。図2中、第2のコンデンサ37は第6のインバータ31の出力の直流成分をカットする役目を果たし、第5のコンデンサ34はコモン電源13の電位安定化の役目を果たし、可変抵抗38は第3の電源8にクランプする役目を果たす。すなわち、コモン信号10と同位相の信号である5ボルト振幅の第6のインバータ31の第1の出力91の電位を、可変抵抗38によって調節する事ができるコモン電源13を発生する。ここで、クランプする電位を第3の電源8の電位とグランドの間の電位としたが、第3の電源の電位の代わりに第1の電源6の電位でも第2の電源7の電位でも良い。

【0014】次に図1で示した走査用IC66に必要な第4の電源11の発生について説明する。図2中、第6のコンデンサ39は第6のインバータ31の出力の直流成分をカットする役目を果たし、第3の抵抗40および第1のショットキーダイオード41はコンデンサ39を第1の電源6の電位にクランプする役目を果たす。p型モストランジスタ35およびn型モストランジスタは、それぞれ第4のインバータ29からの第2の出力92を1.5ボルトにクランプした信号と第4のインバータ29からの第2の出力をゲートに入力し、第1の電源電位(1.5ボルト)とグランド14間のレベルシフトされた出力をする。

【0015】第7のコンデンサ42はp型モストランジスタ35とn型モストランジスタ36のドレイン出力の直流成分をカットする役目を果たす。第2のショットキーダイオード43、第3のショットキーダイオード44および第8のコンデンサ45は、第7のコンデンサ42の直流成分をカットされた側の電位を第3の電源8の電位にクランプし整流する役目を果たす。結果、第4の電源として-11.1ボルト=-1.5ボルト(直流カットされた側の電位)+3.3ボルト(クランプ電位)+0.6ボルト(ショットキーダイオード2個分)が発生する。ここで、グランド14の(0ボルト電位)にクラ

ンプすれば-14.4ボルトが得られ、第2の電源7の電位(+5ボルト)にクランプすれば-9.4ボルトが得られる。このことにより、消費電力対策と駆動安定性のバランスに応じて電圧を選ぶことができる。

【0016】次に図1で示したデータ用IC65に必要な階調規定電位群12の発生について説明する。図2中、第0ビット電位20はコモン信号10と同位相の5ボルト振幅である第5のインバータ30からの第4の出力94であり、第3ビット電位21はコモン信号10と逆位相の5ボルト振幅である第3のインバータ28からの第3の出力93である。第1ビット電位19および第2ビット電位18は第4の抵抗22、第5の抵抗23および第6の抵抗24の割合によって規定される電位で出力される。

【0017】図3はコモン電源13と階調規定電位群12の出力信号の電位関係を説明するための詳細タイミングチャートを示す。図中、第1のタイミング57、第2のタイミング58および第3のタイミング59は走査走査線の選択切り替え時期を示す。コモン電源13は可変抵抗38によりオフセット調整された-0.5ボルトと+4.5ボルトの電位間の矩形波であり、第1のタイミング57で-0.5ボルトとなり、第2のタイミング58で+4.5ボルトとなり、第3のタイミングで-0.5ボルトとなる。

【0018】0ビット電位20のタイミングチャートである0ビット電位波形72は、0ボルトと+5.0ボルトの電位間の矩形波であり、第1のタイミング57で0ボルトとなり、第2のタイミング58で+5.0ボルトとなり、第3のタイミングで0ボルトとなる。1ビット電位19のタイミングチャートである1ビット電位波形73は、第4の抵抗22、第5の抵抗23および第6の抵抗24の割合で定まる+0.5ボルトと+4.5ボルト電位間の矩形波であり、第1のタイミング57で+0.5ボルトとなり、第2のタイミング58で+4.5ボルトとなり、第3のタイミングで0.5ボルトとなる。

【0019】2ビット電位18のタイミングチャートである2ビット電位波形74は、第4の抵抗22、第5の抵抗23および第6の抵抗24の割合で定まる+1.5ボルトと+3.5ボルト電位間の矩形波であり、第1のタイミング57で+3.5ボルトとなり、第2のタイミング58で+1.5ボルトとなり、第3のタイミングで3.5ボルトとなる。3ビット電位21の出力0ビット電位波形71は、0ボルトと+5.0ボルトの電位間の矩形波であり、第1のタイミング57で+5.0ボルトとなり、第2のタイミング58で0ボルトとなり、第3のタイミングで+5.0ボルトとなる。

【0020】本発明はロジック回路をインバータとしたが、NANDでもNOR等他のロジック回路でも同様である。また、本実施例ではCMOSトランジスタのロジ

ック回路としたが、TTLトランジスタでも同様である。階調規定電位群12の各ビット電位は本発明の電位に規定するものではない。また、本発明では第1の電源6から第4の電源11を発生したが、逆に第4の電源から第1の電源を発生することも可能である。

#### 【0021】

【発明の効果】以上の発明から明らかなように、本発明によれば、小型TFT型液晶表示装置に対して、ロジック回路用ICを用いてコモン電源、負電源、階調規定電位を発生することができるので、電源回路からの電源出力数を減らすことができ、小配線数で実装容積が少なく安価な液晶表示装置とすることが可能となる。

#### 【図面の簡単な説明】

【図1】本発明の実施の形態における液晶表示装置の回路構成を説明するためのブロック図面である。

#### 【図2】本発明の実施の形態における液晶表示装置の詳\*

\*細回路を説明するための図面である。

【図3】本発明の実施の形態における液晶表示装置のタイミングチャートを説明するための図面である。

【図4】従来の液晶表示装置の回路構成を説明するためのブロック図面である。

#### 【符号の説明】

- 4 : 電位発生回路ブロック

- 11 : 第4の電源

- 12 : 階調電位群

- 13 : コモン電源

- 17 : インバータ回路

- 38 : 可変抵抗

- 72 : 0ビット電位チャート

- 73 : 1ビット電位チャート

- 74 : 2ビット電位チャート

- 75 : 3ビット電位チャート

【図1】

【図2】

【図4】

フロントページの続き

(51) Int.CI.<sup>7</sup>

G 0 9 G 3/20

6 2 4

識別記号

G 0 9 G 3/20

6 2 4

F I

G 0 9 G 3/20

テ-マコ-ト<sup>®</sup> (参考)

6 1 2 F

6 2 4 C

(72)発明者 関口 金孝

東京都西東京市田無町六丁目1番12号 シ

チズン時計株式会社内

F ターム(参考) 2H093 NA16 NA51 NC03 NC05 NC09

NC11 NC34 ND42 NG20

5C006 AC26 BC03 BC06 BC11 BF43

BF46 FA41 FA45

5C080 AA10 BB05 DD22 DD27 DD28

FF03 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2003280608A</a>                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2003-10-02 |

| 申请号            | JP2002084643                                                                                                                                                                                                                                                                                                                              | 申请日     | 2002-03-26 |

| [标]申请(专利权)人(译) | 西铁城控股株式会社                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 西铁城钟表有限公司                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 矢野敬和<br>高橋和壽<br>宮部光正<br>関口金孝                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 矢野 敬和<br>▲高▼橋 和壽<br>宮部 光正<br>関口 金孝                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                               |         |            |

| F1分类号          | G09G3/36 G02F1/133.520 G02F1/133.550 G09G3/20.612.D G09G3/20.612.E G09G3/20.612.F G09G3/20.624.C                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA51 2H093/NC03 2H093/NC05 2H093/NC09 2H093/NC11 2H093/NC34 2H093/ND42 2H093/NG20 5C006/AC26 5C006/BC03 5C006/BC06 5C006/BC11 5C006/BF43 5C006/BF46 5C006/FA41 5C006/FA45 5C080/AA10 5C080/BB05 5C080/DD22 5C080/DD27 5C080/DD28 5C080/FF03 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 2H193/ZA04 2H193/ZD21 2H193/ZF03 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                 |         |            |

## 摘要(译)

需要具有各种电位的电源来驱动TFT型液晶显示装置。迄今为止，在大型的液晶显示装置中，由于需要面积引起的电流，因此从电源电路产生上述电位的电源。如果将该电路原样应用于小型液晶显示装置，则可以容易且可靠地进行驱动，但是在安装数量和价格上与大型液晶显示装置相同。为了解决上述问题，采用可以由5伏特驱动的逻辑通用IC作为公共电源，当从高电位电源向低电源产生电源时，该IC用于电平转换。该电势通过反相的输出之间的多个电阻器容易产生不同电势的信号。