# (19)日本国特許庁(JP) (12) **公 開 特 許 公 報**(A) (11)特許出願公開番号

特開2003 - 208135

(P2003 - 208135A)

(43)公開日 平成15年7月25日(2003.7.25)

| (51) Int .CI <sup>7</sup> | 識別記号 | FI                | テーマコード(参考)  |

|---------------------------|------|-------------------|-------------|

| G 0 9 G 3/36              |      | G 0 9 G 3/36      | 2 H O 9 3   |

| G 0 2 F 1/133             | 550  | G 0 2 F 1/133 550 | 5 C O O 6   |

| G 0 9 G 3/20              | 621  | G 0 9 G 3/20 621  | M 5 C 0 8 0 |

|                           | 623  | 623               | F           |

|                           |      | 623               | G           |

審査請求 未請求 請求項の数 110 L (全 11数) 最終頁に続く

(21)出願番号 特願2002 - 178008(P2002 - 178008)

(22)出願日 平成14年6月19日(2002.6.19)

(31)優先権主張番号 2002 - 2090

平成14年1月14日(2002.1.14) (32)優先日

(33)優先権主張国 韓国(KR)

(71)出願人 599127667

エルジー フィリップス エルシーディー

カンパニー リミテッド

大韓民国 ソウル、 ヨンドンポーク、 ヨ

イドードン 20

リー、 ソク ウー (72)発明者

大韓民国 ソウル, グロ-ク, オリュー

1 - ドン 338号

(74)代理人 100109726

弁理士 園田 吉隆 (外1名)

最終頁に続く

# (54) 【発明の名称】 液晶表示装置のデータ駆動装置及び方法

# (57)【要約】

【目的】本発明はDAC部を時分割駆動して既存のチッ プ面積と比較して大きくチップ面積を増加させないか、 むしろチップ面積を減少させながらデータ駆動ICの出 カチャネル数を増加させることでデータ駆動IC及びT C Pの数を減らすことができる液晶表示装置のデータ駆 動装置及び方法を提供する。

【解決手段】本発明は、入力された画素データを時分割 して供給するためのマルチプレクサ部と:マルチプレク サ部からの画素データを画素電圧信号に変換するための デジタル・アナログ変換部と:デジタルーアナログ変換 部からの画素電圧信号を複数の出力ラインに選択的に供 給するためのディマルチプレクサ部と;ディマルチプレ クサ部からの画素電圧信号をサンプリング及びホールデ ィングして複数のデータラインに出力するためのサンプ リング及びホールディング部とを具備することを特徴と する。

# 【特許請求の範囲】

【請求項1】 入力された画素データを時分割して供給するためのマルチプレクサ部と、

1

前記マルチプレクサ部からの画素データを画素電圧信号 に変換するためのデジタル・アナログ変換部と、

前記デジタル・アナログ変換部からの画素電圧信号を複数の出力ラインに選択的に供給するためのディマルチプレクサ部と、

前記ディマルチプレクサ部からの画素電圧信号をサンプ ンプリング及びホルタリング及びホールディングして複数のデータラインに出 10 ホルダのそれぞれは、力するためのサンプリング及びホールディング部とを具 前記ディマルチプレク備することを特徴とする液晶表示装置のデータ駆動装 列に接続される第1万置。 グ素子と、

【請求項2】 前記マルチプレクサ部は、少なくとも2 n/3個のマルチプレクサを具備して少なくとも2 n個の画素データを少なくとも2 n/3個ずつ時分割して供給するマルチプレクサ・アレイであり、

前記デジタル・アナログ変換部は、前記少なくとも2n 第1及び第2ホール / 3個のデジタル・アナログ変換器を具備して前記少な 備することを特徴とくとも2n/3個の画素データを画素電圧信号に変換す 20 のデータ駆動装置。るデジタル・アナログ変換アレイであり、 【請求項7】 前記

前記ディマルチプレクサは、少なくとも2n/3個のディマルチプレクサを具備して前記少なくとも2n/3個ずつの画素電圧信号を少なくとも2n個の出力ラインに選択的に供給するディマルチプレクサ・アレイであることを特徴とする請求項1に記載の液晶表示装置のデータ駆動装置。

【請求項3】 サンプリング信号を順次発生するためのシフトレジスタ部と、

前記サンプリング信号に応じて前記少なくとも 2 n 個の 30 画素データを所定の単位ずつ順次ラッチして前記マルチプレクサ部に同時に出力するためのラッチ部と、

前記サンプリング及びホールディング部からの画素電圧 信号をバッファして前記複数のデータラインに出力する ためのバッファ部とを更に具備することを特徴とする請 求項2に記載の液晶表示装置のデータ駆動装置。

【請求項4】 前記デジタル・アナログ変換器はそれぞれ。

前記画素データを正極性の画素電圧信号に変換するため の正極性部と、

負極性の画素電圧信号に変換するための負極性部と、 正極性部及び負極性部の出力を選択するマルチプレクサ とを具備することを特徴とする請求項2に記載の液晶表 示装置のデータ駆動装置。

【請求項5】 前記マルチプレクサはそれぞれ、

第1乃至第3スイッチング制御素子のそれぞれに応じて 少なくとも3個の画素データを1つのデジタル・アナロ グ変換器に時分割して供給するための第1乃至第3スイ ッチング素子を具備し、

前記ディマルチプレクサはそれぞれ、前記第1乃至第3 50 前記マルチプレクサ部に同時に供給する段階と、

スイッチング制御信号のそれぞれに応じて前記デジタル・アナログ変換器からの画素電圧信号を少なくとも3個の出力ラインに選択的に供給するための第4乃至第6スイッチング素子を具備することを特徴とする請求項2に記載の液晶表示装置のデータ駆動装置。

【請求項6】 前記サンプリング及びホールディング部は、前記ディマルチプレクサ部の少なくとも2 n個の出力ラインのそれぞれに接続された少なくとも2 n個のサンプリング及びホルダを具備し、前記サンプリング及びホルダのそれぞれは、

前記ディマルチプレクサ部の出力ラインのそれぞれに並列に接続される第1及び第2サンプリング・スイッチング素子と、

前記サンプリング・スイッチング素子を経由した画素電 圧信号を充電するための第1及び第2キャパシタと、

前記第1及び第2キャパシタに充電された画素電圧信号をホールディングした後、前記データラインに放電する第1及び第2ホールディング・スイッチング素子とを具備することを特徴とする請求項2に記載の液晶表示装置のデータ駆動装置。

【請求項7】 前記第1キャパシタに充電される画素電圧信号をサンプリングする第1サンプリング・スイッチング素子と、前記第2キャパシタに充電された画素電圧信号をホールディング及び放電する第2ホールディング・スイッチング素子は、同一の第1スイッチング制御信号によって駆動され、

前記第2キャパシタに充電される画素電圧信号をサンプリングする第2サンプリング・スイッチング素子と、前記第1キャパシタに充電された画素電圧信号をホールディング及び放電する第1ホールディング・スイッチング素子は、前記第1スイッチング制御信号と論理状態が反転した同一の第2スイッチング制御信号によって駆動されることを特徴とする、請求項6に記載の液晶表示装置のデータ駆動装置。

【請求項8】 マルチプレクサ部で入力された画素データを時分割して供給する段階と、

デジタル・アナログ変換部で前記マルチプレクサ部から の画素データを画素電圧信号に変換する段階と、

ディマルチプレクサ部で前記デジタル・アナログ変換部 40 からの画素電圧信号を複数の出力ラインに選択的に供給 する段階と、

サンプリング及びホールディング部で前記ディマルチプレクサ部からの画素電圧信号をサンプリング及びホールディングして複数のデータラインに出力する段階を含むことを特徴とする液晶表示装置のデータ駆動方法。

【請求項9】 シフトレジスタ部でサンプリング信号を順次発生する段階と、

前記サンプリング及びホールディング部で出力される前 記画素電圧信号をバッファし、前記少なくとも2 n 個の データラインに供給する段階を更に含むことを特徴とす る請求項8に記載の液晶表示装置のデータ駆動方法。

【請求項10】 前記マルチプレクサ部で前記画素デー タを時分割する段階は、第1乃至第3スイッチング制御 信号に応じて少なくとも2n個の画素データを少なくと も3区間に時分割して供給する段階であり、前記ディマ ルチプレクサ部で前記画素電圧信号を複数の出力ライン に選択的に供給する段階は、前記第1乃至第3スイッチ 10 ング制御信号に応じて前記画素電圧信号のそれぞれを少 なくとも3個の出力ラインに選択的に供給する段階であ ることを特徴とする、請求項8に記載の液晶表示装置の データ駆動方法。

【請求項11】 前記サンプリング及びホールディング 部に含まれるサンプリング及びホルダのそれぞれが、第 1及び第2サンプリング・スイッチング素子と、第1及 び第2キャパシタと、第1及び第2ホールディング・ス イッチング素子とを具備し、

前記サンプリング及びホールディング部で画素電圧信号 20 ライバは多数個の集積回路(以下、ICという)に集積 をサンプリング及びホールディングする段階は、

任意の水平期間で前記第1サンプリング・スイッチング 素子が前記マルチプレクサ部からの画素電圧信号をサン プリングして前記第1キャパシタに充電にすると共に、 同時に前記第2ホールディング・スイッチング素子が前 記第2キャパシタに充電される前の水平期間の画素電圧 信号を対応するデータラインに放電する段階と、

次の水平期間で前記第2サンプリング・スイッチング素 子が前記ディマルチプレクサ部からの画素電圧信号をサ ンプリングして前記第2キャパシタに充電すると共に、30 同時に前記第1ホールディング・スイッチング素子が前 記第1キャパシタに充電される前の水平期間の画素電圧 信号を対応するデータラインに放電する段階とを含むこ とを特徴とする、請求項8に記載の液晶表示装置のデー タ駆動方法。

#### 【発明の詳細な説明】

# [0001]

【発明の属する技術分野】本発明は液晶表示装置に関す るもので、特にデジタル・アナログ変換部を時分割駆動 してデータ駆動集積回路とテープ・キャリア・パッケー 40 ジの数を減らすことができる液晶表示装置のデータ駆動 装置及び方法に関するものである。

#### [0002]

【従来の技術】通常の液晶表示装置は電界を利用して液 晶の光透過率を調節することで画像を表示する。このた めに、液晶表示装置は液晶セルがマトリックス状に配列 された液晶パネルと、この液晶パネルを駆動するための 駆動回路とを具備する。液晶パネルにはそれぞれ複数の ゲートラインとデータラインが交差して配列されて、そ の交差部に設けられる領域に液晶セルが配設される。こ 50 8)と、DAC(18)からの画素電圧信号を緩衝して

の液晶パネルには液晶セルのそれぞれに電界を印加する ための複数の画素電極と共通電極が設けられる。画素電 極のそれぞれはスイッチング素子である薄膜トランジス タのソース及びドレーン端子を経由してデータラインの いずれか1つに接続される。薄膜トランジスタのゲート 端子は、画素電圧信号を1ライン分ずつの画素電極に印 加するゲートラインの中のいずれか1つに接続される。 駆動回路はゲートラインを駆動するためのゲートドライ バと、データラインを駆動するためのデータドライバ と、共通電極を駆動するための共通電圧発生部とを具備 する。ゲートドライバはスキャニング信号をゲートライ ンに順次供給し、液晶パネルの上の液晶セルを 1 ライン 分ずつ順次駆動する。データドライバはゲートラインの いずれか1つにゲート信号が供給される毎にデータライ ンのそれぞれに画素電圧信号を供給する。共通電圧発生 部は共通電極に共通電圧信号を供給する。これにより、 液晶表示装置は、液晶セル別に画素電圧信号が画素電極 と共通電極の間に印加した電界により、光透過率を調節 することで画像を表示する。データドライバとゲートド 化される。集積化されたデータドライバICとゲートド ライバICのそれぞれはテープ・キャリア・パッケージ (以下、TCPという)に実装されて、タブ(TAB: Tape Automated Bonding)方式で液晶パネルに接続され るか、CGO(Chip On Glass)方式で液晶パネル上に 実装される。

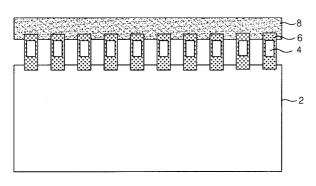

【0003】図1は従来の液晶表示パネル装置を概念的 に図示しており、データTCP(6)を通して液晶パネ ル(2)に接続された複数のデータ駆動IC(4)と、 TCP(6)を通してデータ駆動IC(4)に接続され たデータ印刷回路基板(以下、PCBという)(8)と を具備する。

【0004】データPCB(8)は、タイミング制御部 (図示しない)から供給される各種の制御信号及びデー タ信号とパワー部 (図示しない)からの駆動電圧信号を 入力してデータ駆動IC(4)に中継する役割を有す る。TCP(6)は液晶パネル(2)の上段部に設けら れたデータパッドに電気的に接続されると共に、データ PCB(8)に設けられた出力パッドに電気的に接続さ れる。データ駆動IC(4)はデジタル信号である画素 データ信号を、アナログ信号である画素電圧信号に変換 して液晶パネル(2)上のデータラインに供給する。

【0005】このために、データ駆動IC(4)のそれ ぞれは、図2に図示されるように、サンプリング信号が 順次供給されるシフトレジスタ部(14)と、サンプリ ング信号に応じて画素データ(VD)を順次ラッチし、 同時に出力するラッチ部(16)と、ラッチ部(16) からの画素データ(VD)を画素電圧信号に変換するデ ジタル・アナログ変換部(以下、DAC部という)(1

出力する出力バッファ部(26)とを具備する。また、 データ駆動IC(4)は、タイミング制御部(図示しな い)から供給される各種の制御信号と画素データ(V D)を中継する信号制御部(10)と、DAC部(1 8)で必要とする正極性及び負極性ガンマ電圧を供給す るガンマ電圧部(12)とを更に具備する。このような 構成を有するデータ駆動IC(4)のそれぞれは、n個 ずつのデータライン(DL1乃至DLn)を駆動する。 【0006】信号制御部(10)は、タイミング制御部 (図示しない)からの各種の制御信号(SSC、SS P、SOE、POLなど)と画素データ(VD)が各構 成要素に出力されるように制御する。

【0007】ガンマ電圧部(12)は、ガンマ基準電圧 発生部(図示しない)から入力される複数のガンマ基準 電圧をグレイ別に細分化して出力する。

【0008】シフトレジスタ部(14)に含まれるn/ 6個のシフトレジスタは、信号制御部(10)からのソ ース・スタート・パルス(SSP)をソース・サンプリ ング・クロック信号(SSC)により順次シフトさせ、 サンプリング信号として出力する。

【0009】ラッチ部(16)は、シフトレジスタ部 (14)からのサンプリング信号に応じて信号制御部 (10)からの画素データ(VD)を一定の単位ずつ順 次サンプリングしてラッチする。このために、ラッチ部 はn個の画素データ(VD)をラッチするためのn個の ラッチで構成されており、該ラッチのそれぞれは画素デ -タ(VD)のビット数(3ビットまたは6ビット)に 対応する大きさを有する。特にタイミング制御部(図示 しない)は、伝送周波数を減らすため、画素データ(V D)を偶数画素データと奇数画素データに分けて伝送ラ 30 インを通して同時に出力する。ここで、偶数画素データ と奇数画素データのそれぞれは、赤(R)、緑(G)、 青(B)の画素データを含む。これによりラッチ部(1 6)は、サンプリング信号毎に信号制御部(10)を経 由して供給される偶数画素データと奇数画素データ、即 ち6個の画素データを同時にラッチする。続いて、ラッ チ部(16)は信号制御部(10)からのソース出力イ ネーブル信号(SOE)に応じてラッチされた n 個の画 素データ(VD)を同時に出力する。この場合、ラッチ 部(16)はデータ反転選択信号(REV)に応じてト 40 らない。このために、データ駆動ICの構成が複雑にな ランジション・ビット数を減らすように修正された画素 データ(VD)を復元させ出力する。これは、タイミン グ制御部におけるデータ伝送の際の電気的な干渉(EM I)を最小化するために、トランジションされるビット 数が基準値を超えないようトランジション・ビット数を 減らすように画素データ(VD)を修正して供給するた めである。

【0010】DAC部(18)はラッチ部(16)から の画素データ(VD)を同時に正極性及び負極性の画素 電圧信号に変換して出力する。このために、DAC部

(18)はラッチ部(16)に共通接続されたP(Posi tive) デコーディング部(20)及びN(Negative) デ コーディング部(22)と、Pデコーディング部(2 0)及びNデコーディング部(22)の出力信号を選択 するためのマルチプレクサ(MUX;24)とを具備す る。

【0011】Pデコーディング部(20)に含まれるn 個のPデコーダは、ラッチ部(16)から同時に入力さ れるn個の画素データを、ガンマ電圧部(12)からの 10 正極性のガンマ電圧を利用して、正極性の画素電圧信号 に変換する。Nデコーディング部(22)に含まれるn 個のNデコーダは、ラッチ部(16)から同時に入力さ れるn個の画素データを、ガンマ電圧部(12)からの 負極性のガンマ電圧を利用して、負極性の画素電圧信号 に変換する。マルチプレクサ(24)は信号制御部(1 0)からの極性の制御信号(POL)に応じてPデコー ダ(20)からの正極性の画素電圧信号またはNデコー ダ(22)からの負極性の画素電圧信号を選択して出力

20 【0012】出力バッファ部(26)に含まれるn個の 出力バッファは、n個のデータライン(DL1乃至DL n)にそれぞれ直列に接続されて電圧追従機を構成す る。このような出力バッファはDAC部(18)からの 画素電圧信号を信号緩衝し、データライン(DL1乃至 DLn)に供給する。

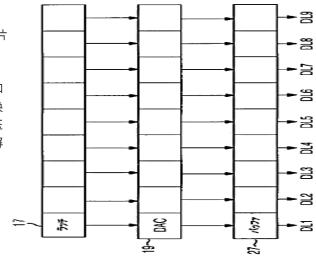

【 0 0 1 3 】図 3 は、図 2 に図示されたデータ駆動 I C (4)内の一部の画素データの伝送経路を具体的に図示 している。

【0014】図3でラッチ部(16)のラッチ(17) は9個の画素データをDAC部(18)を構成する9個 のDAC(デジタル・アナログ変換器)(19)のそれ ぞれに出力して画素電圧信号に変換する。画素電圧信号 は出力バッファ部(26)のバッファ(27)を通して 第1乃至第9データライン(DL1乃至DL9)のそれ ぞれに供給される。

【0015】このように、従来のデータ駆動ICのそれ ぞれは、n個のデータライン(DL1乃至DLn)を駆 動するためにPデコーダ及びNデコーダとマルチプレク サのそれぞれを含むn個のDACとを具備しなければな り、製造単価が相対的に高くなる。したがって、液晶表 示装置の製造費用を節減するためにデータ駆動ICの数 を減らすことが要求される。

【0016】データ駆動ICの数を減らす方法にデータ 駆動ICが駆動することができるデータラインの数、即 ち出力チャネル数を増加させる方法が検討されている。 しかし、データ駆動ICの駆動チャネル数を増加させる 場合、複雑な構成のDAC数が増加するので、チップ面 積が増大することにより面積に比例してTCPの費用が 50 上昇するだけでなく、集積化が難しく、製造費用及び不

する。

7

良率の上昇などの問題点を生じる。

#### [0017]

【発明が解決しようとする課題】従って、本発明の目的は、DAC部を時分割駆動し、既存のチップ面積と比較して大きくチップ面積を増加させないか、むしろチップ面積を減少させながらデータ駆動ICの出力チャネル数を増加させることで、データ駆動IC及びTCPの数を減らすことができる液晶表示装置のデータ駆動装置及び方法を提供することである。

# [0018]

【課題を解決するための手段】前記目的を達成するために、本発明による液晶表示装置のデータ駆動装置は、入力された画素データを時分割して供給するためのマルチプレクサ部と、マルチプレクサ部からの画素データを画素電圧信号に変換するためのデジタル・アナログ変換部と、デジタル・アナログ変換部からの画素電圧信号を多数の出力ラインに選択的に供給するためのディマルチプレクサ部と、ディマルチプレクサ部からの画素電圧信号をサンプリング及びホールディングして複数のデータラインに出力するためのサンプリング及びホールディング 20とを具備することを特徴とする。

【 0 0 1 9 】ここで、第 1 マルチプレクサ・アレイは、少なくとも 2 n / 3 個のマルチプレクサを具備し、少なくとも 2 n / 3 個ずつ時分割して供給し、デジタル・アナログ変換のアレイは、少なくとも 2 n / 3 個のデジタル・アナログ変換器と、少なくとも 2 n / 3 個の画素データを画素電圧信号に変換するための前記少なくとも 2 n / 3 個のデジタル・アナログ変換器を具備し、ディマルチプレクサ・アレイは少なくとも 2 n / 3 個のディマルチプレクサを具備 30 して少なくとも 2 n / 3 個ずつの画素電圧信号を少なくとも 2 n 個以上の出力ラインに選択的に供給することを特徴とする。

【0020】また、本発明の液晶表示装置のデータ駆動装置は、サンプリング信号を順次発生するためのシフト・レジスタ部と、サンプリング信号に応じて少なくとも2n個以上の画素データを所定の単位ずつ順次ラッチしてマルチプレクサ部に同時に出力するためのラッチ部と、サンプリング及びホールディング部からの画素電圧信号をバッファして複数のデータラインに出力するため40のバッファ部とを更に具備することを特徴とする。

【0021】また、デジタル・アナログ変換器のそれぞれは、画素データを正極性の画素電圧信号に変換するための正極性部と、負極性の画素電圧信号に変換するための負極性部と、正極性部及び負極性部の出力を選択するマルチプレクサとを具備することを特徴とする。

【0022】特に、マルチプレクサのそれぞれは、第1 乃至第3スイッチング制御素子のそれぞれに応じて少なくとも3個の画素データを1つのデジタル・アナログ変 物器に時分割して供給するための第1乃至第3スイッチ ング素子を具備し、ディマルチプレクサのそれぞれは、前記第1乃至第3スイッチング制御信号のそれぞれに応じてデジタル・アナログ変換器からの画素電圧信号を、少なくとも3個の出力ラインに選択的に供給するための第4乃至第6スイッチング素子を具備することを特徴と

【0023】サンプリング及びホールディング部はディマルチプレクサ部の少なくとも2n個の出力ラインのそれぞれに接続される少なくとも2n個のサンプリング及びホルダとを具備し、サンプリング及びホルダのそれぞれは前記ディマルチプレクサ部の出力ラインのそれぞれに並列に接続される第1及び第2サンプリング・スイッチング素子と、サンプリング・スイッチング素子を経由した画素電圧信号を充電するための第1及び第2キャパシタと、第1及び第2キャパシタに充電された画素電圧信号がホールディングされるようにした後、データラインに放電されるようにする第1及び第2ホールディング・スイッチング素子とを具備することを特徴とする。

【0024】ここで、第1キャパシタに充電される画素電圧信号をサンプリングする第1サンプリング・スイッチング素子と、第2キャパシタに充電された画素電圧信号をホールディング及び放電させる第2ホールディング・スイッチング素子は、同一の第1スイッチング制御信号に応じて駆動され、第2キャパシタに充電される画素電圧信号をサンプリングする第2サンプリング・スイッチング素子と、第1キャパシタに充電された画素電圧信号をホールディング及び放電させる第1ホールディング・スイッチング素子は、第1スイッチング制御信号と論理状態を反転する同一の第2スイッチング制御信号に応じて駆動されることを特徴とする。

【0025】本発明による液晶表示装置のデータ駆動方法は、マルチプレクサ部で入力された画素データを時分割して供給する段階と、デジタル・アナログ変換部でマルチプレクサ部からの画素で一タを画素電圧信号に変換する段階と、ディマルチプレクサ部でデジタル・アナログ変換部からの画素電圧信号を多数の出力ラインに選択的に供給する段階と、サンプリング及びホールディング部でディマルチプレクサ部からの画素電圧信号をサンプリング及びホールディングして複数のデータラインに出力する段階を含むことを特徴とする。

【0026】また、本発明の液晶表示装置のデータ駆動方法は、シフトレジスタ部でサンプリング信号を順次発生する段階と、ラッチ部でサンプリング信号に応じて少なくとも2n個の画素データを所定の単位ずつ順次ラッチし、マルチプレクサ部に同時に供給する段階と、サンプリング及びホールディング部で出力される画素電圧信号をバッファして少なくとも2n個のデータラインに供給する段階を更に含むことを特徴とする。

くとも3個の画素データを1つのデジタル・アナログ変 【0027】そして、マルチプレクサ部で画素データを 換器に時分割して供給するための第1乃至第3スイッチ50 時分割する段階は、第1乃至第3スイッチング制御信号

8

に応じて少なくとも2n個の画素データを少なくとも3 区間に時分割して供給する段階であり、ディマルチプレ クサ部で画素電圧信号を複数の出力ラインに選択的に供 給する段階は、第1乃至第3スイッチング制御信号に応 じて画素電圧信号のそれぞれを少なくとも3個の出力ラ インに選択的に供給する段階であることを特徴とする。 【0028】また、サンプリング及びホールディング部 に含まれるサンプリング及びホルダのそれぞれが、第1 及び第2サンプリング・スイッチング素子と、第1及び 第2キャパシタと、第1及び第2ホールディング・スイ 10 ッチング素子とを具備し、サンプリング及びホールディ ング部で画素電圧信号をサンプリング及びホールディン グされるようにする段階は、任意の水平期間で第1サン プリング・スイッチング素子がマルチプレクサ部からの 画素電圧信号をサンプリングし、第1キャパシタに充電 されるようにすると共に、同時に第2ホールディング・ スイッチング素子が前記第2キャパシタに充電される前 の水平期間の画素電圧信号を対応するデータラインに放 電されるようにする段階と、次の水平期間で第2サンプ リング・スイッチング素子が前記ディマルチプレクサ部 20 からの画素電圧信号をサンプリングし、第2キャパシタ に充電されるようにすると共に、同時に第1ホールディ ング・スイッチング素子が前記第1キャパシタに充電さ れる前の水平期間の画素電圧信号を対応するデータライ ンに放電されるようにする段階を含むことを特徴とす る。

9

# [0029]

【作用】本発明による液晶表示装置のデータ駆動装置及 び方法は、DAC部を時分割駆動することで、既存のチ ップ面積に比較して大きくチップ面積を増加させない か、むしろチップ面積を減少させながらデータ駆動IC の出力のチャネル数を従来対比 2 倍に増加させることが できる。これにより、本発明による液晶表示装置のデー 夕駆動装置及び方法によると、データ駆動ICのチャネ ル数を増加させ、データ駆動IC及びTCPの数を従来 比1/2に減らすことができるので、液晶表示装置の製 造費用を低くすることができる。

# [0030]

【発明の実施態様】以下、図4乃至図8を参照して本発 明の好ましい実施例に対して説明する。

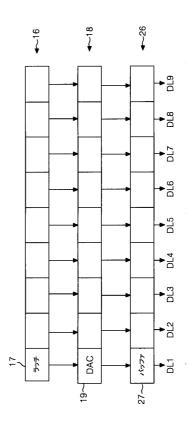

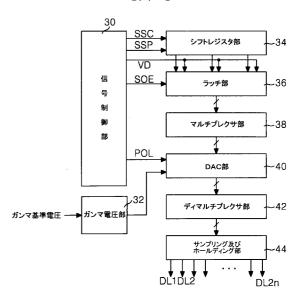

【0031】図4は本発明の実施例によるLCDのデー タ駆動装置を図示したブロック図である。

【0032】図4に図示されたLCDのデータ駆動装置 は、順次サンプリング信号を供給するシフト・レジスタ 部(34)と、サンプリング信号に応答して画素データ (VD)を順次ラッチして同時に出力するラッチ部(3) 6)と、ラッチ部(36)からの画素データ(VD)を 時分割して供給するマルチプレクサ部(38)と、マル チプレクサ部(38)からの画素データ信号(VD)を 画素電圧信号に変換するDAC部(40)と、出力ライ 50 マルチプレクサ(46)を具備する。マルチプレクサ

ンを時分割駆動してDAC(40)からの画素電圧信号 を供給するディマルチプレクサ部(42)と、ディマル チプレクサ部(42)から入力される画素電圧信号をサ ンプリング及びホールディングしてデータライン(DL 1乃至 D L 2 n ) に同時に供給するサンプリング及びホ ールディング部(44)とを具備する。また、データ駆 動装置はタイミング制御部(図示しない)から供給され る制御信号と画素データ(VD)を中継する信号制御部 (30)と、DAC部(40)で必要とする正極性及び 負極性のガンマ電圧を供給するガンマ電圧部(32)と を更に具備する。このような構成を有するデータ駆動装 置は、1つのデータ駆動ICに集積化されて従来のデー タ駆動ICと比較して2倍に増加された2n個のデータ ライン(DL1乃至DL2n)を駆動する。

【0033】信号制御部(30)は、タイミング制御部 (図示しない)からの各種の制御信号(SSC、SS P、SOE、POLなど)と、画素データ(VD)が対 応する構成要素などに出力されるように制御する。

【0034】ガンマ電圧部(32)は、ガンマ基準電圧 発生部(図示しない)から入力される複数個のガンマ基 準電圧をグレイ別に細分化して出力する。

【0035】シフトレジスタ部(34)に含まれるシフ トレジスタは、信号制御部(30)からのソース・スタ ート・パルス(SSP)をソース・サンプリング・クロ ック信号(SSC)により順次シフトさせ、サンプリン グ信号に出力する。

【0036】ラッチ部(36)は、シフトレジスタ部 (34)からのサンプリング信号に応じて信号制御部 (30)からの画素データ(VD)を一定の単位ずつ順 30 次サンプリングしてラッチする。このためにラッチ部 (36)は、図5に図示したように、2n個の画素デー タ(VD)をラッチするために2n個のラッチ(46) に構成され、該ラッチ(46)のそれぞれは画素データ (VD)のビット数(3ビットまたは6ビット)に対応 する大きさを有する。このようなラッチ部(36)はサ ンプリング信号毎に信号制御部(30)を経由して供給 される偶数画素データと奇数画素データ、即ち6個の画 素データを同時にラッチする。続いてラッチ部(36) は、信号制御部(30)からのソース出力イネーブル信 40 号(SOE)に応じてラッチされた2n個の画素データ (VD)を同時に出力する。この場合、ラッチ部(3) 6)はデータ反転選択信号(REV)に応じてトランジ ション・ビット数が減少するように修正された画素デー タ(VD)を復元させ出力する。

【0037】マルチプレクサ部(36)はラッチ部(3 6)から入力される2n個の画素データを時分割して出 力する。この2n個の画素データを3区間に時分割する 場合、マルチプレクサ部(36)は図5に図示したよう に3個ずつのラッチ(46)に接続された2n/3個の

(46)のそれぞれは、3個ずつのラッチ(46)から 入力された画素データを時分割し、1つの出力ラインに 順次供給する。さらに詳細には、マルチプレクサ部(3 6) はラッチ部(36) から入力される2n個の画素デ ータを 2 n / 3 個ずつ時分割して D A C 部 (40) に出 力する。

11

【0038】DAC部(40)はマルチプレクサ部(3 8)から入力される画素データを正極性及び負極性の画 素電圧信号に変換し、極性制御信号(POL)に応じて 正極性及び負極性の画素電圧信号を選択的に出力する。 このために、DAC部(40)は、図5に図示したよう に、マルチプレクサ(48)のような2n/3個のDA C(50)を具備する。DAC(50)のそれぞれは、 マルチプレクサ(48)に共通接続されたPデコーダ及 びNデコーダと、Pデコーダ及びNデコーダの出力信号 を選択するためのマルチプレクサとを具備する。Pデコ ーダは画素データをガンマ電圧部(34)からの正極性 のガンマ電圧を利用して正極性の画素電圧信号に変換す る。Nデコーダは画素データをガンマ電圧部(34)か らの負極性のガンマ電圧を利用して負極性の画素電圧信 20 号に変換する。マルチプレクサは信号制御部(32)か らの極性制御信号(POL)に応じて正極性の画素電圧 信号又は負極性の画素電圧信号を選択して出力する。

【0039】ディマルチプレクサ部(42)は出力ライ ンを時分割駆動してDAC部(40)からの画素電圧信 号を選択的に供給する。このために、ディマルチプレク サ部(42)は、図5に図示したように、DAC(5 0)と同様にの2n/3個のディマルチプレクサ(5 2)を具備する。ディマルチプレクサ(52)のそれぞ れは、3個の出力ラインを時分割駆動してDAC(5 0)から供給される画素電圧信号を選択的に供給する。 さらに詳細には、ディマルチプレクサ部(42)はDA C(40)から入力される2n/3個づつの画素電圧信 号を異なる出力ラインに順次サンプリング及びホールデ ィング部(44)に出力する。

【0040】サンプリング及びホールディング部(4 4)は、ディマルチプレクサ部(42)から入力される 画素電圧信号をサンプリングしてホールディングした 後、データライン(DL1乃至DL2n)に同時に出力 する。このために、サンプリング及びホールディング部 40 に、ディマルチプレクサ(52)は入力ラインが1つの (44)は、図5に図示されたように、データライン (DL1乃至DL2n)と同一の2n個のサンプリング 及びホルダ(54)を具備する。サンプリング及びホル ダ(54)のそれぞれは、ディマルチプレクサ(52) から時間差を置いて入力される画素電圧信号をサンプリ ングしてホールディングした後、データライン(DL1 乃至DL2n)のそれぞれに同時に出力する。さらに詳 細には、サンプリング及びホールディング部(44)は ディマルチプレクサ部(42)から2n/3個ずつ入力

した後、2 n個の画素電圧信号がすべてサンプリングさ れると画素電圧信号などを第1乃至第2nデータライン (DL1乃至DL2 n)に同時に出力する。

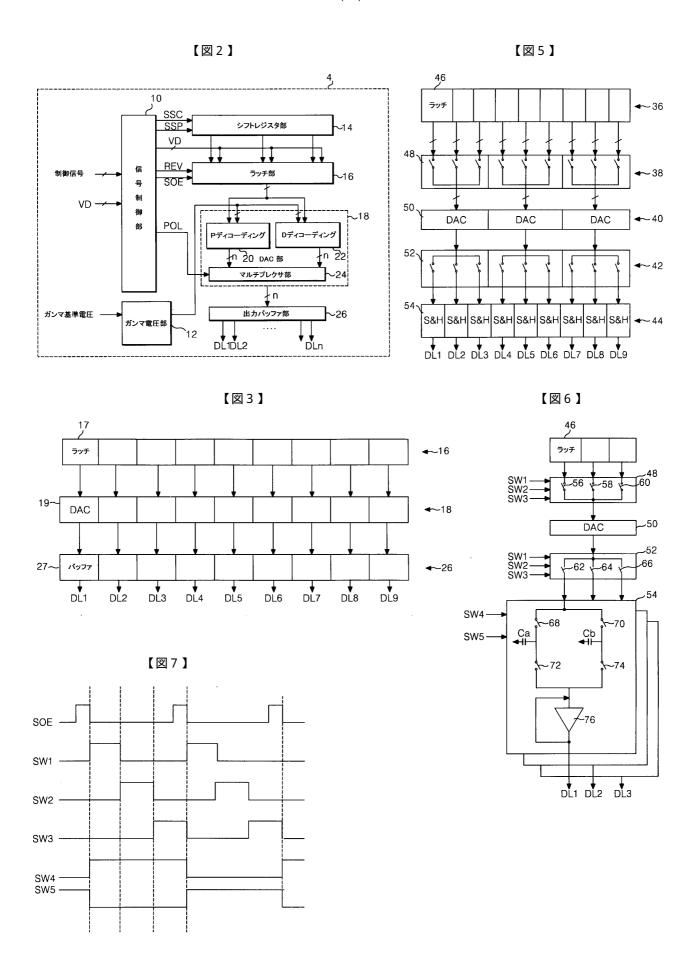

【0041】図6は、図5に図示されたデータ駆動IC 内における3個のR、G、B画素データに対する伝送経 路を具体的に図示しており、図7は図6に図示された構 成要素の駆動を制御する制御信号を図示している。

【0042】図6で3個のラッチ(46)のそれぞれ は、タイミング制御部(図示しない)から図4に図示さ 10 れた信号制御部(30)を経由して、出力イネーブル信 号(SOE)に応じたR、G、B画素データをマルチプ レクサ(48)に出力する。出力イネーブル信号(SO E)には、通常、図7に図示されたように、1水平期間 (1H)毎にラッチ(46)に共通的に供給される。

【0043】マルチプレクサ(48)は3個のラッチ (46)から入力されるR、G、B画素データを時分割 し、1つのDAC(50)に順次供給する。このため に、マルチプレクサ(48)は入力ラインが3個のラッ チ(46)のそれぞれに接続されて、出力ラインが1つ のDAC(50)に共通接続された第1乃至第3スイッ チ(56、58、60)とを具備する。第1乃至第3ス イッチ(56、58、60)は、タイミング制御部から 信号制御部(300を経由して入力される第1乃至第3 スイッチ制御信号(SW1、SW2、SW3)のそれぞ れに応じてラッチ(46)からの画素データを出力す る。例えば、第1乃至第3スイッチ(56、58、6 0)は、図7に図示されたように、順次イネーブルされ る第1乃至第3スイッチ制御信号(SW1、SW2、S W3)に応じてラッチ(46)から入力されたR、G、 30 B 画素データを、順次1つのDAC(50)に出力す る。

【0044】DAC(50)はマルチプレクサ(48) から入力されるR、G、B画素データをR、G、B画素 電圧信号に変換し、ディマルチプレクサ(52)に出力

【0045】ディマルチプレクサ(52)は、DAC (50)から順次入力されるR、G、B画素電圧信号 を、相互に異なる出力ラインを通して3個のサンプリン グ及びホルダ(54)のそれぞれに出力する。このため DAC(50)の出力ラインに共通に接続され、出力ラ インが3個のサンプリング及びホルダ(54)のそれぞ れに接続された、第4乃至第6スイッチ(62、64、 66)とを具備する。第4乃至第6スイッチ(62、6 4、66)は、タイミング制御部から信号制御部(3 0)を経由して入力される第1乃至第3スイッチ制御信 号(SW1、SW2、SW3)のそれぞれに応じてDA C(50)からの画素データを相互に異なる出力ライン を通して出力する。この場合、ディマルチプレクサ(5 される画素電圧信号をサンプリングしてホールディング 50 2)は、マルチプレクサ(48)と同一の第1乃至第3

スイッチ制御信号(SW1、SW2、SW3)を利用す る。例えば、第4乃至第6スイッチ(62、64、6 6)は、図7に示したように、順次イネーブルされる第 1乃至第3スイッチ制御信号(SW1、SW2、SW 3)に応じてDAC(50)から順次入力されるR、 G、B画素電圧信号を、3個のサンプリング及びホルダ (54)に分離して供給する。

13

【0046】3個のサンプリング及びホルダ(54) は、ディマルチプレクサ(52)から順次入力される R、G、B画素電圧信号をサンプリングしてホールディ 10 充電のための一対の第1及び第2キャパシタ(Ca、C ングした後、同時に第1乃至第3データライン(DL1 乃至DL3)のそれぞれに出力する。このためにサンプ リング及びホルダ(54)は、入力ラインがディマルチ プレクサ(52)の1つの出力ラインに共通接続された 第7及び第8スイッチ(68、70)と、第7及び第8 スイッチ(68、70)のそれぞれの出力ラインに接続 された第1及び第2キャパシタ(Ca、Cb)と、入力 ラインが1つのデータライン(DL)に共通接続された 第9及び第10スイッチ(72、74)とを具備する。 また、サンプリング及びホルダ(54)は、第9及び第20 10スイッチ(72、74)の出力ラインとデータライ ンの間に接続されたバッファ(76)とを更に具備す る。

【0047】対角線方向に位置する第7及び第10スイ ッチ(68、74)は、同一の第4スイッチ制御信号 (SW4)に応答し、第8及び第9スイッチ(70、7 2)は第4スイッチ制御信号(SW4)と相反した論理 状態を有する第5スイッチ制御信号(SW5)に応答す る。 第 4 及び第 5 スイッチ制御信号(SW4、SW5) は、異なる制御信号とタイミング制御部から信号制御部 30 (30)を通して供給される。第1及び第2キャパシタ (Ca、Cb)は互いに異なる、即ち時間的に隣接した 水平ラインのデータを充電する。

【0048】例えば、1水平期間を示す図7に図示され るように、ハイ状態に供給される第4スイッチ制御信号 (SW4)に応じて第7及び第10スイッチ(68、7) 4) がターン・オンされる。これにより、ターン・オン された第7スイッチ(68)により、ディマルチプレク サ(52)から供給される画素電圧信号がサンプリング され、第1キャパシタ(Ca)に充電されてホールディ 40 ングされる。これと同時に、直前の水平期間に第2キャ パシタ(Cb)に充電されていた画素電圧信号がターン ・オンされた第10スイッチ(74)とバッファ(7 6)を経由してデータライン(DL)に供給される。 【0049】次に、1水平期間を示す図7に図示される ように、ハイ状態に供給される第5スイッチ制御信号 (SW5)に応答して第8及び第9スイッチ(70、7 2) がターン・オンされる。これにより、ターン・オン された第8スイッチ(70)によりディマルチプレクサ (52)から供給される画素電圧信号がサンプリングさ50液晶表示装置の製造費用を低くすることができるように

れ、第2キャパシタ(Cb)に充電されてホールディン グされる。これと同時に、直前の水平期間で第1キャパ シタ(Ca)に充電されていた画素電圧信号が、ターン ・オンされた第9スイッチ(72)とバッファ(76) を経由して対応するデータライン(DL)に供給され る。

【0050】このように、サンプリング及びホルダ(5 4)が、画素電圧信号のサンプリングのための一対の第 7及び第8スイッチ(68、70)と、画素電圧信号の b)と、画素電圧信号のホールディングのための一対の 第9及び第10スイッチ(72、74)とを具備し、そ れぞれ相互交替的に駆動されるようにすることで、サン プリング及びホールディングの動作による信号遅延を防 止することができる。

【0051】以上説明したように、本発明の実施例によ るデータ駆動ICは、DAC部の時分割駆動でDAC数 を少なくとも1/3に減らすことにより、IC内でDA C部が占める空間を減らす。これにより、既存のチップ 面積と比較して大きくチップ面積を増加させないか、む しろチップ面積を減少させながら、データ駆動ICが駆 動するデータラインの数、即ち出力チャネル数を従来対 比2倍に増加させることが可能になり、よってデータ駆 動ICとそれに実装されるTCPの数を1/2に減らす ことができる。

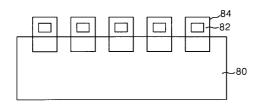

【0052】さらに詳細には、図8に図示されたよう に、2倍の出力チャネルを有するデータ駆動IC(8 2)がTCP(84)上に実装されて液晶パネル(8 0)に接続される。

【0053】例えば、SXGAモード(1280\*10 24)の液晶パネル(80)を駆動するために、従来で は384チャネルデータ駆動IC10個を必要とした反 面、前述した本発明のデータ駆動IC(82)を使用す る場合、チップ面積の増大させることなく768チャネ ルを確保することができるので、1/2である5個のデ ータ駆動IC(82)だけが必要となる。これにより、 データ駆動 I C (82) 及び T C P (84) の数を従来 より少なくとも1/2に減らすことができるので、液晶 表示装置の製造費用を低くすることができる。

#### [0054]

【発明の効果】上述したように、本発明による液晶表示 装置のデータ駆動装置及び方法では、DAC部を時分割 駆動して、既存のチップ面積と比較して大きくチップ面 積を増加させないか、むしろチップ面積を減少させなが ら、データ駆動ICの出力チャネル数を増加させること ができる。これにより、本発明による液晶表示装置のデ ータ駆動装置及び方法によると、データ駆動ICのチャ ネル数を増加させることにより、データ駆動IC及びT CPの数を従来対比1/2に減らすことができるので、

【 0 0 5 5 】以上説明した内容を通し、当業者であれば本発明の技術思想を逸脱しない範囲で多様な変更及び修正が可能であることが分かる。従って、本発明の技術的な範囲は、明細書の詳細な説明に記載された内容に限定されず、特許請求の範囲によって定められなければならない。

# 【図面の簡単な説明】

なる。

【図1】 図1は従来の液晶表示装置のデータ駆動装置 を概略的に図示した図面である。

【図2】 図2は図1に図示されたデータ駆動集積回路の詳細な構成を図示したブロック図である。

【図3】 図3は図2に図示されたデータ駆動集積回路内での一部のデータ伝送経路を具体的に図示した図面である。

【図4】 図4は本発明の実施例による液晶表示装置の データ駆動集積回路の構成を図示したブロック図であ る。

【図5】 図5は図4に図示されたデータ駆動集積回路内での一部のデータ伝送経路を図示した図面である。

【図6】 図6は図5に図示されたサンプリング及びホルダの構成を具体化し、データ伝送経路を図示した図面である。

【図7】 図7は図6に図示されたスイッチを制御するスイッチ制御信号の波形図である。

【図8】 図8は本発明によるデータ駆動集積回路を含\*

\*む液晶表示装置のデータ駆動装置を概略的に図示した図面である。

16

# 【符号の説明】

2、80:液晶パネル

4、82:データ駆動集積回路(IC)

6、84:テープ・キャリア・パッケージ(TCP)

8:データ印刷回路基板(PCB)

10、30:信号制御部

12、32:ガンマ電圧部

10 14、34:シフト・レジスタ部

16、36:ラッチ部

17、46:ラッチ

18、40:デジタル・アナログ変換(DAC)部

19、50:デジタル・アナログ変換器(DAC)

20:Pデコーディング部

22:Nデコーディング部

24、38:マルチプレクサ(MUX)部

26:出力バッファ部

27、76:バッファ

20 42: ディマルチプレクサ (DEMUX)部

44:サンプリング及びホールディング部

48:マルチプレクサ(MUX)

52:ディマルチプレクサ(DEMUX)

54:サンプリング及びホルダ

56, 58, 60, 62, 64, 66, 68, 70, 7

2、74:スイッチ

【図1】

【図8】

【図4】

# フロントページの続き

| (51) Int .Cl .<br>G 0 9 G |                          | F I<br>G 0 9 G 3/20 | テ-マコート<br>6 2 3 H    | ' (参考 ) |

|---------------------------|--------------------------|---------------------|----------------------|---------|

|                           |                          |                     | 6 2 3 L              |         |

|                           | 6 4 1                    |                     | 6 4 1 C              |         |

|                           | 6 8 0                    |                     | 6 8 0 G              |         |

| (72)発明者                   | ソン, ジン キョン               | F ターム(参考) 2H093 N   | A16 NC13 NC22 NC23 N | C24     |

|                           | 大韓民国 キョンサンブク・ドー, クミ      | N                   | C25 NC26 NC27 NC28 N | C34     |

|                           | - シ , ジンピュン - ドン , イニュイジ | N                   | 003 ND39 ND42 ND50 N | E07     |

|                           | グ 82ビー2エル, シンスン ヴィラ      | 5C006 A             | A16 AA22 AF25 AF43 A | F46     |

|                           | 303号                     | A                   | 71 AF82 BB16 BC02 B  | C12     |

|                           |                          | В                   | C13 BF03 BF04 BF11 B | F24     |

|                           |                          | В                   | F25 BF37 EB05 FA16 F | A42     |

|                           |                          | F.                  | A43 FA51             |         |

|                           |                          | 5C080 A             | A10 BB05 CC03 DD12 D | D23     |

|                           |                          | D                   | 025 DD26 DD28 EE29 F | F11     |

|                           |                          | G                   | 311 JJ02 JJ03 JJ04 J | J06     |

| 专利名称(译)        | 液晶显示装置的数据驱动装置和方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 法       |            |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | <u>JP2003208135A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2003-07-25 |  |

| 申请号            | JP2002178008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2002-06-19 |  |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |

| [标]发明人         | リーソクウー<br>ソンジンキョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |

| 发明人            | リー, ソク ウー<br>ソン, ジン キョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |  |

| CPC分类号         | G09G3/3685 G09G3/3688 G09G2310/027 G09G2310/0297 G09G2352/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.621.M G09G3/20.623.F G09G3/20.623.G G09G3/20.623.H G09G3/20.623.L G09G3/20.641.C G09G3/20.680.G                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |  |

| F-TERM分类号      | 2H093/NA16 2H093/NC13 2H093/NC22 2H093/NC23 2H093/NC24 2H093/NC25 2H093/NC26 2H093 /NC27 2H093/NC28 2H093/NC34 2H093/ND03 2H093/ND39 2H093/ND42 2H093/ND50 2H093/NE07 5C006/AA16 5C006/AA22 5C006/AF25 5C006/AF43 5C006/AF46 5C006/AF71 5C006/AF82 5C006 /BB16 5C006/BC02 5C006/BC12 5C006/BC13 5C006/BF03 5C006/BF04 5C006/BF11 5C006/BF24 5C006/BF25 5C006/BF37 5C006/EB05 5C006/FA16 5C006/FA42 5C006/FA43 5C006/FA51 5C080 /AA10 5C080/BB05 5C080/CC03 5C080/DD12 5C080/DD23 5C080/DD25 5C080/DD26 5C080/DD28 5C080/EE29 5C080/FF11 5C080/GG11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 2H193 /ZA04 |         |            |  |

| 优先权            | 1020020002090 2002-01-14 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |  |

# 摘要(译)

[目的]与现有芯片面积相比,本发明不通过时分驱动DAC单元来增加芯片面积,或者更确切地说减小芯片面积并增加数据驱动IC的输出通道数量。提供了一种能够减少驱动IC和TCP的数量的液晶显示器的数据驱动装置和方法。 根据本发明,提供了一种用于对输入像素数据进行时分和提供的多路复用器单元;一种用于将来自多路复用器单元的像素数据转换为像素电压信号的数模转换器;解复用器单元,用于选择性地将像素电压信号从模拟转换单元提供给多个输出线;以及采样,用于将来自多路分解器单元的像素电压信号保持和输出到多个数据线还有一个控股单位。