(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-77670

(P2004-77670A)

(43) 公開日 平成16年3月11日(2004.3.11)

(51) Int.Cl.<sup>7</sup>G02F 1/1368

H01L 21/336

H01L 29/786

F 1

G02F 1/1368

H01L 29/78 612Z

テーマコード(参考)

2 H 0 9 2

5 F 1 1 O

審査請求 未請求 請求項の数 6 O L (全 10 頁)

(21) 出願番号

(22) 出願日特願2002-236053 (P2002-236053)

平成14年8月13日 (2002.8.13)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100062764

弁理士 樽澤 裕

(74) 代理人 100092565

弁理士 樽澤 聰

(72) 発明者 清田 敏也

埼玉県深谷市幡羅町一丁目9番地2 株式会社東芝深谷工場内

(72) 発明者 堤 純誠

埼玉県深谷市幡羅町一丁目9番地2 株式会社東芝深谷工場内

最終頁に続く

(54) 【発明の名称】半導体素子および液晶表示装置の製造方法、および、液晶表示装置

## (57) 【要約】

【課題】特性を向上した液晶表示装置の製造方法を提供する。

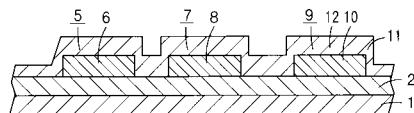

【解決手段】薄膜トランジスタ7の半導体層8と補助容量9の一方の電極10を形成する。半導体層8および一方の電極10上に、容量領域12を含むゲート絶縁膜11を形成する。ゲート絶縁膜11を介して半導体層8および補助容量9の一方の電極10に不純物を注入し、一方の電極10をメタルライクにする。不純物を注入した後にゲート絶縁膜11の表面を除去する。ゲート絶縁膜11を介してゲート電極19および他方の電極20を形成する。ゲート絶縁膜11の表面のダメージを除去するため、バイアス電圧の変化によるゲート、ソース間の電圧の鈍りが小さくなり立ちあがりが急峻になるとともに、ゲート絶縁膜11で確実に絶縁できるので効率良く動作するため電力消費量も抑制できる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

絶縁基板上に半導体膜を形成する半導体膜形成工程と、

この半導体膜上に絶縁膜を形成する絶縁膜形成工程と、

この絶縁膜を介して前記半導体膜に不純物を注入する不純物注入工程と、

半導体膜に不純物を注入した後に絶縁膜の表面を除去する除去工程と、

前記絶縁膜を介して半導体膜に対向して電極を形成する電極形成工程と

を具備したことを特徴とする半導体素子の製造方法。

**【請求項 2】**

絶縁基板上に薄膜スイッチング素子の半導体層および容量素子の一方の電極となる半導体膜を形成する半導体膜形成工程と、

薄膜スイッチング素子の半導体層上に形成され、かつ容量素子の一方の電極上に形成される容量領域となる絶縁膜を形成する絶縁膜形成工程と、

この絶縁膜を介して薄膜スイッチング素子の半導体層および容量素子の一方の電極となる半導体膜に不純物を注入する不純物注入工程と、

薄膜スイッチング素子の半導体層および容量素子の一方の電極となる半導体膜に不純物を注入した後絶縁膜の表面を除去する除去工程と、

絶縁膜を介して薄膜スイッチング素子の半導体層に対向して電極を形成するとともに容量領域を介して容量素子の一方の電極に対向した他方の電極を形成する電極形成工程と

を具備したことを特徴とする半導体素子の製造方法。 10 20

**【請求項 3】**

絶縁膜は、酸化膜である

ことを特徴とする請求項 1 または 2 記載の半導体素子の製造方法。

**【請求項 4】**

除去工程では、2 nm 以上絶縁膜の表面を除去する

ことを特徴とする請求項 1 または 2 記載の半導体素子の製造方法。

**【請求項 5】**

請求項 1 または 2 記載の半導体素子の製造方法を用いてアレイ基板を形成するアレイ基板形成工程と、

このアレイ基板に対向する対向基板を形成する対向基板形成工程と、

アレイ基板および対向基板を対向させアレイ基板および対向基板間に液晶層を形成する液晶層形成工程と

を具備したことを特徴とする液晶表示装置の製造方法。 30

**【請求項 6】**

請求項 1 または 2 記載の半導体素子の製造方法を用いて形成されたアレイ基板と、

このアレイ基板に対向して配設される対向基板と、

前記アレイ基板および対向基板間に挟持される液晶層と

を具備したことを特徴とする液晶表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、特性を向上した半導体素子および液晶表示装置の製造方法、および、液晶表示装置に関する。

**【0002】****【従来の技術】**

従来、多結晶シリコン(p-Si)の半導体素子を用いて駆動回路内蔵型の液晶表示装置が製造されている。

**【0003】**

そして、液晶表示装置で内蔵する駆動回路の高機能化および高性能化を図りながら消費電力の増加を抑制させるためには、半導体素子の高性能化ならびに高品質化を図らなければ 50

ならない。

【0004】

このため、回路構成上で液晶表示装置を安定して駆動するために容量素子となる補助容量が形成されこの補助容量はMOS構造が採用されていたが、近年は両極性の容量保証が要求されるため、MIM構造の補助容量が要求されている。

【0005】

そして、MIM構造の補助容量を製造工程を増加することなく形成する場合には、この補助容量を薄膜スイッチング素子となる薄膜トランジスタと同じ工程で製造する必要がある。この場合、補助容量は、電極間に容量領域の絶縁膜を挟持した構成で、補助容量の一方の電極に半導体を用い、この半導体に $n^+$ または $p^+$ の高濃度の不純物を注入させてメタルライクの特性を持たせて形成している。すなわち、薄膜トランジスタは、たとえば半導体層およびゲート電極間にゲート絶縁膜が形成されているが、補助容量の一方の電極を薄膜トランジスタの半導体層と一緒に形成し、補助容量の容量領域を薄膜トランジスタのゲート絶縁膜と一緒に形成し、補助容量の他方の電極を薄膜トランジスタのゲート電極と一緒に形成し、薄膜トランジスタの半導体層のコンタクト領域に高濃度の不純物を注入する際に、補助容量の一方の電極にも高濃度の不純物を注入している。

【0006】

【発明が解決しようとする課題】

しかしながら、他方の電極を形成する前に $n^+$ または $p^+$ の高濃度不純物領域を他方の電極に含有する必要があり、絶縁膜上にレジストマスクのみを用いた状態で不純物を注入処理すると、不純物注入処理後にレジストマスクを除去するためには、レジストマスクの表面の変質層をプラズマ処理で除去しなければならず、このプラズマ処理により薄膜トランジスタのゲート絶縁膜などへのダメージが信頼性を損なうおそれがある。

【0007】

本発明は、上記問題点に鑑みなされたもので、特性を向上した半導体素子および液晶表示装置の製造方法、および、液晶表示装置を提供することを目的とする。

【0008】

【課題を解決するための手段】

本発明は、絶縁基板上に半導体膜を形成する半導体膜形成工程と、この半導体膜上に絶縁膜を形成する絶縁膜形成工程と、この絶縁膜を介して前記半導体膜に不純物を注入する不純物注入工程と、半導体膜に不純物を注入した後に絶縁膜の表面を除去する除去工程と、前記絶縁膜を介して半導体膜に対向して電極を形成する電極形成工程とを具備したり、あるいは、絶縁基板上に薄膜スイッチング素子の半導体層および容量素子の一方の電極となる半導体膜を形成する半導体膜形成工程と、薄膜スイッチング素子の半導体層上に形成され、かつ容量素子の一方の電極上に形成される容量領域となる絶縁膜を形成する絶縁膜形成工程と、この絶縁膜を介して薄膜スイッチング素子の半導体層および容量素子の一方の電極となる半導体膜に不純物を注入する不純物注入工程と、薄膜スイッチング素子の半導体層および容量素子の一方の電極となる半導体膜に不純物を注入した後絶縁膜の表面を除去する除去工程と、絶縁膜を介して薄膜スイッチング素子の半導体層に対向して電極を形成するとともに容量領域を介して容量素子の一方の電極に対向した他方の電極を形成する電極形成工程とを具備したもので、不純物注入工程の際に絶縁膜の表面にダメージが生じても、不純物注入工程の後に、絶縁膜の表面を除去することにより、絶縁膜の表面のダメージを受けた部分が除去できるため、薄膜スイッチング素子の特性に悪影響を与えることを防止して、特性を向上する。

【0009】

【発明の実施の形態】

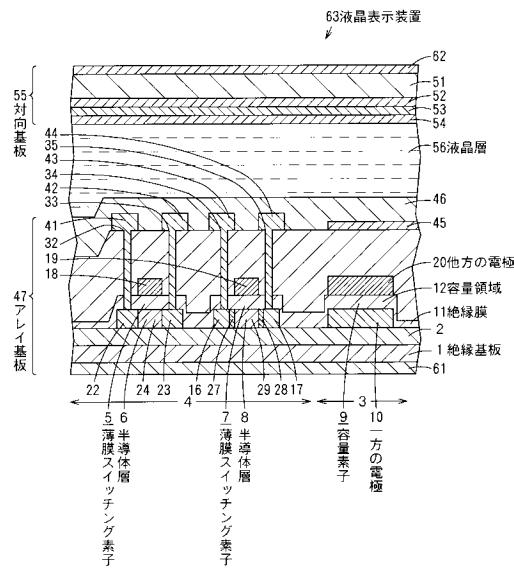

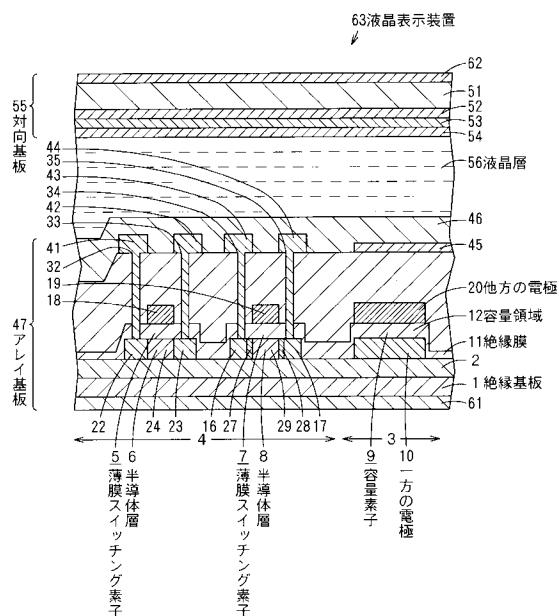

以下、本発明の液晶表示装置の一実施の形態を製造方法に従い図面を参照して説明する。

【0010】

まず、図2に示すように、絶縁基板であるガラス基板1上にガラス基板1からのナトリウム(Na)などのイオンをブロックするパッシベーション膜2およびアモルファスシ

10

20

30

40

50

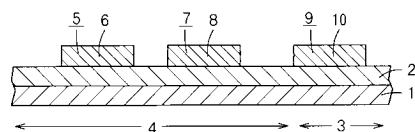

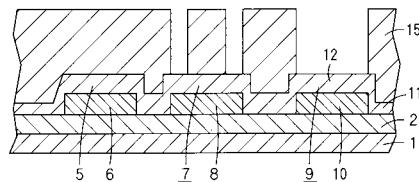

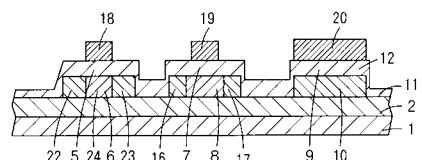

リコン( a - S i )のアモルファスシリコン層を順次積層して成膜する。そして、このアモルファスシリコン層にエキシマレーザを照射してアニールして溶融させた後に再結晶化させてアモルファスシリコン層を多結晶化してポリシリコン( p - S i )として半導体膜であるポリシリコン層とし、フォトリソグラフィ工程でマスクを形成し、ポリシリコン層を島状にエッティングする半導体膜形成工程をする。一方、ほぼ中央に位置する矩形状の表示領域 3 を有し、この表示領域 3 の周囲にはいわゆる額縁領域 4 が形成され、この額縁領域 4 には駆動用の薄膜スイッチング素子である p チャネルの薄膜トランジスタ 5 の半導体層 6 、同様の薄膜スイッチング素子である n チャネルの薄膜トランジスタ 7 の半導体層 8 、および、容量素子である補助容量 9 の一方の電極 10 を形成する。なお、半導体層 6 , 8 および一方の電極 10 には必要に応じて低濃度の不純物を注入する。

10

## 【 0 0 1 1 】

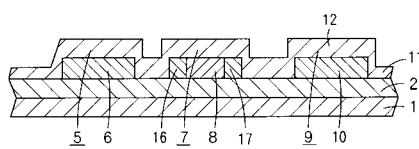

また、図 3 に示すように、絶縁膜形成工程では、これら半導体層 6 , 8 および一方の電極 10 を含むパッシベーション膜 2 上に、 C V D 法を用いてたとえばテトラエトキシシラン( T E O S : Tetra Ethoxy Silane )を原料ガスとして、膜厚 80 nm の T E O S 膜であるゲート絶縁膜 11 を成膜し、一方の電極 10 上のゲート絶縁膜 11 は容量領域 12 となる。なお、ゲート絶縁膜 11 としては酸化膜である T E O S 膜を用いているが、他の絶縁膜を用いてもよく、膜厚に関しては特性に応じて設定する。

## 【 0 0 1 2 】

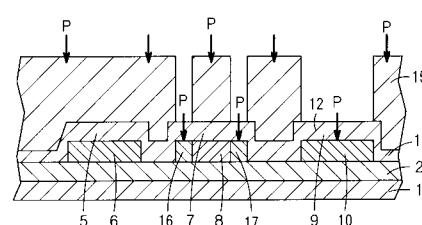

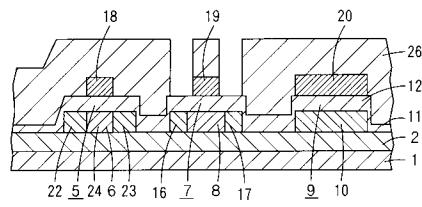

そして、ゲート絶縁膜 11 上にレジスト層を形成し、図 4 に示すように、 n チャネルの薄膜トランジスタ 7 の半導体層 8 上の一部および補助容量 9 の一方の電極 10 上を除き、 p チャネルの薄膜トランジスタ 5 の半導体層 6 を含むゲート絶縁膜 11 上を覆うレジストマスク 15 をフォトリソグラフィを用いて形成する。

20

## 【 0 0 1 3 】

続いて、図 5 に示すように、不純物注入工程では、イオンの質量分離機能を装荷しないイオンドーピング装置を用いてたとえば加速電圧 50 keV で  $1.3 \times 10^{15}$  atom/cm<sup>2</sup> のドーズ量でリン( P )イオンを、 n チャネルの薄膜トランジスタ 7 の半導体層 8 のコンタクト領域であるソース領域 16 およびドレイン領域 17 、および、補助容量 9 の一方の電極 10 に高濃度に n<sup>+</sup> の不純物を注入し、メタルライク化する。なお、不純物の注入の条件は、 n チャネルの薄膜トランジスタ 7 の特性および膜構成によって設定可能であり、不純物注入方法としてイオンの質量分離機能を装荷しないイオンドーピング装置を用いたが、イオンの質量分離機能装荷したイオン注入装置を用いてもよい。

30

## 【 0 0 1 4 】

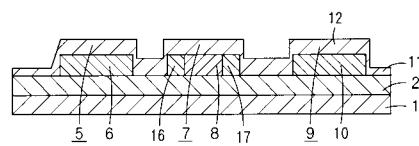

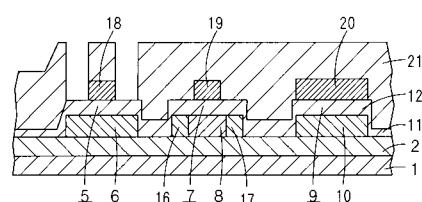

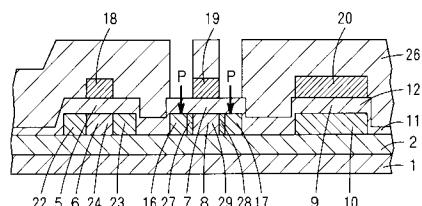

次に、レジストマスク 15 を、図 6 に示すように、酸素プラズマ処理を用いてドライ剥離処理し、ドライ剥離処理後にアルカリ溶液を用いてウエット剥離処理する。なお、レジストマスク 15 の剥離を段階で処理しているが、 1 段階目のプラズマ処理のみでレジストマスク 15 を除去してもよい。

## 【 0 0 1 5 】

次に、除去工程では、ゲート絶縁膜 11 をエッティング量は最低でも 2 nm 以上になるよう条件を設定し、たとえばスピニ型のウエット処理装置を用いて、フッ酸濃度を 1.0 質量% ( 1.0 wt % ) 、エッティング時間を 10 秒として、エッティング量が平均値で 5 nm 、最小エッティング量が 2 nm 以上で図 7 に示すようにエッティングする。なお、エッティング量の上限は、必要とされる p チャネルの薄膜トランジスタ 5 および n チャネルの薄膜トランジスタ 7 の特性に合わせて設定する。このように、最小エッティング量が 2 nm 以上であれば、ゲート絶縁膜 11 に生じたダメージをほとんどの場合除去できるとともに、平均値で 5 nm 程度の除去であればゲート絶縁膜 11 が薄くなつて絶縁破壊することも防止できる。

40

## 【 0 0 1 6 】

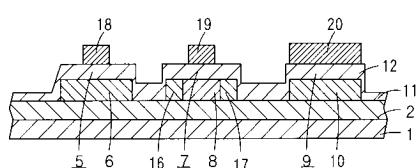

また、このエッティングされたゲート絶縁膜 11 上に金属層を形成し、この金属層をエッティングして、図 8 に示すように、 p チャネルの薄膜トランジスタ 5 の半導体層 6 の中央の上方のゲート絶縁膜 11 上に配線を兼ねたゲート電極 18 、 n チャネルの薄膜トランジスタ

50

7 の半導体層 8 のソース領域 1 6 およびドレイン領域 1 7 を除くほぼ中央の上方のゲート絶縁膜 1 1 上に配線を兼ねたゲート電極 1 9 、および、補助容量 9 の一方の電極 1 0 の上方のゲート絶縁膜 1 1 上に他方の電極 2 0 を形成する。

【 0 0 1 7 】

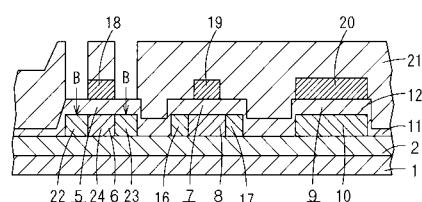

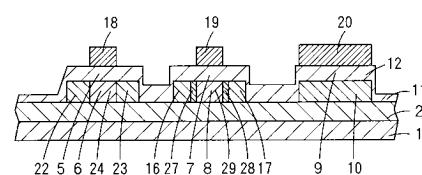

そして、電極形成工程では、p チャネルの薄膜トランジスタ 5 のゲート電極 1 8 、n チャネルの薄膜トランジスタ 7 のゲート電極 1 9 および補助容量 9 の他方の電極 2 0 を含むゲート絶縁膜 1 1 上にレジスト層を形成し、図 9 に示すように、p チャネル用の薄膜トランジスタ 5 以外の部分と p チャネルの薄膜トランジスタ 5 のゲート電極 1 8 のみを覆うレジストマスク 2 1 をフォトリソグラフィを用いて形成する。

【 0 0 1 8 】

続いて、図 1 0 に示すように、ボロン (B) イオンを高濃度に注入し、ゲート電極 1 8 に自己整合させてゲート電極 1 8 により自己整合されていない部分には高濃度で不純物イオンが注入されたコンタクト領域となるソース領域 2 2 およびドレイン領域 2 3 が形成され、これらソース領域 2 2 およびドレイン領域 2 3 の間にはチャネル領域 2 4 が形成される。

【 0 0 1 9 】

次に、レジストマスク 2 1 を、図 1 1 に示すように、剥離処理する。

【 0 0 2 0 】

そして、p チャネルの薄膜トランジスタ 5 のゲート電極 1 8 、n チャネルの薄膜トランジスタ 7 のゲート電極 1 9 および補助容量 9 の他方の電極 2 0 を含むゲート絶縁膜 1 1 上に再びレジスト層を形成し、図 1 2 に示すように、n チャネル用の薄膜トランジスタ 7 以外の部分と n チャネルの薄膜トランジスタ 7 のゲート電極 1 9 のみを覆うレジストマスク 2 6 をフォトリソグラフィを用いて形成する。

【 0 0 2 1 】

続いて、図 1 3 に示すように、リン (P) イオンを低濃度に注入し、ゲート電極 1 9 に自己整合させてゲート電極 1 9 により自己整合されていないソース領域 2 2 およびドレイン領域 2 3 以外の部分に中濃度の不純物イオンが注入されて活性化された LDD (Light Doped Drain) 領域 2 7 , 2 8 が形成され、これら LDD 領域 2 7 , 2 8 間にはチャネル領域 2 9 が形成される。

【 0 0 2 2 】

次に、レジストマスク 2 6 を、図 1 4 に示すように、剥離処理する。

【 0 0 2 3 】

また、図 1 5 に示すように、p チャネルの薄膜トランジスタ 5 のゲート電極 1 8 、n チャネルの薄膜トランジスタ 7 のゲート電極 1 9 および補助容量 9 の他方の電極 2 0 を含むゲート絶縁膜 1 1 上に、層間絶縁膜 3 1 を形成する。

【 0 0 2 4 】

さらに、図 1 6 に示すように、層間絶縁膜 3 1 およびゲート絶縁膜 1 1 の、p チャネルの薄膜トランジスタ 5 のソース領域 2 2 およびドレイン領域 2 3 、および、n チャネルの薄膜トランジスタ 7 のソース領域 1 6 およびドレイン領域 1 7 に対応する部分に、エッティングによりそれぞれコンタクトホール 3 2 , 3 3 , 3 4 , 3 5 を形成する。

【 0 0 2 5 】

そして、図 1 7 に示すように、コンタクトホール 3 2 には p チャネルの薄膜トランジスタ 5 のソース領域 2 2 と電気的に接続され配線を兼ねたソース電極 4 1 、コンタクトホール 3 3 には p チャネルの薄膜トランジスタ 5 のドレイン領域 2 3 と電気的に接続され配線を兼ねたドレイン電極 4 2 、コンタクトホール 3 4 には n チャネルの薄膜トランジスタ 7 のソース領域 1 6 と電気的に接続され配線を兼ねたソース電極 4 3 、および、コンタクトホール 3 5 には n チャネルの薄膜トランジスタ 7 のドレイン領域 1 7 と電気的に接続され配線を兼ねたドレイン電極 4 4 が、それぞれ金属にて形成されている。さらに、表示領域 3 には、ITO (Indium Tin Oxide) の画素電極 4 5 が形成される。

【 0 0 2 6 】

10

20

30

40

50

また、これらの表面には、図18に示すように、保護用のパッシベーション膜46が形成されて、マトリクスアレイ基板47となる。

#### 【0027】

一方、絶縁基板であるガラス基板51上に、カラーフィルタ52およびたとえばITOの透明電極の対向電極53を積層形成し、この対向電極53上にポリイミド膜54を成膜して対向基板55を形成する。

#### 【0028】

そして、マトリクスアレイ基板47および対向基板55を対向させて、これらマトリクスアレイ基板47および対向基板55間に液晶層56を挟持させ、マトリクスアレイ基板47および対向基板55のそれぞれの背面に偏光板61, 62が設けられて、液晶表示装置10を形成する。

#### 【0029】

ここで、nチャネルの薄膜トランジスタ7の半導体層8および補助容量9の一方の電極10に不純物イオンを注入した後に、レジストマスク15を剥離し、ゲート絶縁膜11の表面を除去した上述の実施の形態とゲート絶縁膜11の表面を除去しない比較例との実験結果について説明する。

#### 【0030】

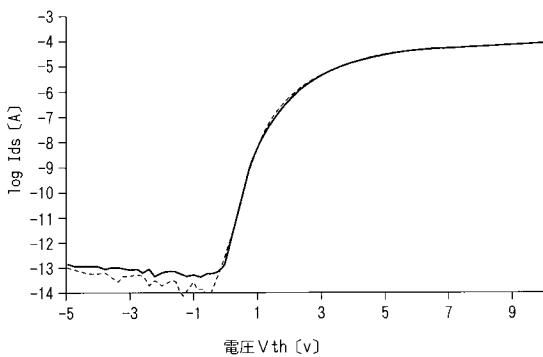

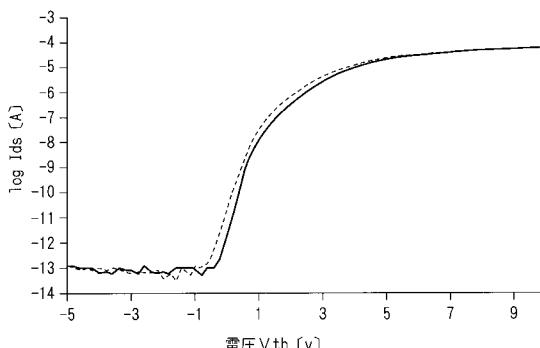

また、I-V初期特性とバイアスおよび温度のストレス条件として90、2000秒で、ゲート、ソース間電圧Vgsを12Vとした試験後のI-V特性は、比較例のものではゲート絶縁膜11の表面にダメージが生じていることがあり、図20に示すように、破線に示すバイアスおよび温度のストレスを掛けた後は、実線に示す初期特性に比べVthが大きくシフトしてしまい特性が変化してしまうのに対し、上述の実施の形態によれば、図19に示すように、破線に示すバイアスおよび温度のストレスを掛けた後でも、実線に示す初期特性と大きな変化がなく特性を維持できる。

#### 【0031】

さらに、図19に示す実施の形態のものでは、図20に示す比較例に比べてバイアス電圧の変化によるゲート、ソース間の電圧Vgsの鈍りが小さくなり立ちあがりが急峻になるとともに、ゲート絶縁膜11で確実に絶縁できるので効率良く動作するため電力消費量も抑えることができる。

#### 【0032】

また、補助容量9の一方の電極10をメタルライク化した半導体で形成し、容量領域12をゲート絶縁膜11で形成し、他方の電極20を金属で形成することにより、MIM(Metal Insulation Metal)構造となり、MOS構造に比べて立ち上がり特性が向上するとともに消費電力も減少する。さらに、補助容量9の一方の電極10は、nチャネルの薄膜トランジスタ7の半導体層8と同一の工程でメタルライク化させて形成し、容量領域12はゲート絶縁膜11を用い、他方の電極20はゲート絶縁膜11とともに形成するため、補助容量9をnチャネルの薄膜トランジスタ7の製造工程と同一で製造できるので、製造工程が複雑化することもない。

#### 【0033】

なお、上記実施の形態では、一方の電極10をn<sup>+</sup>の不純物で形成しているが、p<sup>+</sup>の不純物で形成しても同様の効果を得ることができる。

#### 【0034】

#### 【発明の効果】

本発明によれば、不純物注入工程の際に絶縁膜の表面にダメージが生じても、不純物注入工程の後に、絶縁膜の表面を除去することにより、絶縁膜の表面のダメージを受けた部分が除去できるため、薄膜スイッチング素子の特性に悪影響を与えることを防止して、特性を向上できる。

#### 【図面の簡単な説明】

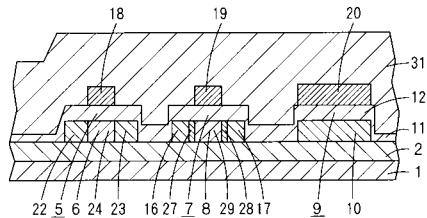

【図1】本発明の一実施の形態の液晶表示装置を示す断面図である。

【図2】同上液晶表示装置の一製造工程を示す断面図である。

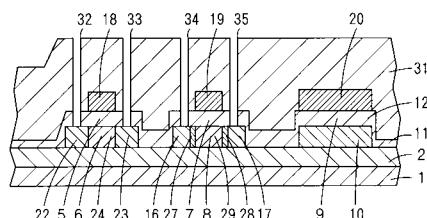

【図3】同上液晶表示装置の図2の次の製造工程を示す断面図である。

【図4】同上液晶表示装置の図3の次の製造工程を示す断面図である。

【図5】同上液晶表示装置の図4の次の製造工程を示す断面図である。

【図6】同上液晶表示装置の図5の次の製造工程を示す断面図である。

【図7】同上液晶表示装置の図6の次の製造工程を示す断面図である。

【図8】同上液晶表示装置の図7の次の製造工程を示す断面図である。

【図9】同上液晶表示装置の図8の次の製造工程を示す断面図である。

【図10】同上液晶表示装置の図9の次の製造工程を示す断面図である。

【図11】同上液晶表示装置の図10の次の製造工程を示す断面図である。

【図12】同上液晶表示装置の図11の次の製造工程を示す断面図である。

【図13】同上液晶表示装置の図12の次の製造工程を示す断面図である。

【図14】同上液晶表示装置の図13の次の製造工程を示す断面図である。

【図15】同上液晶表示装置の図14の次の製造工程を示す断面図である。

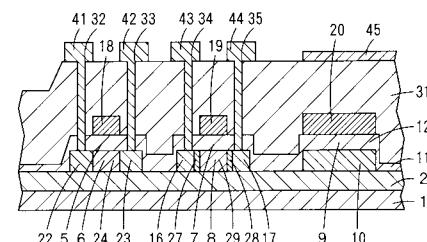

【図16】同上液晶表示装置の図15の次の製造工程を示す断面図である。

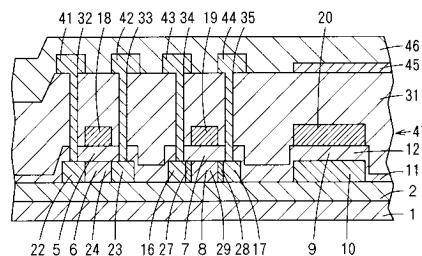

【図17】同上液晶表示装置の図16の次の製造工程を示す断面図である。

【図18】同上液晶表示装置の図17の次の製造工程を示す断面図である。

【図19】同上薄膜トランジスタの初期のI-V初期特性とバイアスおよび温度のストレス後の特性を示したグラフである。

【図20】比較例の薄膜トランジスタの初期のI-V初期特性とバイアスおよび温度のストレス後の特性を示したグラフである。

#### 【符号の説明】

1 絶縁基板としてのガラス基板

5, 7 薄膜スイッチング素子としての薄膜トランジスタ

6, 8 半導体層

9 容量素子としての補助容量

10 一方の電極

11 ゲート絶縁膜

12 容量領域

20 他方の電極

47 マトリクスアレイ基板

55 対向基板

56 液晶層

63 液晶表示装置

10

20

30

【図1】

【図2】

【図6】

【図7】

【図8】

【図3】

【図4】

【図5】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(72)発明者 鎌田 好貴

埼玉県深谷市幡羅町一丁目9番地2 株式会社東芝深谷工場内

F ターム(参考) 2H092 GA59 JA24 JB66 KA04 KA07 KA10 KA12 KA18 KA22 KB04

KB13 MA07 MA13 MA18 MA27 MA30 MA37 MA41 NA21 NA26

5F110 AA09 AA16 BB02 BB04 CC02 DD02 DD11 FF02 FF29 FF36

GG02 GG13 HJ01 HJ04 HJ12 HJ13 HM15 NN01 NN02 NN72

NN73 PP03 QQ11

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 半导体器件，制造液晶显示器器件的方法和液晶显示器                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2004077670A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2004-03-11 |

| 申请号            | JP2002236053                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2002-08-13 |

| [标]申请(专利权)人(译) | 株式会社东芝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 东芝公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 清田敏也<br>堤純誠<br>鎌田好貴                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 清田 敏也<br>堤 純誠<br>鎌田 好貴                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/1368 H01L21/336 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G02F1/1368 H01L29/78.612.Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA59 2H092/JA24 2H092/JB66 2H092/KA04 2H092/KA07 2H092/KA10 2H092/KA12 2H092 /KA18 2H092/KA22 2H092/KB04 2H092/KB13 2H092/MA07 2H092/MA13 2H092/MA18 2H092/MA27 2H092/MA30 2H092/MA37 2H092/MA41 2H092/NA21 2H092/NA26 5F110/AA09 5F110/AA16 5F110 /BB02 5F110/BB04 5F110/CC02 5F110/DD02 5F110/DD11 5F110/FF02 5F110/FF29 5F110/FF36 5F110/GG02 5F110/GG13 5F110/HJ01 5F110/HJ04 5F110/HJ12 5F110/HJ13 5F110/HM15 5F110 /NN01 5F110/NN02 5F110/NN72 5F110/NN73 5F110/PP03 5F110/QQ11 2H192/AA24 2H192/BC31 2H192/CB02 2H192/CB81 2H192/DA44 2H192/DA62 2H192/EA43 2H192/HA64 2H192/HA65 2H192 /HA80 2H192/HA84 2H192/JA02 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

## 摘要(译)

要解决的问题：提供一种制造具有改进特性的液晶显示装置的方法。解决方案：形成薄膜晶体管（TFT）7的半导体层8和辅助电容9的一个电极10。在半导体层8和一个电极10上形成包含电容区12的栅极绝缘膜11。通过栅极绝缘膜11将杂质掺杂到半导体层8和辅助电容9的一个电极10中，以便使一个电极10成金属状。在掺杂杂质之后，去除栅极绝缘膜11的表面。经由栅极绝缘膜11形成栅电极19和另一电极20。由于去除了栅极绝缘膜11表面上的任何损坏，由于偏置电压的变化导致栅极和源极之间的电压减慢。变小，陡峭的上升增加。同时，由于TFT确实与栅极绝缘膜11绝缘，因此TFT有效地工作，因此抑制了功耗。 $\checkmark$