(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-37648

(P2004-37648A)

(43) 公開日 平成16年2月5日(2004.2.5)

(51) Int.Cl.<sup>7</sup>**G09G 3/36****G02F 1/133****G09G 3/20**

F 1

G09G 3/36

GO2F 1/133 550

G09G 3/20 611A

G09G 3/20 621M

G09G 3/20 623X

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 4 O L (全 8 頁) 最終頁に続く

(21) 出願番号

特願2002-192313(P2002-192313)

(22) 出願日

平成14年7月1日(2002.7.1.)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100083806

弁理士 三好 秀和

(74) 代理人 100068342

弁理士 三好 保男

(74) 代理人 100100712

弁理士 岩▲崎▼幸邦

(74) 代理人 100100929

弁理士 川又 澄雄

(74) 代理人 100108707

弁理士 中村 友之

(74) 代理人 100095500

弁理士 伊藤 正和

最終頁に続く

(54) 【発明の名称】平面表示装置

## (57) 【要約】

【課題】アクティブマトリクス型の液晶表示装置において、大画面化した場合でも低消費電力化で駆動することができるようとする。

【解決手段】信号線Sの略中央部にスイッチ素子SW(SW<sub>1</sub>, SW<sub>2</sub>, ..., SW<sub>m</sub>)を接続し、1フレームの書き込み前半部101ではスイッチ素子SWをすべて導通状態とし、書き込み後半部102ではスイッチ素子SWをすべて非導通状態とすることにより、1フレームで信号線Sの配線容量を半減させる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

表示領域内に、マトリクス状に配列された複数の走査線及び複数の信号線、このマトリクスの各格子毎に配置された画素電極、前記走査線に供給される行選択信号により前記信号線と前記画素電極間を導通させて前記信号線に供給された映像信号を前記画素電極に書き込む、前記各格子毎に設けられた画素スイッチ素子を有するアレイ基板と、前記画素電極と所定間隔をもって対向配置される共通の対向電極を有する対向基板と、前記アレイ基板と前記対向基板との間に保持された表示層とを備えた平面表示装置において、

前記複数の信号線は、それぞれ前記表示領域内で少なくとも1つのスイッチ素子に接続され、一画面分の映像信号の書き込み時に、前記スイッチ素子を挟んで書き込みの前半部と後半部に区分される表示領域のうち、前半部への書き込み時と後半部への書き込み時に応じて、前記スイッチ素子を導通又は非導通とすることを特徴とする平面表示装置。10

**【請求項 2】**

前記前半部への書き込み時は前記スイッチ素子を導通させ、後半部への書き込み時は前記スイッチ素子を非導通とすることを特徴とする請求項1に記載の平面表示装置。

**【請求項 3】**

前記前半部への書き込み時は前記スイッチ素子を非導通とし、後半部への書き込み時は前記スイッチ素子を導通させることを特徴とする請求項1に記載の平面表示装置。

**【請求項 4】**

前記スイッチ素子は、前記各信号線の前記表示領域内における略中央部に接続され、共通の制御信号線に供給される制御信号により導通又は非導通が切り替えられることを特徴とする請求項1乃至3のいずれかに記載の平面表示装置。20

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

この発明は、液晶表示装置などの平面表示装置に関し、詳しくは画面内の信号線容量を半減化して、更なる低消費電力を実現した平面表示装置に関する。

**【0002】****【従来の技術】**

近年、液晶表示装置に代表される平面表示装置は、薄型、軽量且つ低消費電力であることから、各種機器のディスプレイとして用いられている。中でも、画素毎に薄膜トランジスタからなる画素スイッチ素子を配置したアクティブラチタクス型の液晶表示装置は、ノート型PCや携帯型情報端末のディスプレイとして普及しつつある。30

**【0003】**

最近では、これまでのアモルファスシリコンに比べて電子移動度が高いポリシリコン TFTを比較的低温のプロセスで形成する技術が確立したことにより、画素スイッチ素子の小型化が可能となり、大画面化や高精細化が進んでいる。

**【0004】****【発明が解決しようとする課題】**

ところで、画面サイズが大画面化するに伴い、表示領域内でマトリクス状に配列される走査線と信号線の配線長も共に長くなり、画面内における消費電力も大きくなる。とくに、信号線は配線本数が走査線よりも多いため、大画面化に伴う配線容量の増大が著しく、消費電力の削減は難しいものとなっていた。40

**【0005】**

この発明の目的は、画面内の信号線容量を半減することにより、大画面化した場合でも低消費電力化で駆動することができる平面表示装置を提供することにある。

**【0006】****【課題を解決するための手段】**

上記課題を解決するため、請求項1の発明は、表示領域内に、マトリクス状に配列された複数の走査線及び複数の信号線、このマトリクスの各格子毎に配置された画素電極、前記

10

20

30

40

50

走査線に供給される行選択信号により前記信号線と前記画素電極間を導通させて前記信号線に供給された映像信号を前記画素電極に書き込む、前記各格子毎に設けられた画素スイッチ素子を有するアレイ基板と、前記画素電極と所定間隔をもって対向配置される共通の対向電極を有する対向基板と、前記アレイ基板と前記対向基板との間に保持された表示層とを備えた平面表示装置において、前記複数の信号線は、それぞれ前記表示領域内で少なくとも1つのスイッチ素子に接続され、一画面分の映像信号の書き込み時に、前記スイッチ素子を挟んで書き込みの前半部と後半部に区分される表示領域のうち、前半部への書き込み時と後半部への書き込み時に応じて、前記スイッチ素子を導通又は非導通とすることを特徴とする。

## 【0007】

10

請求項2の発明は、請求項1において、前記前半部への書き込み時は前記スイッチ素子を導通させ、後半部への書き込み時は前記スイッチ素子を非導通とすることを特徴とする。

## 【0008】

請求項3の発明は、請求項1において、前記前半部への書き込み時は前記スイッチ素子を非導通とし、後半部への書き込み時は前記スイッチ素子を導通させることを特徴とする。

## 【0009】

請求項4の発明は、請求項1乃至3のいずれかにおいて、前記スイッチ素子は、前記各信号線の前記表示領域内における略中央部に接続され、共通の制御信号線に供給される制御信号により導通又は非導通が切り替えられることを特徴とする。

## 【0010】

20

## 【発明の実施の形態】

以下、本発明に係わる平面表示装置を液晶表示装置として構成した場合の実施の形態について説明する。

## 【0011】

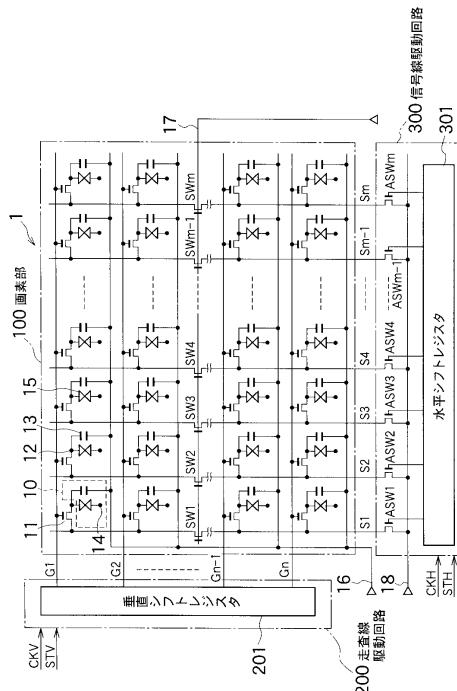

図1は、本実施の形態に係わる液晶表示装置の回路構成を示すブロック図である。

## 【0012】

図1に示す液晶パネル1は、複数の画素10が形成された画素部100、走査線駆動回路200及び信号線駆動回路300を備えている。なお、走査線駆動回路200と信号線駆動回路300は、図示しないアレイ基板上に画素部100と一緒に実装されていてもよいし、図示しない外部駆動基板上に実装されていてもよい。

30

## 【0013】

表示領域となる画素部100には、複数の走査線G1, G2, ..., Gn(以下、総称G)と、複数の信号線S1, S2, ..., Sm(以下、総称S)がマトリクス状に配線されており、このマトリクスの各格子毎に薄膜トランジスタで構成された画素スイッチ素子11が配置されている。各画素トランジスタ11のゲートは行毎に走査線Gに共通に接続され、ソースは列毎に信号線Sに共通に接続されている。また、ドレインは画素電極12及び補助容量素子13に接続されている。

## 【0014】

補助容量子13は、画素電極12と補助容量線16との間に補助容量Csを形成している。また、補助容量線16は、すべての画素10の補助容量素子13と電気的に接続されており、図示しない外部回路から所定の電位が与えられている。

40

## 【0015】

各画素電極12と電気的に相対する対向電極14は、図示しないアレイ基板と対向配置される図示しない対向基板上に形成されている。そして、両基板間には表示層として液晶層15が保持され、画素電極12と対向電極14との間に液晶容量C1cを形成している。対向電極14には、図示しない外部回路から所定のコモン電圧が与えられている。

## 【0016】

信号線Sを通じて書き込まれた映像信号は、各画素10の液晶容量C1cと容量Csにそれぞれ電荷として蓄積され、次フレームの書き込みがなされるまで1フレーム期間保持される。

50

## 【0017】

また、各信号線 S は、画素部 100 内における中央部においてスイッチ素子 SW1, SW2, ... SWm (以下、総称 SW) が接続されている。このスイッチ素子 SW のゲートは共通に制御信号線 17 に接続されており、図示しないコントロール IC から供給されるオン / オフの制御信号により、すべてのスイッチ素子 SW のオン / オフが同時に切り替えられるように構成されている。スイッチ素子 SW がオンすると、信号線 S は長手方向にすべて導通状態となり、信号線駆動回路 300 から出力される映像信号はすべての画素 10 に供給される。またスイッチ素子 SW がオフすると、信号線 S は画素部 100 の下半分で導通状態となり、信号線駆動回路 300 から出力される映像信号は下半分の画素 10 にのみ供給されることになる。

10

## 【0018】

走査線駆動回路 200 は、垂直シフトレジスタ 201 と、図示しないレベルシフタ及びバッファ回路とから構成されている。図示しないコントロール IC から供給された垂直クロック信号 (CKV)、垂直スタート信号 (STV) は、前記レベルシフタやバッファ回路で電圧増幅された後、垂直シフトレジスタ 201 に入力される。垂直シフトレジスタ 201 では、垂直クロック信号に同期して垂直スタート信号を 1 段づつ下方向にシフトしながら、対応する走査線 G に行選択信号として出力する。

## 【0019】

信号線駆動回路 300 は、水平シフトレジスタ 301、ビデオバス 18、アナログスイッチ ASW1, ASW2, ... ASWm (以下、総称 ASW)、及び図示しないレベルシフタから構成されている。図示しないコントロール IC から供給された水平クロック信号 (CKH)、水平スタート信号 (STH) は、前記レベルシフタで電圧増幅された後、水平シフトレジスタ 301 に入力される。水平シフトレジスタ 301 では、水平クロック信号に同期して水平スタート信号を 1 段づつ右方向にシフトしながら、対応するアナログスイッチ ASW に水平走査パルスとして出力する。この水平シフトレジスタ 301 の各出力端から出力された水平走査パルスによりアナログスイッチ ASW がオンすると、ビデオバス 18 に供給された映像信号が対応する信号線 S に書き込まれる。

20

## 【0020】

図 1において、信号線駆動回路 300 から信号線 S1, S2, ... に映像信号が書き込まれ、これと同期して走査線駆動回路 200 から走査線 G1, G2, ... に行選択信号が出力されると、その走査線方向に存在する画素スイッチ素子 11 がオン状態となり、信号線 S1, S2, ... に書き込まれた映像信号が画素スイッチ素子 11 を介して前記走査線方向に存在する画素 10 に印加される。この映像信号は液晶容量 Clc と補助容量 Cs に電荷として蓄積され、これに液晶層 15 が応答することで、その電荷の大きさに応じた階調度の映像が映し出される。

30

## 【0021】

次に、上記のように構成された液晶表示装置において、信号線に映像信号を書き込む際の動作について説明する。

## 【0022】

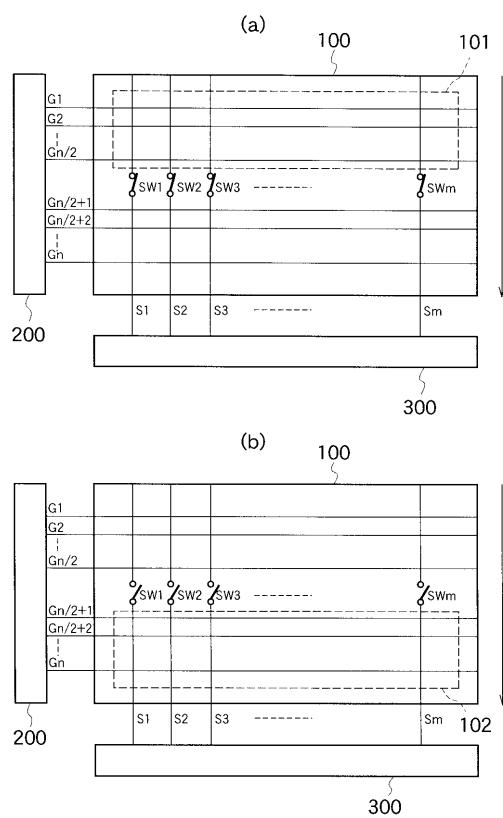

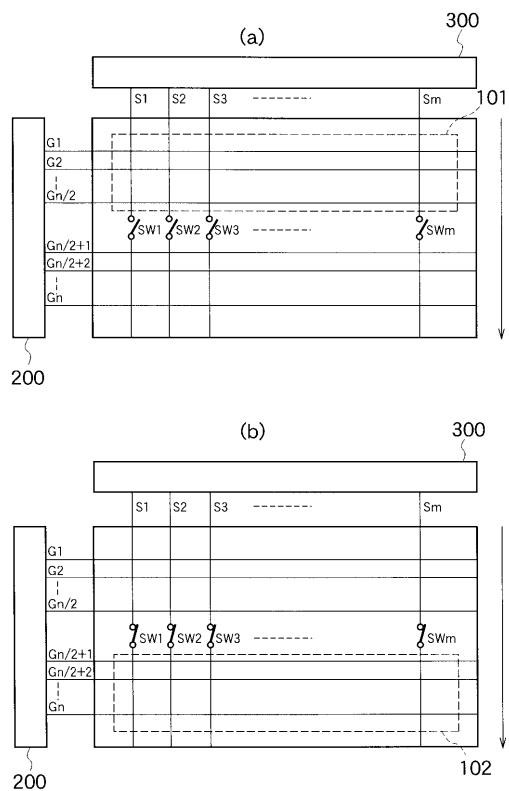

図 2 は、図 1 に示すスイッチ素子と書き込みエリアとの関係を説明するための模式図である。図 2 では、図 1 と同等部分を同一符号で示している。ただし、以下の説明においては、適宜に図 1 の符号を引用する。

40

## 【0023】

ここでは、矢印で示すスキャン方向に沿って映像信号の書き込みが行われるものとする。また画素部 100 は、スイッチ素子 SW を挟んで書き込みの前半部 101 と後半部 102 に区分されるものとし、前半部 101 は走査線 G1, G2, ... Gn / 2 の順に画素がスキャンされ、後半部 102 は走査線 Gn / 2 + 1, Gn / 2 + 2, ... Gn の順に画素がスキャンされるものとする。

## 【0024】

図 2 (a) に示すように、画素部 100 の前半部 101 への映像信号の書き込みでは、図

50

示しないコントロール I C から制御信号線 1 7 にオン信号を供給し、スイッチ素子 S W をすべて導通状態とする。これにより、信号線駆動回路 3 0 0 から信号線 S に出力された映像信号は、走査線 G 1 , G 2 , ... G n / 2 の順に各画素 1 0 に書き込まれる。

#### 【 0 0 2 5 】

次に、前半部 1 0 1 への書き込みが終了し、後半部 1 0 2 への書き込みを開始する直前で図示しないコントロール I C から制御信号線 1 7 にオフ信号を供給し、スイッチ素子 S W をすべて非導通状態とする。その後、図 2 ( b ) に示すように、画素部 1 0 0 の後半部 1 0 2 への映像信号の書き込みでは、信号線駆動回路 3 0 0 から信号線 S に出力された映像信号が、走査線 G n / 2 + 1 , G n / 2 + 2 , ... G n の順に各画素 1 0 に書き込まれる。

#### 【 0 0 2 6 】

なお、後半部 1 0 2 への書き込みの間、前半部 1 0 1 の各画素 1 0 では、先に書き込まれた映像信号が液晶容量 C 1 c と補助容量 C s に電荷として蓄積されているため、前半部 1 0 1 に続いて後半部 1 0 2 への書き込みが終了した時点で 1 フレーム分の映像表示が完成することになる。

#### 【 0 0 2 7 】

以下同様に、各フレームにおいて、書き込みの前半部 1 0 1 と後半部 1 0 2 とでスイッチ素子 S W の導通を切り替えて映像信号の書き込みを行う。この間、各画素には従来通りに映像信号が書き込まれるため、表示される映像に影響を与えることはない。

#### 【 0 0 2 8 】

上記構成によれば、書き込みの後半部 1 0 2 においてスイッチ素子 S W をすべて非導通状態とすることにより、書き込みの後半部 1 0 2 では各信号線 S の配線容量を半分にすることができる。

#### 【 0 0 2 9 】

例えば、D / A コンバータを外付け構成としたアクティブマトリクス型の液晶表示装置において、アナログ系電源ラインの消費電力は、ガラス基板全体の約 8 0 % を占めることが実験的に解明されており、このアナログ系電源ラインのうち、信号線の消費電力は約 5 0 % を占めている。そして、1 フレームの半分で信号線の配線容量を半減させることができるために、全体として信号線の容量を 1 / 2 とすることができます。

#### 【 0 0 3 0 】

ここまで全体的な電力削減の割合をまとめると次による。すなわち、アナログ系電源ラインの消費電力を全体の 8 0 % とすると、このうち信号線の消費電力は約 5 0 % を占めるため、全信号線の消費電力はパネル全体では 4 0 % ( 8 0 % / 2 ) を占めることになる。そして、1 フレームの半分で信号線の配線容量が半分となるため、消費電力は 2 0 % ( 4 0 % / 2 ) となることから、全信号線の消費電力はパネル全体では 1 0 % ( 2 0 % / 2 ) となる。このように、書き込みの後半部において信号線の配線容量を半減させることにより、パネル全体として約 1 0 % の消費電力を削減することができる。

#### 【 0 0 3 1 】

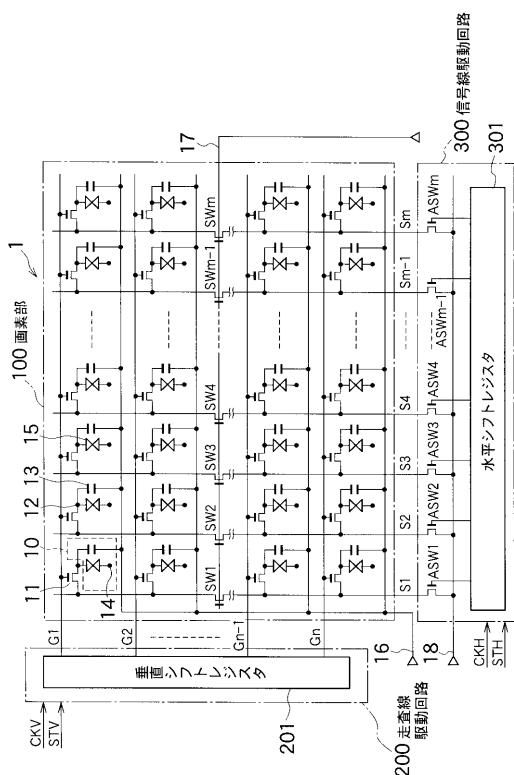

なお、本実施の形態では、画素部 1 0 0 の下部に信号線駆動回路 3 0 0 を配置して、画素部 1 0 0 を上から下方向に向かってスキャンする例について示したが、図 3 に示すように、画素部 1 0 0 の上部に信号線駆動回路 3 0 0 を配置して、画素部 1 0 0 を上から下方向に向かってスキャンするように構成することもできる。

#### 【 0 0 3 2 】

すなわち、図 3 ( a ) に示すように、画素部 1 0 0 の前半部 1 0 1 への映像信号の書き込みでは、図示しないコントロール I C から制御信号線 1 7 にオフ信号を供給し、スイッチ素子 S W をすべて非導通状態とする。これにより、信号線駆動回路 3 0 0 から信号線 S に出力された映像信号は、走査線 G 1 , G 2 , ... G n / 2 の順に各画素 1 0 に書き込まれる。

#### 【 0 0 3 3 】

次に、前半部 1 0 1 への書き込みが終了し、後半部 1 0 2 への書き込みを開始する直前で図示しないコントロール I C から制御信号線 1 7 にオン信号を供給し、スイッチ素子 S W

10

20

30

40

50

をすべて導通状態とする。その後、図3(b)に示すように、画素部100の後半部102への映像信号の書き込みでは、信号線駆動回路300から信号線Sに出力された映像信号が、走査線Gn/2+1, Gn/2+2, ... Gnの順に各画素10に書き込まれる。

#### 【0034】

この場合も、後半部102への書き込みの間、前半部101の各画素10では、先に書き込まれた映像信号が液晶容量C1cと補助容量Csに電荷として蓄積されているため、前半部101に続いて後半部102への書き込みが終了した時点で1フレーム分の映像表示が完成することになる。以下同様に、各フレームにおいて、書き込みの前半部101と後半部102とでスイッチ素子SWの導通を切り替えて映像信号の書き込みを行う。

#### 【0035】

上記構成においても、書き込みの前半部101においてスイッチ素子SWをすべて非導通状態とすることにより、書き込みの前半部101では各信号線Sの配線容量を半分にすることができる。

#### 【0036】

なお、信号線Sにスイッチ素子SWを接続する位置は、本実施の形態で示したように、画素部100内の中央部とすることが好ましいが、図1の例に限定されることなく、他の箇所に接続されていてもよい。

#### 【0037】

また、一本の信号線につき、複数のスイッチ素子を接続するように構成することもできる。

#### 【0038】

更には、制御信号線17を画素部100の左右から引き出してスイッチ素子SWをオン・オフするように構成してもよい。

#### 【0039】

#### 【発明の効果】

以上説明したように、本発明によれば、1画面分の映像信号の書き込みにおいて信号線の配線容量を半減させることができるため、大画面化した場合でも液晶表示装置を低消費電力化で駆動することができる。

#### 【図面の簡単な説明】

【図1】実施の形態に係わる液晶表示装置の回路構成を示すブロック図。

【図2】図1に示すスイッチ素子と書き込みエリアとの関係を説明するための模式図。(a)は書き込み前半部とスイッチ素子の状態を説明するための模式図。(b)は書き込み後半部とスイッチ素子の状態を説明するための模式図。

【図3】図1に示すスイッチ素子と書き込みエリアとの関係を説明するための他の模式図。(a)は書き込み前半部とスイッチ素子の状態を説明するための模式図。(b)は書き込み後半部とスイッチ素子の状態を説明するための模式図。

#### 【符号の説明】

11...画素スイッチ素子、12...画素電極、13...補助容量素子、14...対向電極、15...液晶層、16...補助容量線、17...制御信号線、18...ビデオバス、100...画素部、200...走査線駆動回路、300...信号線駆動回路、G...走査線、S...信号線、SW...スイッチ素子、ASW...アナログスイッチ

【図1】

【図2】

【図3】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 0 9 G 3/20 6 8 0 G

(74)代理人 100101247

弁理士 高橋 俊一

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 鶯 成一

埼玉県深谷市幡羅町一丁目9番地2 株式会社東芝深谷工場内

F ターム(参考) 2H093 NA16 NA21 NA43 NC22 NC34 NC35 ND39 ND43

5C006 AF51 AF53 AF61 AF69 AF71 BB16 BC03 BC11 BC20 BF03

BF14 BF24 FA01 FA47

5C080 AA10 BB05 DD26 FF11 JJ02

|                |                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 平面表示装置                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2004037648A</a>                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2004-02-05 |

| 申请号            | JP2002192313                                                                                                                                                                                                                                                                                                         | 申请日     | 2002-07-01 |

| [标]申请(专利权)人(译) | 株式会社东芝                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 东芝公司                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 鷺成一                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 鷺成一                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.A G09G3/20.621.M G09G3/20.623.X G09G3/20.680.G                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA21 2H093/NA43 2H093/NC22 2H093/NC34 2H093/NC35 2H093/ND39 2H093/ND43 5C006/AF51 5C006/AF53 5C006/AF61 5C006/AF69 5C006/AF71 5C006/BB16 5C006/BC03 5C006/BC11 5C006/BC20 5C006/BF03 5C006/BF14 5C006/BF24 5C006/FA01 5C006/FA47 5C080 /AA10 5C080/BB05 5C080/DD26 5C080/FF11 5C080/JJ02 2H193/ZA04 |         |            |

| 代理人(译)         | 三好秀<br>三好康夫<br>中村智之<br>伊藤雅一<br>高桥俊<br>高松俊夫                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

要解决的问题：提供一种有源矩阵型液晶显示装置，即使屏幕形成较大尺寸，也可以以低功耗驱动。该SOLUTION：开关元件SW ( SW1 , SW2 , ... , SWm ) 连接到信号线S的近似中心部分。所有开关元件SW在一帧的写入的前半部分101中导通并且全部开关元件SW的一部分在写入的第二半102中不导通，由此信号线S的布线容量在一帧中减半。