(19)日本国特許庁( J P )

# 公開特許公報 ( A ) (11)特許出願公開番号

特開2001 - 305579

(P2001 - 305579A)

(43)公開日 平成13年10月31日(2001.10.31)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I            | テマコード <sup>*</sup> (参考) |

|--------------------------|------|----------------|-------------------------|

| G 0 2 F 1/1368           |      | G 0 9 F 9/30   | 338 2 H 0 9 2           |

| G 0 9 F 9/30             | 338  | G 0 2 F 1/136  | 500 5 C 0 9 4           |

| H 0 1 L 21/3065          |      | H 0 1 L 21/302 | L 5 F 0 0 4             |

| 29/786                   |      |                | N 5 F 1 1 0             |

| 21/336                   |      | 29/78          | 612 D                   |

審査請求 未請求 請求項の数 50 L (全 5 数)

(21)出願番号 特願2000 - 120774(P2000 - 120774)

(71)出願人 000005821

松下電器産業株式会社

(22)出願日 平成12年4月21日(2000.4.21)

大阪府門真市大字門真1006番地

(72)発明者 米倉 広顕

大阪府門真市大字門真1006番地 松下電器

産業株式会社内

(74)代理人 100097445

弁理士 岩橋 文雄 (外2名)

最終頁に続く

(54)【発明の名称】 液晶表示装置の製造方法および製造装置

(57)【要約】 (修正有)

【課題】 従来の液晶表示装置の製造方法は、スイッチング素子の半導体層を、ドライエッチング工法を用いてパタニングする工程において、半導体層島化パターン以外の部分に、ドライエッチングプロセスにおいて発生するポリマをゲート絶縁膜上に再付着させてしまい、これが異物となって後のフォトレジストパターンの変形や、ピンホールを発生させることになり、配線間のショート不良が増加し、製造工程における歩留まりの低下を引き起こす。

【解決手段】 半導体層のパタニング時に発生するポリマを除去し、ショート不良を低減し製造工程における歩留まりの向上を達成するために、半導体層のパタニングをドライエッチ工法を利用して行い、エッチングした後、次の薄膜堆積前に希HFにてエッチングすることによって、半導体層のパタニング時に発生するポリマを除去し、配線間のショート不良を低減し製造工程における歩留まりの向上につなげる。

**【特許請求の範囲】**

【請求項1】 絶縁性透明基板上にマトリックス状に配列された複数の画素電極と、前記複数の画素電極に対応して配列された薄膜トランジスタからなる複数のスイッチング素子と、この複数のスイッチング素子のゲート電極を兼ね、前記複数のスイッチング素子に走査信号を供給する走査信号供給配線と、前記複数のスイッチング素子を介して前記複数の画素電極に映像信号を供給する映像信号供給配線と、前記複数の走査信号供給配線上に積層して前記複数のスイッチング素子のゲート絶縁膜となる第1の絶縁体層と、前記複数の映像信号供給配線上に前記複数のスイッチング素子の保護膜となる第2の絶縁体層と、前記走査信号供給配線及び映像信号供給配線及びゲート絶縁膜と同層同材料の誘電体で構成される蓄積容量を少なくともアレー部分の構成要素とし、前記薄膜トランジスタの構成要素である半導体層のパタニニングをドライエッチ工法で行い、その後、次の薄膜堆積前に希HFにてエッ칭することで、前記ゲート絶縁膜上に前記パタニニングで生じるポリマが付着することを抑制する液晶表示装置の製造方法。

【請求項2】 希HFでエッ칭する工程が、半導体層のパタニニングレジストを剥離した後に行われることを特徴とする請求項1記載の液晶表示装置の製造方法。

【請求項3】 希HFの濃度の上限値がHF:H<sub>2</sub>O=1:500であることを特徴とする請求項1記載の液晶表示装置の製造方法。

【請求項4】 請求項1から請求項3のいずれか一つに記載の液晶表示装置の製造方法を有する液晶表示装置の製造装置。

【請求項5】 請求項1から請求項3のいずれか一つに記載の液晶表示装置の製造方法で製造される液晶表示装置。

**【発明の詳細な説明】**

**【0001】**

【発明の属する技術分野】本発明は、アクティブマトリックス方式の液晶表示装置、およびその製造方法およびその製造装置に関する。

**【0002】**

【従来の技術】液晶を応用した表示装置は、低電力、軽量さと従来のディスプレイにない特徴をもち、中でも画素毎にスイッチング素子をもつ薄膜トランジスタ（以下TFTと略す）を用いたアクティブマトリックス方式の液晶表示装置は、クロストークの少ない鮮明な画像表示が得られることから、ノートパソコンやカーナビゲーションのディスプレイ等に使用され、さらに近年では大型ディスプレイモニターとして急速に利用されるようになってきた。

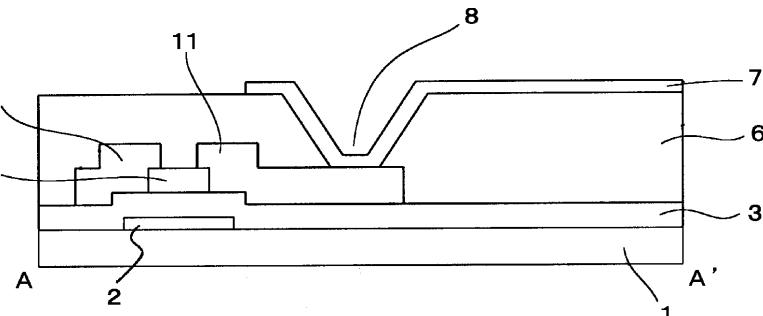

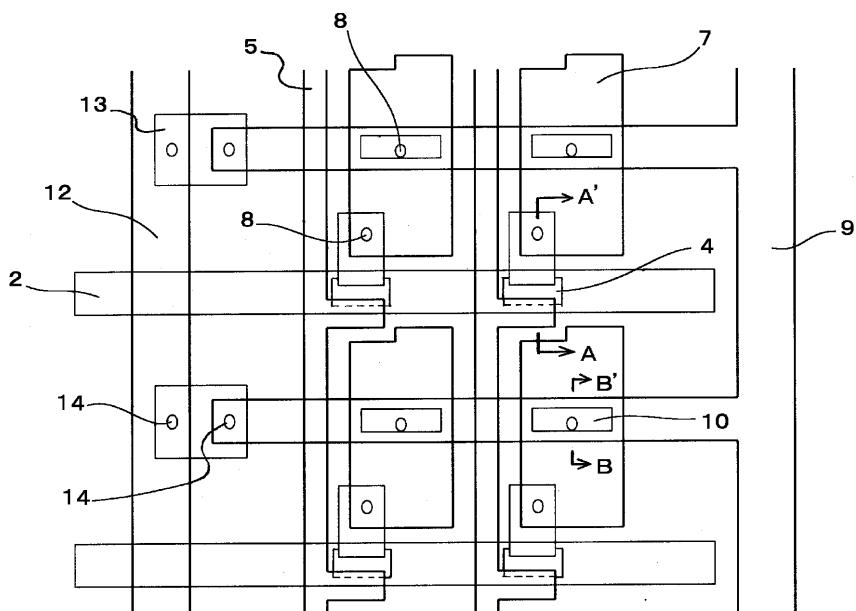

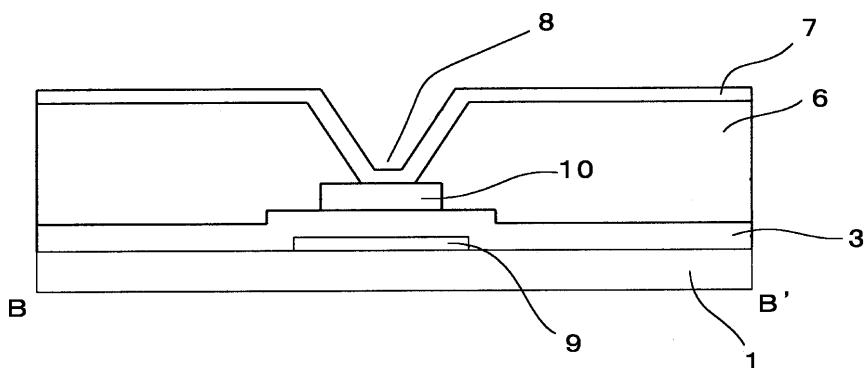

【0003】以下、従来のアクティブマトリックス方式の液晶表示装置の一例について、図面を用いて説明する。図3は従来のアクティブマトリックス方式の液晶表

示装置のTFTを有するアレー部分の概略図であり図4は図3におけるA-A'断面図である。図5は図3におけるB-B'断面図である。図中、2はアレー部分におけるガラス基板1上にマトリックス状に配列されたTFTのゲート電極を兼ね、そのTFTのゲート電極に走査信号を供給する走査信号供給配線、3は走査信号供給配線2上に積層した第1の絶縁体層で、そのTFTのゲート絶縁膜、4はTFTのゲート絶縁膜3の上に形成されたTFTのチャンネル領域を形成するアモルファシリコン半導体膜、7は複数個がマトリックス状に配列された画素電極であり、この画素電極7に対応してTFTが配列されている。

【0004】5はTFTのアモルファシリコン半導体膜4に接続したソース電極を兼ね、ドレイン電極11を介し画素電極7に第2の絶縁層の開口パタン8を通じて映像信号を供給する映像信号供給配線である。6は保護膜としてのパッシベーション絶縁膜である。10は蓄積容量上部電極である。9は共通電極信号供給配線で、走査信号供給配線2と同層かつ同時にパタン形成される。

20 12も共通電極信号供給配線で、映像信号供給配線5と同層かつ同時にパタン形成される。両者の共通電極信号供給配線は、接続部13により第2の絶縁層の開口パタン14を介して電気的に接続されている。

【0005】以上のように構成された液晶表示装置についてその動作を説明する。まず、走査信号供給配線2に電圧が印加され、TFTのアモルファシリコン半導体膜4にTFTのチャンネルが形成されると、映像信号供給配線5からの映像信号がTFTのチャンネルを通してドレイン電極11に流れ込み、画素電極7に伝わり、その画素電極7と平行に対向するカラーフィルタ部分に設けられた対向電極との間の電界により、画素電極7と対向電極の間に注入された液晶の配向を任意に可変し、光透過率を調整することによって所望の画像を作り出す。画素電極7は、蓄積容量上部電極10と接続されており、共通電極信号供給配線9との間で蓄積容量を形成し、走査信号が次のフレームで印可されるまでの間、画素電極電位を保持できるようにする。

【0006】このような液晶表示装置の作成工程としては、走査信号供給配線を選択エッチング形成する第1の工程、スイッチング素子のチャンネル部をエッチング形成する第2の工程、映像信号供給配線を選択エッチング形成する第3の工程、上記絶縁体層を選択エッチングし上記走査信号供給配線および映像信号供給配線を表面に開口する第4の工程、画素電極を選択エッチング形成する第5の工程、上記走査信号供給配線層または上記映像信号供給配線層のいずれか一方で実装端子を形成し、その上に異方性導電膜等を用いて圧着実装する第6の工程を要する。工程の順番は上記のように第1の工程から第6の工程へと行われるのが一般的である。

**【0007】**

【発明が解決しようとする課題】上記のような従来の液晶表示装置における製造方法は、スイッチング素子の半導体層層を、ドライエッチング工法を用いてパターンニングする工程において、半導体層島化パターン以外の部分に、ドライエッチングプロセスにおいて発生するポリマ（レジストとSiとドライエッチングガス成分からなる複合物）をゲート絶縁膜上に再付着させてしまい、これが異物となって後のフォトレジストパターンの変形や、ピンホールを発生させることになる。これにより、配線間のショート不良が増加し、製造工程における歩留まりの低下を引き起こす事になる。

【0008】本発明は、上記問題を解決し、半導体層のパターンニング時に発生するポリマを除去し、ショート不良を低減し製造工程における歩留まりの向上につなげることを目的とする。

#### 【0009】

【課題を解決するための手段】この目的を達成するため、半導体層のパターンニングをドライエッチ工法を利用して行い、エッチングした後、次の薄膜堆積前に希HFにてエッチングすることによって、半導体層のパターンニング時に発生するポリマを除去し、配線間のショート不良を低減し製造工程における歩留まりの向上につなげることを目的とする。

#### 【0010】

【発明の実施の形態】本発明の請求項1に記載の発明は、マトリックス状に配列された複数の画素電極と、この複数の画素電極に対応して配列されたTFTからなる複数のスイッチング素子と、この複数のスイッチング素子のゲート電極を兼ね、前記複数のスイッチング素子に走査信号を供給する走査信号供給配線と、前記複数のスイッチング素子を介して前記複数の画素電極に映像信号を供給する映像信号供給配線と、前記複数の走査信号供給配線上に積層して前記複数のスイッチング素子のゲート絶縁膜となる第1の絶縁体層と、前記複数の映像信号供給配線上に前記複数のスイッチング素子の保護膜となる第2の絶縁体層と、前記走査信号供給配線及び映像信号供給配線及びゲート絶縁膜と同層同材料の誘電体で構成される蓄積容量をアレー部分の構成要素とし、前記薄膜トランジスタの構成要素である半導体層のパターンニングをドライエッチ工法を利用して行い、エッチング後、次の薄膜堆積前に希HFにてエッチングするようにした液晶表示装置の製造方法であり、半導体層のパターンニング時に発生するポリマを除去し、配線間のショート不良を低減し製造工程における歩留まりの向上につなげることができる。

【0011】以下、本発明の実施の形態について、図面を用いて説明する。

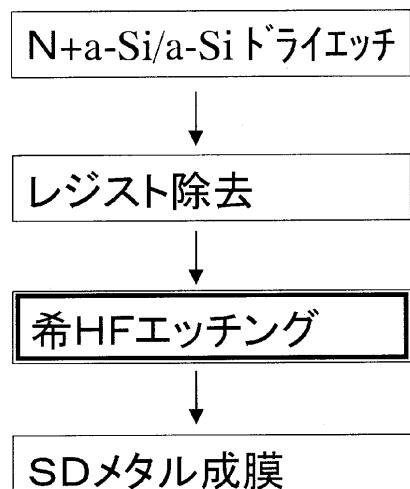

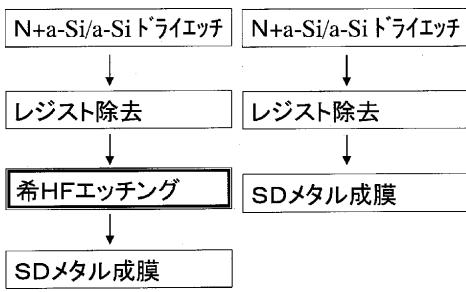

【0012】（実施の形態）図1は本発明の実施の形態におけるアクティブマトリックス方式の液晶表示装置の製造方法のうち本発明に関連する部分を示したフロー図

であり、図2は従来の液晶表示装置の製造方法のうち本発明に関連する部分と比較できる部分を示したフロー図である。図3は本発明の実施の形態におけるアクティブマトリックス方式の液晶表示装置の概略図である。図4は図3におけるA-A'の断面図である。図5は図3におけるB-B'の断面図である。図3、図4、図5の同じ部分については同じ符号を付す。

【0013】図3、図4、図5において、1はガラス基板、2はアレー部分におけるガラス基板1上にマトリックス状に配列されたTFTのゲート電極を兼ね、そのTFTのゲート電極に走査信号を供給する走査信号供給配線、3は走査信号供給配線2上に積層した第1の絶縁体層で、そのTFTのゲート絶縁膜、4はTFTのゲート絶縁膜3の上に形成されたTFTのチャンネル領域を形成するアモルファスシリコン半導体膜、5はTFTのアモルファスシリコン半導体膜4に接続したソース電極を兼ね、ドレイン電極11を介して画素電極7に映像信号を供給する映像信号供給配線、11はTFTのアモルファスシリコン半導体膜4に接続したドレイン電極、7は複数個がマトリックス状に配列された画素電極であり、この画素電極7に対応してTFTが配列されている。

【0014】6は保護膜で例えばSiN<sub>x</sub>、SiO<sub>2</sub>、アクリル樹脂、ポリイミド、ポリアミド、ポリカーボネートまたはこれらの積層膜であり、TFTのパッシベーション絶縁膜である。10は蓄積容量上部電極である。9は共通電極信号供給配線で、走査信号供給配線2と同層かつ同時にパターン形成される。12も共通電極信号供給配線で、映像信号供給配線5と同層かつ同時にパターン形成される。両者の共通電極信号供給配線は、接続部13により第2の絶縁層の開口パターン14を介して電気的に接続されている。8は第2の絶縁膜であるパッシベーション絶縁膜を開口除去したパターンで、このパターンを介して画素電極とドレイン電極または蓄積容量上部電極10を電気的に接続させる。

【0015】このような構成の液晶表示装置のアレー基板作成方法としてまず、ガラス基板1上に走査信号供給配線2をスパッタリング成膜法にて薄膜堆積を行いフォトリソ工程、エッチング工程にて走査信号供給配線2のパターンニングを行う。このような薄膜堆積、フォトリソ工程、エッチング工程のパターンニングを繰り返しアモルファスシリコン半導体膜4、及び映像信号供給配線5及びドレイン電極11及び蓄積容量上部電極10及び画素電極7を形成する。

【0016】このようななかで、半導体層の島化パターンニングにおいて優れたテーパー形状を得るためにフッ素系のガスを用いたドライエッチ工法を採用することが多い。

【0017】図1は上記アレー基板作成方法の内、半導体層の島化パターンニングエッチングからソース、ドレイン電極層成膜までの工程フローを示す。前述のように、

この間の工程としては、半導体層をフッ素系のガスを用いてドライエッチングする工程、フォトレジストを剥離する工程、ソース、ドレイン電極層を成膜する工程をこの順で含む。

【0018】ここまで説明した工程フローは従来例を示す図2と同じであり、本実施の形態を示す図1が従来例を示す図2と異なるところは以下の通りである。すなわち、従来の液晶表示装置における製造方法は、スイッチング素子の半導体層層を、ドライエッチング工法を用いてパターンニングする工程において、半導体層島化パターン以外の部分に、ドライエッチングプロセスにおいて発生するポリマ（レジストとSiとドライエッチングガス成分からなる複合物）をゲート絶縁膜上に再付着させてしまい、これが異物となって後のフォトレジストパターンの変形や、ピンホールを発生させることになる。

【0019】これにより、配線間のショート不良が増加し、製造工程における歩留まりの低下を引き起こす事になる。これに対し、本発明は図1に示すように、半導体層のパターンニングをドライエッチ工法を利用して行い、エッチングした後、次の薄膜堆積前に希HFにてエッチングすることによって、半導体層のパターンニング時に発生するポリマを除去し、配線間のショート不良を低減し製造工程における歩留まりの向上につなげることができる。

#### 【0020】

【発明の効果】以上のように本発明によれば、半導体層のパターンニングをドライエッチ工法を利用して行い、エッチングした後、次の薄膜堆積前に希HFにてエッチング

\*グすることによって、半導体層のパターンニング時に発生するポリマを除去し、配線間のショート不良を、画面サイズが15インチ程度の液晶表示装置において従来は10%以上であったが、3%以下にまで低減することができ、産業的価値が大きい。

#### 【図面の簡単な説明】

【図1】本発明の実施の形態における液晶表示装置の製造方法の一部フロー図

【図2】従来の液晶表示装置の製造方法の一部フロー図

【図3】従来の液晶表示装置の一部概略図

【図4】従来の液晶表示装置の一部断面図

【図5】従来の液晶表示装置の一部断面図

#### 【符号の説明】

- 1 ガラス基板

- 2 走査信号供給配線

- 3 第1絶縁膜

- 4 アモルファスシリコン半導体膜

- 5 映像信号供給配線

- 6 第2絶縁膜

- 7 画素電極

- 8 画素電極／ドレイン電極及び蓄積容量上部電極コンタクトパターン

- 9 共通電極信号供給配線

- 10 蓄積容量上部電極

- 11 ドレイン電極

- 12 共通電極信号供給配線

- 13 接続部

- 14 共通電極信号供給配線間コンタクトパターン

【図1】

【図2】

【図4】

【圖3】

【図5】

## フロントページの続き

F ターム(参考) 2H092 JA24 KA05 KA07 MA05 MA18

NA16 NA29

5C094 AA21 AA42 BA03 BA43 CA19

DA09 EA04 EA07 HA05 HA08

5F004 AA09 DB02 DB30 EA10 EB01

EB02 EB03

5F110 AA26 BB01 CC07 DD02 EE44

GG02 GG15 NN03 NN23 NN24

NN27 NN73 QQ04

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 用于制造液晶显示装置的方法和设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号     | <a href="#">JP2001305579A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2001-10-31 |

| 申请号         | JP2000120774                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2000-04-21 |

| 申请(专利权)人(译) | 松下电器产业有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人      | 米倉 広顕                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人         | 米倉 広顕                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号      | G02F1/136 G02F1/1368 G09F9/30 H01L21/302 H01L21/3065 H01L21/336 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F1分类号       | G09F9/30.338 G02F1/136.500 H01L21/302.L H01L21/302.N H01L29/78.612.D G02F1/1368 H01L21/302.105.B                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-Term分类号   | 2H092/JA24 2H092/KA05 2H092/KA07 2H092/MA05 2H092/MA18 2H092/NA16 2H092/NA29 5C094 /AA21 5C094/AA42 5C094/BA03 5C094/BA43 5C094/CA19 5C094/DA09 5C094/EA04 5C094/EA07 5C094/HA05 5C094/HA08 5F004/AA09 5F004/DB02 5F004/DB30 5F004/EA10 5F004/EB01 5F004 /EB02 5F004/EB03 5F110/AA26 5F110/BB01 5F110/CC07 5F110/DD02 5F110/EE44 5F110/GG02 5F110/GG15 5F110/NN03 5F110/NN23 5F110/NN24 5F110/NN27 5F110/NN73 5F110/QQ04 2H192 /AA24 2H192/BC31 2H192/CB05 2H192/CC04 2H192/DA12 2H192/DA42 2H192/FA35 2H192/FA46 2H192/GA42 2H192/HA63 2H192/HA80 |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

## 摘要(译)

( 带更正 ) 在用于制造液晶显示装置的常规方法中，在使用干蚀刻方法对开关元件的半导体层进行图案化的步骤中，将在干蚀刻工艺中产生的聚合物施加到除半导体层岛图案以外的部分上。栅极绝缘膜上的再沉积导致异物变形并且光致抗蚀剂图案变形并且产生针孔，这增加了布线之间的短路缺陷并降低了制造过程中的成品率。原因 解决方案：为了除去在对半导体层进行构图时生成的聚合物，减少短路缺陷并提高制造过程中的成品率，可使用干蚀刻方法对半导体层进行构图。之后，通过在下一次薄膜沉积之前用稀HF进行蚀刻，去除了在半导体层的图案化过程中产生的聚合物，减少了布线之间的短路缺陷，并且提高了制造工艺中的成品率。