(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2001 - 332739

(P2001 - 332739A)

(43)公開日 平成13年11月30日(2001.11.30)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I            | テ-マコード <sup>*</sup> (参考) |

|--------------------------|------|----------------|--------------------------|

| H 0 1 L 29/786           |      | H 0 1 L 21/20  | 2 H 0 9 2                |

| G 0 2 F 1/1368           |      | 29/78          | 626 C 5 F 0 0 4          |

| H 0 1 L 21/20            |      | G 0 2 F 1/136  | 500 5 F 0 5 2            |

| 21/3065                  |      | H 0 1 L 21/302 | J 5 F 1 1 0              |

| 21/336                   |      | 29/78          | 627 G                    |

審査請求 未請求 請求項の数 170 L (全 10数)

(21)出願番号 特願2000 - 152882(P2000 - 152882)

(22)出願日 平成12年5月24日(2000.5.24)

(71)出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目2番3号

(71)出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(72)発明者 高鍋 昌一

東京都千代田区丸の内二丁目2番3号 三菱

電機株式会社内

(74)代理人 100064746

弁理士 深見 久郎 (外4名)

最終頁に続く

(54)【発明の名称】薄膜トランジスタおよび液晶表示装置ならびにそれらの製造方法

(57)【要約】

【課題】オフ電流  $I_{off}$  および S 値がともに低く、p 型 TFT と n 型 TFT の  $V_{th}$  の対称性が良好な TFT、LCD およびそれらの製造方法を提供する。

【解決手段】この TFT の製造方法は、基板 1 の上に下地膜 2 を形成する工程と、下地膜を 500 以上に加熱する工程と、加熱された下地膜の上にトランジスタを形成するシリコン膜 30a を成膜する工程とを備える。

## 【特許請求の範囲】

【請求項1】 基板の上に下地膜を形成する工程と、前記下地膜を500以上に加熱する工程と、前記加熱された下地膜の上にトランジスタ形成用のシリコン膜を成膜する工程とを備える、薄膜トランジスタの製造方法。

【請求項2】 前記500以上の加熱が、レーザ照射によってなされる、請求項1に記載の薄膜トランジスタの製造方法。

【請求項3】 前記500以上の加熱が、R T A (Rapid Thermal Annealing)によってなされる、請求項1に記載の薄膜トランジスタの製造方法。 10

【請求項4】 基板の上に下地膜を形成する工程と、前記下地膜の上にアモルファスシリコン膜を成膜する工程と、

前記アモルファスシリコン膜をレーザ照射した後、そのレーザ照射されたシリコン膜を除去する工程と、前記シリコン膜を除去した後の前記下地膜の上にトランジスタ形成用のシリコン膜を成膜する工程とを備える、薄膜トランジスタの製造方法。 20

【請求項5】 基板の上に下地膜を形成する工程と、前記下地膜の上にアモルファスシリコン膜を成膜する工程と、

前記アモルファスシリコン膜を除去する工程と、前記アモルファスシリコン膜が除去された後の前記下地膜をレーザ照射する工程と、前記レーザ照射された後の下地膜の上にトランジスタ形成用のシリコン膜を成膜する工程とを備える、薄膜トランジスタの製造方法。 30

【請求項6】 前記レーザ照射されたシリコン膜またはアモルファスシリコン膜の除去は、ウェットエッチャリングによってなされる、請求項4または5に記載の薄膜トランジスタの製造方法。 30

【請求項7】 前記下地膜は、シリコン酸化膜およびシリコン酸化膜とシリコン窒化膜との2層膜、のうちのいずれか一方である、請求項1～6のいずれかに記載の薄膜トランジスタの製造方法。

【請求項8】 前記トランジスタ形成用のシリコン膜を成膜する工程は、減圧CVDによりアモルファスシリコン膜を成膜した後、レーザ照射により結晶化して多結晶体シリコン膜を形成する工程を有する、請求項1～7のいずれかに記載の薄膜トランジスタの製造方法。 40

【請求項9】 前記下地膜を形成する工程の前に、前記基板上に熱吸収の高い薄膜を形成する工程を備える、請求項1～8のいずれかに記載の薄膜トランジスタの製造方法。

【請求項10】 前記下地膜へのレーザ照射は、炭酸ガスレーザ発振装置を用いて行う、請求項2、5、6、7、8または9のいずれかに記載の薄膜トランジスタの製造方法。 \*50

\*【請求項11】 前記請求項1～10のいずれかに記載の薄膜トランジスタの製造方法を用いて、液晶の下方の下部基板の駆動回路領域および画素領域に薄膜トランジスタを設ける、アクティブマトリックス方式の液晶表示装置の製造方法。

【請求項12】 トランジスタの主要部であるシリコン膜が接している前記下地膜の表面における組成、結晶構造および電子構造のうち、少なくともいずれか一つが、下地膜の上へのシリコン膜の成膜とその除去を行わずにトランジスタ形成用シリコン膜を成膜した薄膜トランジスタにおける下地膜とは、相違している、薄膜トランジスタ。

【請求項13】 トランジスタの主要部であるシリコン膜が接している前記下地膜の表面における組成、結晶構造および電子構造のうち、少なくともいずれか一つが、下地膜への加熱処理を行わずにトランジスタ形成用シリコン膜を成膜した薄膜トランジスタにおける下地膜とは、相違している、薄膜トランジスタ。

【請求項14】 前記シリコン膜が接している下地がシリコン酸化膜である、請求項12または13に記載の薄膜トランジスタ。 20

【請求項15】 前記シリコン膜が、下地膜の表面に成膜されたアモルファスシリコン膜がレーザアニールにより多結晶体シリコン膜とされたシリコン膜である、請求項12～14のいずれかに記載の薄膜トランジスタ。

【請求項16】 前記下地膜の下に熱吸収性の良い膜を備えている、請求項12～15のいずれかに記載の薄膜トランジスタ。

【請求項17】 前記請求項12～16のいずれかに記載の薄膜トランジスタを、液晶の後方の下部基板の駆動回路領域および画素領域に備えている、アクティブマトリックス方式の液晶表示装置。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は、薄膜トランジスタ(TFT:Thin Film Transistor)およびそのTFTを搭載した液晶表示装置(LCD:Liquid Crystal Display)ならびにそれらの製造方法に関する。

## 【0002】

【従来の技術】アクティブマトリックス方式のLCDでは、画素領域の画素ごとに2個ずつのn型TFTを、また駆動回路領域にn型TFTとp型TFTとを備えて、画像信号に応じて各画素領域の液晶に電圧を印加し、光を変調し表示画面を形成している。これらのTFTを形成する場合、アモルファスシリコン膜からレーザアニール等によって結晶化された多結晶体シリコン膜にTFTを形成する方法が用いられている。

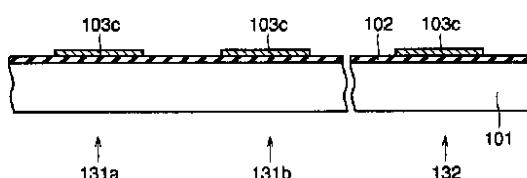

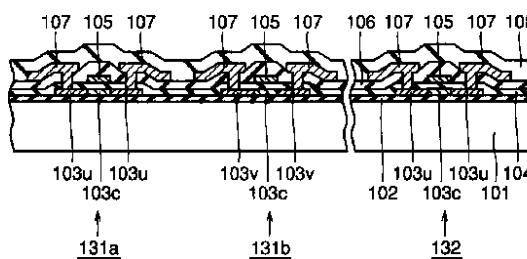

【0003】図17～図22を用いて、従来のLCDの製造方法の概略を説明する。まず、ガラス基板101の表面に下地膜102を成膜する(図17)。次いで、こ

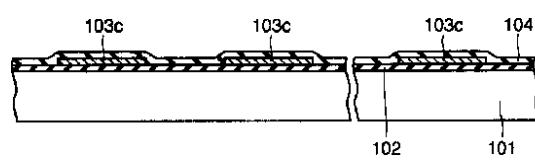

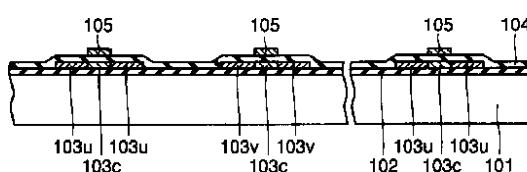

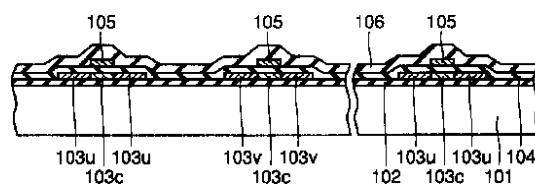

の下地膜102の表面にアモルファスシリコン膜103aを成膜し、レーザアニール等により結晶化して多結晶体シリコン膜とし、パターニングによりチャネル形状103cを形成する(図18)。次いで、多結晶体シリコン膜のチャネル形状103cと下地膜102との表面にゲート絶縁膜104を成膜する(図19)。次いで、レジスト(図示せず)によりp型TFT131bの上を覆って、画素領域のn型TFT132および駆動回路領域のn型TFT131aのソース、ドレン領域にn型不純物を高濃度に打ち込み、n+型不純物領域103uを形成する。次いで、駆動回路領域および画素領域のn型TFT131a, 132の上をレジストで覆って、駆動回路領域のp型TFT131bのソース、ドレン領域にp型不純物、例えばBイオンを打ち込み、ソース、ドレン領域103vを形成する(図20)。その後、図21に示すように、層間絶縁膜106を成膜し、次いで、ソース、ドレン領域の上の層間絶縁膜にコンタクトホールを開口する。次に、このコンタクトホールを埋めるように導電膜を成膜して、ソース、ドレン電極配線107を形成した後、パッシベーション膜108を成膜する(図22)。さらに、この上に下部電極を形成して、下部基板の骨格を完成する。

【0004】上記した下部基板と所定のギャップをあけて上部電極を備える上部基板を設け、そのギャップに液晶を注入する。表示画面は、上記の下部基板上のTFTに加えられる画像信号に基いて、上記TFTにより液晶に電圧を印加して光を変調させることにより形成される。

【0005】従来、上記TFT用のアモルファスシリコン膜を成膜する際、TFTの電気特性のばらつきを抑制するために、下地膜とアモルファスシリコン膜とを連続して、大気開放なしに形成する必要があった。大気開放されると、下地膜の表面にパーティクル等の塵芥が載り、正常な成膜を行うことができない。下地膜とアモルファスシリコン膜とを連続して大気開放なしに形成するためには、アモルファスシリコン膜を下地膜と同じプラズマCVD装置によって形成しなければならない。しかし、プラズマCVD装置によってアモルファスシリコン膜を形成すると、TFTにおけるキャリアの移動度の低下を伴う問題があった。したがって、現状は、やむをえず下地膜を形成した後、一度、大気にさらした後、減圧CVDにより下地膜の上にアモルファスシリコン膜を形成している。この方法によれば、キャリア移動度の高いTFTを得ることが可能となる。

#### 【0006】

【発明が解決しようとする課題】しかしながら、上記の方法で得られたp型TFTは、オフ電流Ioffが高く、かつS値が大きいという問題があった。S値は、ドレン電流Idを1桁(1Dec)上げるために必要なゲート電圧上昇分であり、この値が小さいほうが、小さなゲート

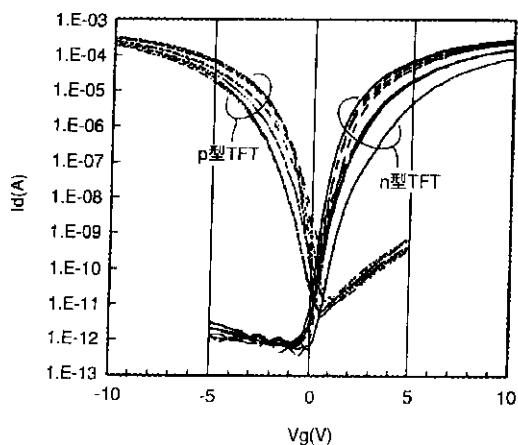

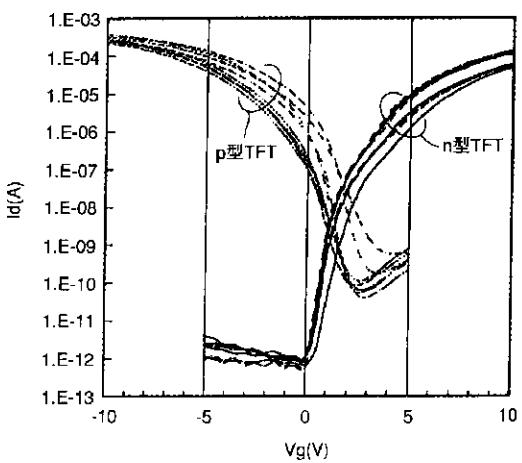

電圧上昇で同じドレン電流を制御することができるので、好ましい。また、p型TFTとn型TFTとのV<sub>th</sub>の中心値がゼロからずれていた。図23は、下地膜をプラズマCVDによって成膜した後に、大気にさらし、次いで減圧CVDによりアモルファスシリコン膜を成膜して作製したn型TFTおよびp型TFTのドレン電流Idとゲート電圧Vgとの関係を示す図である。p型TFTのオフ電流Ioffは高く、ドレン電流を1桁上昇させるのに必要なゲート電圧上昇分であるS値が高いことが分かる。Ioffが高いことは、誤動作の原因と消費電力の増大につながる。また、S値が高いことは、上記したように、ゲート電圧印加によるドレン電流の制御性が劣ることを意味する。また、p型TFTとn型TFTとのV<sub>th</sub>の中心値はゼロから大きく偏倚している。これらの電気特性はTFTやLCDの基本性能に関わるものであり、上記の特性の改善要求が強く出されていた。

【0007】本発明は、オフ電流Ioff、およびドレン電流を1オーダー上げるのに必要なゲート電圧上昇分であるS値、をともに低くし、かつp型TFTとn型TFTのV<sub>th</sub>の中央値がゼロに近いTFT、およびそのTFTを搭載したLCDならびにそれらの製造方法を提供することを目的とする。

#### 【0008】

【課題を解決するための手段】本発明の第1の局面のTFTの製造方法は、基板の上に下地膜を形成する工程と、下地膜を500以上に加熱する工程と、加熱された下地膜の上にトランジスタ形成用のシリコン膜を成膜する工程とを備える(請求項1)。

【0009】下地膜が500以上に加熱されることにより、下地膜が改質処理されて膜質の優れたトランジスタ形成用シリコン膜を成膜することができる。本発明者らは、450の加熱では不充分であり、500以上の加熱で効果が生じることを確認している。この結果、TFTのうちでもとくにp型TFTのオフ電流IoffおよびS値の両方をともに低減することができる。また、n型TFTおよびp型TFTのしきい値電圧V<sub>th</sub>の中心をゼロ付近にすることができる、駆動回路領域にこれらのTFTを並置して、無駄のない小さい振幅の正負の電圧切換えを行うことが可能となる。

【0010】上記第1の局面のTFTの製造方法では、500以上の加熱が、レーザ照射によってなされている(請求項2)。

【0011】上記レーザ照射により、下地膜表面の改質処理が促進され、良好な膜質のシリコン膜が成膜され、その結果、オフ電流Ioffが低く、ゲート電圧によるドレン電流の制御が良く効くp型TFTが形成される。また、p型TFTとn型TFTのV<sub>th</sub>の中央値をゼロ付近にすることができる。

【0012】上記第1の局面のTFTの製造方法では、500以上の加熱が、RTA(Rapid Thermal Anneal)

ng)によってなされている(請求項3)。

【0013】上記のRTAはランプアニールによりなされるので、簡便に下地膜の改質処理を行うことができ、 $I_{off}$ およびS値を低くすることができる。

【0014】本発明の第2の局面のTFTの製造方法は、基板の上に下地膜を形成する工程と、下地膜の上にアモルファスシリコン膜を成膜する工程と、アモルファスシリコン膜をレーザ照射した後、そのレーザ照射されたシリコン膜を除去する工程と、シリコン膜を除去した後の下地膜の上にトランジスタ形成用のシリコン膜を成膜する工程とを備える(請求項4)。

【0015】上記の構成により、アモルファスシリコン膜が形成され、レーザアニールにより結晶化され、次いで除去されるという工程により、加熱のみの処理とは異なる方法により下地膜の改質処理がなされる。この結果、下地膜の表面の組成、結晶構造、電子構造等が改質される。このため、トランジスタ形成用に良好な膜質のシリコン膜が成膜され、p型TFTの $I_{off}$ やS値を低下させ、p型TFTとn型TFTの $V_{th}$ の中心値をゼロ付近にすることが可能となる。

【0016】本発明の第3の局面のTFTの製造方法は、基板の上に下地膜を形成する工程と、下地膜の上にアモルファスシリコン膜を成膜する工程と、アモルファスシリコン膜を除去する工程と、アモルファスシリコン膜が除去された後の下地膜をレーザ照射する工程と、レーザ照射された後の下地膜の上にトランジスタ形成用のシリコン膜を成膜する工程とを備える(請求項5)。

【0017】上記方法により、下地膜の独特的な改質効果を得ることができ、上記改質処理がなされた下地膜の表面に形成されるp型TFTは、さらに良好なレベルに改善されて、より低い $I_{off}$ とより低いS値を確保することができる。また、p型TFTとn型TFTの $V_{th}$ の中心値をよりゼロ付近に近づけることが可能となる。

【0018】上記第2および第3の局面のTFTの製造方法では、レーザ照射されたシリコン膜またはアモルファスシリコン膜の除去は、ウエットエッティングによってなされている(請求項6)。

【0019】ウエットエッティングではエッティングの選択性を大きくできるエッチャントが豊富にあり、他の部分に影響しないで、上記レーザ照射されたシリコン膜またはレーザ照射なしのアモルファスシリコン膜を完全に除去することができる。そのため、残存物等を残さずにクリーンに改質処理を進行させることができる。

【0020】上記第1～第3の局面のTFTの製造方法では、下地膜は、シリコン酸化膜およびシリコン酸化膜とシリコン窒化膜との2層膜、のうちのいずれか一方である(請求項7)。

【0021】本発明における改質処理は、シリコン酸化膜が下地膜である場合に良好な結果をもたらす場合が多い。このため、下地膜のシリコン酸化膜における過剰な

10

20

30

40

50

酸素が、アモルファスシリコン膜を成膜して除去することで是正される現象や、加熱により過剰な酸素がガスとして除去されることなどが考えられる。上記構成により、本発明の下地膜改質処理によって確実に良好な結果を得ることができる。すなわち、p型TFTにおける低い $I_{off}$ および低いS値を得ることができ、かつ、n型TFTとp型TFTの $V_{th}$ の中央値をゼロ付近にすることができる。

【0022】上記第1～第3の局面のTFTの製造方法では、トランジスタ形成用のシリコン膜を成膜する工程は、減圧CVDによりアモルファスシリコン膜を成膜した後、レーザ照射により結晶化して多結晶体シリコン膜を形成する工程を有している(請求項8)。

【0023】上記構成により、上記の効果をもたらす下地膜の改質処理を行ったうえで、大面積にわたってTFTを形成することが可能となる。また、本発明の下地膜の改質は、アモルファスシリコン膜をレーザ照射して多結晶体シリコン膜にする過程を含む場合に、上記した効果が明りょうに現れる。

【0024】上記第1～第3の局面のTFTの製造方法では、下地膜を形成する工程の前に、基板上に熱吸収の高い薄膜を形成する工程を備えている(請求項9)。

【0025】上記構成により、加熱による下地膜の改質処理が効果的に行われ、n型TFTとp型TFTの $V_{th}$ の中心値をゼロ付近にすることができる。

【0026】上記第1および第2の局面のTFTの製造方法では、下地膜へのレーザ照射は、炭酸ガスレーザ発振装置を用いて行われる(請求項10)。

【0027】下地膜としてはシリコン酸化膜が一般的であり、そのシリコン酸化膜の熱吸収は、波長が約10μmの光に対して大きい。このため、炭酸ガスレーザ発振装置により、約10μmの波長のレーザを発振させ、シリコン酸化膜に照射することにより、シリコン酸化膜に効率よく熱吸収が行われ、上記の効果を確実に得ることができる。

【0028】上記第1～3の局面のいずれかのTFTの製造方法を用いて、液晶の下方の下部基板の駆動回路領域および画素領域に薄膜トランジスタを設ける、アクティブラチックス方式のLCDの製造方法(請求項11)。

【0029】この製造方法により、駆動回路領域に並置されるn型TFTとp型TFTの $V_{th}$ の中間値をゼロ付近にすることでき、液晶への交互の正負電圧の印加を小さな振幅で効率よく行うことができる。また、p型TFTのオフ電流 $I_{off}$ を低減し、S値を減少させることができる。この結果、消費電力を抑制することができ、かつゲート電圧によるチャネル駆動性を良好なものとすることが可能となる。

【0030】本発明の第1の局面のTFTは、トランジスタの主要部であるシリコン膜が接している下地膜の表

面における組成、結晶構造および電子構造のうち、少なくともいづれか一つが、下地膜の上へのシリコン膜の成膜とその除去を行わずにトランジスタ形成用シリコン膜を成膜したTFTにおける下地膜とは、相違している（請求項12）。

【0031】本発明における表面改質の原因は、上記の下地の表面における組成、結晶構造および電子構造のうち、少なくともいづれか一つが改良された結果である。これらの要因は、表面改質処理を行わずにトランジスタ形成用シリコン膜を成膜して形成されたTFTにおける値と明確に相違している。これらの相違が原因となって、上記の $I_{off}$ および $S$ 値の低下、およびp型TFTとn型TFTの $V_{th}$ の良好な対称性を得ることができる。

【0032】本発明の第2の局面のTFTは、トランジスタの主要部であるシリコン膜が接している下地膜の表面における組成、結晶構造および電子構造のうち、少なくともいづれか一つが、下地膜への加熱処理を行わずにトランジスタ形成用シリコン膜を成膜したTFTにおける下地膜とは、相違している（請求項13）。

【0033】上記構成は、改質処理として、下地膜への加熱処理が行われたTFTの構成を示す。本発明におけるこの構成上の相違により、上記特性の改良を得ることができる。

【0034】上記第1および第2の局面におけるTFTでは、シリコン膜が接している下地がシリコン酸化膜である（請求項14）。

【0035】シリコン酸化膜表面の改質により、オフ電流が低く、 $S$ 値の低いp型TFTを得ることができ、かつp型TFTとn型TFTの $V_{th}$ の中央値をゼロ付近にすることができる。

【0036】上記第1および第2の局面の薄膜トランジスタでは、シリコン膜が、下地膜の表面に成膜されたアモルファスシリコン膜がレーザアニールにより多結晶体シリコン膜とされたシリコン膜である（請求項15）。

【0037】下地膜の改質は、上記のアモルファスシリコン膜の成膜およびレーザアニールによる多結晶体シリコン膜への結晶化の過程を通じて、上記の効果を発現する場合が多い。したがって、上記の構成により、TFTにおける $I_{off}$ および $S$ 値の低下、ならびにp型TFTとn型TFTの $V_{th}$ の良好な対称性を、より確実に得ることが可能となる。

【0038】上記第1および第2の局面の薄膜トランジスタでは、下地膜の下に熱吸収性の良い膜を備えている（請求項16）。

【0039】上記の構成により、下地膜の改質を効率良く行うことができる。アクティブラトリックス方式のLCDは、上記第1および第2の局面のいづれかのTFTを、液晶の後方の下部基板の駆動回路領域および画素領域に備えていることが望ましい（請求項17）。

【0040】駆動回路領域に並置されるn型TFTとp型TFTの $V_{th}$ の中間値を、ゼロ付近にすることができ、液晶への交互の正負電圧の印加を効率よく行うことができる。また、p型TFTのオフ電流 $I_{off}$ を低減し、 $S$ 値を減少させることができる。この結果、消費電力を抑制することができ、かつゲート電圧によるチャネル駆動性を良好なものとすることができる。

#### 【0041】

【発明の実施の形態】次に、本発明の実施の形態について図面を用いて説明する。

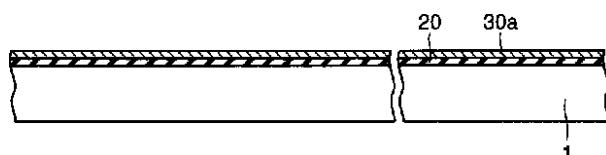

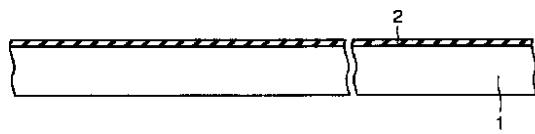

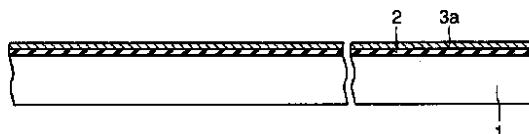

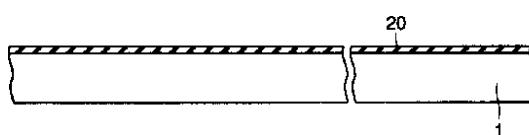

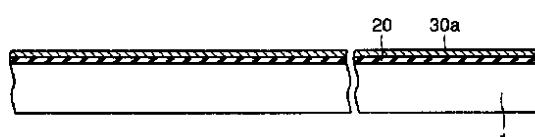

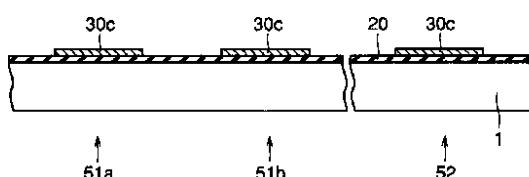

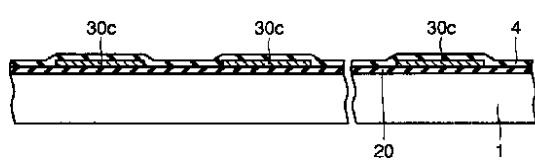

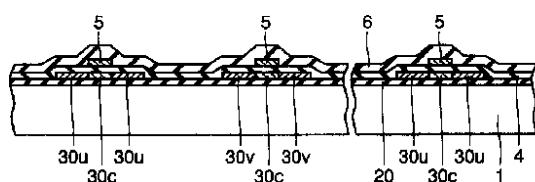

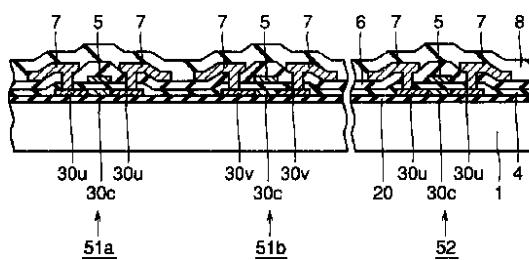

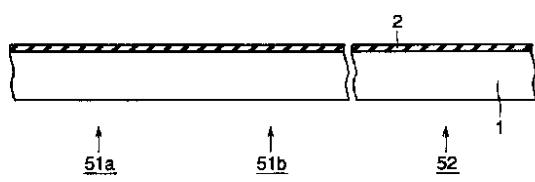

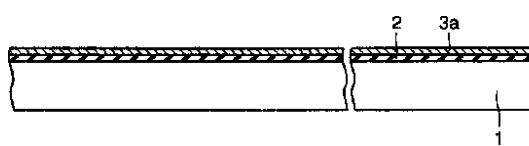

【0042】（実施の形態1）図1～図10に本発明の実施の形態1におけるLCDの製造方法を説明する。まず、ガラス基板1の表面に下地膜2として、シリコン酸化膜を上層とする（シリコン酸化膜/シリコン窒化膜）の2層膜をプラズマCVD装置により成膜する（図1）。その後、図2に示すように、プリカーサのアモルファスシリコン膜3aを減圧CVD装置により成膜し、その後、そのアモルファスシリコン膜3aにエキシマレーザ照射を行い、結晶化して多結晶体シリコン膜3bを得る（図3）。さらに、この多結晶体シリコン膜をウエットエッティングによって除去する（図4）。この改質処理によって、上記シリコン酸化膜の表面の組成が変化したり、結晶構造や電子構造が変化したりする。この改質処理を受けた下地膜を符号20によって表示する。このシリコン酸化膜の表面改質処理の後、再び、図5に示すように、減圧CVD装置を用いてシリコン酸化膜の表面にトランジスタ形成用のアモルファスシリコン膜30aを成膜し、エキシマレーザを用いたレーザアニールにより結晶化して多結晶体シリコン膜とする。この後、図6に示すように、上記の多結晶体シリコン膜をチャネル形状30cにパターニングした後、この上にゲート絶縁膜4としてシリコン酸化膜をプラズマCVDにより成膜する（図7）。

【0043】その後、ゲート電極膜としてAl合金、Cr、Taのような金属膜をスパッタリングにより成膜し、パターニングおよびエッティング加工により、ゲート電極5を形成する（図8）。この後、p型TFTの領域51bはレジスト（図示せず）で覆い、n型TFTのソース、ドレイン領域にn型不純物を打ち込み、ソース、ドレイン領域30uを形成する。次いで、n型TFTの領域51a、52をレジスト（図示せず）で覆い、p型不純物をp型TFTのソース、ドレイン領域に打ち込み、ソース、ドレイン領域30vを形成する（図8）。次いで、層間絶縁膜6をプラズマCVD装置によって成膜する（図9）。つぎに、層間絶縁膜6にコンタクトホールを開口し、ソース、ドレイン配線用の導電膜を成膜後に、ソース、ドレイン配線7にパターニングする。つぎに、最後のプラズマCVDによってパッシベーション膜8であるSiN膜を成膜する（図10）。

【0044】この後、下部電極を形成し、この下部基板

と所定のギャップをあけて上部電極を備える上部基板を設け、そのギャップに液晶を注入する。表示画面は、上記TFTに加えられる画像信号に基いて、上記TFTにより液晶に電圧を印加して光を変調させることにより形成される。

【0045】本発明に基き、下地膜（シリコン酸化膜/シリコン窒化膜）の上にアモルファスシリコン膜を成膜し、レーザ照射により多結晶体シリコン膜とした後に除去する改質処理を行ったTFTの6例についての特性を図11に示す。従来の製造方法による多結晶体シリコンTFTの特性を示す図23と比較することにより、本実施の形態における多結晶体シリコンTFTのオフ電流 $I_{off}$ は低く、ゲート電圧の制御性の指標であるS値も良好であることが分かる。また、図11においては、n型TFTとp型TFTの $V_{th}$ の中央値がゼロ付近にあり、LCDの駆動回路として用いるのに適していることが分かる。

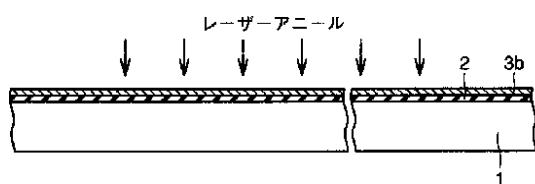

【0046】（実施の形態2）本実施の形態では、アモルファスシリコン膜の成膜後、そのアモルファスシリコン膜をウエットエッティングにより除去し、下地膜であるシリコン酸化膜にレーザ照射を施す点に特徴がある。まず、図12に示すように、ガラス基板1の表面に、下地膜2としての（シリコン酸化膜/シリコン窒化膜）の2層膜をプラズマCVDによって成膜する。その後、図13に示すように、アモルファスシリコン膜3aを減圧CVDで成膜し、次いでウエットエッティングによりそのアモルファスシリコン膜を除去する（図14）。この時点の下地膜19は、改質処理がすでになされているが完了していない改質途中の下地膜である。次に、露出されたシリコン酸化膜にアモルファスシリコン膜の多結晶体化と同じ条件でレーザ照射を施す。この時点で改質処理が終了した下地膜20が形成される（図15）。その後、減圧CVDによりアモルファスシリコン膜を成膜し、レーザ照射により結晶化させる。この後の製造方法は、実\*

\*施の形態1における製造方法と同様である。

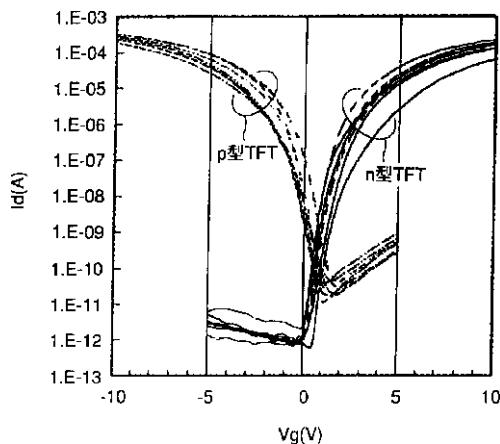

【0047】上記実施の形態2の製造方法で作製したTFTの6例についての $I_d - V_g$ 曲線を図16に示す。図23の従来例のTFTの $I_d - V_g$ 曲線と比較して、本実施の形態において、TFTは、低い $I_{off}$ と良好なS値を得ることができる。また、p型TFTとn型TFTの $V_{th}$ の中間値はゼロ付近にあり、LCDの駆動回路に適したTFTが形成されている。

【0048】（実施の形態3）実施の形態1においては、アモルファスシリコンが結晶化された多結晶体シリコン膜はウエットエッティングにより除去されていた。本実施の形態3では、ドライエッティングにより、多結晶体シリコン膜を除去する。ドライエッティングの条件は下記の通りである。

(a) 圧力：20Pa

(b) SF<sub>6</sub>流量：180sccm (standard cubic cm/min)

(c) O<sub>2</sub>流量：30sccm (standard cubic cm/min)

(d) F<sub>123</sub>流量：100sccm (standard cubic cm/min)

(e) RFパワー：1kW

(f) モード：PEモード

このドライエッティング条件によって多結晶体シリコン膜を除去した下地膜を用いて、この後、実施の形態1と同様の製造方法で製造したTFTは、実施の形態1または2におけるTFTと同様に、低い $I_{off}$ と良好なS値を得ることができる。かつ、p型TFTとn型TFTの $V_{th}$ の中間値はゼロ付近にすることができる。

【0049】

【実施例】本発明の実施の形態1による改質処理（本発明例1）および実施の形態2による改質処理（本発明例2）を適用した実施例を表1に示す。

【0050】

【表1】

| 特性                | n型 TFT       |           | p型 TFT       |           | n型 TFTとp型 TFTの $V_{th}$ の中間値(v) |

|-------------------|--------------|-----------|--------------|-----------|---------------------------------|

|                   | $V_{th}$ (V) | S値(V/Dec) | $V_{th}$ (V) | S値(V/Dec) |                                 |

| 本発明例1<br>(実施の形態1) | 2.81         | 0.27      | -1.51        | 0.41      | 0.65                            |

| 本発明例2<br>(実施の形態2) | 2.26         | 0.26      | -2.08        | 0.37      | 0.09                            |

| 従来例               | 3.82         | 0.29      | -0.80        | 0.54      | 1.51                            |

【0051】表1によれば、p型TFTのS値は、本発明例1では0.41V/Dec(Dec: Idの1桁分)であり、また本発明例2では0.37V/Decであった。これに対して、従来例では、0.54V/Decであり、本発明例1および2はともに従来例よりもS値は低く、ゲート電圧によるドレン電流の制御性に優れている。また、p型

TFTとn型TFTの $V_{th}$ の中間値は、本発明例1が0.65Vであり、本発明例2が0.09Vであるのにに対して従来例は1.51Vと非常にゼロから偏倚している。この結果より、本発明例はともに、S値や $V_{th}$ の対称性が従来例よりも優れていることが分かる。また、本発明例のなかで比較すると、実施の形態2による方法、

すなわち下地膜にアモルファスシリコン膜を成膜し除去し、レーザアニールして下地膜表面を改質する方法のほうが、実施の形態1における方法よりも良好な結果をもたらす傾向がある。

【0052】上記において、本発明の実施の形態について説明を行なったが、上記に開示された本発明の実施の形態は、あくまで例示であって、本発明の範囲はこれら発明の実施の形態に限定されない。本発明の範囲は、特許請求の範囲の記載によって示され、さらに特許請求の範囲の記載と均等の意味および範囲内のすべての変更を含む。

10

#### 【0053】

【発明の効果】本発明によれば、オフ電流  $I_{off}$ 、およびドレン電流を1オーダー上げるのに必要なゲート電圧上昇分であるS値、をともに低くし、かつp型TFTとn型TFTの  $V_{th}$  の中央値がゼロに近いTFTを製造することができる。さらにそのTFTを搭載した、消費電力が低く制御性に優れたLCDを得ることができる。

#### 【図面の簡単な説明】

【図1】 実施の形態1において、ガラス基板の上に下地膜を成膜した段階の断面図である。

20

【図2】 図1の状態に対して、アモルファスシリコン膜を成膜した段階の断面図である。

【図3】 図2の状態に対して、レーザアニールしてアモルファスシリコン膜を多結晶体シリコン膜にした段階の断面図である。

【図4】 図3の状態に対して、ウエットエッチングにより多結晶体シリコン膜を除去した段階の断面図である。

【図5】 図4の状態に対して、アモルファスシリコン膜を減圧CVDで成膜した段階の断面図である。

30

【図6】 図5の状態に対して、レーザアニールにより多結晶体シリコン膜として、パターニングしてチャネル形状にした段階の断面図である。

【図7】 図6の状態に対して、ゲート絶縁膜を成膜した段階の断面図である。

【図8】 図7の状態に対して、ゲート電極をパターニングして、その後n型TFTのソース、ドレン領域にn型不純物を打ち込み、p型TFTのソース、ドレン領域にp型不純物を打ち込んだ段階の断面図である。

40

【図9】 図8の状態に対して、層間絶縁膜を成膜した段階の断面図である。

【図10】 図9の状態に対して、パッシベーション膜を成膜した段階の断面図である。

【図11】 実施の形態1の方法で製造したTFTの  $I_d - V_g$  曲線を示す図である。

【図12】 実施の形態2において、ガラス基板の上に下地膜を成膜した段階の断面図である。

【図13】 図12の状態に対して、アモルファスシリコン膜を成膜した段階の断面図である。

【図14】 図13の状態からアモルファスシリコン膜をウエットエッチングによって除去した段階の断面図である。

【図15】 図14の状態に対して、レーザ照射した段階の断面図である。

【図16】 実施の形態2の方法で製造したTFTの  $I_d - V_g$  曲線を示す図である。

【図17】 従来法において、ガラス基板の上に下地膜およびアモルファスシリコン膜を成膜した段階の断面図である。

【図18】 アモルファスシリコン膜にレーザアニールして多結晶体シリコン膜を形成し、チャネル形状にパターニングした段階の断面図である。

【図19】 ゲート絶縁膜を成膜した段階の断面図である。

【図20】 ゲート電極をパターニングして形成し、n型TFTのソース、ドレン領域にn型不純物を打ち込み、p型TFTのソース、ドレン領域にp型不純物を打ち込んだ段階の断面図である。

【図21】 層間絶縁膜を成膜した段階の断面図である。

【図22】 層間絶縁膜にコンタクトホールを開口し、ソース、ドレン配線を形成し、その上にパッシベーション膜を成膜した段階の断面図である。

【図23】 従来法で製造したTFTの  $I_d - V_g$  曲線を示す図である。

#### 【符号の説明】

- 1 ガラス基板、2 下地膜、3a アモルファスシリコン膜、3b 多結晶体シリコン膜、4 ゲート絶縁膜、5 ゲート電極、6 層間絶縁膜、7 ソース、ドレン配線、8 パッシベーション膜、19 改質途中の下地膜、20 改質された下地膜、30a トランジスタ形成用アモルファスシリコン膜、30c トランジスタ形正用チャネル形状多結晶体シリコン、30u n型TFTのソースドレン領域、30v p型TFTのソースドレン領域、51a 駆動回路領域のn型TFT、51b 駆動回路領域のp型TFT、52 画素領域のn型TFT。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図13】

【図11】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

フロントページの続き

(72)発明者 林 正美

東京都千代田区丸の内二丁目2番3号 三

菱電機株式会社内

(72)発明者 小松 紀和

長野県諏訪市大和3丁目3番5号 セイコ

一エプソン株式会社内

F ターム(参考) 2H092 JA25 JA29 JA38 JA42 JA44

JA46 JB13 JB23 JB32 JB33

JB38 JB51 JB57 JB63 JB69

KA04 KA07 KB24 MA05 MA07

MA14 MA15 MA16 MA18 MA19

MA20 MA27 MA30 MA35 MA37

MA41

5F004 AA16 BB13 DA00 DA18 DA26

DB02

5F052 AA02 AA24 BB06 BB07 DA02

DB02 EA12 FA22 HA01 JA01

5F110 AA06 AA08 BB02 BB04 CC02

DD02 DD13 DD14 DD17 EE04

EE06 EE44 FF02 FF30 GG02

GG13 GG47 GG57 NN02 NN24

NN35 PP03 QQ04 QQ11

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|

| 专利名称(译)        | 薄膜晶体管和液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |

| 公开(公告)号        | <a href="#">JP2001332739A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2001-11-30 |  |

| 申请号            | JP2000152882                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2000-05-24 |  |

| [标]申请(专利权)人(译) | 三菱电机株式会社<br>精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |

| 申请(专利权)人(译)    | 三菱电机株式会社<br>精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |

| [标]发明人         | 高鍋昌一<br>林正美<br>小松紀和                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |

| 发明人            | 高鍋 昌一<br>林 正美<br>小松 紀和                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |  |

| IPC分类号         | G02F1/136 G02F1/1368 H01L21/20 H01L21/302 H01L21/3065 H01L21/336 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |

| F1分类号          | H01L21/20 H01L29/78.626.C G02F1/136.500 H01L21/302.J H01L29/78.627.G G02F1/1368 H01L21/302.105.Z H01L21/302.301.Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |  |

| F-TERM分类号      | 2H092/JA25 2H092/JA29 2H092/JA38 2H092/JA42 2H092/JA44 2H092/JA46 2H092/JB13 2H092/JB23 2H092/JB32 2H092/JB33 2H092/JB38 2H092/JB51 2H092/JB57 2H092/JB63 2H092/JB69 2H092/KA04 2H092/KA07 2H092/KB24 2H092/MA05 2H092/MA07 2H092/MA14 2H092/MA15 2H092/MA16 2H092/MA18 2H092/MA19 2H092/MA20 2H092/MA27 2H092/MA30 2H092/MA35 2H092/MA37 2H092/MA41 5F004/AA16 5F004/BB13 5F004/DA00 5F004/DA18 5F004/DA26 5F004/DB02 5F052 /AA02 5F052/AA24 5F052/BB06 5F052/BB07 5F052/DA02 5F052/DB02 5F052/EA12 5F052/FA22 5F052/HA01 5F052/JA01 5F110/AA06 5F110/AA08 5F110/BB02 5F110/BB04 5F110/CC02 5F110 /DD02 5F110/DD13 5F110/DD14 5F110/DD17 5F110/EE04 5F110/EE06 5F110/EE44 5F110/FF02 5F110/FF30 5F110/GG02 5F110/GG13 5F110/GG47 5F110/GG57 5F110/NN02 5F110/NN24 5F110 /NN35 5F110/PP03 5F110/QQ04 5F110/QQ11 2H192/AA24 2H192/CB02 2H192/CB34 2H192/EA76 2H192/FB02 2H192/HA82 2H192/HA90 5F152/AA14 5F152/BB02 5F152/CC02 5F152/CD13 5F152 /CD14 5F152/CE05 5F152/CE13 5F152/FF03 |         |            |  |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |

| 摘要(译)                                                                                                                                                | n型 TFT            |            | p型 TFT         |            | n型 TFT 与 p型 TFT の Vth の 中間 値 (V) |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|----------------|------------|----------------------------------|

|                                                                                                                                                      | 特性                | Vth<br>(V) | S 值<br>(V/Dec) | Vth<br>(V) | S 值<br>(V/Dec)                   |

| 解决的问题：提供一种TFT，具有低截止电流Ioff和低S值，并且具有p型 TFT和n型 TFT的良好的Vth对称性的LCD及其制造方法。解决方案：该 TFT制造方法包括以下步骤：在基板1上形成基膜2；将基膜加热到500°C 或更高的步骤；以及在加热的基膜上形成晶体管的硅。以及形成膜30a的步骤。 | 本発明例1<br>(実施の形態1) | 2.81       | 0.27           | -1.51      | 0.41                             |

|                                                                                                                                                      | 本発明例2<br>(実施の形態2) | 2.26       | 0.26           | -2.08      | 0.37                             |

|                                                                                                                                                      | 従来例               | 3.82       | 0.29           | -0.80      | 0.54                             |

|                                                                                                                                                      |                   |            |                |            | 1.51                             |