(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4361844号 (P4361844)

(45) 発行日 平成21年11月11日(2009.11.11)

(24) 登録日 平成21年8月21日 (2009.8.21)

(51) Int. Cl.

GO2F 1/1368 (2006.01)

GO2F 1/1368

FL

請求項の数 1 (全 37 頁)

(21) 出願番号 特願2004-220263 (P2004-220263) (22) 出願日 平成16年7月28日 (2004.7.28) (65) 公開番号 特開2006-39290 (P2006-39290A) (43) 公開日 平成18年2月9日 (2006.2.9) 審査請求日 平成18年10月24日 (2006.10.24) (73)特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番 1号

|(73)特許権者 501358079

友達光電股▲ふん▼有限公司

AU Optronics Corpor ation

台湾新竹科學工業園區新竹市力行二路一号 No. 1, Lt-Hsin Rd, II, Science-Based Indus trial Park, Hsinchu, Taiwan, R. O. C.

(74)代理人 100091672

弁理士 岡本 啓三

最終頁に続く

# (54) 【発明の名称】液晶表示装置

## (57)【特許請求の範囲】

# 【請求項1】

相互に対向して配置された第1及び第2の基板と、

前記第1及び第2の基板間に封入された液晶と、

前記第1の基板に形成されたゲートバスライン及びデータバスラインと、

前記ゲートバスライン及び前記データバスラインに接続された薄膜トランジスタと、

前記ゲートバスライン及び前記データバスラインにより区画される画素領域内に形成された複数の副画素電極と、

前記複数の副画素電極のうちの少なくとも1つと容量結合し、前記データバスラインから前記薄膜トランジスタを介して表示電圧が印加される制御電極とを有する液晶表示装置において、

前記制御電極と容量結合した副画素電極と前記ゲートバスライン及び前記データバスラインのうちの少なくとも一方のバスラインとの間を電気的にシールドするシールド部材を有することを特徴とする液晶表示装置。

【発明の詳細な説明】

# 【技術分野】

### [0001]

本発明は、1画素領域内に複数の副画素電極を有する液晶表示装<u>置に</u>関し、特に副画素電極のうちの少なくとも1つが表示電圧が印加される制御電極と容量結合した液晶表示装置に関する。

## 【背景技術】

# [0002]

液晶表示装置は、CRT (Cathode Ray Tube)に比べて薄くて軽量であり、低電圧で駆動できて消費電力が小さいという利点がある。そのため、液晶表示装置は、テレビ、ノート型PC (パーソナルコンピュータ)、ディスクトップ型PC、PDA (携帯端末)及び携帯電話など、種々の電子機器に使用されている。特に、各画素(サブピクセル)毎にスイッチング素子としてTFT (Thin Film Transistor:薄膜トランジスタ)を設けたアクティブマトリクス型液晶表示装置は、その駆動能力の高さからCRTにも匹敵する優れた表示特性を示し、ディスクトップ型PCやテレビなど、従来CRTが使用されていた分野にも広く使用されるようになった。

[0003]

一般的に、液晶表示装置は、2枚の基板と、これらの基板間に封入された液晶とにより構成されている。一方の基板には画素毎に画素電極及びTFT等が形成され、他方の基板には画素電極に対向するカラーフィルタと、各画素共通のコモン(共通)電極とが形成されている。カラーフィルタには赤色(R)、緑色(G)及び青色(B)の3種類があり、画素毎にいずれか1色のカラーフィルタが配置されている。隣接して配置された赤色(R)、緑色(G)及び青色(B)の3つの画素で1つのピクセル(Pixel)を構成する。以下、画素電極及びTFTが形成された基板をTFT基板と呼び、TFT基板に対向して配置される基板を対向基板と呼ぶ。また、TFT基板と対向基板との間に液晶を封入してなる構造物を液晶パネルという。

[0004]

従来は、2枚の基板間に水平配向型液晶(誘電率異方性が正の液晶)を封入し、液晶分子をツイスト配向させるTN(Twisted Nematic )型液晶表示装置が広く使用されていた。しかし、TN型液晶表示装置には視野角特性が悪く、画面を斜め方向から見たときにコントラストや色調が大きく変化するという欠点がある。このため、視野角特性が良好なMVA(Multi-domain Vertical Alignment )型液晶表示装置が開発され、実用化されている。

[0005]

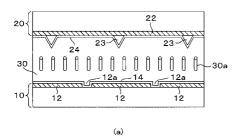

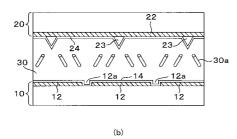

図1(a),(b)は、MVA型液晶表示装置の一例を示す模式断面図である。TFT基板10及び対向基板20はスペーサ(図示せず)を挟んで配置されており、これらの基板10,20の間には垂直配向型液晶(誘電率異方性が負の液晶)30が封入されている。TFT基板10の画素電極12には、電圧印加時の液晶分子の傾斜方向を決めるドメイン規制用構造物として、スリット12aが設けられている。この画素電極12の表面は、例えばポリイミドからなる垂直配向膜14に覆われている。

[0006]

対向基板 2 0 のコモン電極 2 2 の下には、ドメイン規制用構造物として複数の土手状の 突起 2 3 が形成されている。これらの突起 2 3 は、図 1 (a)に示すように、基板 1 0 側 のスリット 1 2 a に対し斜め方向にずれた位置に配置されている。コモン電極 2 2 及び突 起 2 3 の表面も、例えばポリイミドからなる垂直配向膜 2 4 に覆われている。

[0007]

TFT基板10の下側及び対向基板20の上側にはそれぞれ偏光板(図示せず)が配置される。これらの偏光板は、吸収軸を相互に直交させて配置される。

[0008]

このように構成されたMVA型液晶表示装置において、画素電極12とコモン電極22との間に電圧を印加しない状態では、図1(a)に示すように、殆どの液晶分子30aは基板面に対し垂直に配向する。但し、突起23の近傍の液晶分子30aは、突起23の傾斜面に垂直な方向に配向する。この場合、TFT基板10の下側から偏光板を通って液晶層に進入した光は、偏光方向が変化することなく液晶層を通過し、対向基板側20の上側の偏光板により遮断される。すなわち、この場合は黒表示となる。

[0009]

10

20

30

画素電極12とコモン電極22との間に所定の電圧を印加すると、電界の影響により液晶分子30aは基板面に対し斜めに配向する。この場合に、図1(b)に示すように、スリット12a及び突起23の両側では液晶分子30aの傾斜方向が異なり、いわゆる配向分割(マルチドメイン)が達成される。この図1(b)に示すように液晶分子30aが基板面に対し斜めに配向したときは、TFT基板10の下側から偏光板を通って液晶層に進入した光は、液晶層で偏光方向が変化し、対向基板20の上側の偏光板を通過するようになる。偏光板を通過する光の量は、画素電極12とコモン電極22との間に印加される電圧に依存する。

## [0010]

また、MVA型液晶表示装置では、図1(b)に示すように、電圧を印加したときの液晶分子30aの傾斜方向がスリット12a及び突起23の両側で異なるので、斜め方向への光の漏れが抑制され、優れた視野角特性が得られる。

## [0011]

上記の例ではドメイン規制用構造物が突起及びスリットの場合について説明したが、基板表面の窪み(溝)をドメイン規制用構造物とすることもある。また、図1(a),(b)ではTFT基板10及び対向基板20の両方にドメイン規制用構造物を設けた例について説明したが、TFT基板10及び対向基板20のうちのいずれか一方のみにドメイン規制用構造物を形成してもよい。

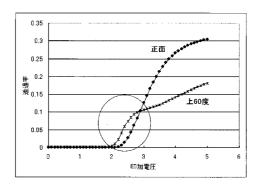

#### [0012]

ところで、従来のMVA型液晶表示装置では、画面を斜め方向から見たときに白っぽくなる現象が発生する。図2は、横軸に印加電圧(V)をとり、縦軸に透過率をとって、画面を正面から見たときのT・V(透過率・電圧)特性と、上60°の方向から見たときのT・V特性とを示す図である。この図2に示すように、しきい値電圧よりも若干高い電圧を画素電極に印加したとき(図中丸で囲んだ部分)には、斜め方向から見たときの透過率よりも高くなる。また、印加電圧がある程度高くなると、斜め方向から見たときの透過率は、正面から見たときの透過率よりも低くなる。このため、斜め方向から見たときには赤色画素、緑色画素及び青色画素の輝度差が小さくなり、その結果前述したように画面が白っぽくなる現象が発生する。この現象は、白茶け(discolor)と呼ばれている。白茶けは、MVA型液晶表示装置だけでなく、TN型液晶表示装置でも発生する。

### [0013]

米国特許第4840460号の明細書には、1つの画素を複数の副画素に分割して、それらの副画素を容量結合することが提案されている。このような液晶表示装置では、各副画素の容量比によって電位が分割されるため、各副画素に相互に異なる電圧を印加することができる。従って、見かけ上、1つの画素にT・V特性のしきい値が異なる複数の領域が存在することになる。このように1つの画素にT・V特性のしきい値が異なる複数の領域が存在すると、正面から見たときの透過率よりも斜め方向から見たときの透過率が高くなる現象が抑制され、その結果画面が白っぽくなる現象(白茶け)も抑制される。このように1つの画素を容量結合した複数の副画素に分割して表示特性を改善する方法は、容量結合によるHT(ハーフトーングレースケール)法と呼ばれる。なお、米国特許第4840460号の明細書に記載された液晶表示装置は、TN型液晶表示装置である。

#### [0014]

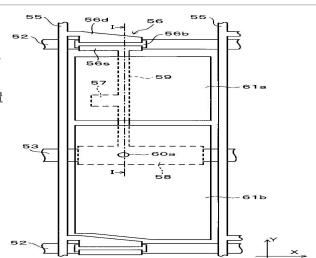

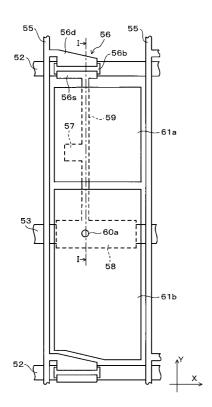

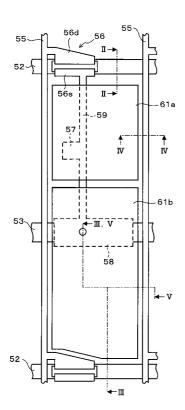

図3は容量結合によるHT法を実現する液晶表示装置のTFT基板の一例を示す平面図、図4は図3のI-I線による断面図である。

## [0015]

TFT基板のベースとなるガラス基板 5 1 の上には、水平方向( X 方向)に延びる複数のゲートバスライン 5 2 と、垂直方向( Y 方向)に延びる複数のデータバスライン( ドレインバスライン) 5 5 とが形成されている。これらのゲートバスライン 5 2 及びデータバスライン 5 5 により区画される矩形の領域がそれぞれ画素領域である。また、ガラス基板 5 1 の上には、ゲートバスライン 5 2 と平行に配置され、各画素領域の中央を横断する補

10

20

30

40

20

30

40

50

助容量バスライン53が形成されている。

#### [0016]

ゲートバスライン 5 2 及び補助容量バスライン 5 3 とデータバスライン 5 5 との間には第 1 の絶縁膜 5 4 が形成されており、この第 1 の絶縁膜 5 4 によりゲートバスライン 5 2 及び補助容量バスライン 5 3 とデータバスライン 5 5 との間が電気的に分離されている。

#### [0017]

各画素領域には、TFT56と、制御電極57と、補助容量電極58と、副画素電極61a,61bとが形成されている。TFT56は、図3に示すようにゲートバスライン52の一部をゲート電極としている。また、図4に示すように、TFT56の活性層となる半導体膜56aはゲートバスライン52の上方に形成されており、この半導体膜56aの上にはチャネル保護膜56bが形成されている。

#### [0018]

TFT56のドレイン電極56dはデータバスライン55に接続しており、ソース電極56sはゲートバスライン52を挟んでドレイン電極56dに対向する位置に配置されている。更に、補助容量電極58は第1の絶縁膜54を挟んで補助容量バスライン53に対向する位置に形成されている。更にまた、制御電極57は、図3に示すように、配線59を介してソース電極56sと補助容量電極58とに電気的に接続されている。

# [0019]

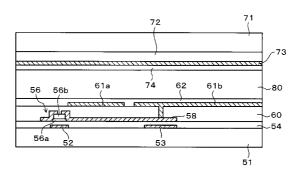

これらのデータバスライン55、TFT56、制御電極57、補助容量電極58及び配線59は第2の絶縁膜60に覆われており、副画素電極61a,61bは第2の絶縁膜60上に形成されている。副画素電極61aは、第2の絶縁膜60を挟んで制御電極57と容量結合している。また、副画素電極61bは、第2の絶縁膜60に形成されたコンタクトホール60aを介して補助容量電極58と電気的に接続している。副画素電極61a,61bの表面は配向膜62に覆われている。

#### [0020]

一方、対向基板は、図4に示すように、ベースとなるガラス基板71の一方の面側(図4では下側)に形成されたカラーフィルタ72と、カラーフィルタ72の面上に形成されたコモン電極73と、コモン電極73の表面を覆う配向膜74とを備えている。

## [0021]

これらのTFT基板及び対向基板はスペーサ(図示せず)を挟んで配置される。そして TFT基板と対向基板との間には液晶80が封入される。

# [0022]

透過型液晶表示装置の場合、副画素電極 6 1 a , 6 1 b は I T O (Indium-Tin Oxide) 等の透明導電体により形成される。また、反射型液晶表示装置の場合、副画素電極 6 1 a , 6 1 b はアルミニウム等の反射率が高い材料により形成される。

## [0023]

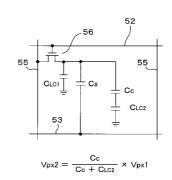

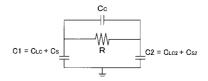

図 5 は、上述したTFT基板を備えた液晶表示装置の1画素を示す等価回路図である。この図 5 において、 $C_{LC1}$  は副画素電極 6 1 b とコモン電極 7 3 とにより構成される容量であり、 $C_{S}$  は補助容量電極 5 8 と補助容量バスライン 5 3 とにより構成される容量であり、 $C_{C}$  は副画素電極 6 1 a と制御電極 5 7 とにより構成される容量であり、 $C_{LC2}$  は副画素電極 6 1 a とコモン電極 7 3 とにより構成される容量である。この図 5 に示すように、副画素電極 6 1 a とコモン電極 7 3 との間の容量  $C_{LC2}$  と制御容量  $C_{C}$  とで分圧されるため、副画素電極 6 1 b に印加される電圧  $V_{D}$  とすると、副画素電極 6 1 a に印加される電圧  $V_{D}$  は下記(1)式に示すようになる。

#### [0024]

# 【数1】

$$V_{px2} = \frac{C_C}{C_C + C_{LC2}} \times V_{px1} \quad \cdots (1)$$

実際の電圧比(Vpx2 / Vpx1 )は液晶表示装置の表示特性の設計事項であるが、およ

そ0.6~0.8が理想的であるとされている。

#### [0025]

以下、副画素電極61aのように容量結合を介して表示電圧が印加される副画素電極を、フローティング副画素電極という。また、副画素電極61bのように低抵抗の導電体(配線等)を介してTFTに電気的に接続された副画素電極を、TFTに直結した副画素電極という。

#### [0026]

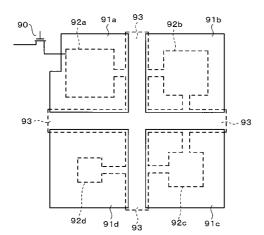

特許第3076938号の明細書(特開平5-66412号公報)には、図6に示すように、画素電極を複数(図6では4つ)の副画素電極91a~91dに分割し、各副画素電極91a~91dの下方に絶縁膜を介して制御電極92a~92dをそれぞれ配置したTN型液晶表示装置が開示されている。この液晶表示装置では、TFT90を介して制御電極92a~92dに表示電圧が印加される。各副画素電極91a~91dの大きさは相互に異なっているので、副画素電極91a~91dに印加される電圧も相互に異なり、HT法による効果、すなわち白茶けを抑制する効果を得ることができる。なお、この液晶表示装置では、副画素電極91a~91dの間から光が漏れることを防止するために、副画素電極91a~91dの間にも制御電極93を配置している。

【特許文献1】米国特許第4840460号明細書

【特許文献2】特許第3076938号明細書

【発明の開示】

【発明が解決しようとする課題】

[0027]

しかしながら、本願発明者等の実験研究により、上述した従来のフローティング副画素 電極を有する液晶表示装置では焼き付きにより表示特性が劣化することが判明した。

#### [0028]

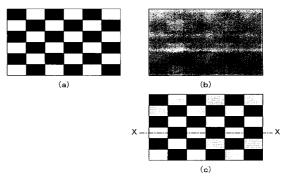

図7(a)~(c)及び図8は、焼き付きの程度を測定する試験方法を示す模式図である。まず、液晶表示装置に、図7(a)に示すような白黒のチェッカーパターンを一定時間連続して表示する。その後、液晶表示装置の全面に、図7(b)に示すような中間調の表示を行う。このとき、画面に焼き付きが発生すると、図7(c)に示すように、チェッカーパターンが薄く見える。チェッカーパターンの表示から中間調の表示に切り替えた後、例えば図7(c)のX・X線に沿って輝度を測定する。そして、図8に示すように暗い部分の輝度をa、暗い部分と明るい部分との輝度差をbとしたときに、100×b/(a+b)で定義される焼き付き率を計算する。

[0029]

上記の方法により、フローティング副画素電極を有しない液晶表示装置の焼き付き率とフローティング副画素電極を有する液晶表示装置の焼き付き率を測定した。その結果、フローティング副画素電極を有しない液晶表示装置の焼き付き率が5%以下であるのに対し、フローティング副画素電極を有する液晶表示装置の焼き付き率は10%以上と高いものであった。

[0030]

以上から、本発明の目的は、容量結合HT法を使用して白茶けを抑制する液晶表示装置において、焼き付きの発生を回避できる液晶表示装置を提供することである。

【課題を解決するための手段】

## [0031]

上記した課題は、相互に対向して配置された第1及び第2の基板と、前記第1及び第2の基板間に封入された液晶と、前記第1の基板に形成されたゲートバスライン及びデータバスラインと、前記ゲートバスライン及び前記データバスラインに接続された薄膜トランジスタと、前記ゲートバスライン及び前記データバスラインにより区画される画素領域内に形成された複数の副画素電極と、前記複数の副画素電極のうちの少なくとも1つと容量結合し、前記データバスラインから前記薄膜トランジスタを介して表示電圧が印加される制御電極とを有する液晶表示装置において、前記制御電極と容量結合した副画素電極と前

10

20

30

40

記ゲートバスライン及び前記データバスラインのうちの少なくとも一方のバスラインとの間を電気的にシールドするシールド部材を有する液晶表示装置により解決する。

## [0032]

本発明においては、制御電極と容量結合した副画素電極とゲートバスライン及びデータバスラインのうちの少なくとも一方のバスラインとの間を、例えば一定の電位に保持される補助容量バスラインに接続されたシールド部材により電気的にシールドする。このように、制御電極と容量結合した副画素電極をシールド部材でシールドすることにより、ゲートバスライン又はデータバスラインから副画素電極への電荷の注入が回避され、その結果焼き付きが防止される。

#### [0033]

シールド部材として、TFTに直結された副画素電極を使用することもできる。例えば 制御電極と容量結合した副画素電極とゲートバスラインとの間にTFTに直結した副画素 電極を配置することにより、ゲートバスラインから制御電極と容量結合した副画素電極へ 電荷が注入されることを回避できる。

【発明を実施するための最良の形態】

#### [0043]

以下、本発明について、更に詳細に説明する。

# [0044]

通常、液晶表示装置の焼き付きは、ゲートバスライン及びデータバスライン等に流れる信号に直流電圧成分が存在し、白表示時と黒表示時とで液晶層の C R 値(液晶容量及び液晶抵抗の値)が変化することが原因である。以下に、フローティング副画素電極を有する液晶表示装置で焼き付きが発生する理由について説明する。

#### [0045]

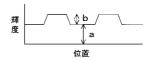

図9はフローティング副画素電極を備えた液晶表示装置の1画素を示す平面図であり、図10(a)は図9のII-II線の位置における模式断面図、図10(b)は図9のII-III線の位置における模式断面図、図10(c)は図9のIV-IV線の位置における模式断面図、図10(d)は図9のV-V線の位置における模式断面図である。

#### [0046]

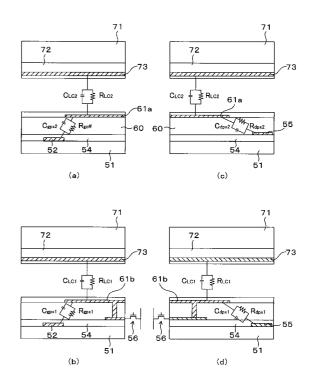

図 9 に示す液晶表示装置においては、図 1 0 ( a ) に示すように、副画素電極(フローティング副画素電極) 6 1 a とコモン電極 7 3 との間に、 $C_{LC2}$  と $R_{LC2}$  とが並列に接続されているとみなすことができる。ここで、 $C_{LC2}$  は副画素電極 6 1 a とコモン電極 7 3 との間の容量であり、 $R_{LC2}$  は副画素電極 6 1 a とコモン電極 7 3 との間の抵抗である。

#### [0047]

また、副画素電極 6 1 a とゲートバスライン 5 2 との間にも、  $C_{gpx2}$ と  $R_{goff}$ とが並列に接続されているとみなすことができる。ここで、  $C_{gpx2}$ は副画素電極 6 1 a とゲートバスライン 5 2 との間の容量であり、  $R_{goff}$ は副画素電極 6 1 a とゲートバスライン 5 2 との間の抵抗である。

## [0048]

一方、副画素電極(TFT56に直結した副画素電極)61bとコモン電極73との間にも、図10(b)に示すように、 $C_{LC1}$  と $R_{LC1}$  とが並列に接続されているとみなすことができる。ここで、 $C_{LC1}$  は副画素電極61bとコモン電極73との間の容量であり、 $R_{LC1}$  は副画素電極61bとコモン電極73との間の抵抗である。

## [0049]

また、副画素電極 6 1 b とゲートバスライン 5 2 との間には、  $C_{gp\times 1}$  と  $R_{gp\times 1}$  とが並列に接続されているとみなすことができる。ここで、  $C_{gp\times 1}$  は副画素電極 6 1 b とゲートバスライン 5 2 との間の容量であり、  $R_{gp\times 1}$  は副画素電極 6 1 b とゲートバスライン 5 2 との間の抵抗である。

# [0050]

10

20

30

40

## [0051]

図 1 0 ( c ) に示すように、副画素電極 6 1 a とデータバスライン 5 5 との間には、 C  $_{\rm dpx2}$ と R  $_{\rm dpx2}$ とが並列に接続されているとみなすことができる。ここで、 C  $_{\rm dpx2}$ は副画素電極 6 1 a とデータバスライン 5 5 との間の容量であり、 R  $_{\rm dpx2}$ は副画素電極 6 1 a とデータバスライン 5 5 との間の抵抗である。

#### [0052]

また、図10(d)に示すように、副画素電極61bとデータバスライン55との間にも、 $C_{dp \times 1}$ と $R_{dp \times 1}$ とが並列に接続されているとみなすことができる。ここで、 $C_{dp \times 1}$ は副画素電極61bとデータバスライン55との間の容量であり、 $R_{dp \times 1}$ は副画素電極61bとデータバスライン55との間の抵抗である。

# [0053]

データバスライン 5 5 には、フィードスルー電圧を補償するために、コモン電極 7 3 の電位に対し 1 ~ 2 V 程度高い直流電圧を表示信号(交流信号)に重畳させている。この直流電圧に応じた電荷も、容量  $C_{dp \times 2}$ と抵抗  $R_{dp \times 2}$ とを介して副画素電極 6 1 a に蓄積される。

# [0054]

しかし、前述したように、1フィールド毎に1回づつTFT56がオンになって、副画素電極61bとデータバスライン55とが電気的に接続されるため、副画素電極61bではTFT56がオフの期間に蓄積された電荷がオンの期間にデータバスライン55に流れる。このため、副画素電極61bには直流電圧成分は残留しない。一方、副画素電極61aでは、TFT56がオンになっても、副画素電極61aに蓄積された電荷はそのまま保持される。このため、副画素電極61aには直流電圧成分が残留する。

# [0055]

このように、TFT56に直結した副画素電極61bでは直流電圧成分の蓄積は殆どないのに対し、フローティング副画素電極61aでは電荷が蓄積されて直流電圧成分が残留する。

# [0056]

次に、フローティング副画素電極に蓄積された電荷と焼き付きとの関係について説明する。

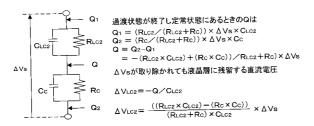

# [0057]

図11は、フローティング副画素電極により構成される副画素の等価回路を示す図である。制御電極とコモン電極との間の直流電圧成分を Vsとし、フローティング副画素電極の電荷量をQ、コモン電極の電荷量をQ1、制御電極の電荷量をQ2とする。過渡状態が終了し定常状態にあるときのQ1、Q2、Qは、下記(2)式に示すようになる。

## [0058]

30

10

20

【数2】

$$Q1 = \frac{R_{LC2}}{R_{LC2} + R_C} \times \Delta V_S \times C_{LC2}$$

$$Q2 = \frac{R_C}{R_{LC2} + R_C} \times \Delta V_S \times C_C$$

$$Q = Q2 - Q1$$

$$= \frac{-((R_{LC2} \times C_{LC2}) - (R_C \times C_C))}{R_{LC2} + R_C} \times \Delta V_S$$

制御電極とコモン電極との間の直流電圧成分 V s が取り除かれても、下記(3)式に示す直流電圧成分 V<sub>LC2</sub> が液晶層に残留する。

[0059]

【数3】

$$\Delta V_{LC2} = -Q/Q_{LC2}$$

$$= \frac{((R_{C2} \times Q_{C2}) - (R_C \times C_C))}{(R_{C2} + R_C) \times Q_{C2}} \times \Delta V_S \quad \cdots (3)$$

副画素電極の面積をS、セル厚をdとすると、液晶容量 $C_{LC2}$  は、 $C_{LC2}$  = (S/d)で表される。ここで、 は液晶の誘電率である。液晶分子が基板面に垂直に配向しているときの誘電率と水平に配向しているときの誘電率とは異なるため、チェッカーパターンの白部分を表示している画素と黒部分を表示している画素では液晶容量の値が異なり、その結果液晶層に印加される直流電圧成分  $V_{LC2}$  の値も異なる。チェッカーパターンの表示から中間調の表示に切り替えても液晶層に残留する直流電圧成分は直ぐには変化しないため、白を表示していた画素と黒を表示していた画素とでは洗の透過率が異なり、焼き付きが発生する。なお、このような原因で発生した焼き付きは副画素電極と制御電極及びコモン電極との間の時定数に応じた時間で減少するが、表示品質を向上させるためには焼き付きをできるだけ少なくすることが必要である。

[0060]

図12は、横軸に制御電極とコモン電極との間の直流電圧成分 Vs をとり、縦軸に液晶層に残留する直流電圧成分  $V_{LC2}$  をとって、液晶層に表示電圧が印加されたとき(液晶 ON) の Vs と  $V_{LC2}$  との関係と、液晶層に表示電圧が印加されていないとき(液晶 OFF) の Vs と  $V_{LC2}$  との関係とを示す図である。但し、ここでは、図 9 に示す構造の液晶表示装置を想定しており、画素ピッチを125 $\mu$  m、制御電極58と容量結合した副画素電極61aとTFT56に直結した副画素電極61bとの面積比を3:7、副画素電極(フローティング副画素電極)61aに印加される表示電圧と副画素電極(TFTに直結した副画素電極)61bに印加される表示電圧との比を0.72として計算している。

[0061]

この図12からわかるように、制御電極とコモン電極との間の直流電圧成分 Vsの数倍の電圧が液晶層に印加されてしまう。このため、制御電極とコモン電極との間の直流電圧成分Vsを小さくしても、焼き付きを抑制する効果は小さい。

[0062]

本願発明者等は、焼き付けを防止するためには、次のいずれかの対策をとることが必要であると考えた。

[0063]

50

30

20

30

40

50

(1) 直流電圧成分を有する信号が流れるバスライン(ゲートバスライン及びデータバスライン)とフローティング副画素電極との間を電気的にシールドして、フローティング副画素電極への電荷の蓄積を抑制する。

(9)

[0064]

(2) ゲートバスラインに流れる信号が有する直流電圧成分とデータバスラインに流れる信号が有する直流電圧成分とは逆極性である。これら2つの直流電圧成分の影響が打ち消し合うようにフローティング副画素電極とゲートバスライン及びデータバスラインとの間の抵抗を最適化する。

[0065]

(3)フローティング副画素電極と制御電極との間の抵抗を小さくすると、液晶層に残留する直流電圧成分が小さくなる。しかし、フローティング副画素電極と制御電極との間の抵抗を小さくしすぎると、白茶けを抑制する効果が得られなくなる。白茶け及び焼き付きが発生しないように、フローティング副画素電極と制御電極との間の抵抗を最適化する

[0066]

(4)フローティング副画素電極に蓄積された電荷を一定の周期でデータバスライン又は補助容量バスライン等に流す。

[0067]

(5)フローティング副画素電極とコモン電極との間の容量(液晶容量)と並列に補助容量を形成して、液晶容量の変化の影響を小さくする。

[0068]

以下、これらの対策を施した本発明の実施形態の液晶表示装置について説明する。

[0069]

(第1の実施形態)

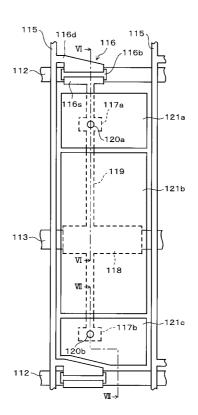

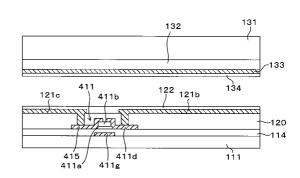

図13は本発明の第1の実施形態に係る液晶表示装置を示す平面図、図14(a)は図13のVI-VI線による断面図、図14(b)は図13のVII-VII線による断面図である。

[0070]

TFT基板のベースとなるガラス基板111の上には、水平方向(X方向)に延びる複数のゲートバスライン112と垂直方向(Y方向)に延びる複数のデータバスライン115とが形成されている。これらのゲートバスライン112及びデータバスライン115により区画される矩形の領域がそれぞれ画素領域である。また、ガラス基板111の上には、ゲートバスライン112と平行に配置され、各画素領域の中央を横断する補助容量バスライン113が形成されている。

[0071]

ゲートバスライン 1 1 2 及び補助容量バスライン 1 1 3 とデータバスライン 1 1 5 との間には、例えば S i N 又は S i O  $_2$  等の絶縁材料よりなる第 1 の絶縁膜 1 1 4 が形成されており、この第 1 の絶縁膜 1 1 4 によりゲートバスライン 1 1 2 及び補助容量バスライン 1 1 3 とデータバスライン 1 1 5 との間が電気的に分離されている。

[0072]

各画素領域には、TFT116と、接続電極117a,117bと、制御電極118と、ITO等の透明導電体からなる副画素電極121a~121cとが形成されている。制御電極118は補助容量バスライン115及び第1の絶縁膜114とともに補助容量電極を構成している。TFT116は図13に示すようにゲートバスライン112の一部をゲート電極としている。また、図14(a)に示すように、TFT116の活性層となる半導体膜116aはゲートバスライン112の上方に形成されており、この半導体膜116aの上にはチャネル保護膜116bが形成されている。

[0073]

TFT116のドレイン電極116dはデータバスライン115に接続しており、ソース電極116sはゲートバスライン112を挟んでドレイン電極116dに対向する位置

に配置されている。また、制御電極118は第1の絶縁膜114を挟んで補助容量バスライン113に対向する位置に形成されている。接続電極117aは副画素電極121aの下方に配置されており、接続電極117bは副画素電極121cの下方に配置されている。これらの接続電極117a,117b及び制御電極118は、配線119を介してソース電極116sに接続されている。

### [0074]

データバスライン 1 1 5、 T F T 1 1 6、 接続電極 1 1 7 a , 1 1 7 b 、制御電極 1 1 8 及び配線 1 1 9 は、 S i N 又は絶縁性樹脂等からなる第 2 の絶縁膜 1 2 0 により覆われており、この第 2 の絶縁膜 1 2 0 の上に副画素電極 1 2 1 a ~ 1 2 1 c が形成されている。図 1 3 に示すように、副画素電極(フローティング副画素電極) 1 2 1 b は画素領域の中央に配置されており、制御電極 1 1 8 と容量結合している。また、副画素電極 1 2 1 a は副画素電極 1 2 1 b と上側のゲートバスライン 1 1 2 との間に配置され、副画素電極 1 2 1 c は副画素電極 1 2 1 b と下側のゲートバスライン 1 1 2 との間に配置されている。これらの副画素電極 1 2 1 a , 1 2 1 c は、コンタクトホール 1 2 0 a , 1 2 0 b 、接続電極 1 1 7 a , 1 1 7 b 及び配線 1 1 9 を介して T F T 1 1 6 のソース電極 1 1 6 s に電気的に接続されている。また、副画素電極 1 2 1 a ~ 1 2 1 c の表面は、例えばポリイミドからなる配向膜 1 2 2 に覆われている。

#### [0075]

なお、ゲートバスライン 1 1 2 及び補助容量バスライン 1 1 3 は、例えば C r 膜又は A 1 - T i 積層膜をフォトリソグラフィ法によりパターニングして同時に形成される。また、データバスライン 1 1 5 、ソース電極 1 1 6 s 、ドレイン電極 1 1 6 d 及び制御電極 1 1 8 は、例えば T i - A 1 - T i 積層膜をフォトリソグラフィ法によりパターニングして同時に形成される。

#### [0076]

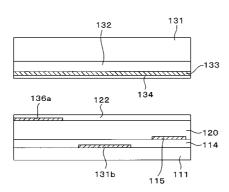

一方、対向基板は、図14(a),(b)に示すように、ベースとなるガラス基板131の一方の面側(図14(a),(b)では下側)に形成されたカラーフィルタ132と、カラーフィルタ132の面上に形成されたコモン電極133と、コモン電極133の表面を覆う配向膜134とを備えている。コモン電極133はITO等の透明導電体により形成され、配向膜134は例えばポリイミドにより形成される。

# [0077]

TFT基板と対向基板とはそれぞれ配向膜が形成された面を内側にして配置され、スペーサを挟んで接合される。そして、これらのTFT基板と対向基板との間には液晶140が封入されている。

### [0078]

上述のように構成された第1の実施形態の液晶表示装置において、副画素電極121a , 121 c は T F T 1 1 6 に電気的に接続しているので、 T F T 1 1 6 がオンになるとデータバスライン 1 1 5 に接続される。このため、 T F T 1 1 6 がオフの期間にゲートバスライン 1 1 2 に流れる信号の直流電圧成分により副画素電極 1 2 1 a , 1 2 1 b に電荷が蓄積されても、これらの電荷は T F T 1 1 6 がオンの期間にデータバスライン 1 1 5 に流れ、電荷の蓄積が回避される。従って、これらの副画素電極 1 2 1 a , 1 2 1 b では焼き付きが発生しない。

# [0079]

一方、制御電極118と容量結合した副画素電極(フローティング副画素電極)121 bは、ゲートバスライン112から離れているとともに、ゲートバスライン112との間 に副画素電極121a,121cが介在しているので、ゲートバスライン112に流れる 信号の直流電圧成分によるフローティング副画素電極121bへの電荷の蓄積が極めて少 ない。これにより、焼き付きの発生が回避され、良好な表示品質が得られる。

# [0080]

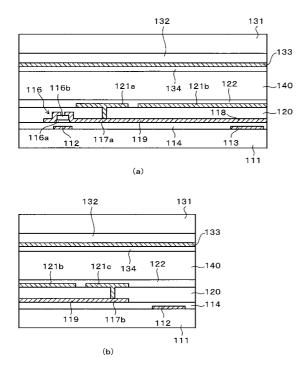

# (変形例1)

図15は第1の実施形態の変形例1の液晶表示装置を示す平面図、図16は図15のV

10

20

30

40

III - VIII 線による断面図である。これらの図15,図16において、図13,図14と同一物には同一符号を付して、その詳しい説明は省略する。

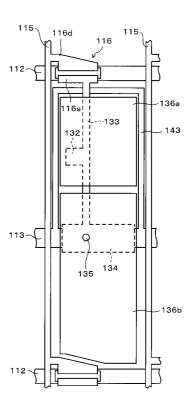

#### [0081]

図15,図16に示す変形例1の液晶表示装置においては、1画素内に2つの副画素電極136a,136bが設けられている。また、副画素電極136aの下方には第2の絶縁膜120を挟んで制御電極132が設けられており、副画素電極136aは制御電極132と容量結合している。

## [0082]

補助容量バスライン 1 1 3 の上方には補助容量電極 1 3 4 が設けられており、この補助容量電極 1 3 4 はコンタクトホール 1 3 5 を介して副画素電極 1 3 6 b と電気的に接続されている。また、補助容量電極 1 3 4 及び制御電極 1 3 2 は、配線 1 3 3 を介してTFT 1 1 6 のソース電極 1 1 6 s に電気的に接続されている。

#### [0083]

更に、副画素電極136aとデータバスライン115との間には、補助容量バスライン113から延び出したシールドパターン131a,131bが配置されている。補助容量バスライン113は、コモン電極133と同電位、又はコモン電極133の電位に対し一定の電位に維持される。

# [0084]

この変形例1の液晶表示装置においては、フローティング副画素電極136aとデータバスライン115との間に補助容量バスライン113と同電位に維持されるシールドパターン131a,15に流れる信号の直流成分によるフローティング副画素電極136への電荷の蓄積が抑制される。これにより、焼き付きが抑制されるという効果を奏する。

## [0085]

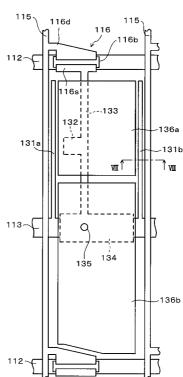

## (変形例2)

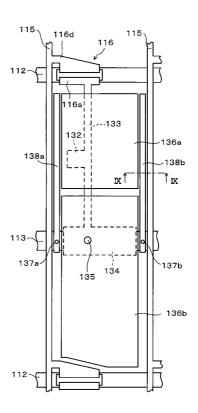

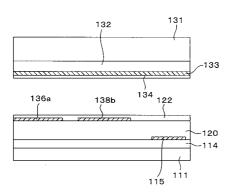

図17は第1の実施形態の変形例2の液晶表示装置を示す平面図、図18は図17のI X・IX線による断面図である。これらの図17,図18において、図15,図16と同 一物には同一符号を付して、その詳しい説明は省略する。

## [0086]

図17,図18に示す変形例2の液晶表示装置においては、フローティング副画素電極136aとデータバスライン115との間に、副画素電極136aと同じ層に形成されたシールドパターン138a,138bが配置されている。これらのシールドパターン138a,138bは、第1及び第2の絶縁膜114,120に形成されたコンタクトホール137a,137bを介して補助容量バスライン113に電気的に接続されている。補助容量バスライン113は、変形例1の液晶表示装置と同様に、コモン電極133と同電位、又はコモン電極133の電位に対し一定の電位に維持される。

# [0087]

図15,図16に示す変形例1の液晶表示装置ではシールドパターン131a,131 b がデータバスライン115及び副画素電極136aよりも下層に形成されているのに対し、変形例2の液晶表示装置ではシールドパターン138a,138 b が副画素電極136aと同じ層に形成されている。このため、変形例2の液晶表示装置では第1の絶縁膜114の抵抗成分がなくなり、変形例1の液晶表示装置に比べて副画素電極136aをデータバスライン115からシールドする効果が大きい。これにより、変形例2の液晶表示装置に比べて焼き付きをより一層確実に回避することができる。

## [0088]

# (変形例3)

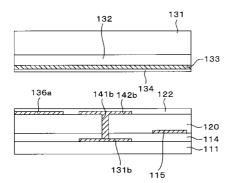

図19は第1の実施形態の変形例3の液晶表示装置を示す平面図、図20は図19のX-X線による断面図である。これらの図19,図20において、図15,図16と同一物には同一符号を付して、その詳しい説明は省略する。

# [0089]

50

10

20

30

図19,図20に示す変形例3の液晶表示装置においては、フローティング副画素電極136aとデータバスライン115との間に、補助容量バスライン113から延びるシールドパターン131a,131bと、副画素電極136aと同じ層に形成されたシールドパターン142a,142bは、第1及び第2の絶縁膜114,120に形成されたコンタクトホール141a,141bを介してシールドパターン131a,15に電気的に接続されている。

#### [0090]

この変形例3の液晶表示装置においても、フローティング副画素電極136aとデータバスライン115との間にシールドパターン131a,131b,142a,142bが形成されているので、データバスライン115に流れる直流電圧成分によるフローティング副画素電極136への電荷の蓄積が抑制され、焼き付きを回避することができる。

10

#### [0091]

#### (変形例4)

図21は、第1の実施形態の変形例4の液晶表示装置を示す平面図である。この図21 において、図15と同一物には同一符号を付してその詳しい説明は省略する。

#### [0092]

図21に示す変形例4の液晶表示装置においては、フローティング副画素電極136aの周囲を、補助容量バスライン113と同じ層に形成されて補助容量バスライン113に接続したシールドパターン143が囲んでいる。

# [0093]

20

この変形例4の液晶表示装置においては、データバスライン115に流れる信号に含まれる直流電圧成分だけでなく、データバスライン112に流れる信号に含まれる直流電圧成分もシールドすることができるので、変形例1の液晶表示装置に比べて焼き付きをより一層確実に回避できるという効果を奏する。

## [0094]

#### (変形例5)

図 2 2 は、第 1 の実施形態の変形例 5 の液晶表示装置を示す平面図である。この図 2 2 において、図 1 3 と同一物には同一符号を付して、その詳しい説明を省略する。

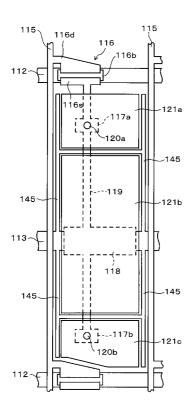

## [0095]

30

図22に示す液晶表示装置では、フローティング副画素電極121bと図22の上側及び下側に示すゲートバスライン112との間に副画素電極121a,121cが配置されている。これらの副画素電極121a,121cは、コンタクトホール120a,120b及び配線119を介してTFT116と電気的に接続されている。また、フローティング副画素電極121bと図22の右側及び左側のデータバスライン115との間には、それぞれ補助容量バスライン113から延び出したシールドパターン145が配置されている。

# [0096]

この変形例5の液晶表示装置では、副画素電極121a,121c及びシールドパターン145によりフローティング副画素電極121bがゲートバスライン112及びデータバスライン115からシールドされるので、ゲートバスライン112及びデータバスライン115を流れる信号の直流電圧成分による電荷の蓄積が抑制され、焼き付きを効果的に回避できるという効果を奏する。

40

50

## [0097]

また、変形例 5 の液晶表示装置においては、TFT116に電気的に接続している副画素電極 1 2 1 a , 1 2 1 b とデータバスライン 1 1 5 との間にもシールドパターン 1 4 5 が配置されているので、データバスライン 1 1 5 を流れる信号に含まれる直流電圧成分による副画素電極 1 2 1 a , 1 2 1 b への電荷の蓄積が抑制されるという効果もある。

# [0098]

# (変形例6)

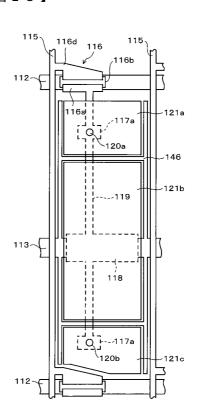

図23は、第1の実施形態の変形例6の液晶表示装置を示す平面図である。この図23

において、図22と同一物には同一符号を付して、その詳しい説明を省略する。

#### [0099]

図23に示す変形例6の液晶表示装置においては、フローティング副画素電極121bと、TFT116に直結した副画素電極121a,121cとの間にも、補助容量バスライン113と同じ層に形成されて補助容量バスライン113に接続しているシールドパターン146が配置されている。この変形例6の液晶表示装置においても、ゲートバスライン112及びデータバスライン115を流れる信号の直流電圧成分による電荷の蓄積が抑制され、焼き付きを効果的に回避できる。

# [0100]

(変形例7)

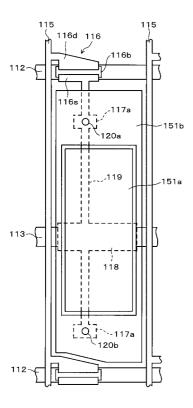

図24は、第1の実施形態の変形例7の液晶表示装置を示す平面図である。この図24 において、図13と同一物には同一符号を付してその詳しい説明は省略する。

#### [0101]

図 2 4 に示す変形例 7 の液晶表示装置においては、フローティング副画素電極 1 5 1 a の周囲を、副画素電極 1 5 1 b が囲んでいる。この副画素電極 1 5 1 b は、コンタクトホール 1 2 0 a , 1 2 0 b 及び配線 1 1 9 を介してTFT 1 1 6 のソース電極 1 1 6 s と電気的に接続されている。

#### [0102]

この変形例 7 の液晶表示装置においても、フローティング副画素電極 1 5 1 a がゲートバスライン 1 1 2 及びデータバスライン 1 1 5 からシールドされるので、ゲートバスライン 1 1 2 及びデータバスライン 1 1 5 を流れる信号の直流電圧成分による電荷の蓄積が抑制され、焼き付きを効果的に回避できるという効果を奏する。

## [0103]

(第2の実施形態)

以下、本発明の第2の実施形態について説明する。

## [0104]

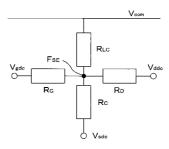

図25は、本発明の第2の実施形態の原理を示す図である。この図25は、フローティング副画素電極F<sub>SE</sub>とコモン電極、制御電極、ゲートバスライン及びデータバスラインとの間の等価回路を示している。

# [0105]

図 2 5 に示すように、フローティング副画素電極  $F_{SE}$ とゲートバスラインとの間には抵抗  $R_D$  が存在し、フローティング副画素電極  $F_{SE}$ とデータバスラインとの間には抵抗  $R_D$  が存在し、フローティング副画素電極  $F_{SE}$ と制御電極との間には抵抗  $R_C$  が存在し、フローティング副画素電極  $F_{SE}$ とコモン電極との間には抵抗(液晶抵抗)  $R_{LC}$ が存在するということができる。ここで、制御電極の電位を  $V_{sdc}$  、コモン電極の電位を  $V_{com}$  、ゲートバスラインを流れる信号の直流電圧成分(中心電位)を  $V_{gdc}$  、データバスラインを流れる信号の直流電圧成分(中心電位)を  $V_{gdc}$  とする。

## [0106]

前述したように、ゲートバスラインには、TFTをオフにするために、コモン電極の電位に対し - 12 V程度の直流電圧が印加される。また、データバスラインには、フィードスルー電圧を補償するために、コモン電極の電位に対し + 2 V程度の直流電圧を表示信号に重畳させている。ゲートバスラインに印加される直流電圧成分とデータバスラインに印加される直流電圧成分とは逆極性であるので、下記(4)式が成り立つように $V_{\rm ddc}$ ,  $V_{\rm gdc}$ 、 $R_{\rm g}$  及び $R_{\rm d}$  の値を設定すれば、ゲートバスライン及びデータバスラインを流れる信号の直流電圧成分によるフローティング副画素電極への電荷の蓄積が防止され、ひいては焼き付きの発生を防止することができる。

## [0107]

# 【数4】

$V_{ddc} \times R_g - V_{gdc} \times R_d = 0 \quad \cdots \quad (4)$

10

30

20

ゲートバスラインに流れる信号の直流電圧成分の影響の大きさ及びデータバスラインに流れる信号の直流電圧成分の影響の大きさは、電位差と抵抗とにより決定される。しかし、電位差  $V_{\rm adc}$  ,  $V_{\rm gdc}$  は TFTの性能などにも関係し、調整の自由度は比較的小さい。一方、抵抗  $R_{\rm g}$  ,  $R_{\rm d}$  はフローティング副画素電極の大きさ、形状及び位置、並びに絶縁膜の厚さなどにより決定され、自由度は比較的大きい。そこで、本実施形態においては、ゲートバスラインに流れる信号の直流電圧成分の影響とデータバスラインに流れる信号の直流電圧成分の影響を相殺するように、フローティング副画素電極とゲートバスライン及びデータバスラインとの間の抵抗  $R_{\rm g}$  ,  $R_{\rm d}$  を調整する。

# [0108]

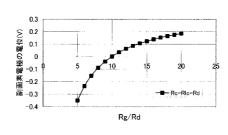

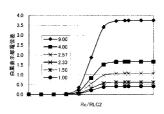

図 2 6 は、横軸に  $R_g$  /  $R_d$  の値をとり、縦軸にフローティング副画素電極の最終到達電位をとって、それらの関係を示す図である。但し、図 2 6 において、抵抗  $R_C$  、  $R_{LC}$  及び  $R_d$  は同じ( $R_C$  =  $R_{LC}$  =  $R_d$  )としている。また、  $V_{com}$  及び  $V_{sdc}$  はいずれも 0  $V_{sdc}$  は - 1 1 . 2 8  $V_{com}$  としている。この場合、図 2 6 からわかるように、抵抗  $R_d$  の値を抵抗  $R_g$  の 1 0 倍( $R_g$  /  $R_d$  = 1 0 )とすると、ゲートバスラインに流れる信号の直流電圧成分の影響がデータバスラインに流れる直流電圧成分の影響により相殺され、焼き付きの発生を防止することができる。

## [0109]

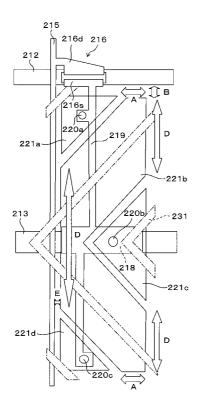

図27は、フローティング副画素電極とゲートバスライン及びデータバスラインとの間の抵抗を調整する方法を示す液晶表示装置の画素部の模式平面図、図28は同じくその模式断面図である。

#### [0110]

図27,図28に示す液晶表示装置は、ゲートバスライン212とデータバスライン215とにより区画される画素領域毎に、TFT216と4つの副画素電極221a~221dと、制御電極218とを有している。

#### [0111]

制御電極218は、配線219を介してTFT216のソース電極216sに電気的に接続されている。また、副画素電極221a,221dはコンタクトホール220a,220c及び配線219を介してTFT216のソース電極と電気的に接続されており、副画素電極221cはコンタクトホール220b、制御電極218及び配線219を介して制御電極218に電気的に接続されている。一方、副画素電極(フローティング副画素電極)221bは、第2の絶縁膜220を介して制御電極218と容量結合している。

# [0112]

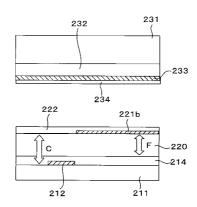

図28に示すように、ゲートバスライン212及び補助容量バスライン213はガラス基板211の上に形成されており、第1の絶縁膜214に覆われている。第1の絶縁膜214の上にはデータバスライン215、ソース電極216s、ドレイン電極216は、制御電極218及び配線219が形成されている。これらのデータバスライン215、ソース電極216s、ドレイン電極216d、制御電極218及び配線219は第2の絶縁膜220に覆われており、第2の絶縁膜220上に副画素電極221a~221dが形成されている。これらの副画素電極221a~221dは、ゲートバスライン212及び補助容量バスライン213の上方で屈曲するジグザグの線に沿って形成されたスリットにより分割されている。

#### [0113]

なお、図27において、一点鎖線231は対向基板側に形成される土手状の突起(ドメイン規制用構造物)の位置を示している。

#### [0114]

このような液晶表示装置において、ゲートバスライン 2 1 2 とフローティング副画素電極 2 2 1 b とが対向する部分の長さ(図 2 7 中に矢印 A で示す部分)を長くすると抵抗 R  $_g$  の値が減少し、短くすると抵抗 R  $_g$  の値が増加する。また、ゲートバスライン 2 1 2 と フローティング副画素電極 2 2 1 b との間の距離(図 2 7 中に矢印 B で示す部分)を大きくすると抵抗 R  $_g$  の値が増加し、小さくすると抵抗 R  $_g$  の値が減少する。更に、第 1 の絶

10

20

30

40

縁膜214と第2の絶縁膜220との合計の厚さ(図28中に矢印Cで示す部分)を厚くするとR。の値が増加し、薄くすると抵抗R。の値が減少する。

# [0115]

また、データバスライン 2 1 5 とフローティング副画素電極 2 2 1 b とが対向する部分の長さ(図 2 7 中に矢印 D で示す部分)を長くすると抵抗 R 。の値が減少し、短くすると抵抗 R 。の値が増加する。更に、データバスライン 2 1 5 とフローティング副画素電極 2 2 1 b との間の距離(図 2 7 中に矢印 E で示す部分)を大きくすると抵抗 R 。が増加し、小さくすると抵抗 R 。の値が減少する。更にまた、第 2 の絶縁膜 2 2 0 の厚さ(図 2 8 中に矢印 F で示す部分)を厚くすると抵抗 R 。が増加し、薄くすると抵抗 R 。の値が減少する。

[0116]

第2の実施形態においては、これらのパラメータを調整することにより、ゲートバスライン 2 1 2 に流れる信号に含まれる直流電圧成分の影響とデータバスライン 2 1 5 に流れる信号に含まれる直流電圧成分の影響とを打ち消す。これにより、焼き付きを回避できて、良好な表示特性を得ることができる。

[0117]

(第3の実施形態)

以下、本発明の第3の実施形態について説明する。

【 0 1 1 8 】

前述した(3)式を変形すると、下記(5)式が得られる。

[0119]

【数5】

$$\Delta V_{LC2} = \frac{((R_{LC2} \times C_{LC2}) - (R_C \times C_C))}{(R_{LC2} + R_C) \times C_{LC2}} \times \Delta V_S$$

$$= \frac{(1 - (R_C / R_{LC2} \times C_C / C_{LC2}))}{(1 + R_C / R_{LC2})} \times \Delta V_S \quad \cdots (5)$$

この(5)式において、制御電極とフローティング副画素電極との間の容量  $C_c$  とフローティング副画素電極とコモン電極との間との間の容量(液晶容量)  $C_{LC2}$  との比  $C_c$  /  $C_{LC2}$  は、TFTに直結した副画素電極の電圧とフローティング副画素電極の電圧との電圧比に応じて決定される設計値である。

[0120]

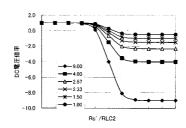

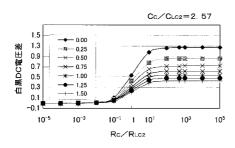

図 2 9 は、横軸に R  $_{\rm C}$  と R  $_{\rm LC2}$  との比をとり、縦軸に直流電圧の倍率をとって、 C  $_{\rm C}$  / C  $_{\rm LC2}$  を一定( C  $_{\rm C}$  / C  $_{\rm LC2}$  = 1 . 0 0 ~ 9 . 0 0 )にした状態で制御電極とフローティング副画素電極との間の抵抗 R  $_{\rm C}$  とフローティング副画素電極とコモン電極との間の抵抗 R  $_{\rm LC2}$  に対する焼き付き電圧の依存性( D C 電圧倍率)を計算した結果を示す図、図 3 0 は同じくその計算値を示す図である。

[0121]

図3,図4に示す構造の液晶表示装置の場合、液晶の比抵抗はTFTの絶縁膜の比抵抗に比べて2桁以上低いため、 $R_C$  /  $R_{LC2}$  の値は10 $^3$  に近い値となる。このような場合、図29,図30からわかるように、直流電圧の倍率は $C_C$  /  $C_{LC2}$  にほぼ等しくなる。容量結合HT法ではフローティング副画素電極とTFTに直結した副画素電極との電圧比は0.9~0.6程度に設定されるため、直流電圧の倍率は最大で9程度になり、焼き付きが発生しやすくなる

一方、図31から、制御電極とフローティング副画素電極との間の  $R_{\rm C}$  を低下させることでフローティング副画素電極の電圧を大きく下げることができることがわかる。図31は、横軸に  $R_{\rm C}$  /  $R_{\rm LC2}$  の値をとり、縦軸に白表示部及び黒表示部の副画素電極の電位差をとって、それらの関係を示す図である。ここでは、 $C_{\rm LCON}$  /  $C_{\rm LCoff}$  = 1.5として計算している。

[0122]

10

30

20

40

20

30

40

50

この図31からわかるように、フローティング副画素電極の電圧(直流電圧成分)を下げるためには、 $R_C$ の値が $R_{LG2}$ の値の100倍以下であることが必要である。

## [0123]

但し、制御電極とフローティング副画素電極との間の抵抗R<sub>C</sub>が低くなると、フローティング副画素電極とTFTに直結した副画素電極との間で電流が流れるため、これらの副画素電極間の電位差が徐々に失われて、容量結合HT法による白茶け抑制の効果が小さくなってしまう。

## [0124]

### [0125]

#### 【数6】

$VC(t) = VC(0) \times exp - (t/(Cse+CC) \times R) \quad \cdots \quad (6)$

但し、CseはC1とC2との直列接続容量(Cse=(1/((1/C1)-(1/C2)))である。

### [0126]

図33は、横軸にフローティング副画素電極とTFTに直結した副画素電極との間の抵抗Rをとり、縦軸に1フレーム期間(t=16.6msec)における電圧保持率をとって、それらの関係を示す図である。但し、ここでは図3,図4に示す構造の液晶表示装置を想定しており、画素ピッチを125μm、フローティング副画素電極とTFTに直結した副画素電極との面積比を3:7、フローティング副画素電極に印加される表示電圧とTFTに直結した副画素電極に印加される表示電圧との比を0.72として計算している。

## [0127]

この図33からわかるように、例えばフローティング副画素電極とTFTに直結した副画素電極との間の抵抗を10<sup>11</sup> 以上にすれば、電圧保持率が約90%以上に維持される。電圧保持率が50%よりも低くなると抵抗のばらつきによる電位差の変動が最大になることから、表示の安定性を考慮すれば電圧保持率を50%以上とすることが好ましい、

以上のことから、 $R_C$  が  $R_{LC2}$  の 1 0 0 倍以下であり、 1 フレーム期間の電圧保持率が 5 0 %以上となるようにフローティング副画素電極とTFT に直結した副画素電極との間の抵抗 R を設定することにより、焼き付きを防止する効果が得られる。

#### [0128]

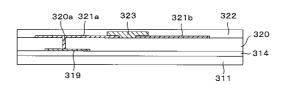

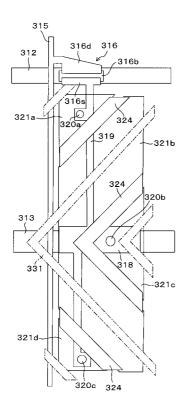

図34は、上記の対策を施した第3の実施形態の液晶表示装置のTFT基板を示す平面図、図35は同じくその断面図である。

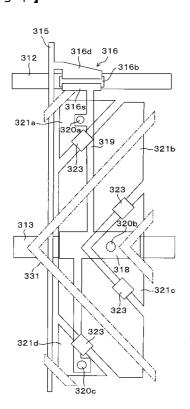

#### [0129]

図34に示すように、TFT基板には、水平方向に延びる複数(図34では1本のみ図示)のゲートバスライン312と、垂直方向に延びる複数(図34では1本のみ図示)のデータバスライン315とが形成されている。これらのゲートバスライン312及びデータバスライン315により区画される矩形の領域がそれぞれ画素領域である。また、TFT基板には、画素領域を横断する補助容量バスライン313がゲートバスライン312と平行に形成されている。ゲートバスライン312及び補助容量バスライン313とデータバスライン315との間には後述するように第1の絶縁膜314が形成されており、この第1の絶縁膜314によりゲートバスライン312及び補助容量バスライン313とデータバスライン315との間が電気的に分離されている。

# [0130]

各画素領域には、TFT316と、制御電極318と、4つの副画素電極321a~3

2 1 d とが形成されている。TFT316のドレイン電極316はデータバスライン315 に接続しており、ソース電極316 s は配線319を介して制御電極318に接続されている。

## [0131]

副画素電極321a~321dは、ゲートバスライン312及び補助容量バスライン313の上で屈曲するジグザグの線に沿って形成されたスリットにより分離されている。そして、副画素電極321a、321dは、コンタクトホール320a,320c及び配線319を介してソース電極316sに電気的に接続されており、副画素電極321cはコンタクトホール320bを介して制御電極318に電気的に接続されている。また、副画素電極(フローティング副画素電極)321bは、後述する第2の絶縁膜320を介して制御電極318に容量結合している。更に、これらの副画素電極321a~321dは、高抵抗導電材料によりなる接続部323により電気的に接続されている。なお、制御電極318は補助容量電極を兼ねており、補助容量バスライン313及び第1の絶縁膜314とともに補助容量を構成する。

### [0132]

以下、図35を参照してTFT基板の層構造について説明する。

#### [0133]

TFT基板のベースとなるガラス基板 3 1 1 の上には、ゲートバスライン 3 1 2 及び補助容量バスライン 3 1 3 が形成されている。これらのゲートバスライン 3 1 2 及び補助容量バスライン 3 1 3 は、例えば C r 膜又は A 1 - T i 積層膜をフォトリソグラフィ法によりパターニングして同時に形成される。

#### [0134]

また、ガラス基板 3 1 1 の上には、S i N 又は S i O  $_2$  等の絶縁材料からなる第 1 の絶縁膜 3 1 4 が形成されており、この第 1 の絶縁膜 3 1 4 によりゲートバスライン 3 1 2 及び補助容量バスライン 3 1 4 が覆われている。

## [0135]

第1の絶縁膜314の上には、データバスライン315と、TFT316のソース電極316s及びドレイン電極316dと、制御電極318と、配線319とが形成されている。これらのデータバスライン315、ソース電極316s、ドレイン電極316d、制御電極318及び配線319は、例えばTi-Al-Ti積層膜をフォトリソグラフィ法によりパターニングして同時に形成される。

# [0136]

図34に示すように、TFT316はゲートバスライン312の一部をゲート電極としており、ゲート電極の上に活性層となる半導体膜(図示せず)とチャネル保護膜316b とが形成されている。ソース電極316s及びドレイン電極316dは、ゲートバスライン312を挟んで対向して配置されている。

# [0137]

#### [0138]

副画素電極321a~321dは、高抵抗の導電体材料からなる接続部323を介して電気的に接続されている。そして、副画素電極321a~321d及び接続部323の上には、例えばポリイミドからなる配向膜322が形成されている。

10

20

30

40

20

30

40

50

### [0139]

接続部323は例えば不純物を導入したアモルファスシリコンにより形成され、前述したようにフローティング副画素電極321bとTFT316に直結した副画素電極321a,321c,321dとの間の抵抗Rがフローティング副画素電極321bとコモン電極との間の抵抗の100倍以下であり、且つ1フレーム期間の電圧保持率が50%以上となるように設定される。

#### [0140]

接続部323の材料は上述したアモルファスシリコンに限定されるものではなく、例えば有機導電体物質により形成してもよい。しかし、接続部323の材料としては、適度な範囲の抵抗値を有し、且つ液晶を汚染するおそれがないことが好ましい。また、配向膜形成プロセス等に耐性があることも必要である。例えば、溶剤に溶けにくく、耐熱性が高いものが好ましい。

#### [0141]

なお、図34において、一点鎖線331は対向基板側に形成される土手状の突起(ドメイン規制用構造物)の位置を示している。

#### [0142]

本実施形態の液晶表示装置においては、フローティング副画素電極321bとTFT316に直結された副画素電極321a,321c,321dとの間が高抵抗の接続部323により電気的に接続され、フローティング副画素電極321bとTFT316に直結した副画素電極321a,321c,321dとの間の抵抗Rがフローティング副画素電極321bとコモン電極との間の抵抗の100倍以下であり、且つ1フレーム期間の電圧保持率が50%以上となるように設定されているので、白茶けを抑制できるとともに、焼き付きの発生を回避することができ、良好な表示品質が得られる。

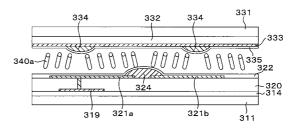

#### [0143]

## (変形例1)

図36は第3の実施形態の変形例1の液晶表示装置を示す平面図、図37は同じくその断面図である。これらの図36,図37において、図34,図35と同一物には同一符号を付してその詳しい説明は省略する。

## [0144]

この変形例1の液晶表示装置においては、フローティング副画素電極321bとTFT316に直結した副画素電極321a,321c,321dとの間を電気的に接続する接続部324が、副画素電極321a~321dを分離するスリットに沿って土手状に形成されている。接続部324は、例えば不純物を導入したアモルファスシリコン等の高抵抗の導電材料により形成されている。副画素電極321a~321d及び接続部324の表面は配向膜322に覆われている。

## [0145]

一方、対向基板のベースとなるガラス基板331の一方の面側(図37では下側)には、カラーフィルタ332及びコモン電極333が形成されており、コモン電極333の上(図37では下側)にはドメイン規制用突起334が土手状に形成されている。コモン電極333及び突起334の表面は配向膜335で覆われている。突起334は誘電体により形成してもよく、接続部324と同様に高抵抗の導電材料により形成してもよい。

#### [0146]

この液晶表示装置においては、図37に示すように、TFT基板側に形成された土手状の接続部324と対向基板側に形成された土手状の突起334とによりマルチドメインを達成することができる。すなわち、電圧印加時には液晶分子34aの傾斜方向が土手状の接続部324及び突起334の両側で異なり、斜め方向への光の漏れを防止することができる。

### [0147]

この液晶表示装置においても、フローティング副画素電極 3 2 1 b とTFT 3 1 6 に直結された副画素電極 3 2 1 a , 3 2 1 c , 3 2 1 d との間が例えばアモルファスシリコン

からなる高抵抗の接続部323により電気的に接続され、フローティング副画素電極32 1 b と制御電極318との間の抵抗がフローティング副画素電極321 b とコモン電極と の間の抵抗の100倍以下であり、且つ1フレーム期間の電圧保持率が50%以上となる ように設定されている。これにより、白茶けを抑制できるとともに、焼き付きの発生を回 避することができ、良好な表示品質が得られる。

## [0148]

なお、ドメイン規制用突起となる接続部324が低抵抗であると、接続部324全体が 画素電極321a~321dと同電位になるため、接続部324から基板面に対し垂直方 向に電気力線が発生するようになり、マルチドメインを達成することができなくなる。し かし、上記の例では接続部324が高抵抗の導電材料により形成されているため、液晶分 子を所定の方向に配向させることができる。

10

#### [0149]

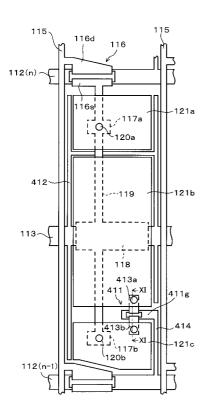

#### (第4の実施形態)

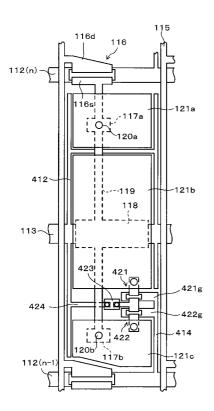

図38は本発明の第4の実施形態の液晶表示装置を示す平面図、図39は同じくそのXI-XI線における断面図である。これらの図38,図39において、図13,図14(a),(b)と同一物には同一符号を付してその詳しい説明は省略する。

## [0150]

本実施形態においては、ゲートバスライン 1 1 2 とデータバスライン 1 1 5 とにより区画される 1 画素領域に、 3 つの副画素電極 1 2 1 a ~ 1 2 1 c を有している。副画素電極 1 2 1 a , 1 2 1 c は第 2 の絶縁膜 1 2 0 に形成されたコンタクトホール 1 2 0 a , 1 2 0 b を介して、TFT 1 1 6 のソース電極 1 1 6 s から延び出した配線 1 1 9 に電気的に接続されている。また、副画素電極(フローティング副画素電極) 1 2 1 b は第 2 の絶縁膜 1 2 0 を挟んで制御電極 1 1 8 と容量結合している。

20

#### [0151]

副画素電極 1 2 1 b とデータバスライン 1 1 5 との間、及び副画素電極 1 2 1 b と副画素電極 1 2 1 a との間は、補助容量バスライン 1 1 3 と接続されたシールドパターン 4 1 2 によりシールドされている。

## [0152]

副画素電極 1 2 1 b と副画素電極 1 2 1 c との間には、TFT4 1 1 が形成されている。このTFT4 1 1 のゲート電極 4 1 1 g は、TFT 1 1 6 が接続されているゲートバスライン 1 1 2 ( n - 1 番目のゲートバスライン)とは別のゲートバスライン 1 1 2 ( n - 1 番目のゲートバスライン)に接続されており、ソース電極 4 1 1 s 及びドレイン電極 4 1 1 d はコンタクトホール 4 1 3 a , 4 1 3 b を介して副画素電極 1 2 1 b , 1 2 1 c に接続されている。

30

# [0153]

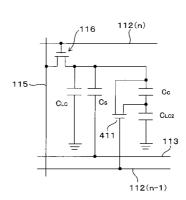

図40は、上述した液晶表示装置の1画素を示す等価回路図である。図40において、TFT116はn番目のゲートバスライン112(n)に接続されたTFTであり、上述したようにTFT116のソース電極116sは副画素電極121a,121c及び制御電極118に直結している。 $C_{LC}$ はTFT116に直結した副画素電極121a,121cとコモン電極133との間の容量(液晶容量)であり、 $C_{S}$ は制御電極118と補助容量バスライン113との間の容量(補助容量)である。また、 $C_{C}$ は制御電極118とフローティング副画素電極121bとの間の容量であり、 $C_{LC2}$ はフローティング副画素電極121bとコモン電極133との間の容量である。

40

# [0154]

更に、TFT411は、副画素電極121b,121c間に形成されたTFTであり、 そのゲート電極411gはn-1番目のゲートバスライン112(n-1)に接続されている。

# [0155]

本実施形態の液晶表示装置は、TFT116を介して副画素電極121a,121c及び制御電極118に表示電圧が印加される前(1水平走査期間の時間分だけ前)に、TF

20

30

40

50

T411がオンになってフローティング副画素電極121bの電位がTFT116に直結した副画素電極121a,121c及び制御電極118の電位と同じになる。これにより、ゲートバスライン112及びドレインバスライン115に流れる信号に含まれる直流電圧成分に起因してフローティング副画素電極121bに蓄積された電荷が、副画素電極121a,121c及び制御電極118に流れる。従って、フローティング副画素電極121bへの電荷の蓄積が抑制され、焼き付きが回避されるという効果が得られる。

#### [0156]

# (変形例1)

図41は第4の実施形態の液晶表示装置の変形例1を示す平面図である。この図41において、図38と同一物には同一符号を付してその詳しい説明は省略する。

#### [0157]

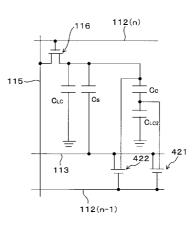

本実施形態においては、TFT116に直結した副画素電極121cとフローティング副画素電極121bとの間に、2つのTFT421,422が配置されている。これらのTFT421,422はドレイン電極同士が接続されている。また、TFT421,422のゲート電極421g,422gは配線414を介してn-1番目のゲートバスライン122(n)に接続されており、ソース電極はそれぞれフローティング副画素電極121b、副画素電極121cに接続されている。そして、TFT421,422のドレイン電極は、接続部423及び配線424を介して、補助容量バスライン113から延び出したシールドパターン412に接続されている。

# [0158]

図42は上述した液晶表示装置の1画素を示す等価回路図である。図42において、TFT116はn番目のゲートバスライン112(n)に接続されたTFTであり、このTFT116のソース電極116sは副画素電極121a,121c及び制御電極118に電気的に接続している。 $C_{LC}$ はTFT116に直結した副画素電極121a,121cとコモン電極133との間の容量(液晶容量)であり、 $C_{S}$ は制御電極118と補助容量バスライン113との間の容量(補助容量)である。また、 $C_{C}$ は制御電極118とフローティング副画素電極121bとの間の容量であり、 $C_{LC2}$ はフローティング副画素電極121bとコモン電極133との間の容量である。

# [0159]

更に、TFT421,422は副画素電極121b,121c間に接続されたTFTである。このTFT421のゲート電極はn-1番目のゲートバスライン112(n-1)に接続され、ソース電極及びドレイン電極はフローティング副画素電極121bと容量バスライン113との間に接続されている。また、TFT422のゲート電極もn-1番目のゲートバスライン112(n-1)に接続され、ソース電極及びドレイン電極は副画素電極121cと補助容量バスライン113との間に接続されている。なお、補助容量バスライン113は、TFT基板側のコモン電極と同電位に維持されるものとする。

# [0160]

本実施形態の液晶表示装置においても、TFT116を介して副画素電極121a,121c及び制御電極118に表示電圧が印加される前(1水平走査期間の時間分だけ前)に、TFT421,422がオンになってフローティング副画素電極121b及びTFT116に直結された副画素電極121a,121cの電位が補助容量バスライン113の電位と同じになる。これにより、ゲートバスライン112及びドレインバスライン115に流れる信号に含まれる直流電圧成分に起因してフローティング副画素電極121b及び副画素電極121a,121cに蓄積された電荷が、補助容量バスライン113に流れる。従って、フローティング副画素電極121bへの電荷の蓄積が抑制され、焼き付きを回避できるという効果を得ることができる。

#### [0161]

なお、上記の変形例1ではTFT116に直結した副画素電極121a,121cに蓄積される電荷をTFT422を介して補助容量バスライン113に流すものとしたが、前述したようにこれらの副画素電極121a,121cは1フレーム毎にデータバスライン

1 1 5 に接続されるので、副画素電極 1 2 1 a , 1 2 1 c に蓄積される電荷の影響は極めて少ない。従って、TFT 4 2 2 を省略することも可能である。

#### [0162]

(第5の実施形態)

以下、本発明の第5の実施形態について説明する。

#### [0163]

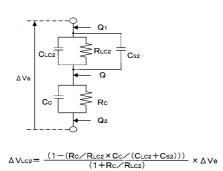

図 4 3 は第 5 の実施形態の原理を示す画素の回路図である。この図 4 3 において、 $C_c$ ,  $R_c$  はそれぞれ制御電極とフローティング副画素電極との間の容量及び抵抗であり、 $C_{LC2}$ ,  $R_{LC2}$  はそれぞれフローティング副画素電極とコモン電極との間の容量(液晶容量)及び抵抗(液晶抵抗)である。

## [0164]

前述したように、白表示部と黒表示部でフローティング副画素電極に電位差が生じる原因の一つは、液晶容量  $C_{LC2}$  が変動するためである。そこで、第 5 の実施形態においては、液晶容量  $C_{LC2}$  に並列に補助容量  $C_{S2}$  を接続し、フローティング副画素電極とコモン電極との間の容量の変動の影響を小さくする。

#### [0165]

図 4 4 は、横軸に  $R_C$  /  $R_{LC2}$  をとり、縦軸に白表示部及び黒表示部のフローティング副画素電極の電位差をとって、補助容量  $C_{S2}$ がないとき( 0 . 0 0 倍)、及び補助容量  $C_{S2}$ の値が液晶容量  $C_{LC2}$  の値の 0 . 2 5 倍~ 1 . 5 倍のときの  $R_C$  /  $R_{LC2}$  と、白表示部及び黒表示部のフローティング副画素電極の電位差との関係を示す図である。但し、ここでは、  $C_C$  /  $C_{LC2}$  の値は 2 . 5 7 としている。

#### [ 0 1 6 6 ]

この図 4 4 と図 3 1 との比較からわかるように、液晶容量  $C_{LC2}$  に並列に補助容量  $C_{S2}$  を接続することにより、白表示部及び黒表示部のフローティング副画素電極の電位差が減少する。例えば、補助容量  $C_{S2}$  の値が液晶容量  $C_{LC2}$  の値と同じ( $C_{S2}$  /  $C_{LC2}$  = 1 . 0 0 )であるとすると、焼き付きの原因となる白表示部及び黒表示部のフローティング副画素電極の電位差は、ほぼ 1 / 2 に減少する。

#### [0167]

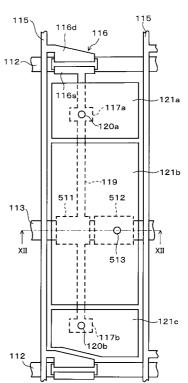

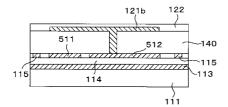

図45は上述の対策を施した液晶表示装置を示す平面図、図46は図45のXII-XII 線による断面図である。図45,図46において、図13,図14(a),(b)と同一物には同一符号を付してその詳しい説明は省略する。

# [0168]

本実施形態の液晶表示装置においては、補助容量バスライン113の上方に、制御電極511と補助容量電極512とが形成されている。制御電極511は、第2の絶縁膜140を介してフローティング副画素電極121bに容量結合している。また、制御電極511は配線119を介してTFT116のソース電極116sに電気的に接続されているとともに、配線119とコンタクトホール120a,120bを介して副画素電極121a,121cに電気的に接続されている。更に、制御電極511は、補助容量バスライン113及び第1の絶縁膜114とともに第1の補助容量を構成している。なお、補助容量バスライン113は、対向基板側のコモン電極と同電位に維持されるものとする。

# [0169]

補助容量電極 5 1 2 は、第 2 の絶縁膜 1 4 0 に形成されたコンタクトホール 5 1 3 を介してフローティング副画素電極 1 2 1 b に電気的に接続している。また、補助容量電極 5 1 2 は、補助容量バスライン 1 1 3 及び第 1 の絶縁膜 1 1 4 とともに第 2 の補助容量 C <sub>S2</sub> を構成している。

# [0170]

本実施形態においては、図43の等価回路図に示すように、液晶容量 $C_{LC2}$ と並列に補助容量 $C_{S2}$ を設けているので、白表示部及び黒表示部のフローティング副画素電極の電位差が小さくなり、焼き付きの発生を防止することができる。

## [0171]

50

10

20

30

なお、補助容量電極 5 1 2 を設けないでフローティング副画素電極 1 2 1 b と補助容量 バスライン 1 1 3 とにより補助容量  $C_{S2}$ を構成することも考えられる。しかし、その場合はフローティング副画素電極 1 2 1 b と補助容量バスライン 1 1 3 との間に第 1 及び第 2 の絶縁膜 1 1 4 , 1 2 0 が介在するため、補助容量  $C_{S2}$ の容量値が小さくなり、焼き付きの発生を防止する効果が小さくなってしまう。このため、上述したように第 1 の絶縁膜 1 1 4 上に補助容量電極 5 1 2 を形成し、この補助容量電極 5 1 2 とフローティング副画素電極 1 2 1 b とを電気的に接続することが好ましい。

## [0172]

上記第1~第5の実施形態に示した焼き付き防止方法は、TN型液晶表示装置及びVA型液晶表示装置など、種々の構造の液晶表示装置に適用することができる。また、本発明は、透過型液晶表示装置だけでなく、反射型液晶表示装置及び半透過型液晶表示装置に適用することもできる。

## [0173]

以下、本発明の諸態様を、付記としてまとめて記載する。

#### [0174]

(付記1)相互に対向して配置された第1及び第2の基板と、

前記第1及び第2の基板間に封入された液晶と、

前記第1の基板に形成されたゲートバスライン及びデータバスラインと、

前記ゲートバスライン及び前記データバスラインに接続された薄膜トランジスタと、

前記ゲートバスライン及び前記データバスラインにより区画される画素領域内に形成された複数の副画素電極と、

前記複数の副画素電極のうちの少なくとも1つと容量結合し、前記データバスラインから前記薄膜トランジスタを介して表示電圧が印加される制御電極とを有する液晶表示装置において、

前記制御電極と容量結合した副画素電極と前記ゲートバスライン及び前記データバスラインのうちの少なくとも一方のバスラインとの間を電気的にシールドするシールド部材を有することを特徴とする液晶表示装置。

#### [0175]

(付記2) 前記シールド部材が、前記複数の副画素電極のうち前記薄膜トランジスタに接続された副画素電極であることを特徴とする付記1に記載の液晶表示装置。

### [0176]

(付記3) 前記シールド部材となる副画素電極が、前記制御電極と容量結合した副画素電極の周囲を囲んでいることを特徴とする付記2に記載の液晶表示装置。

### [ 0 1 7 7 ]

(付記4) 更に、一定の電位に維持され、前記制御電極と容量結合して補助容量を構成する補助容量バスラインを有することを特徴とする付記1に記載の液晶表示装置。

#### [0178]

(付記 5) 前記シールド部材が前記補助容量バスラインに電気的に接続されていることを特徴とする付記 4 に記載の液晶表示装置。

## [0179]

(付記6) 前記シールド部材が、前記副画素電極と同じ層に形成されていることを特徴とする付記5に記載の液晶表示装置。

## [0180]

(付記 7) 前記制御電極と容量結合した副画素電極と前記ゲートバスラインとの間に前記シールド部材として前記複数の副画素電極のうち前記薄膜トランジスタに接続された副画素電極が配置され、前記制御電極と容量結合した副画素電極と前記データバスラインとの間に前記補助容量バスラインに電気的に接続したシールド部材が配置されていることを特徴とする付記 4 に記載の液晶表示装置。

# [0181]

(付記8) 相互に対向して配置された第1及び第2の基板と、

10

20

30

40

前記第1及び第2の基板間に封入された液晶と、

前記第1の基板に形成されたゲートバスライン及びデータバスラインと、

前記ゲートバスライン及び前記データバスラインに接続された薄膜トランジスタと、

前記ゲートバスライン及び前記データバスラインにより区画される画素領域内に形成された複数の副画素電極と、

前記複数の副画素電極のうちの少なくとも 1 つと容量結合し、前記データバスラインから前記薄膜トランジスタを介して表示電圧が印加される制御電極と、

前記第2の基板に形成されて前記第1の基板の前記複数の副画素電極に対向するコモン電極とを有する液晶表示装置の焼き付き防止方法であって、

前記コモン電極の電位に対する前記ドレインバスラインの中心電位を $V_{\rm ddc}$ 、前記コモン電極の電位に対する前記ゲートバスラインの中心電位を $V_{\rm gdc}$ 、前記制御電極と容量結合した副画素電極と前記データバスラインとの間の抵抗を $R_{\rm d}$ 、前記制御電極と容量結合した副画素電極と前記ゲートバスラインとの間の抵抗を $R_{\rm g}$  としたときに、 $V_{\rm ddc}$  ・  $V_{\rm gd}$  。 ×  $R_{\rm d}$  /  $R_{\rm g}$  がほぼ 0 となるように前記制御電極と容量結合した副画素電極の大きさ、形状及び位置並びに絶縁膜の厚さを設定することを特徴とする液晶表示装置の焼き付き防止方法。

## [0182]

(付記9) 相互に対向して配置された第1及び第2の基板と、

前記第1及び第2の基板間に封入された液晶と、

前記第1の基板に形成されたゲートバスライン及びデータバスラインと、

前記ゲートバスライン及び前記データバスラインに接続された薄膜トランジスタと、

前記ゲートバスライン及び前記データバスラインにより区画される画素領域内に形成された複数の副画素電極と、

前記複数の副画素電極のうちの少なくとも1つと容量結合し、前記データバスラインから前記薄膜トランジスタを介して表示電圧が印加される制御電極と、

前記第2の基板に形成されて前記第1の基板の複数の副画素電極に対向するコモン電極とを有する液晶表示装置において、

前記制御電極と容量結合した副画素電極と、前記薄膜トランジスタに接続された副画素電極との間が、抵抗体を介して接続されていることを特徴とする液晶表示装置。

# [0183]

(付記10) 前記抵抗体の抵抗値が、前記制御電極と容量結合した副画素電極と前記コモン電極との間の抵抗 R<sub>LC</sub>の抵抗値の100倍以下であることを特徴とする付記9に記載の液晶表示装置。

# [0184]

(付記11) 前記抵抗体の抵抗値が、前記制御電極と容量結合した副画素電極の1フレーム期間における電圧保持率が50%以上となるように設定されていることを特徴とする付記9に記載の液晶表示装置。

## [0185]

(付記12) 前記抵抗体が、シリコンにより形成されていることを特徴とする付記9 に記載の液晶表示装置。

# [0186]

(付記13) 前記抵抗体が前記複数の副画素電極間を分離するスリットに沿って土手状に形成され、該抵抗体が液晶分子の傾斜方向を決めるドメイン規制用構造物の少なくとも一部を構成することを特徴とする付記9に記載の液晶表示装置。

#### [0187]

(付記14) 相互に対向して配置された第1及び第2の基板と、

前記第1及び第2の基板間に封入された液晶と、

前記第1の基板に形成されたゲートバスライン及びデータバスラインと、

前記ゲートバスライン及び前記データバスラインに接続された薄膜トランジスタと、

前記ゲートバスライン及び前記データバスラインにより区画される画素領域内に形成さ

10

20

30

40

れた複数の副画素電極と、

前記複数の副画素電極のうちの少なくとも 1 つと容量結合し、前記データバスラインから前記薄膜トランジスタを介して表示電圧が印加される制御電極と、

一定の電位に保持され、前記制御電極との間で補助容量を構成する補助容量バスライン とを有する液晶表示装置において、

前記制御電極と容量結合した副画素電極と前記補助容量バスラインとの間、又は前記制御電極と容量結合した副画素電極と前記薄膜トランジスタに接続した副画素電極との間に、前記薄膜トランジスタが接続されたゲートバスラインとは別のゲートバスラインに流れる信号で駆動するスイッチング素子を有することを特徴とする液晶表示装置。

[0188]

10

20

30

(付記15) 前記スイッチング素子が薄膜トランジスタであることを特徴とする付記 14に記載の液晶表示装置。

[0189]

(付記16) 相互に対向して配置された第1及び第2の基板と、

前記第1及び第2の基板間に封入された液晶と、

前記第1の基板に形成されたゲートバスライン及びデータバスラインと、

前記ゲートバスライン及び前記データバスラインに接続された薄膜トランジスタと、

前記ゲートバスライン及び前記データバスラインにより区画される画素領域内に形成された複数の副画素電極と、

前記複数の副画素電極のうちの少なくとも1つと容量結合し、前記データバスラインから前記薄膜トランジスタを介して表示電圧が印加される制御電極と、

一定の電位に保持され、前記制御電極との間で第1の補助容量を構成する補助容量バスラインとを有する液晶表示装置の焼き付き防止方法であって、

前記制御電極と容量結合した副画素電極と前記コモン電極との間の容量に並列に第2の補助容量を形成することを特徴とする液晶表示装置の焼き付き防止方法。

[0190]

(付記17) 相互に対向して配置された第1及び第2の基板と、

前記第1及び第2の基板間に封入された液晶と、

前記第1の基板に形成されたゲートバスライン及びデータバスラインと、

前記ゲートバスライン及び前記データバスラインに接続された薄膜トランジスタと、

前記ゲートバスライン及び前記データバスラインにより区画される画素領域内に形成された複数の副画素電極と、

前記複数の副画素電極のうちの少なくとも1つと容量結合し、前記データバスラインから前記薄膜トランジスタを介して表示電圧が印加される制御電極と、

一定の電位に保持され、前記制御電極との間で第1の補助容量を構成する補助容量バスラインと、

前記制御電極と容量結合する副画素電極と電気的に接続し、前記補助容量バスラインとの間で第2の補助容量を構成する補助容量電極と

を有することを特徴とする液晶表示装置。

[0191]

40

(付記18) 前記補助容量電極が、前記制御電極と前記補助容量バスラインとの間の層に形成されていることを特徴とする付記17に記載の液晶表示装置。

【図面の簡単な説明】

[0192]

【図1】図1(a),(b)は、MVA型液晶表示装置の一例を示す模式断面図である。

【図2】図2は、液晶表示装置の画面を正面から見たときのT-V(透過率-電圧)特性と、上60°の方向から見たときのT-V特性とを示す図である。

【図3】図3は、容量結合によるHT法を実現する液晶表示装置のTFT基板の一例を示す平面図である。

【図4】図4は、図3のI-I線による断面図である。

20

30

- 【図5】図5は、図3に示す液晶表示装置の1画素を示す等価回路図である。

- 【図6】図6は、特許第3076938号の明細書に開示された液晶表示装置を示す平面図である。

- 【図7】図7(a)~(c)は、焼き付きの程度を測定する試験方法を示す模式図(その1)である。

- 【図8】図8は、焼き付きの程度を測定する試験方法を示す模式図(その2)である。

- 【図9】図9は、フローティング副画素電極を備えた液晶表示装置の1画素を示す平面図である。

- 【図10】図10(a)は図9のII・II線の位置における模式断面図、図10(b)は図9のIII・III 線の位置における模式断面図、図10(c)は図9のIV・IV線の位置における模式断面図、図10(d)は図9のV・V線の位置における模式断面図である。

- 【図11】図11は、フローティング副画素電極により構成される副画素の等価回路を示す図である。

- 【図12】図12は、液晶層に表示電圧が印加されたとき(液晶ON)の Vs  $V_{LC}$  2 との関係と、液晶層に表示電圧が印加されていないとき(液晶OFF)の Vs  $V_{LC}$  との関係とを示す図である。

- 【図13】図13は、本発明の第1の実施形態に係る液晶表示装置を示す平面図である。

- 【図14】図14(a)は図13のVI-VI線による断面図、図14(b)は図13のVII-VII線による断面図である。

- 【図15】図15は、第1の実施形態の変形例1の液晶表示装置を示す平面図である。

- 【図16】図16は。図15のVIII VIII 線による断面図である。

- 【図17】図17は、第1の実施形態の変形例2の液晶表示装置を示す平面図である。

- 【図18】図18は、図17のIX-IX線による断面図である。

- 【図19】図19は、第1の実施形態の変形例3の液晶表示装置を示す平面図である。

- 【図20】図20は。図19のX-X線による断面図である。

- 【図21】図21は、第1の実施形態の変形例4の液晶表示装置を示す平面図である。

- 【図22】図22は、第1の実施形態の変形例5の液晶表示装置を示す平面図である。

- 【図23】図23は、第1の実施形態の変形例6の液晶表示装置を示す平面図である。

- 【図24】図24は、第1の実施形態の変形例7の液晶表示装置を示す平面図である。

- 【図25】図25は、本発明の第2の実施形態の原理を示す図である。

- 【図 2 6 】図 2 6 は、 R  $_{\rm g}$  / R  $_{\rm d}$  とフローティング副画素電極の最終到達電位との関係を示す図である。

- 【図27】図27は、フローティング副画素電極とゲートバスライン及びデータバスラインとの間の抵抗を調整する方法を示す液晶表示装置の画素部の模式平面図である。

- 【図28】図28は、同じくその模式断面図である。

- 【図 2 9 】図 2 9 は、制御電極とフローティング副画素電極との間の抵抗 R<sub>C</sub> とフローティング副画素電極とコモン電極との間の抵抗 R<sub>LC2</sub> に対する焼き付き電圧の依存性(D C電圧倍率)を計算した結果を示す図である。

- 【図30】図30は、同じくその計算値を示す図である。

- 【図31】図31は、R<sub>C</sub> / R<sub>LC2</sub> と白表示部及び黒表示部の副画素電極の電位差との関 40 係を示す図である。

- 【図32】図32は、フローティング副画素電極とTFTに直結した副画素電極とを示す 等価回路図である。

- 【図33】図33は、フローティング副画素電極とTFTに直結した副画素電極との間の抵抗Rと、1フレーム期間(t=16.6msec)における電圧保持率との関係を示す図である。

- 【図34】図34は、本発明の第3の実施形態の液晶表示装置のTFT基板を示す平面図である。

- 【図35】図35は、同じくその断面図である。

- 【図36】図36は、第3の実施形態の変形例1の液晶表示装置を示す平面図である。

- 【図37】図37は、同じくその断面図である。

- 【図38】図38は、本発明の第4の実施形態の液晶表示装置を示す平面図である。

- 【図39】図39は、図38のXI-XI線における断面図である。

- 【図40】図40は、第4の実施形態の液晶表示装置の1画素を示す等価回路図である。

- 【図41】図41は、第4の実施形態の液晶表示装置の変形例1を示す平面図である。

- 【図42】図42は、第4の実施形態の変形例1の液晶表示装置の1画素を示す等価回路図である。

- 【図43】図43は、本発明の第5の実施形態の原理を示す画素の回路図である。

- 【図44】図44は、R<sub>C</sub> / R<sub>LC2</sub> と、白表示部及び黒表示部のフローティング副画素電極の電位差との関係を示す図である。

- 【図45】図45は第5の実施形態の液晶表示装置を示す平面図である。

- 【図46】図46は、図45のXII-XII線による断面図である。

#### 【符号の説明】

- [0193]

- 10...TFT基板、

- 12...画素電極、

- 14,24,62,74,122,134,322,335...配向膜、

- 20...対向基板、

- 22,73,133,33...コモン電極、

- 23,231,331,334...突起(ドメイン規制用構造物)、

- 30,80,140...液晶、

- 5 1 , 7 1 , 1 1 1 , 1 3 1 , 2 1 1 , 3 1 1 , 3 3 1 ... ガラス基板、

- 5 2 , 1 1 2 , 2 1 2 , 3 1 2 ... ゲートバスライン、

- 53,113,213,313...補助容量バスライン、

- 54,60,114,120,214,220,314,320...絶縁膜、

- 5 5 , 1 1 5 , 2 1 5 , 3 1 5 ... データバスライン、

- 56,90,93,116,216,316,411,421,422...TFT

- 57,92a~92d,118,132,218,318,511...制御電極、

- 5 8 , 1 3 4 , 5 1 2 ... 補助容量電極、

- 59,133,219,319...配線、

- 61a,61b,91a~91d,121a~121c、136a,136b,151

- a , 1 5 1 b , 2 2 1 a ~ 2 2 1 d , 3 2 1 a ~ 3 2 1 d ...副画素電極、

- 71,132,332...カラーフィルタ、

- 131a,131b,138a,138b,142a,142b,143,145,1 46...シールドパターン、

- 323,324…高抵抗の接続部。

10

20

【図1】

# 【図2】

# 【図3】

# 【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

# 【図11】 【図13】

【図12】

# 【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

# 【図30】

|                 | 0.9   | 0.8   | 0.72  | 0.7   | 0.6   | 0.5   |

|-----------------|-------|-------|-------|-------|-------|-------|

|                 | 9.00  | 4.00  | 2.57  | 2.33  | 1.50  | 1.00  |

| 10-5            | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10-4            | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10-3            | 0.99  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10-2            | 0.90  | 0.95  | 0.97  | 0.98  | 0.98  | 0.99  |

| 10-1            | 0.09  | 0.55  | 0.70  | 0.77  | 0.82  | 0.88  |

| 1               | -4.00 | -1.50 | -0.67 | -0.25 | 0.00  | 0.25  |

| 101             | -8.09 | -3.55 | -2.03 | -1.27 | -0.82 | -0.36 |

| 10 <sup>2</sup> | -8.90 | -3.95 | -2.30 | -1.48 | -0.98 | -0.49 |

| 10 <sup>3</sup> | -8.99 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

| 104             | -9.00 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

| 10 <sup>5</sup> | -9.00 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

# 【図32】

# 【図33】

【図31】

1フレーム(16. 6msec)後の電圧保持率

120

100

86) 80

世 40

世 40

107 108 109 1010 1011 1012 1013 1014

副画素電極間抵抗R(Ω)

【図34】

# 【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図45】

# 【図44】

【図46】

## フロントページの続き

(72)発明者 鎌田 豪

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 笹林 貴

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 上田 一也

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 吉田 秀史

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

## 審査官 小濱 健太

(56)参考文献 特開平04-348323(JP,A)

特開2002-258307(JP,A)

国際公開第94/022046(WO,A1)

(58)調査した分野(Int.CI., DB名)

G02F 1/1368

G02F 1/1343

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                              |         |            |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | JP4361844B2                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2009-11-11 |  |  |

| 申请号            | JP2004220263                                                                                                                                                                                                                                                                                                        | 申请日     | 2004-07-28 |  |  |

| [标]申请(专利权)人(译) | 富士通显示技术股份有限公司<br>友达光电股份有限公司                                                                                                                                                                                                                                                                                         |         |            |  |  |

| 申请(专利权)人(译)    | 富士通显示器科技公司<br>友达光电股▼ふん▲有限公司                                                                                                                                                                                                                                                                                         |         |            |  |  |

| 当前申请(专利权)人(译)  | 富士通株式会社<br>友达光电股▲ふん▼有限公司                                                                                                                                                                                                                                                                                            |         |            |  |  |

| [标]发明人         | 鎌田豪<br>笹林貴<br>上田一也<br>吉田秀史                                                                                                                                                                                                                                                                                          |         |            |  |  |

| 发明人            | 鎌田 豪<br>笹林 貴<br>上田 一也<br>吉田 秀史                                                                                                                                                                                                                                                                                      |         |            |  |  |

| IPC分类号         | G02F1/1368                                                                                                                                                                                                                                                                                                          |         |            |  |  |

| CPC分类号         | G02F1/136213 G02F2001/134354 G02F2001/136218 B01J47/014 C02F1/42 C02F1/48 C02F1/50 C02F1/68 C02F5/08                                                                                                                                                                                                                |         |            |  |  |

| FI分类号          | G02F1/1368                                                                                                                                                                                                                                                                                                          |         |            |  |  |

| F-TERM分类号      | 2H092/GA11 2H092/JA24 2H092/JA41 2H092/JA46 2H092/JB22 2H092/JB31 2H092/JB56 2H092<br>/NA01 2H092/NA25 2H092/PA01 2H092/PA02 2H092/PA08 2H192/AA24 2H192/BC23 2H192/BC31<br>2H192/CB05 2H192/CB71 2H192/CC04 2H192/DA13 2H192/DA15 2H192/DA73 2H192/DA74 2H192<br>/EA43 2H192/GA03 2H192/GD14 2H192/GD61 2H192/JA13 |         |            |  |  |

| 代理人(译)         | 冈本圭造                                                                                                                                                                                                                                                                                                                |         |            |  |  |

| 其他公开文献         | JP2006039290A                                                                                                                                                                                                                                                                                                       |         |            |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                    |         |            |  |  |

# 摘要(译)

要解决的问题:提供一种能够避免在液晶显示装置中产生余辉的液晶显示装置,其中通过使用电容耦合HT(半色调)方法来抑制变色并提供防止持久性的方法。解决方案:直接连接到TFT 116的子像素电极121a和121c设置在与控制电极118和栅极总线112电容耦合的子像素电极(浮置子像素电极)121b之间,以防止从栅极总线112注入电荷。浮动子像素电极121b。在浮置子像素电极121b和数据总线115之间形成电连接到辅助电容总线113的屏蔽图案145.通过屏蔽图案145避免从数据总线115到浮置子像素电极121b的电荷注入。.Ž