(19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-180828 (P2008-180828A)

(43) 公開日 平成20年8月7日(2008.8.7)

(51) Int.Cl. GO2F 1/1368 (2006.01) FI

GO2F 1/1368

テーマコード (参考)

2HO92

審査請求 未請求 請求項の数 5 OL (全 13 頁)

(21) 出願番号 (22) 出願日

特願2007-13266 (P2007-13266) 平成19年1月24日 (2007.1.24)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74)代理人 100086298

弁理士 船橋 國則

(72) 発明者 榊原 功士

東京都品川区北品川6丁目7番35号 ソ

二一株式会社内

Fターム(参考) 2H092 GA29 HA04 JA24 JA46 JB56

JB67 JB68 JB69 KA04 KA18 KA22 KB04 KB13 MA12 MA17

NA21 NA25 NA29 PA02

### (54) 【発明の名称】液晶表示装置

### (57)【要約】

【課題】液晶表示装置の画素を駆動する際の保持容量を 大きくして、保持能力を向上させること。

【解決手段】本発明は、液晶を挟んで形成された一対の 基板のうち、一方の基板上に、第1の方向に沿って形成 される走査線1-3と、第1の方向に交差する第2の方 向に沿って形成される信号線8-1と、走査線1-3お よび信号線8-1の交差部に対応して設けられる画素電 極と、画素電極をスイッチング制御するトランジスタと 、画素電極に電気的に接続されるキャパシタ4-1、4 - 2とを備える液晶表示装置であり、キャパシタ4 - 1 、4-2の画素電位を有する画素電極と対向する電極が 、画素電位に対して高電位を有する第1の電極8-2と 、画素電位に対して低電位を有する第2の電極8-4と を備えているものである。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

液晶を挟んで形成された一対の基板のうち、一方の基板上に、第1の方向に沿って形成される走査線と、

前記第1の方向に交差する第2の方向に沿って形成されるデータ線と、

前記走査線および前記データ線の交差部に対応して設けられる画素電極と、

前記画素電極に印加する画素電位をスイッチング制御するトランジスタと、

前記画素電極に電気的に接続される蓄積容量とを備える液晶表示装置において、

前記蓄積容量の前記画素電極と対向する電極が、前記画素電位に対して高電位を有する 第1の電極と、前記画素電位に対して低電位を有する第2の電極とを備えている ことを特徴とする液晶表示装置。

【請求項2】

前記第1の電極と前記第2の電極とが前記基板上の同一の層に形成され、かつ前記画素電極と対応する表示領域において隣接する表示領域間で前記第1の電極同士もしくは前記第2の電極同士が隣接して設けられている

ことを特徴とする請求項1記載の液晶表示装置。

#### 【請求項3】

前記第1の電極と前記第2の電極とが前記基板上の異なる層に形成され、前記第1の電極と前記第2の電極との間に前記蓄積容量の画素電位側の電極が配置されていることを特徴とする請求項1記載の液晶表示装置。

【請求項4】

前記画素電極と対応する表示領域の外部から前記第1の電極および前記第2の電極へ電位を供給するための配線が前記基板上の異なる層に形成されている

ことを特徴とする請求項3記載の液晶表示装置。

#### 【請求項5】

前記第1の電極と前記第2の電極とが前記基板上の同一の層に形成され、かつ前記画素電極と対応する表示領域の中において前記第1の電極と前記第2の電極とが隣接して設けられている

ことを特徴とする請求項1記載の液晶表示装置。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、液晶に電圧を印加して表示を行う液晶表示装置に関する。

#### 【背景技術】

[0002]

一般的に、一対の基板に挟んだ液晶に電圧を印加して表示を行う表示装置では、一方に基準となる一定電圧を印加した対向電極を有し、他方の基板上に交流電位を印加される画素電極と信号線、半導体層、走査線(ゲート)、蓄積容量(CS)、及びこれらの素子や配線を電気的に分離するための層間絶縁膜と各素子および配線を電気的に接続するためのコンタクトホールを有している。

[ 0 0 0 3 ]

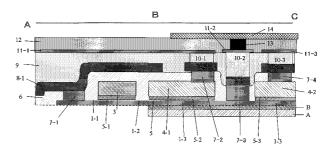

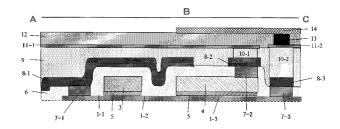

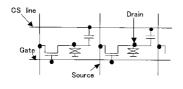

図11、図12、は、従来の液晶表示装置の画素領域の一部分を示す模式図で、(a)は平面図、(b)は回路図である。また、図12は、配線レイアウトを説明する模式平面図である。なお、図11では、図12のキャパシタライン11 1と画素台座11 2と画素電極14を削除した状態を表記したものである。また、図13は、図11、図12におけるABC間の断面図である。

#### [0004]

すなわち、図11に示すように、信号線8-1に直行するように走査線(ゲート)3を設けてあり、信号線8-1と走査線(ゲート)3との直行点にスイッチング素子として半導体層(ソース)1-1と半導体層(ドレイン)1-2と走査線(ゲート)3にて形成さ

10

20

30

40

れる画素トランジスタを設けてある。

[00005]

図 1 3 に示すように、前記トランジスタの半導体層(ソース) 1 - 1 と信号線 8 - 1 とは絶縁膜 6 中の第一コンタクト 7 - 1 を介して接続されている。また、半導体層(ドレイン) 1 - 2 は第一コンタクト 7 - 3、ドレインと画素を繋ぐ電極 8 - 3、画素台座 1 1 - 2、第三コンタクト 1 3 を介して画素電極 1 4 に接続されている。

[0006]

図 1 1 に示すように、キャパシタ 4 は各画素に設けられており、図 1 3 に示すように、キャパシタ 4 は画素側キャパシタ電極 1 - 3 に絶縁膜 5 を挟んで対向するように設けられている。前記キャパシタ 4 は、第一コンタクト 7 - 2 、キャパシタ 4 と画素を繋ぐ電極 8 - 2 、第二コンタクト 1 0 - 1 を介してキャパシタライン 1 1 - 1 に接続されている。

[0007]

ここで、前記画素電極の駆動時の電圧は、画素電極を有する基板と液晶とを介して、対向する基板に形成された電極の電位を基準とした交流駆動で対向電極電位±数 V (例えば7±5 V)となっている(図11(b)参照)。そして前記画素電位を保持するための蓄積容量(CS)に印加する電圧は固定電位と同電位(例えば7V)になっている。

[0008]

したがって、画素電位を保持するための蓄積容量を増加させるためには、蓄積容量に蓄えられる電荷(Q=CV)を増やす必要があり、容量Cを増やすか電圧Vを増やすことにより実現できる(例えば、特許文献 1 参照。)。

[0009]

【特許文献1】特開2002-98997号公報

【発明の開示】

【発明が解決しようとする課題】

[0010]

しかしながら、従来の方法によると蓄積容量の固定電極側の電位は対向基板側の電極電位と同電位としているため、±数 V (例えば 5 V)以上の電圧をかけることはできず、印加電圧の増加による保持能力向上は望めない。また、画素電位によって保持容量が変動するため、画素に蓄えられた電荷のリークによる保持特性の変動が問題となる。

【課題を解決するための手段】

[0011]

本発明は、このような課題を解決するために成されたものである。すなわち、本発明は、液晶を挟んで形成された一対の基板のうち、一方の基板上に、第1の方向に沿って形成される走査線と、第1の方向に交差する第2の方向に沿って形成されるデータ線と、走査線およびデータ線の交差部に対応して設けられる画素電極と、画素電極に印加する画素電位をスイッチング制御するトランジスタと、画素電極に電気的に接続される蓄積容量とを備える液晶表示装置であり、蓄積容量の画素電極と対向する電極が、画素電位に対して高電位を有する第1の電極と、画素電位に対して低電位を有する第2の電極とを備えているものである。

[0012]

このような本発明では、画素電極に電圧を交流で印加して表示する液晶表示装置において、蓄積容量に、画素電位に対して正負の異なる2種の固定電位を第1の電極および第2の電極から印加することで、固定電位と画素電位との差を一定にし、かつ、電位差を大きくできるため、同一面積でもより大きな保持容量を確保できるようになる。

【発明の効果】

[0013]

したがって、本発明によれば次のような効果がある。すなわち、液晶表示装置の画素を 駆動する際の保持容量を大きくすることができ、保持能力を向上させることが可能となる

【発明を実施するための最良の形態】

10

20

30

40

20

30

40

50

#### [0014]

以下、本発明の実施の形態を図に基づき説明する。

#### [0015]

< 概要 >

本発明の液晶表示装置に係る第1の実施形態としては、液晶層を介して対向する一対の基板の一方の基板上に形成された画素に、一方の基板側の電極の電位に対して正負電位を交互に印加して表示を行う液晶表示装置において、画素電極に対し、画素電位を保持するための蓄積容量を形成するために、誘電体層を介して、2つの固定電極を形成し、これらの2つの固定電極には、それぞれ画素電位のとりうる範囲の電位よりも、高電位の電位と、低電位の電位の2種の電位を印加することを特徴としている。

[0016]

このような形態によると、蓄積容量による保持電位を常に一定とすることができ、かつ 蓄積容量を形成するための誘電体層を介して対向する電極面積を増やすことなく、保持容 量を増加させることができる。

[0017]

また、本発明の第2の実施形態としては、前記液晶表示装置において、異なる電位を有する2つの固定電極が画素電極を挟んで作成しX、Y方向共に1画素おきに配置されていることを特徴としている。

[0018]

また、本発明の第3の実施形態としては、前記異なる電位を有する2つの固定電極が、 蓄積容量の画素電位を有する電極を介して、対向するように配置されていることを特徴と している。

[0019]

このような形態によれば、蓄積容量の一方の電極である画素電位側の電極の基板表面側と基板裏面側の両方の面を蓄積容量を形成するための電極として利用できるため、同一層で形成した場合よりも、蓄積容量の面積を容易に増やすことができ、保持するための容量を増加させることができるため、良好な表示ができる液晶表示装置を提供できる。

[0020]

また、本発明の第4の実施形態としては、第3の形態における蓄積容量の異なる電位を有する固定電位側の電極に表示領域外部から電位を供給するための配線が、異なる層で形成されていることを特徴としている。

[0021]

<具体的な実施形態>

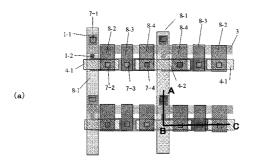

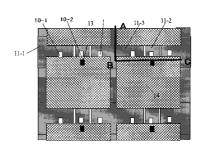

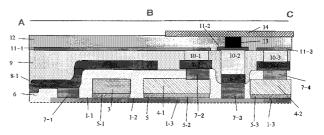

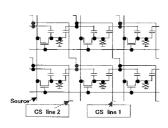

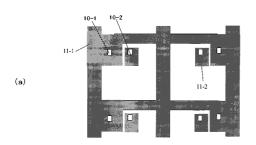

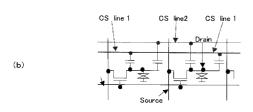

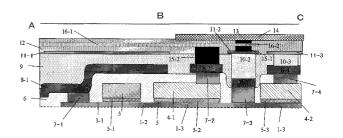

図1は、第1の実施形態に係る液晶表示装置を説明する模式図で、(a)は画素部分の模式平面図、(b)は回路図である。また、図2は、画素部分の配線レイアウトを説明する模式平面図、図3は、図2に示すA-B-C間の模式断面図である。

[0022]

すなわち、この液晶表示装置は、液晶を挟んで形成された一対の基板のうち、一方の基板(駆動側基板)上に、第1の方向に沿って形成される走査線(ゲート)3と、第1の方向に交差する第2の方向に沿って形成される信号線8-1と、走査線(ゲート)3および信号線8-1の交差部に対応して設けられる画素電極14と、画素電極14をスイッチング制御するため、半導体層(ソース)1-1と半導体層(ドレイン)1-2と走査線(ゲート)3にて形成される画素トランジスタと、画素電極14および画像側キャパシタ電極1・3に電気的に接続されるキャパシタ4-1、4-2とを備えている。

[0023]

また、キャパシタ4 - 1、4 - 2の画素電位を有する画素側キャパシタ電極1 - 3と対向する電極が、画素電位に対して高電位を有する第1の電極8 - 2と、画素電位に対して低電位を有する第2の電極8 - 4との2つから構成される。

[0024]

図3に示すように、前記トランジスタの半導体層(ソース)1-1と信号線8-1とは

20

30

40

50

絶縁膜 6 中の第一コンタクト7-1を介して接続されている。また、半導体層(ドレイン)1-2は第一コンタクト7-3、ドレインと画素を繋ぐ電極8-3、画素台座11-2、第三コンタクト13を介して画素電極14に接続されている。

[0025]

キャパシタ4 - 1、4 - 2 は各画素に設けられており、図3に示すように、キャパシタ4 - 1 は画素側キャパシタ電極1 - 3 に絶縁膜5 - 2 を挟んで対向するよう設けられ、キャパシタ4 - 2 は画素側キャパシタ電極1 - 3 に絶縁膜5 - 3 を挟んで対向するように設けられている。

[0026]

キャパシタ4 - 1 は、第一コンタクト7 - 2、キャパシタ4 - 1 と画素を繋ぐ第1の電極8 - 2、第二コンタクト10 - 1を介してキャパシタライン11 - 1 に接続されている

[0027]

また、キャパシタ4 - 2 は、第一コンタクト7 - 4、キャパシタ4 - 2 と画素を繋ぐ第2の電極8 - 4、第二コンタクト10 - 3を介してキャパシタライン11 - 3 に接続されている。

[0028]

このような本実施形態の液晶表示装置の駆動時における印加電圧としては、例えば、図 1 (b)に示す回路図にて、前記信号線印加電圧  $7\pm5$  V でキャパシタ4 - 1、4 - 2に印加する電圧を 7 V とした場合、キャパシタ4 - 1、4 - 2に印加する 2 種の電圧は、例えば第 1 の電極 8 - 2につながる 2 C S 1 ine 1 (キャパシタライン 1 1 - 1)が 1 4 V 以上、第 2 の電極 8 - 4につながる 2 C S 1 ine 2 (キャパシタライン 1 1 - 3)が 0 V 以下とする。つまり、第 1 の電極 8 - 2には、高い側の画素電位(7 + 5 = 1 2 V)より高い電圧を印加し、第 2 の電極 8 - 4には、低い側の画素電位(7 - 5 = 2 V)より低い電圧を印加する。

[0029]

図 1 における 2 つのキャパシタ 4 - 1、 4 - 2 の面積は従来のキャパシタを 2 分割したものであるとしたとき、保持容量の能力は Q = C V より従来では 2 ( C ) × 5 ( V ) = 1 0 ( Q ) に対し、本実施形態では 1 × ( 1 2 + 2 ) = 1 4 となり保持能力の向上を図ることができる。

[0030]

図 1、図 2、図 3 にて第 1 実施形態に係る液晶表示装置の製造プロセスを説明する。先ず、例えば石英基板に半導体層(ソース) 1 1 と半導体層(ドレイン) 1 - 2 を含む電極として減圧 C V D 等でポリシリコン層を 1 0 0 n m 成膜した後、パターニング後、エッチングを行い電極の形成を行う。

[0031]

次に、前記ポリシリコン膜を例えば約1000 の温度にて熱酸化することにより30nm程度の較的薄い膜厚のシリコンの熱酸化膜を形成する。

[0032]

前記シリコンの熱酸化膜はゲート膜 5 - 1 とキャパシタ(CS)膜用絶縁膜 5 - 2 、 5 - 3 として使用する。

[0033]

次に、例えばゲート電極(走査線)として減圧 C V D にてポリシリコン層を 4 0 0 n m 成膜し、パターニングした後、エッチングを行うことにより走査線(ゲート) 3 を形成する。

[0034]

本実施形態では、走査線(ゲート)3と同時にキャパシタ4・1、4・2の作成も行っているが走査線(ゲート)3とキャパシタの材質、膜厚、作成工程は別でももちろん良い。前記キャパシタ4・1、4・2は前記半導体層(ドレイン)1 2に書き込まれた電位を保持する目的をもつ。

20

30

40

50

#### [0035]

次に、トランジスタの半導体領域形成のためNチャネルトランジスタであればパターニング後、例えばV族元素P、As等をドーズする。なお、Pチャネルトランジスタ使用時はB、BF₂等をドーズする。

### [0036]

次に、例えば常圧または低圧 C V D により走査線(ゲート) 3 、キャパシタ 4 - 1 、 4 - 2 を包むように酸化シリコン膜等からなる絶縁膜 6 を 1 1 0 0 n m 成膜する。

#### [0037]

次に、前記半導体層(ソース) 1 1 と信号線 8 1 を繋ぐため絶縁膜 6 中に第一コンタクトホール 7 1 を形成する。前記第一コンタクトホール 7 1 形成と同時にキャパシタ4-1、4-2 部とドレイン部の引き出しのための絶縁膜 6 中に第一コンタクトホール 7 2、7 3、7-4 も形成する。

#### [0038]

次に、例えばアルミニウム(Al)等の低抵抗金属を成膜し、パターニングした後、エッチングにより信号線8 1を形成する。なお、配線材料はアルミニウム(Al)以外に銅(Cu)、チタン(Ti)、窒化チタン(TiN)、タンタル(Ta)等の使用も可能である。

### [0039]

そして、前記信号線 8 1 形成時にキャパシタ部とドレイン部引き出し用電極 8 - 3、第 1 の電極 8 - 2、第 2 の電極の形成も行う。

#### [0040]

次に、例えば絶縁膜として酸化シリコン等からなる絶縁膜9を700nm成膜する。次いで、前記キャパシタ部と各電極8 2、8 3、8-4への接続を目的とし、絶縁膜9中に第二コンタクトホール10 1、10 2、10-3を形成する。

### [ 0 0 4 1 ]

次に、例えば前記信号線 8 - 1 と同様に、低抵抗金属の成膜を行った後、パターニング後、エッチングを行い、前記第ニコンタクトホール 1 0 1、10 2、10 3 に対しキャパシタライン 1 1 1、11 - 3、画素台座 1 1 2 を形成する。

#### [0042]

次に、絶縁膜として全面に例えばシリコン酸化膜等からなる絶縁膜12を500nm成膜する。

### [0043]

次いで、画素台座11 2への接続のため絶縁膜12中に第三コンタクトホール13を 形成する。

## [ 0 0 4 4 ]

次に、 画素電極 1 4 として例えば I T O (Indium Tin Oxide) 等の透明電極を 1 0 0 n m 程度成膜し、パターニングとエッチングを行い、 画素電極 1 4 を形成する。

#### [0045]

最後に、画素電極14の上に配向膜として例えばポリイミド系の配向膜を塗布し、配向 方向を揃えるためラビングを行う。

### [0046]

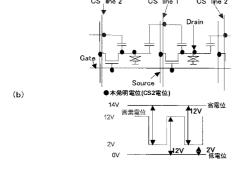

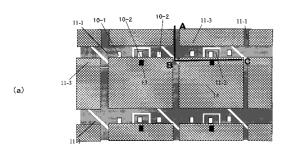

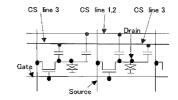

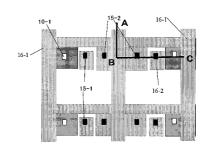

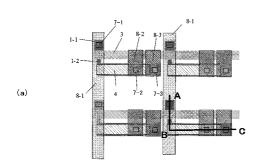

次に、第2の実施形態を説明する。図4は、第2の実施形態を説明する模式図であり、(a)は画素部分の配線レイアウトの模式平面図、(b)は回路図である。第2の実施形態では、先に説明した第1の実施形態におけるCS lineの引き回し形状を変更したものである。

### [0047]

すなわち、図3に示すキャパシタライン11-1、11-3と信号線8-1間でカップリングが発生する場合、信号線に印加された電圧7±5 Vがキャパシタライン11-1、11-3の電圧に引っ張られ、キャパシタライン11-1(14 V印加)に近い信号線は高電圧側、キャパシタライン11-3(0 V印加)に近い信号線は低電圧側に引っ張られ

る可能性がある。

#### [0048]

この回避案として図4(a)の配線レイアウトおよび図4(b)に示す回路図のように、キャパシタライン11-1、11-3を信号線に対して斜めに走らせることにより1画素おきに信号線上のキャパシタライン11-1、11-3に印加されている電圧がHigh、Lowと入れ替わることによって、一定方向に電位がシフトすることを防ぐことができる。

#### [0049]

次に、第3の実施形態を説明する。図5は、第3の実施形態を説明する模式図で、(a)は画素部分の模式平面図、(b)は回路図である。本実施形態は、第1の実施形態のパターン形状に対し、画素側キャパシタ電極1-3の下層に第3キャパシタ配線(A)と第3キャパシタ絶縁膜(B)とを追加して第3キャパシタを構成することにより電位保持能力を向上させたものである。

### [0050]

本実施形態の構造を形成するには、駆動側基板である例えば石英基板に第 1 の実施形態で説明した各層を形成するに先立ち、駆動側基板上に先ず、例えば高温( 1 0 0 0 度)に耐え得る配線としてたとえばW S i 等を基板(駆動側基板)上に成膜し、パターニングした後、エッチングによりにより第 3 キャパシタ配線( A ) を形成する。

### [0051]

次に、形成した第3キャパシタ配線(A)上に、例えばSiO2等の絶縁膜を成膜することによって第3キャパシタ絶縁膜(B)を形成する。そして、以降のプロセスは第1の実施形態における半導体層(ソース)1 1と半導体層(ドレイン)1-2を含む電極形成等の製造プロセスと同じとなる。

#### [0052]

すなわち、先に形成した第3キャパシタの上に、半導体層(ソース)1 1 と半導体層 (ドレイン)1-2を含む電極として減圧CVD等でポリシリコン層を100nm成膜後 パターニング後エッチング行い電極を形成する。

#### [ 0 0 5 3 ]

次に、前記ポリシリコン膜を例えば約1000 の温度にて熱酸化することにより30 nm程度の較的薄い膜厚のシリコンの熱酸化膜を形成する。

#### [0054]

前記シリコンの熱酸化膜はゲート膜 5 - 1 とキャパシタ( C S )膜用絶縁膜 5 - 2 、 5 - 3 として使用する。

#### [0055]

次に、例えばゲート電極(走査線)として減圧 C V D にてポリシリコン層を 4 0 0 n m 成膜し、パターニングした後、エッチングを行うことにより走査線(ゲート) 3 を形成する。

#### [0056]

次に、トランジスタの半導体領域形勢のため N チャネルトランジスタであればパターニング後、例えば V 族元素 P 、 A s 等をドーズする。なお、 P チャネルトランジスタ使用時は B 、 B F  $_2$ 等をドーズする。

#### [0057]

次に、例えば常圧または低圧 C V D により走査線(ゲート) 3 、 キャパシタ 4 - 1 、 4 - 2 を包むように酸化シリコン膜等からなる絶縁膜 6 を 1 1 0 0 n m 成膜する。

#### [0058]

次に、前記半導体層(ソース) 1 1 と信号線 8 1 を繋ぐため絶縁膜 6 中に第一コンタクトホール 7 1 を形成する。前記第一コンタクトホール 7 1 形成と同時にキャパシタ4-1、4-2 部とドレイン部の引き出しのための絶縁膜 6 中に第一コンタクトホール 7 2、7 3、7-4 も形成する。

### [0059]

50

10

20

30

20

30

40

50

次に、例えばアルミニウム(Al)等の低抵抗金属を成膜し、パターニングした後、エッチングにより信号線 8 1を形成する。なお、配線材料はアルミニウム(Al)以外に銅(Cu)、チタン(Ti)、窒化チタン(TiN)、タンタル(Ta)等の使用も可能である。

[0060]

そして、前記信号線 8 1 形成時にキャパシタ部とドレイン部引き出し用電極 8 - 3、第 1 の電極 8 - 2、第 2 の電極の形成も行う。

[0061]

次に、例えば絶縁膜として酸化シリコン等からなる絶縁膜9を700nm成膜する。次いで、前記キャパシタ部と各電極8 2、8 3、8-4への接続を目的とし、絶縁膜9中に第二コンタクトホール10 1、10 2、10-3を形成する。

[0062]

次に、例えば前記信号線 8 - 1 と同様に、低抵抗金属の成膜を行った後、パターニング後、エッチングを行い、前記第ニコンタクトホール 1 0 1、10 2、10 - 3 に対しキャパシタライン 1 1 1、11 - 3、画素台座 1 1 2 を形成する。

[0063]

次に、絶縁膜として全面に例えばシリコン酸化膜等からなる絶縁膜12を500nm成膜する。

[0064]

次いで、画素台座11 2への接続のため絶縁膜12中に第三コンタクトホール13を 形成する。

[0065]

次に、 画素電極 1 4 として例えば I T O (Indium Tin Oxide) 等の透明電極を 1 0 0 n m 程度成膜し、パターニングとエッチングを行い、 画素電極を形成する。

[0066]

最後に、画素電極14の上に配向膜として例えばポリイミド系の配向膜を塗布し、配向 方向を揃えるためラビングを行う。

[0067]

第3の実施形態に係る構造をとることにより、第1の実施形態と同様に2つのキャパシタそれぞれ印加できる電圧が自由になり、さらに面積増加の効果が得られるために更なる保持能力性能の向上を図ることが可能となる。

[0068]

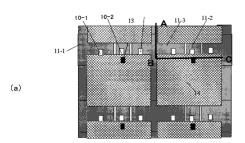

図 6 は、画素部分の配線レイアウトを説明する模式平面図で、( a )は画素部全体のレイアウト、( b )は上層に形成したキャパシタラインを同電位にする場合のレイアウトである。また、図 7 は、図 5 、図 6 に示す A - B - C 間の模式断面図である。

[0069]

上層のキャパシタ4 - 1、4 - 2 は各画素に設けられており、図 6 に示すように、キャパシタ4 - 1 は画素側キャパシタ電極 1 - 3 に絶縁膜 5 - 2 を挟んで対向するよう設けられ、キャパシタ4 - 2 は画素側キャパシタ電極 1 - 3 に絶縁膜 5 - 3 を挟んで対向するように設けられている。

[0070]

キャパシタ4 - 1 は、第一コンタクト 7 - 2、キャパシタ4 - 1 と画素を繋ぐ第 1 の電極 8 - 2、第二コンタクト 1 0 - 1 を介してキャパシタライン 1 1 - 1 に接続されている。また、キャパシタ4 - 2 は、第一コンタクト 7 - 4、キャパシタ 4 - 2 と画素を繋ぐ第 2 の電極 8 - 4、第二コンタクト 1 0 - 3 を介してキャパシタライン 1 1 - 3 に接続されている。

[0071]

また、画素側キャパシタ電極1・3の下層には、第3キャパシタ絶縁膜(B)を介して第3キャパシタ電極(A)が設けられ、第3のキャパシタを構成している。これら3つのキャパシタによって電位保持能力の向上を図る。

20

30

40

50

#### [0072]

また、第1の実施形態および第2の実施形態と同様、第1のキャパシタ4-1につながる第1の電極8-2と、第2のキャパシタ4-2につながる第2の電極8-4とに別電位を与える場合には、図6(a)に示すような配線レイアウトとなる。

### [0073]

一方、 2 つのキャパシタに対する別電位印加の考え方を、第 1 のキャパシタ4 - 1 および第 2 のキャパシタ4 - 2 の組みと、第 3 のキャパシタとの 2 つで行う場合には、図 6 ( b ) に示すように、第 1 の電極 8 - 1 につながる第 1 のキャパシタライン 1 1 - 1 と第 2 の電極 8 - 2 につながる第 2 のキャパシタライン 1 1 - 3 とを統一する構成にすればよい。これにより、第 1 のキャパシタ 4 - 1 と第 2 のキャパシタ 4 - 2 とを 1 組として例えば高い側の画素電位(7 + 5 = 1 2 V )より高い電圧を印加し、第 3 のキャパシタに例えば低い側の画素電位(7 - 5 = 2 V )より低い電圧を印加する。なお、電圧の印加は上記と反対であってもよい。

[ 0 0 7 4 ]

[0075]

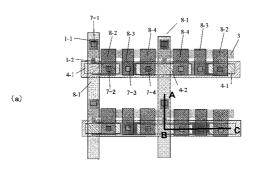

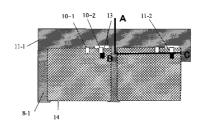

次に、第4の実施形態を説明する。図8は、第4の実施形態を説明する模式図であり、(a)は画素部分の配線レイアウト(主として第1のキャパシタライン)の模式平面図、(b)は回路図である。また、図9は、画素部分の配線レイアウト(主として第2のキャパシタライン)の模式平面図、図10は、図9に示すA-B-C間の模式断面図である。

本実施形態のパターン形状は、第1の実施形態で同層であったCS line1(キャパシタライン11-1)とCS line2(キャパシタライン16-1)とをそれぞれ基板上において異なる層の配線として別途形成したものとなっている。第4実施形態のパターン形状を構成するには、第1の実施形態におけるプロセスの信号線形成後より別となる。

[0076]

すなわち、先ず、第1実施形態と同様に、例えば石英基板に半導体層(ソース)1 1 と半導体層(ドレイン)1 - 2 を含む電極として減圧 C V D 等でポリシリコン層を100 n m 成 膜 した後、パターニング後、エッチングを行い電極の形成を行う。

[0077]

次に、前記ポリシリコン膜を例えば約1000 の温度にて熱酸化することにより30 nm程度の較的薄い膜厚のシリコンの熱酸化膜を形成する。

[0078]

前記シリコンの熱酸化膜はゲート膜 5 - 1 とキャパシタ( C S )膜用絶縁膜 5 - 2 、 5 - 3 として使用する。

[0079]

次に、例えばゲート電極(走査線)として減圧 C V D にてポリシリコン層を 4 0 0 n m 成膜し、パターニングした後、エッチングを行うことにより走査線(ゲート) 3 を形成する。

[0080]

次に、トランジスタの半導体領域形勢のためNチャネルトランジスタであればパターニング後、例えばV族元素P、As等をドーズする。なお、Pチャネルトランジスタ使用時はB、BF₂等をドーズする。

[0081]

次に、例えば常圧または低圧 C V D により走査線(ゲート) 3 、キャパシタ4 - 1 、 4 - 2 を包むように酸化シリコン膜等からなる絶縁膜 6 を 1 1 0 0 n m 成膜する。

[0082]

次に、前記半導体層(ソース) 1 1 と信号線 8 1 を繋ぐため絶縁膜 6 中に第一コンタクトホール 7 1 を形成する。前記第一コンタクトホール 7 1 形成と同時にキャパシタ4-1、4-2 部とドレイン部の引き出しのための絶縁膜 6 中に第一コンタクトホール 7 2、7 3、7-4 も形成する。

20

30

40

50

[0083]

次に、例えばアルミニウム(Al)等の低抵抗金属を成膜し、パターニングした後、エッチングにより信号線 8 1を形成する。なお、配線材料はアルミニウム(Al)以外に銅(Cu)、チタン(Ti)、窒化チタン(TiN)、タンタル(Ta)等の使用も可能である。

[0084]

そして、前記信号線 8 1 形成時にキャパシタ部とドレイン部引き出し用電極 8 - 3 、第 1 の電極 8 2 、第 2 の電極の形成も行う。ここまでは、第 1 の実施形態と同じプロセスである。

[0085]

次に、第4の実施形態では、第1のキャパシタ4 - 1と第1のキャパシタライン11 - 1とを繋ぐ第1の電極8 - 2へのコンタクトとして、コンタクト10 - 1を形成する。次に、このコンタクト10 - 1上へ第1のキャパシタライン11 - 1を形成する。

[0086]

また、第2のキャパシタ4 - 2と導通する第2の電極8 - 4上にコンタクト10 - 3を 形成し、このコンタクト10 - 3上へ第2のキャパシタライン11 - 3を形成する。

[0087]

さらに、ドレインと画素電極とを繋ぐ電極8-3上にコンタクト10-2を形成し、その上に画素台座11-2を形成し、その上にコンタクト10-2を形成し、別層の画素台座16-2を形成する。

[0088]

また、画素台座 1 6 - 2 を形成するのと同じ工程で、第 1 のキャパシタ4 - 2 と第 1 のキャパシタライン 1 1 - 1 とを繋ぐ第 1 の電極 8 - 2 へのコンタクトとして、コンタクト 1 5 - 2 を形成する。そして、このコンタクト 1 5 - 2 上へ第 1 のキャパシタライン 1 6 - 1 を形成する。

[0089]

第1のキャパシタライン16-1は画素台座16-2と同じ層、第2のキャパシタライン11-3とは別の層となる。この第1のキャパシタライン16-1の配線材料は、第1のキャパシタライン11-1と同種のアルミニウム(Al)以外に、銅(Cu)、チタン(Ti)、窒化チタン(TiN)、タンタル(Ta)等の使用も可能である。

[0090]

第 1 のキャパシタライン 1 6 - 1 と第 2 のキャパシタライン 1 1 - 3 とを別層で形成することにより配線幅の増加による配線抵抗の低下と遮光性能の向上とが得られる。

【図面の簡単な説明】

[0091]

【図1】第1の実施形態に係る液晶表示装置を説明する模式図で、(a)は画素部分の模式平面図、(b)は回路図である。

- 【図2】画素部分の配線レイアウトを説明する模式平面図である。

- 【図3】図2に示すA-B-C間の模式断面図である。

【図4】第2の実施形態を説明する模式図であり、(a)は画素部分の配線レイアウトの模式平面図、(b)は回路図である。

【図5】第3の実施形態を説明する模式図で、(a)は画素部分の模式平面図、(b)は回路図である。

【図 6 】画素部分の配線レイアウトを説明する模式平面図で、( a )は画素部全体のレイアウト、( b )は上層に形成したキャパシタラインを同電位にする場合のレイアウトである。

- 【図7】図7は、図5、図6に示すA-B-C間の模式断面図である。

- 【図8】第4の実施形態を説明する模式図であり、(a)は画素部分の配線レイアウト( 主として第1のキャパシタライン)の模式平面図、(b)は回路図である。

- 【図9】、画素部分の配線レイアウト(主として第2のキャパシタライン)の模式平面図

である。

- 【図10】図9に示すA-B-C間の模式断面図である。

- 【図11】従来の液晶表示装置の画素領域の一部分を示した平面図である。

- 【図12】配線レイアウトを説明する模式平面図である。

- 【図13】図11、図12におけるA B C間の断面図である。

#### 【符号の説明】

#### [0092]

1 - 1 ... 半導体層(ソース)、1 - 2 ... 半導体層(ドレイン)、1 - 3 ... 走査線(ゲート)、4 - 1 ... 第 1 のキャパシタ、4 - 2 ... 第 2 のキャパシタ、5 - 1 ... ゲート絶縁膜、5 - 2 ... 第 1 キャパシタ絶縁膜、5 - 2 ... 第 2 キャパシタ絶縁膜、6 ... 絶縁膜、7 - 1 ... 第一コンタクト、8 - 1 ... 信号線、8 - 2 ... 第 1 の電極、8 - 3 ... ドレインと画素とを繋ぐ電極、8 - 4 ... 第 2 の電極、9 ... 絶縁膜、1 0 - 1 ... 第二コンタクト、1 1 - 1 ... 第 1 のキャパシタライン、1 1 - 2 ... 画素台座、1 1 - 3 ... 第 2 のキャパシタライン、1 3 ... 第三コンタクト、1 4 ... 画素電極

### 【図1】

### 【図2】

【図3】

# 【図4】

# 【図5】

(b)

(h)

# 【図6】

# 【図7】

(b)

# 【図8】

# 【図9】

【図10】

# 【図11】

# 【図12】

【図13】

(b)

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | JP2008180828A                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2008-08-07 |

| 申请号            | JP2007013266                                                                                                                                                                                                                                                                                                                     | 申请日     | 2007-01-24 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 榊原功士                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 榊原 功士                                                                                                                                                                                                                                                                                                                            |         |            |

| IPC分类号         | G02F1/1368                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G02F1/1368                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA29 2H092/HA04 2H092/JA24 2H092/JA46 2H092/JB56 2H092/JB67 2H092/JB68 2H092 /JB69 2H092/KA04 2H092/KA18 2H092/KA22 2H092/KB04 2H092/KB13 2H092/MA12 2H092/MA17 2H092/NA21 2H092/NA25 2H092/NA29 2H092/PA02 2H192/AA24 2H192/BC31 2H192/CB02 2H192 /CC05 2H192/DA13 2H192/DA15 2H192/DA52 2H192/DA65 2H192/EA04 2H192/GD61 |         |            |

| 代理人(译)         | 船桥 国则                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                        |         |            |

|                |                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

要解决的问题:通过在驱动液晶显示装置的像素时增加保持容量来增加保持容量。解决方案:本发明涉及一种液晶显示装置,包括在一个基板上夹着液晶的一对基板,沿第一方向形成的扫描线1-3,对应于扫描线1-3与信号线8-1的交叉点设置的像素电极,用于控制像素电极的切换的晶体管,电容器4-1和4-2电连接到像素电极。与具有电容器4-1和4-2的像素电位的像素电极相对的电极是像素电位相对于像素电位具有高电位的第一电极8-2和相对于像素电位具有低电位的第二电极8-4。点域1