## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

テーマコード (参考)

特開2006-189896 (P2006-189896A)

(43) 公開日 平成18年7月20日(2006.7.20)

(51) Int. C1. F 1

**GO2F** 1/1368 (2006.01) GO2F 1/1368 2HO92 **HO1L** 29/786 (2006.01) HO1L 29/78 612Z 5F11O

HO1L 21/336 (2006,01)

審査請求 有 請求項の数 2 OL (全 13 頁)

(21) 出願番号 特願2006-64659 (P2006-64659) (22) 出願日 平成18年3月9日 (2006.3.9)

(62) 分割の表示 特願2001-387961 (P2001-387961)

の分割

原出願日 平成13年12月20日(2001.12.20)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74)代理人 110000338

特許業務法人原謙三国際特許事務所

(72) 発明者 藤川 徹也

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 土井 誠児

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

Fターム(参考) 2H092 HA04 JA24 JB64 JB68 KA04

KA05 KA18 KA22 KB04 KB13 MA05 MA17 MA30 NA07 NA16

NA29

最終頁に続く

(54) 【発明の名称】薄膜トラジスタ基板および液晶表示装置

## (57)【要約】

【課題】 有効画素領域を広く確保すると共に、補助蓄 積容量の電極間の短絡を防止することのできる薄膜トラ ンジスタ基板及び液晶表示装置を提供する。

【解決手段】 薄膜トランジスタ基板は、導電材料層のゲート電極2 t とキャパシタ下部電極2 c を覆って、基板上に形成された第1絶縁層3 t、3 c と、第1絶縁層3を介して、上方に形成された高抵抗率半導体のチャネル層11t、11c、13t、13cと、チャネル層上に形成された1対のソース/ドレイン電極4tと、キャパシタ上部電極下部層上に形成されたキャパシタ上部電極上部層4cと、これらを覆って,第1絶縁層上に形成された第2絶縁層14と、第2絶縁層を貫通し、ソース電極を露出する第1接続孔8tとキャパシタ上部電極上部層の接続領域を露出する第2接続孔8cと、その上に形成された画素電極5とを有する。

【選択図】 図2

### 【特許請求の範囲】

## 【請求項1】

絶縁性表面を有する基板と、

前記基板上に形成され、同一の導電材料層からなるゲート電極およびキャパシタ下部電極と、

第 1 絶縁層を介して、前記ゲート電極を跨いで形成され、前記ゲート電極上方の表面に 凹部を有する高抵抗率半導体のチャネル層と、

前記第1絶縁層を介して、前記キャパシタ下部電極上方に、前記チャネル層と同一材料層で形成され、表面に凹部は有さない高抵抗率半導体のキャパシタ上部電極下部層と、

前記チャネル層の凹部両側領域上に形成された低抵抗率の1対のソース/ドレイン電極と、

前記キャパシタ上部電極下部層上に,前記ソース/ドレイン電極と同一材料層で形成されたキャパシタ上部電極上部層と、

前記ソース/ドレイン電極,前記キャパシタ上部電極上部層を覆って,前記第1絶縁層上に形成された第2絶縁層を貫通し、前記1対のソース/ドレイン電極の一方を露出する第1接続孔、および、前記キャパシタ上部電極上部層の接続領域を露出する第2接続孔と

前記第2絶縁層上に形成され,前記第1接続孔および第2接続孔で、前記一方のソース/ドレイン電極および前記キャパシタ上部電極上部層と接続された画素電極と、

を有する薄膜トランジスタ基板。

#### 【請求項2】

請求項1記載の薄膜トランジスタ基板と、

透明基板上に、カラーフィルタ,透明コモン電極を形成したカラーフィルタ基板と、 前記薄膜トランジスタ基板と前記カラーフィルタ基板との間に挟持された液晶層と、 を有する液晶表示装置。

【発明の詳細な説明】

## 【技術分野】

#### [00001]

本発明は、薄膜トランジスタ基板および液晶表示装置に関し、特に補助蓄積容量を有する薄膜トラジスタ基板および液晶表示装置に関する。

### 【背景技術】

## [0002]

液晶表示装置は、近年情報機器などに広く用いられ、さらなる低コスト化、高画質化が求められている。薄膜トランジスタ基板の多くは,画素毎に画素電極用の情報を蓄積するため,補助蓄積容量を有している。補助蓄積容量は、通常不透明体で形成されるため、画素面積を減少させる原因となる。比較的大きい面積を占める補助蓄積容量の小型化が要求される。また、補助蓄積容量の製造工程において、層間短絡等が生じると不良が発生する。不良発生は極力低減することが望まれる。

## [0003]

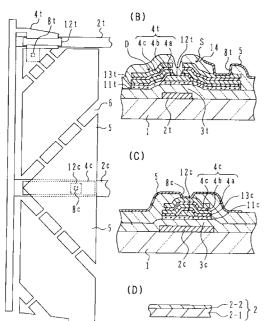

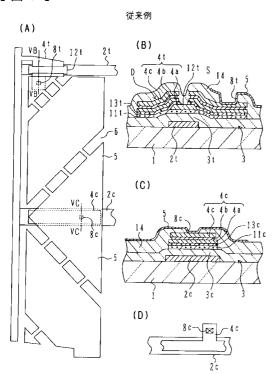

図5は、従来技術による薄膜トランジスタ基板の構成例を示す。

## [ 0 0 0 4 ]

図5(A)は、従来技術による薄膜トランジスタ基板の平面図を示す。図5(B)は、図5(A)のVB-VB線に沿う薄膜トランジスタ部分の断面図を示し、図5(C)は、図5(A)のVC-VC線に沿う補助蓄積容量部分の断面図を示す。

#### [0005]

ガラス基板等の絶縁性表面を有する基板1の上に、同一金属層をパターニングすることによりゲートバスライン2 t と補助蓄積容量バスライン2 c が形成される。バスライン2 t と2 c とは、互いに電気的に分離されている。バスライン2 t と2 c を覆って、基板1全面上に窒化シリコン等の絶縁層3が形成される。絶縁層3は、薄膜トランジスタ部分では、ゲート絶縁膜3 t を構成し、補助蓄積容量部分では、キャパシタ誘電体膜3 c を構成

20

10

30

0

40

する。

[0006]

絶縁層3の上に、薄膜トランジスタのチャネルを構成することのできる高抵抗率アモルファスシリコン層11が堆積され、その上にエッチングストッパの機能を有する窒化シリコン層12が堆積される。窒化シリコン層12をパターニングし、薄膜トランジスタのチャネルとなる領域上にのみチャネル保護層12tを残す。チャネル保護層12tを覆って、高抵抗率アモルファスシリコン層11の上に、n型不純物を高濃度にドープしたn゚型(低抵抗率)アモルファスシリコン層13を堆積する。なお、アモルファスシリコン層、窒化シリコン層は、例えば化学気相堆積(CVD)で堆積する。

[0007]

アモルファスシリコン層 1 3 の上に、Ti層 4 a、 A 1 層 4 b、 Ti層 4 c を例えばスパッタリングで積層する。Ti層 4 c の上にレジストパターンを形成し、Ti層 4 c 、 A 1 層 4 b、 Ti層 4 a、 n <sup>†</sup>型アモルファスシリコン層 1 3、高抵抗率アモルファスシリコン層 1 1をパターニングする。なお、チャネル領域上にはチャネル保護層 1 2 t が形成されているため、チャネル領域上のエッチングはチャネル保護層 1 2 t で停止され、その下の高抵抗率アモルファスシリコン層 1 1 はエッチングされない。

[0008]

このようにして、薄膜トランジスタ領域にはソース / ドレイン電極、補助蓄積容量領域においては、キャパシタの上部電極が形成される。

[0009]

Ti層4cを覆って、絶縁層3の上に窒化シリコン等の絶縁保護層14をCVD等により堆積する。薄膜トランジスタのソース領域上および補助蓄積容量の接続領域の上部電極上にコンタクト用開口8t及び8cを形成する。このエッチング工程において、例えばTi層4c、A1層4b、Ti層4aにピンホールが存在すると、エッチングはその下の層にまで及んでしまう。

[0010]

図 5 ( C ) に示す接続孔 8 c の底面の金属積層に、ピンホールが存在すると、エッチングはアモルファスシリコン層 1 3 c 、 1 1 c およびその下の絶縁層 3 c に及び、下部電極 2 c まで達することもある。

[0011]

その後、保護絶縁層14の上に、接続孔を覆って、ITO(インジウム・錫酸化物)層5を堆積し、パターニングすることにより画素電極を形成する。なお、ピンホールにより下部電極2cが露出していると、画素電極5がキャパシタの下部電極と上部電極とを短絡し、キャパシタが機能を失ってしまう。

[0012]

図5(D)は、このような短絡を防止するため、画素電極とキャパシタの上部電極とのコンタクトをキャパシタの下部電極外の領域に設けた構成例を示す。上部電極のコンタクトが下部電極の外部に形成されるため、例えピンホールが生じても短絡を防止することができる。しかし、下部電極及び上部電極はそれぞれ不透明な層であり、下部電極よりも上部電極が外部に張り出すことにより、画素電極の有効面積はその分減少してしまう。

【特許文献 1 】特開平 8 - 1 6 0 4 5 7 号公報、公開日:平成 8 年 6 月 2 1 日

【 特 許 文 献 2 】 特 開 平 6 - 3 3 7 4 3 6 号 公 報 、 公 開 日 : 平 成 6 年 1 2 月 6 日

【発明の開示】

【発明が解決しようとする課題】

[0013]

補助蓄積容量を有する薄膜トランジスタ基板において、補助蓄積容量の電極間の短絡を防止すると共に、有効画素領域をできるだけ広く確保することは容易ではなかった。

[0014]

本発明の目的は、有効画素領域を広く確保すると共に、補助蓄積容量の電極間の短絡を防止することのできる薄膜トランジスタ基板及び液晶表示装置を提供することである。

10

20

30

40

20

30

50

#### [0015]

本発明の他の目的は、新規な構成を有する薄膜トランジスタ基板及び液晶表示装置を提供することである。

【課題を解決するための手段】

### [0016]

本発明によれば、絶縁性表面を有する基板と、前記基板上に形成され、同一の導電材料層からなるゲート電極およびキャパシタ下部電極と、第1絶縁層を介して、前記ゲート電極上方の表面に凹部を有する高抵抗率半導体のチャネル層と、前記第1絶縁層を介して、前記キャパシタ上部電極上方に、前記チャネル層で形成され、表面に凹部は有さない高抵抗率半導体のキャパシタ上部電極と、前記チャネル層の凹部は有さない高抵抗率の1対のソース/ドレイン電極と、前記キャパシタ上部電極下形成された低抵抗率の1対のソース/ドレイン電極と高に、前記キャパシタ上部電極上部層と、前記ソース/ドレイン電極、前記キャパシタ上部電極上部層を覆って、前記第1絶縁層上に形成された第2絶縁層上に形成された第3~を露出する第1接続孔、および、前記キャパシタ上部電極上部層の接続領域を露出する第2接続孔と、前記第2絶縁層上に形成され、前記第1接続孔をの接続領域を露出する第2接続孔と、前記第2絶縁層上に形成され、前記第1接続孔が第2接続れた画素電極と、を有する薄膜トランジスタ基板が提供される。

#### [0017]

また、本発明によれば、上述のような薄膜トランジスタ基板と、透明基板上に、カラーフィルタ、透明コモン電極を形成したカラーフィルタ基板と、薄膜トランジスタ基板とカラーフィルタ基板との間に挟持された液晶層と、を有する液晶表示装置が提供される。

### 【発明の効果】

[0018]

本発明の薄膜トランジスタ基板によれば、画素電極の有効領域を広く確保しつつ、補助蓄積容量の電極間短絡を防止することができる。それ故、新規な構成の薄膜トランジスタ 基板及び液晶表示装置が提供される。

【発明を実施するための最良の形態】

## [0019]

#### 〔参考形態〕

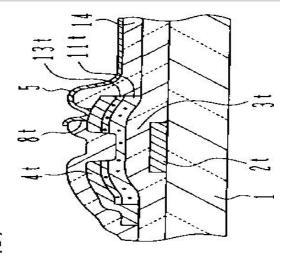

図1(A)~(D)は、本発明の参考形態による薄膜トランジスタ基板の構成を示す平面図及び断面図である。図1(B)は、図1(A)のIB IB線に沿う薄膜トランジスタ部分の断面図であり、図1(C)は、図1(A)のIC IC線に沿う補助蓄積容量部分の断面図である。

## [0020]

ガラス基板 1 の上に、電極層を例えばスパッタリングにより堆積し、ホトリソグラフィを用いたパターニングを行なうことにより、ゲートバスライン 2 t 及び補助蓄積容量バスライン 2 c を形成する。透過型液晶表示装置の場合は、透明基板を用いる。反射型液晶表示装置の場合は、透明基板に限らず、不透明基板を用いることもできる。但し、表面は絶縁性であることが必要である。酸化膜を形成したシリコン基板、表面に絶縁層を形成した金属板等、絶縁性表面を有する基板であればよい。

[0021]

図 1 ( D ) に示すように、この電極層は、好ましくは例えば下側に厚さ約 1 0 0 n m の A 1 層 2 - 1、上側に厚さ約 5 0 n m の T i 層 2 2 を積層して形成する。

#### [0022]

電極層のパターニングの後、例えば厚さ 4 0 0 n m の S i  $_3$  N  $_4$  層で形成した絶縁層 3 を 例えば C V D により堆積する。この絶縁層 3 は、薄膜トランジスタ領域においてはゲート 絶縁膜 3 t を構成し、補助蓄積容量においてはキャパシタ誘電体膜 3 c を形成する。

### [0023]

絶縁層3の上に、薄膜トランジスタのチャネルを構成することのできる、例えば厚さ3

0 n m の高抵抗率アモルファスシリコン層 1 1 を例えば C V D により堆積する。高抵抗率アモルファスシリコン層 1 1 の上に、エッチングストッパ層として、例えば厚さ約 1 5 0 n m の S i  $_3$  N  $_4$  層 1 2 を C V D により堆積する。 S i  $_3$  N  $_4$  層 1 2 を ホトリソグラフィーとエッチングを用いてパターニングし、薄膜トランジスタ領域にチャネル保護層 1 2 t を残し、補助蓄積容量領域にキャパシタ保護層 1 2 c を残す。

#### [0024]

この絶縁層 1 2 t 、 1 2 c を覆うように、高抵抗率アモルファスシリコン層 1 1 の上に例えば厚さ約 3 0 n m の  $n^{+}$ 型(低抵抗率)アモルファスシリコン層 1 3 を C V D で堆積する。その上に、例えば厚さ約 2 0 n m の T i 層 4 a 、厚さ約 7 5 n m の A l 層 4 b 、厚さ約 4 0 n m の T i 層 4 c を順次スパッタリングにより堆積する。

[0025]

その後、Ti層4cの上にレジストパターンを形成し、例えばC1系エッチングガスを用いた反応性イオンエッチング(RIE)によりTi層4c、A1層4b、Ti層4aをエッチングし、さらにn<sup>+</sup>型アモルファスシリコン層13、高抵抗率アモルファスシリコン層11をエッチングする。

#### [0026]

チャネル保護層12tは、エッチングストッパとして機能し、その下の高抵抗率シリコン層11tを保護する。チャネル保護層12tの両側においては、 n <sup>+</sup>型シリコン層13 tが高抵抗率シリコン層11tの上にコンタクトする。このようにして、チャネル層11 tの離れた領域上に1対のソース/ドレイン電極S,Dが形成される。

[0027]

又、補助蓄積容量領域においては、キャパシタ保護層 1 2 c は限られた領域内にのみ残されており、その周囲においては n <sup>†</sup>型シリコン層 1 3 c がその下の高抵抗率シリコン層 1 1 c にコンタクトする。高抵抗率シリコン層 1 1 c 、 n <sup>†</sup>型シリコン層 1 3 c 、金属電極 4 a 、 4 b 、 4 c は、キャパシタの上部電極を構成する。

[0028]

その後、ソース / ドレイン電極 S , D 及び上部電極を覆うように、例えば厚さ約 3 0 0 n m の S i  $_3$  N  $_4$  層の上部保護層 1 4 を C V D により堆積する。上部保護層 1 4 は、 S i  $_3$  N  $_4$  層の他、有機絶縁層等で形成してもよい。 S i  $_3$  N  $_4$  層 1 4 の上に、レジストパターンを形成し、ソース電極 S 上及び上部電極上に接続穴を開口するエッチングを行なう。この時、ドレイン電極 D はレジストパターンに覆われている。

[0029]

[0030]

なお、薄膜トランジスタのソース電極Sにおいては、同様に開口8tが形成される。ソース電極Sにおいては、例えピンホールが存在しても、ソース電極Sの一部がエッチングされるのみであり、その機能に与える影響は小さい。

[ 0 0 3 1 ]

Si₃ N₄層14に開口を形成した後、その上にITO層を堆積し、パターニングすることにより透明画素電極5を形成する。キャパシタの上部電極は、透明画素電極5を介してソース電極Sに接続され、ドレイン電極D,ソース電極Sを介して画素電極に駆動電圧が与えられた時に、キャパシタにその電圧を蓄積することができる。

[0032]

なお、アモルファスシリコン層を用いて薄膜トランジスタを形成する場合を説明したが、アモルファスシリコン層を堆積した後、XeC1レーザ光のアニーリングを行なうこと等により、アモルファスシリコン層を多結晶シリコン層に変換してもよい。多結晶シリコ

10

20

30

40

ン層を用いれば、薄膜トランジスタの性能を向上することができる。

#### [0033]

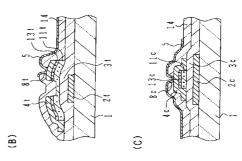

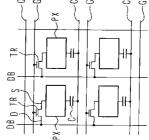

図2(A)は、薄膜トランジスタ基板に形成される回路の等価回路を示す。ドレインバスラインDBは、縦方向に複数本形成されている。ゲートバスラインGB及び補助蓄積容量バスラインCSBはそれぞれ水平方向に複数本形成されている。

#### [0034]

ドレインバスラインDBとゲートバスラインGBの各交差点に、薄膜トランジスタTRが接続される。薄膜トランジスタTRのドレイン電極DがドレインバスラインDBに接続され、絶縁ゲート電極がゲートバスラインGBに接続され、ソース電極Sは、透明画素電極PXに接続される。

## [0035]

透明画素電極PXと補助蓄積容量バスラインCSBとの間に、キャパシタCが接続される。補助蓄積容量バスラインCSBは接地電圧等の定電圧に保持され、キャパシタCは、ドレインバスラインDBからドレイン電極Dを介して供給される画像信号電圧を蓄積する。図には、2行、2列の構成を示したが、実際の薄膜トランジスタ基板には、多数行、多数列の画素が形成される。

### [0036]

上記参考例では、チャネル層の上にエッチングストッパを形成する構成を説明したが、 チャネル層を厚くし、エッチングストッパを省略することもできる。

### [0037]

〔実施の形態〕

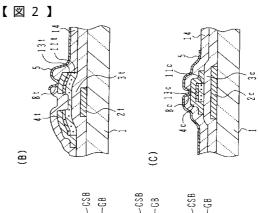

図 2 ( B ) は、本発明の実施の形態として、チャネルエッチタイプの薄膜トランジスタを用いた場合の構成を示す。なお、図 1 における構成と同様の構成には、同様の符号を付して説明を簡略化する。

### [0038]

ゲート絶縁層3t、キャパシタ誘電体層3cを構成する絶縁層3を堆積した後、チャネルを形成することのできる高抵抗率アモルファスシリコン層11を堆積し、その上にn型不純物を高濃度にドープしたn゚型アモルファスシリコン層13を堆積する。その後、n゚型アモルファスシリコン層13の上にレジストパターンを形成し、エッチングを行なうことによりn゚型アモルファスシリコン層13、n型アモルファスシリコン層11をパターニングし、薄膜トランジスタ領域及び蓄積容量形成領域にのみシリコン層13t、11t、13c、11cを残す。

#### [0039]

その後、金属電極層 4 を堆積し、パターニングを行なうことによりソース / ドレイン電極 4 t 及びキャパシタの上部金属電極 4 c をパターニングする。このエッチングにおいて、金属電極層をエッチングした後エッチング量をコントロールすることにより、 n <sup>+</sup>型アモルファスシリコン層 1 3 t はエッチングするが、その下の高抵抗率アモルファスシリコン層 1 1 t の厚さの一部は残るようにエッチングを制御する。なお、補助蓄積容量領域においては、アモルファスシリコン層 1 3 c、 1 1 c は完全に金属電極層 4 c で覆われている。

# [ 0 0 4 0 ]

その後、前述の参考形態と同様、 $Si_3N_4$ 層 1 4 を堆積し、 $Si_3N_4$ 層 1 4 を貫通する接続孔 8 t、 8 c をエッチングで形成する。接続孔 8 t、 8 c を開口した後、透明画素電極 5 を堆積、パターニングする。

#### [0041]

S  $i_3$  N  $_4$  層に接続孔 8 t 、 8 c をエッチングする時に、金属電極層 4 c にピンホールが存在しても、エッチングは先ずその下のシリコン層 1 3 c 、 1 1 c に対して行なわれ、その後 S  $i_3$  N  $_4$  層 3 c に進む。従って、下部電極 2 c が露出する前にエッチングを停止することができ、上部電極と下部電極との短絡を防止することができる。

## [0042]

50

20

10

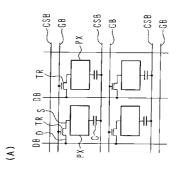

30

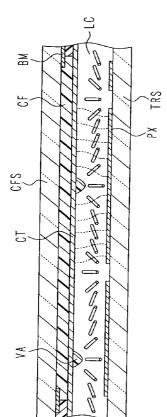

図3は、上述のような薄膜トランジスタ基板と公知のカラーフィルタ基板とを用いて液晶表示装置を形成した状態を示す。薄膜トランジスタ基板TRSの表面には、画素電極PXが形成されている。

#### [0043]

対向するカラーフィルタ基板 CFSの上には、例えば赤、緑、青のカラーフィルタ CFが形成され、カラーフィルタ CFの上に表示領域全体に共通の透明コモン電極 CTがIT Oで形成されている。さらに、局所的に絶縁性突起部 VAが形成されている。突起部 VA が存在する部分においては、電気力線の分布が調整される。

#### [0044]

電極間に電圧を印加しない状態においては、液晶層LCの液晶分子は、基板表面に垂直に配向する。電極間に電圧を印加すると、液晶層LC内の液晶は、電気力線に垂直に配列するようにその配向が変調される。突起部VAにおいては、電圧無印加時の液晶分子の配向が傾いているため、電圧を印加した時に液晶分子が倒れこむ方向を制御することができる。従って、配向方向の異なる複数の領域を有するマルチバーチィカル配列(MVA)液晶表示装置が構成される。

#### [0045]

補助蓄積容量は、ゲートバスラインと別個に補助蓄積容量バスラインを形成し、その上に形成する場合に限らない。ゲートバスラインを利用して補助蓄積容量を形成することもできる。

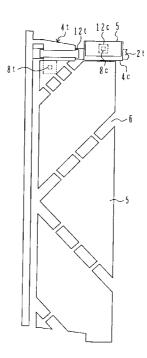

### [0046]

図 4 は、ゲートバスライン上に補助蓄積容量を形成する構成例を示す。ゲートバスライン 2 tを形成する。ゲートバスライン 2 t は、薄膜トランジスタを形成する領域の他、補助蓄積キャパシタを形成する領域を含む。ゲートバスラインの上にゲート絶縁膜を形成した後、チャネルを構成する高抵抗率アモルファスシリコン層、エッチングストッパとなる S i  $_3$  N  $_4$  層を堆積する。 S i  $_3$  N  $_4$  層を選択的にエッチングし、ゲートバスライン上の薄膜トランジスタ領域と補助蓄積キャパシタ領域にチャネル保護膜 1 2 t、キャパシタ保護膜 1 2 c を残す。

#### [0047]

ソース / ドレイン電極及び上部電極を形成する n <sup>+</sup>型アモルファスシリコン層、金属電極層を堆積し、パターニングすることにより、薄膜トランジスタ領域にソース / ドレイン電極 4 t を形成すると共に、補助蓄積キャパシタ領域に上部電極 4 c を形成する。その後、前述の実施例同様の工程を行なうことにより、薄膜トランジスタ基板を形成する。

#### [0048]

なお、上部電極 4 c は、図中上の画素の透明画素電極 5 と接続孔 8 c を介して接続される。このような構成とすれば、補助蓄積容量の上部電極に印加される電圧は隣の画素の電圧であり、その時ゲートバスライン 2 t は定電位に保持されている。従って、補助蓄積容量に効率的に電荷を蓄積することができる。

### [0049]

ゲートバスライン、補助蓄積容量下部電極を A 1 / T i 積層で形成する場合を説明したが、このバスラインは他の導電体で形成してもよい。例えば、 C r 単層、 A 1 / M o 積層構成とすることもできる。

#### [0050]

ゲート絶縁膜、エッチングストッパ層、上部絶縁保護膜を窒化シリコン層で形成する場合を説明したが、他の絶縁層を用いてもよい。例えば、酸化シリコン層、酸化窒化シリコン層を用いることもできる。複数種類の絶縁層を組合わせて用いてもよい。

## [0051]

ソース / ドレインの金属電極を T i / A l / T i 積層で形成する場合を説明したが、他の導電体で形成しても良い。例えば、 C r 単層、 M o / A l / M o 積層で形成しても良い

## [0052]

40

20

その他種々の変更、改良、組み合わせが可能なことは当業者に自明であろう。

## [0053]

以下,本発明の特徴を付記する。

#### [0054]

(付記1) 絶縁性表面を有する基板と、前記基板上に形成された導電材料層のゲート 電極と、前記基板上に,前記ゲート電極と同一材料層で形成されたキャパシタ下部電極と 前記ゲート電極と前記キャパシタ下部電極とを覆って,前記基板上に形成された第1絶 縁層と、前記第1絶縁層上で、前記ゲート電極を跨いで形成された高抵抗率半導体のチャ ネル層と、前記第1絶縁層上で、前記キャパシタ下部電極上方に、前記チャネル層と同一 材料層で形成された高抵抗率半導体のキャパシタ上部電極下部層と、前記チャネル層の中 間部上に形成されたチャネル保護層と、前記キャパシタ上部電極下部層の接続領域上に, 前 記 チャ ネ ル 保 護 層 と 同 一 材 料 層 で 形 成 さ れ た キャ パ シ タ 保 護 層 と 、 前 記 チャ ネ ル 保 護 層 上で分離されて、前記チャネル層上に形成された゚゚・型の1対のソース/ドレイン電極と、 前記キャパシタ保護層を覆って、前記キャパシタ上部電極下部層上に,前記ソース/ドレ イン 電極と同一材料層で形成されたキャパシタ上部電極上部層と、前記ソース / ドレイン 電 極 ,前記 キャパシタ上部 電 極 上部 層 を 覆 っ て ,前 記 第 1 絶 縁 層 上 に 形 成 さ れ た 第 2 絶 縁 層と、前記第2絶縁層を貫通し、前記1対のソース/ドレイン電極の一方を露出する第1 接続孔と、前記第2絶縁層を貫通し、前記キャパシタ上部電極上部層の接続領域を露出す る第2接続孔と、前記第2絶縁層上に形成され,前記第1接続孔および第2接続孔で、前 記 一 方 の ソ ー ス / ド レ イ ン 電 極 お よ び 前 記 キ ャ パ シ タ 上 部 電 極 上 部 層 と 接 続 さ れ た 画 素 電 極と、を有する薄膜トランジスタ基板。

#### [0055]

(付記2) 前記ゲート電極と前記キャパシタ下部電極とが、それぞれ、前記基板上に 形成された電気的に分離されたバスラインの一部で形成されている付記1記載の薄膜トランジスタ基板。

## [0056]

(付記3) 前記ゲート電極と前記キャパシタ下部電極とが、前記基板上に形成された ゲートバスラインの異なる部分で形成されている付記1記載の薄膜トランジスタ基板。

## [ 0 0 5 7 ]

(付記4) 前記チャネル層,前記キャパシタ上部電極下部層は,高抵抗率アモルファスシリコン層で形成され,前記ソース/ドレイン電極,前記キャパシタ上部電極上部層は、前記高抵抗率アモルファスシリコン層上に形成されたドープドアモルファスシリコン層を含む付記1記載の薄膜トランジスタ基板。

## [0058]

(付記5) 絶縁性表面を有する基板と、前記基板上に形成された導電材料層のゲート電極と、前記基板上に,前記ゲート電極と同一材料層で形成されたキャパシタ下電極と高記が一ト電極と前記まれた第12000 表面に野記第1 絶縁層上で、前記が一ト電極を跨いで形成され、前記が一ト電極上で、前記が一ト電極を跨いで形成され、前記が一ト電極上で、前記キャネル層と、前記第1 絶縁層上で、前記キャル層と、前記第1 絶縁層上で、前記キャネル層の凹部両側領域上に形成 カンタト部電極上方に、前記チャネル層の凹部両側領域上に形成 前記 チャネル層の凹部電極上に形成 前記 チャネル層の凹部電極上に形成 前記 チャスル層の凹部電極上に形成 前記 カンタ上部電極上に形成 前記 キャパシタ上部電極上に形成 前記 カンタース / ドレイン電極と、前記 キャパシタ上部電極上に形成 された 中スノドレイン電極の一方を 大大 に 前記第2 絶縁層を貫通し、前記 キャパシタ上部電極上部層の接続 1 接続孔と、前記第2 絶縁層上に形成され,前記第1 接続孔および第2 接続孔で、前記一方のソース / ドレイン電極および前記キャパシタ上部電極上部層と接続 領域を露出する第2 接続孔と、前記第2 絶縁層上に形成され,前記第1 接続孔および第2 接続孔で、前記一方のソース / ドレイン電極および前記キャパシタ上部電極上部層と接続 領域を露出する第2 接続孔と、前記第2 絶縁層上に形成され,前記第1 接続孔および第2 接続孔で、前記一方のソース / ドレイン電極および前記キャパシタ上部電極上部層と接続 1 表記第2 を有する薄膜トランジスタ基板。

## [0059]

50

40

20

10

20

30

40

50

(付記6) 前記ゲート電極と前記キャパシタ下部電極とが、それぞれ、前記基板上に 形成された電気的に分離されたバスラインの一部で形成されている付記5記載の薄膜トランジスタ基板。

#### [0060]

(付記7) 前記ゲート電極と前記キャパシタ下部電極とが、前記基板上に形成された ゲートバスラインの異なる部分で形成されている付記5記載の薄膜トランジスタ基板。

## [0061]

(付記8) 前記チャネル層,前記キャパシタ上部電極下部層は,高抵抗率アモルファスシリコン層で形成され,前記ソース/ドレイン電極,前記キャパシタ上部電極上部層は、前記高抵抗率アモルファスシリコン層上に形成されたドープドアモルファスシリコン層を含む付記5記載の薄膜トランジスタ基板。

#### [0062]

(付記9) 付記1~8のいずれか1項記載の薄膜トランジスタ基板と、透明基板上に、カラーフィルタ,透明コモン電極を形成したカラーフィルタ基板と、前記薄膜トランジスタ基板と前記カラーフィルタ基板との間に挟持された液晶層と、を有する液晶表示装置

## [0063]

(付記10) ( a ) 基板上に、導電材料層を堆積し,パターニングすることにより、 ゲ ー ト 電 極 と キ ャ パ シ タ 下 部 電 極 と を 形 成 す る 工 程 と 、 ( b ) 前 記 ゲ ー ト 電 極 と 前 記 キ ャ パシタ下部電極とを覆って,前記基板上に第1絶縁層を堆積する工程と、(c)前記第1 絶 縁 層 上 に 、 高 抵 抗 率 半 導 体 層 と 、 そ の 上 に エ ッ チ ン グ ス ト ッ パ 層 と を 堆 積 す る 工 程 と 、 ( d )前記エッチングストッパ層を選択的にエッチングし、前記ゲート電極上方の前記高 抵抗率半導体層のチャネル領域の中間部上にチャネル保護層を、前記キャパシタ下部電極 上方の前記高抵抗率半導体層の接続領域上にキャパシタ保護層を残す工程と、(e)前記 チャネル保護層,前記キャパシタ保護層を覆って,前記高抵抗半導体層上に低抵抗率半導 体層を堆積し,その上に金属層を堆積する工程と、(f)前記金属層,前記低抵抗率半導 体層,前記高抵抗率半導体層を選択的にエッチングし、高抵抗率半導体層のチャネル層, その上に前記チャネル保護層上で分離された低抵抗率の 1 対のソース / ドレイン電極、高 抵抗率半導体層のキャパシタ上部電極下部層、前記キャパシタ保護層を覆う、前記キャパ シ タ 上 部 電 極 下 部 層 上 の キ ャ パ シ タ 上 部 電 極 上 部 層 を 形 成 す る 工 程 と 、 ( g ) 前 記 ソ ー ス / ドレイン電極 , 前記キャパシタ上部電極上部層を覆って , 前記第 1 絶縁層上に第 2 絶縁 層を形成する工程と、(h)前記第2絶縁層を貫通し、前記1対のソース/ドレイン電極 の一方を露出する第1接続孔と、前記第2絶縁層を貫通し、前記キャパシタ上部電極上部 層を露出する第2接続孔とをエッチングする工程と、(i)前記第2絶縁層上に,前記第 1 接 続 孔 お よ び 第 2 接 続 孔 で 、 前 記 一 方 の ソ ー ス / ド レ イ ン 電 極 お よ び 前 記 キ ャ パ シ タ 上 部 電 極 上 部 層 と 接 続 さ れ た 画 素 電 極 を 形 成 す る 工 程 と 、 を 有 す る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製造方法。

### [0064]

(付記11) 前記工程(f)が、前記1対のソース / ドレイン電極間の前記チャネル保護層をエッチングストッパとして,前記金属層,前記低抵抗率半導体層,前記高抵抗率半導体層をエッチングする工程を含み、む付記10記載の薄膜トランジスタ基板の製造方法。

## [0065]

(付記12) (a)基板上に、導電材料層を堆積し、パターニングすることにより、ゲート電極とキャパシタ下部電極とを形成する工程と、(b)前記ゲート電極と前記キャパシタ下部電極とを覆って、前記基板上に第1絶縁層を堆積する工程と、(c)前記第1 絶縁層上に、高抵抗率半導体層、その上の低抵抗率半導体層を堆積し、パターニングすることにより、前記ゲート電極を跨いだチャネル層とコンタクト層、前記キャパシタ下部電極上方のキャパシタ上部電極下部層とを形成する工程と、(d)前記コンタクト層、前記キャパシタ上部電極下部層を覆って、前記第1絶縁層上に金属電極層を堆積する工程と、

(e)前記金属電極層,前記チャネル層上の前記高抵抗率半導体層を選択的にエッチングし、分離された低抵抗率の1対のソース / ドレイン電極、前記キャパシタ上部電極下部層上のキャパシタ上部電極上部層を形成する工程と、(f)前記ソース / ドレイン電極,前記キャパシタ上部電極上部層を覆って,前記第1絶縁層上に第2絶縁層を形成する工程と、(g)前記第2絶縁層を貫通し、前記1対のソース / ドレイン電極の一方を露出する第1接続孔と、前記第2絶縁層を貫通し、前記キャパシタ上部電極上部層を露出する第2接続孔とをエッチングする工程と、(h)前記第2絶縁層上に,前記第1接続孔および第2接続孔で、前記一方のソース / ドレイン電極および前記キャパシタ上部電極上部層と接続された画素電極を形成する工程と、を有する薄膜トランジスタ基板の製造方法。

[0066]

10 電 極

(付記13) 前記工程(e)が、前記1対のソース/ドレイン電極間の前記金属電極層,前記コンタクト層、前記チャネル層の一部厚さをエッチングし前記1対のソース/ドレイン電極を形成する工程を含む付記12記載の薄膜トランジスタ基板の製造方法。

[0067]

(付記14) 絶縁性表面を有する基板と、前記基板上に形成され、同一の導電材料層からなるゲート電極およびキャパシタ下部電極と、第1絶縁層を介して、前記ゲート記を跨いで形成された高抵抗率半導体のチャネル層と、前記第1絶縁層を介して、前記チャネル層と、前記第1絶縁層を介して、前記チャネル層と、前記第1絶縁層を介して、前記チャネル層と、前記第1絶縁層を介して、前記チャネル保護層と、前記チャネル保護層と、前記チャネル保護層と、前記チャネル保護層と、前記チャネル保護層とに形成されたチャネル保護層と、前記チャネル保護層とに形成成記チャネル層上に形成成記チャネル層上に形成成記チャネル層上に形成は主ャパシタ保護層を覆って、前記チャネル保護層をで形成されたキャパシタと部電極上部層と、前記ソース/ドレイン電極、前記キャパシタ上部電極上部層を開通し、前記1対のソース/ドレイン電極、前記第1絶縁層上に形成された第2絶縁層を貫通し、前記1対のソース/ドレイン電極の一方を露出する第1接続孔、および、前記キャパシタ上部電極上部層の接続領域をである第2接続孔と、前記第2絶縁層上に形成され、前記第1接続孔および第2接続記で素電極と、を有する薄膜トランジスタ基板。

[0068]

30

20

(付記15) 前記ゲート電極と前記キャパシタ下部電極とが、それぞれ、前記基板上に形成された電気的に分離されたバスラインの一部で形成されている付記14記載の薄膜トランジスタ基板。

(付記16) 前記ゲート電極と前記キャパシタ下部電極とが、前記基板上に形成されたゲートバスラインの異なる部分で形成されている付記14記載の薄膜トランジスタ基板。

【産業上の利用可能性】

[0069]

本発明の薄膜トランジスタ基板は、近年情報機器などに広く用いられる液晶表示装置に採用することができる。

【図面の簡単な説明】

40

[ 0 0 7 0 ]

【図1】本発明の参考形態による薄膜トランジスタ基板を説明する平面図及び断面図である。

【図2】(A)は薄膜トランジスタ基板の透過回路図、(B)及び(C)は本発明の実施 形態による薄膜トランジスタ基板を説明する断面図である。

【図3】液晶表示装置の断面図である。

【図4】本発明の他の参考形態よる薄膜トランジスタ基板の構成を示す平面図である。

【図 5 】従来の技術による薄膜トランジスタ基板の構成を説明するための平面図及び断面図である。

【符号の説明】

10

20

[0071]

- 1 基板

- 2 電極層

- 2 1 A l 層

- 2 2 Ti層

- 3 絶縁層(Si<sub>3</sub>N<sub>4</sub>層)

- 4 電極層

- 4 a 、4 c T i 層

- 4 b A l 層

- 5 画素電極層(ITO層)

- 6 突起部

- 8 接続孔

- 11 高抵抗率アモルファスシリコン層

- 1 2 エッチングストッパ層 (Si<sub>3</sub>N<sub>4</sub>層)

- 1 3 n <sup>+</sup>型 (低抵抗率) アモルファスシリコン層

- 1 4 上部 絶 縁 保 護 層 ( S i <sub>3</sub> N <sub>4</sub> 層 )

- t 薄膜トランジスタ領域を示す添字

- c補助蓄積容量領域を示す添字

- DB ドレインバスライン

- GB ゲートバスライン

- CSB 補助蓄積容量バスライン

- TR 薄膜トランジスタ

- PX 画素電極

- Sソース電極

- D ドレイン電極

【図1】

【図3】

【図4】

【図5】

# フロントページの続き

F ターム(参考) 5F110 AA30 BB01 CC07 DD02 DD05 EE03 EE04 EE14 EE44 FF02

FF03 FF04 FF09 FF29 GG02 GG13 GG15 GG25 GG44 HK03

HK04 HK09 HK15 HK22 HK33 HK34 NN04 NN14 NN24 NN35

NN72 NN73 PP03 QQ04

| 专利名称(译)        | 薄膜晶体管基板和液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | JP2006189896A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2006-07-20 |

| 申请号            | JP2006064659                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2006-03-09 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 藤川徹也<br>土井誠児                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 藤川 徹也<br>土井 誠児                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G02F1/1368 H01L29/786 H01L21/336                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G02F1/1368 H01L29/78.612.Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H092/HA04 2H092/JA24 2H092/JB64 2H092/JB68 2H092/KA04 2H092/KA05 2H092/KA18 2H092 /KA22 2H092/KB04 2H092/KB13 2H092/MA05 2H092/MA17 2H092/MA30 2H092/NA07 2H092/NA16 2H092/NA29 5F110/AA30 5F110/BB01 5F110/CC07 5F110/DD02 5F110/DD05 5F110/EE03 5F110 /EE04 5F110/EE14 5F110/EE44 5F110/FF02 5F110/FF03 5F110/FF04 5F110/FF09 5F110/FF29 5F110 /GG02 5F110/GG13 5F110/GG15 5F110/GG25 5F110/GG44 5F110/HK03 5F110/HK04 5F110/HK09 5F110/HK15 5F110/HK22 5F110/HK33 5F110/HK34 5F110/NN04 5F110/NN14 5F110/NN24 5F110 /NN35 5F110/NN72 5F110/NN73 5F110/PP03 5F110/QQ04 2H192/AA24 2H192/BA25 2H192/BC31 2H192/CB05 2H192/CB46 2H192/CB54 2H192/CB71 2H192/CC04 2H192/CC32 2H192/CC72 2H192 /DA12 2H192/DA44 2H192/EA22 2H192/EA43 2H192/GA42 2H192/GD14 2H192/JA13 |         |            |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

解决的问题:提供一种能够确保宽的有效像素区域并防止辅助存储电容器的电极之间短路的薄膜晶体管基板和液晶显示装置。 薄膜晶体管基板覆盖导电材料层的栅电极(2t)和电容器下电极(2c),形成在基板上的第一绝缘层(3t,3c)和第一绝缘层(3)。 形成的高电阻率半导体沟道层11t,11c,13t,13c,在沟道层上形成的一对源极/漏极4t,以及在电容器上部电极下层上形成的电容器上部电极上部分。 层4c,形成在第一绝缘层上并覆盖层4c的第二绝缘层14,穿透第二绝缘层并露出源电极的第一连接孔8t和电容器上电极上层 它具有暴露连接区域的第二连接孔8c和在其上形成的像素电极5。 [选择图]图2