(19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-38212 (P2004-38212A)

(43) 公開日 平成16年2月5日(2004.2.5)

(51) Int.C1.7

$\mathbf{F} \mathbf{1}$

テーマコード (参考)

GO2F 1/1368 HO1L 21/336 HO1L 29/786 GO2F 1/1368

2H092

HO1L 29/78 612D

5F110

審査請求 有 請求項の数 5 〇L (全 10 頁)

(21) 出願番号

特願2003-351828 (P2003-351828)

(22) 出願日 (62) 分割の表示 平成15年10月10日 (2003.10.10) 特願2001-315963 (P2001-315963)

の分割

原出願日

平成4年7月6日 (1992.7.6)

|(71)出願人 302036002

富士通ディスプレイテクノロジーズ株式会

社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100108187

弁理士 横山 淳一

(72) 発明者 廣田 四郎

神奈川県川崎市中原区上小田中1015番

地 富士通株式会社内

(72) 発明者 間島 庭司

神奈川県川崎市中原区上小田中1015番

地 富士通株式会社内

最終頁に続く

#### (54) 【発明の名称】液晶表示装置

### (57)【要約】

【課題】 アクティブマトリックス型の液晶表示装置において、補助容量の製造工程の簡略化を図る。

【解決手段】 薄膜トランジスタと補助容量とをマトリックス状に配置してなる液晶表示装置において、画素領域の薄膜トランジスタが、基板上のゲート電極、ゲート電極を覆うゲート絶縁膜、ゲート絶縁膜上の動作層、動作層上部にのみ形成されるソース電極およびドレイン電極とを覆う保護膜とを備え、ゲート電極と同じ材料からなりゲート電極と同層に設けられる補助容量電極、ソース電極上で接続され、ソース電極外周部の側壁とその下部の動作層の外周部の側壁と接する画素電極、及び、ゲート絶縁膜に連なる絶縁層を含む誘電体で構成される補助容量を有するように構成する。

【選択図】 図3

20

30

40

50

#### 【特許請求の範囲】

#### 【請求項1】

基板上に薄膜トランジスタと補助容量とをマトリックス状に配置してなる液晶表示装置であって.

画素領域の前記薄膜トランジスタが、前記基板上のゲート電極、前記ゲート電極を覆うゲート絶縁膜、前記ゲート絶縁膜上の動作層、前記動作層上部にのみ形成されるソース電極およびドレイン電極、前記ソース電極およびドレイン電極とを覆う保護膜とを備え、

前記ゲート電極と同じ材料からなり前記ゲート電極と同層に設けられる補助容量電極、前記ソース電極上で接続され、前記ソース電極外周部の側壁とその下部の前記動作層の外周部の側壁と接する画素電極、及び、前記ゲート絶縁膜に連なる絶縁層および前記保護膜に連なる絶縁層を含む誘電体で構成される補助容量を有することを特徴とする液晶表示装置。

#### 【請求項2】

基板上に薄膜トランジスタと補助容量とをマトリックス状に配置してなる液晶表示装置であって、

画素領域の前記薄膜トランジスタが、前記基板上のゲート電極、前記ゲート電極を覆うゲート絶縁膜、前記ゲート絶縁膜上の動作層、前記動作層上部にのみ形成されるソース電極およびドレイン電極、ドレインバスライン、前記ソース電極、ドレイン電極および前記ドレインバスラインとを覆う保護膜とを備え、

前記ゲート電極と同じ材料からなり前記ゲート電極と同層に設けられる補助容量電極、前記ソース電極上で接続され、前記ソース電極外周部の側壁とその下部の前記動作層の外周部の側壁と接する画素電極、及び、前記ゲート絶縁膜に連なる絶縁層および前記保護膜に連なる絶縁層を含む誘電体で構成される補助容量を有することを特徴とする液晶表示装置。

#### 【請求項3】

基板上に薄膜トランジスタと補助容量とをマトリックス状に配置してなる液晶表示装置であって、

画素領域の前記薄膜トランジスタが、前記基板上のゲート電極、前記ゲート電極を覆うゲート絶縁膜、前記ゲート絶縁膜上の動作層、前記動作層上部にのみ形成されるソース電極およびドレイン電極、前記ソース電極および前記ドレイン電極と同時に形成されるドレインバスライン、前記ソース電極、ドレイン電極および前記ドレインバスラインとを覆う保護膜とを備え、

前記ゲート電極と同じ材料からなり前記ゲート電極と同層に設けられる補助容量電極、前記ソース電極上で接続された画素電極、及び、前記ゲート絶縁膜に連なる絶縁層および前記保護膜に連なる絶縁層を含む誘電体で構成される補助容量を有することを特徴とする液晶表示装置。

#### 【請求項4】

基板上に薄膜トランジスタと補助容量とをマトリックス状に配置してなる液晶表示装置であって、

画素領域の前記薄膜トランジスタが、前記基板上のゲート電極、前記ゲート電極を覆うゲート絶縁膜、前記ゲート絶縁膜上の動作層、前記動作層上部にのみ形成されるソース電極およびドレイン電極、前記ソース電極およびドレイン電極と同時に形成される前記動作層上部にのみ形成されるドレインバスライン、前記ソース電極、ドレイン電極および前記ドレインバスラインとを覆う保護膜とを備え、

前記ゲート電極と同じ材料からなり前記ゲート電極と同層に設けられる補助容量電極、前記ソース電極上で接続された画素電極、及び、前記ゲート絶縁膜に連なる絶縁層及び前記保護膜に連なる絶縁層を含む誘電体で構成される補助容量を有することを特徴とする液晶表示装置。

#### 【請求項5】

前記画素電極は、前記ソース電極外周部の側壁とその下部の前記動作層の外周部の側壁

20

30

40

50

と接することを特徴とする請求項3または4記載の液晶表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、補助容量の製造工数を削減した構造を有するアクティブマトリックス形の液晶表示装置において、補助容量を大きくするとともに、容量電極の面積を小さくして開口率の向上を図った液晶表示装置に関する。

#### [00002]

液晶表示装置には単純マトリックス形とアクティブマトリックス形とがあり、用途によりそれぞれ使い分けされているが、アクティブマトリックス形は薄膜トランジスタを各画素に備えており、特定の画素を選択する時にそのトランジスタをONさせ、それ以外はOFFにしておくことから、走査線の数が多くてもクロストークを抑制することができ、高いコントラスト比を得ることができる。

#### [00003]

そのため、アクティブマトリックス形の液晶表示装置は大面積表示用に適しており、実用化が進められている。

#### 【背景技術】

#### [0004]

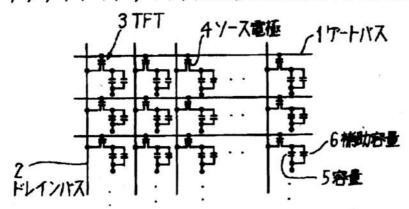

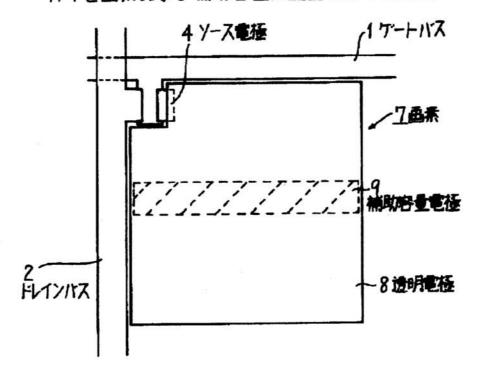

図 4 はアクティブマトリックス形液晶表示装置の等価回路を示しており、また、図 5 は薄膜トランジスタ(TFT)と画素および補助容量の配置を示す正面図である。

#### [0005]

すなわち、複数のゲートバス 1 と複数のドレインバス 2 とがそれぞれ直交し、その交差部に薄膜トランジスタ(TFT) 3 があり、このTFT 3 のソース電極 4 に容量 5 と補助容量 6 とを並列に配列する構造をとる。

#### [0006]

すなわち、TFTのソース電極4は画素7を構成する一方の透明電極8と回路接続しているが、画素7は透明電極8を電極とし、他のガラス基板上に形成した透明電極との間に液晶を介在させて構成されるので、静電容量を有しており、電気的に容量5として示すことができる。

#### [0007]

然し、この容量 5 だけでは静電容量が不足し、TFT 3 のスイッチング動作に当たって 画面のちらつき(フリッカ)や残像(焼きつき)を生ずるという問題がある。

### [ 0 0 0 8 ]

そこで、補助容量 5 の付加が必要であり、ガラス基板上に補助容量電極 9 を形成し、ガラス基板上に形成してある絶縁膜を誘電体と、透明電極 8 と対向させて補助容量 6 を構成している。

#### [0009]

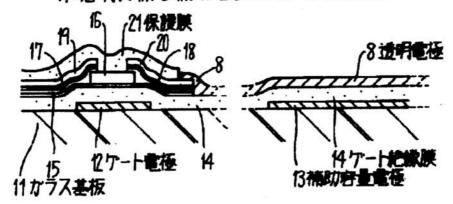

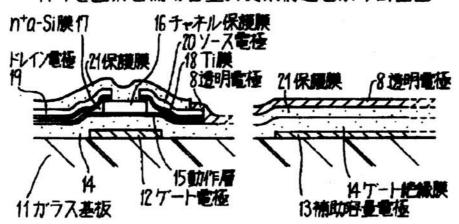

図3は逆スタッガー型TFTと画素と補助容量の従来構造を示す断面図であり、次の工程により作られている。

## [ 0 0 1 0 ]

すなわち、硼珪酸ガラスなどよりなり、厚さが約1mmのガラス基板11の上に、アルミニウム(A1)やタンタル(Ta)のような金属を約100nmの厚さに形成した後、写真蝕刻技術(フォトリソグラフィ)を用いて選択エッチングを行い、ゲート電極12と補助容量電極13を形成する。

## [0011]

次に、プラズマ C V D 法により窒化シリコン( S  $i_3$  N  $_x$  ) のような絶縁物を約 4 0 0 n m の厚さに被覆してゲート絶縁膜 1 4 を形成する。

#### [0012]

次に、この上に先と同様にプラズマCVD法などにより動作層15として働く非晶質シ

リコン膜(以下 a - S i 膜)と S i  $_3$  N  $_x$  膜を形成し、 S i  $_3$  N  $_x$  膜は写真蝕刻技術を用いてパターンニングし、チャネル保護膜 1 6 を形成する。

#### [0013]

次に、プラズマ C V D 法により n 型不純物を添加した非晶質シリコン膜(n <sup>+</sup> a - S i 膜) 1 7 と密着を助けるための T i 膜 1 8 と A 1 膜とを形成し、先と同様に写真蝕刻技術を用いてパターンニングを行なうことにより図示を省略したドレインバスラインに続くドレイン電極 1 9 とソース電極 2 0 を形成する。

#### [0014]

## [0015]

このようにしてTFTは作られているが、補助容量はガラス基板11の上にゲート電極12と同時に形成した補助容量電極13を一方の電極とし、ゲート絶縁膜14と保護膜21を誘電体とし、透明電極8を対極として構成されている。

#### [0016]

こゝで、先に記したように、画面のちらつきや残像を無くするためには補助容量は大きい方が望ましいが、補助容量電極は画素の下に形成してあるために、この電極はむしろ縮小することが好ましい。

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0017]

TFTを使用するアクティブマトリックス形の液晶表示装置においては、TFTのスイッチング動作の際に生じる画面のちらつきや残像を無くするために補助容量を画素の下に設けているが、電気的には静電容量は従来よりも大きいことが望ましい。

#### [0018]

一方、画像表示の面からは補助容量電極の大きさを小さくして有効表示面積(開口率) を向上することが必要である。

【課題を解決するための手段】

#### [0019]

上記の課題は、基板上に薄膜トランジスタと補助容量とをマトリックス状に配置してなる液晶表示装置であって、画素領域の前記薄膜トランジスタが、前記基板上のゲート電極、前記ゲート電極を覆うゲート絶縁膜、前記ゲート絶縁膜上の動作層、前記動作層上部にのみ形成されるソース電極およびドレイン電極、前記ソース電極およびドレイン電極と覆う保護膜とを備え、前記ゲート電極と同じ材料からなり前記ゲート電極と同層に設けられる補助容量電極、前記ソース電極上で接続され、前記ソース電極外周部の側壁とその下部の前記動作層の外周部の側壁と接する画素電極、及び、前記ゲート絶縁膜に連なる絶縁層および前記保護膜に連なる絶縁層を含む誘電体で構成される補助容量を有するように構成された液晶表示装置によって解決することができる。

#### 【発明の効果】

#### [0020]

本発明の実施によって補助容量を小形化して開口率の向上を図り、しかも、補助容量の製造工数を削減した構造を有するアクティブマトリックス形の液晶表示装置を実現することができる。

【発明を実施するための最良の形態】

#### [0021]

先に記したようにアクティブマトリックス形の液晶表示装置においては、高画質化のために補助容量の付加が必要であり、必要とする静電容量はTFTのゲート容量と画素容量

30

20

10

50

から決められる。

[0022]

例えば、ゲート長が 1 0  $\mu$  m , ゲート幅 2 0  $\mu$  m の T F T を用い、 画素電極の大きさを 2 5 5  $\times$  9 0  $\mu$  m とする場合、 画素の下にパターン形成されている補助容量電極として 5 0  $\times$  9 0  $\mu$  m 程度のものが用いられている。

[0023]

こゝで、従来の補助容量の誘電体は図 3 に示すようにゲート絶縁膜 1 4 と保護膜 2 1 との二層構造をとり、厚さが約 7 0 0 n m の S i  $_3$  N  $_x$  を用いて形成されている。

[0024]

そこで、発明者らは誘電体の膜厚を減らすことにより補助容量の小形大容量化を行なう ために、次の何れかの方法をとる。

(1) 補助容量の誘電体をゲート絶縁膜のみで形成する。

(2) 補助容量電極をAlで形成し、誘電体としてはAlを電解酸化して得た酸化アルミニウム皮膜を使用する。

[0025]

本発明は、TFTの駆動が低電圧で行なわれるために補助容量が必ずしも高い絶縁破壊電圧を必要としない点に着目してなされたもので、これにより補助容量電極の大きさを減少することができる。

[0026]

〔実施例1〕(請求項1関連、図1に対応)

図1は本発明の一実施法を示すもので、本発明に係る補助容量とTFTの断面図である

[0027]

すなわち、ガラス基板 1 1 の上にスパッタ法を用いて A 1 を 1 0 0 n m の厚さに形成した後、写真蝕刻技術を用い、ゲート電極 1 2 は、ゲート長 1 0 μ m、ゲート幅 2 0 μ m の寸法で、また、補助容量電極 1 3 は、幅 2 5 μ m、長さ 9 0 μ m の寸法にパターン形成した。

[0028]

[0029]

次に、基板上に $Si_3N_x$ を基板温度を 200 に保つ低温プラズマ CVD法により 350 の nmの厚さに形成して保護膜 21 を形成する。ここまでの工程は、従来の工程と変わらない。

[0030]

すなわち、画素形成部はガラス基板 1 1 の上に補助容量電極 1 3 があり、その上に S i 40  $_3$  N  $_x$  からなるゲート絶縁膜 1 4 と保護膜 2 1 が積層されている。

[0031]

次に、基板上の全域にレジストを被覆した後、画素電極の形成領域のみを窓開けし、次の条件でプラズマエッチングを行い、低温で形成してエッチングされ易い保護膜 2 1 のみを除いた。

[0032]

エッチャント: $CF_4$   $EO_2$  (構成比1:0.1)

総流量 : 5 0 0 s c c m

ガス圧 : 2 0 P a μ波電力 : 8 0 0 W

50

20

次に、スパッタ法によりITOを100nmの厚さに形成し、写真蝕刻技術を用いて透明電極8を形成した。

[0033]

すなわち、従来の補助容量の膜厚が700nmであるため、補助容量電極13として5 0×90μmの面積が必要であったが、膜厚を1/2にすることにより面積を25×90 μmに小形化することができた。その結果、開口率を向上することができる。

[0034]

なお、ゲート絶縁膜をこの例のように単一膜で構成する代わりに複合膜、例えばSi $_3$  N $_x$  / SiО $_2$ で形成されている場合もある。その場合は、保護膜21を除く際に、同時にゲート絶縁膜の上層を除くと効果的である。

[0035]

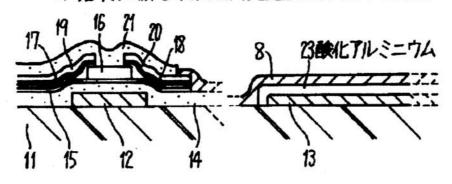

〔実施例2〕(請求項2関連、図2に対応)

図2は本発明の他の実施法を示すもので、本発明に係る別の補助容量とTFTの断面図である。

[0036]

すなわち、ガラス基板 1 1 の上にスパッタ法を用いて A 1 を 5 0 0 n m の厚さに形成した後、写真蝕刻技術を用い、ゲート電極 1 2 はゲート長 1 0  $\mu$  m、ゲート幅 2 0  $\mu$  mの寸法で、また、補助容量電極 1 3 は幅 5  $\mu$  m、長さ 9 0  $\mu$  mの寸法にパターン形成した。

[0037]

[0038]

次に、基板上にSi $_3$ N $_x$ を基板温度を 2 0 0 に保つ低温プラズマ C V D 法により 3 5 0 n m の厚さに形成して保護膜 2 1 を形成する。ここまでの工程は従来の工程と変わらない。

[0039]

すなわち、 画素形成部はガラス基板 1 1 の上に補助容量電極 1 3 があり、この上に S i  $_3$  N  $_x$  よりなるゲート絶縁膜 1 4 と保護膜 2 1 が積層されている。

[0040]

次に、基板上の全域にレジストを被覆した後、画素電極形成領域のみを窓開けし、次の条件で反応性イオンエッチング(略称 R I E )を行い、保護膜 2 1 とゲート絶縁膜 1 4 を除き、 A 1 よりなる補助容量電極 1 3 を露出させた。

[ 0 0 4 1 ]

エッチャント: SF6

流量 : 2 0 0 s c c m

ガス圧 : 2 . 6 P a 電力 : 8 0 0 W

[0042]

こゝで、酸化アルミニウム 2 3 の成長速度は約 1 4 / V であるので、 2 0 0 n m の厚さの A 1 酸化膜が成長している。この比誘電率は約 9 であるために静電容量は従来の厚さが 7 0 0 n m の S i  $_3$  N  $_x$  を用い、補助容量電極の大きさが 5 0 x 9 0  $\mu$  m のものと等価となる。

10

20

30

40

#### [0043]

すなわち、補助容量電極の大きさを 1 / 1 0 に小形化することができ、開口率を向上することができた。

#### [0044]

なお、最近開口率を向上する方法としてゲートバスラインの一部を補助容量電極として 使用する提案もなされているが、この場合にも同様にこの方法を適用することができる。

【図面の簡単な説明】

## [ 0 0 4 5 ]

- 【図1】本発明に係る補助容量とTFTの断面図である。

- 【図2】本発明に係る別の補助容量とTFTの断面図である。

【図3】TFTと画素と補助容量の従来構造を示す断面図である。

- 【図4】アクティブマトリックス形液晶表示装置の等価回路である。

- 【図5】TFTと画素および補助容量の配置を示す正面図である。

- 【符号の説明】

#### [0046]

3 T F T

4 ソース電極

6 補助容量

7 画素

8 透明電極

9、13 補助容量電極

1 1 ガラス基板

1 2 ゲート電極

1 4 ゲート絶縁膜

2 1 保護膜

23 酸化アルミニウム

10

## 【図1】

# 本発明に係る補助容量とTFTの断面図

## 【図2】

## 本発明に係る別の補助容量とTFTの断面図

## 【図3】

## TFTと画素と補助容量の従来構造を示す断面図

## 【図4】

## アクティアマトリックス形液晶表示表置の等価回路

## 【図5】

# TFTと画素および補助容量の配置を示す正面図

## フロントページの続き

F ターム(参考) 2H092 GA11 JA24 JA34 JA37 JA41 JB31 JB56 MA05 MA08 MA17 NA25 PA01 5F110 AA30 BB01 CC07 DD02 EE03 EE37 EE44 FF02 FF03 FF09 FF30 GG02 GG15 GG28 GG29 HK03 HK04 HK09 HK16 HK22 NN04 NN12 NN24 NN35 NN72 NN73

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | JP2004038212A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2004-02-05 |

| 申请号            | JP2003351828                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2003-10-10 |

| [标]申请(专利权)人(译) | 富士通显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 富士通显示器科技公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 廣田四郎<br>間島庭司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 廣田 四郎<br>間島 庭司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/1368 H01L21/336 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G02F1/1368 H01L29/78.612.D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H092/GA11 2H092/JA24 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JB31 2H092/JB56 2H092 /MA05 2H092/MA08 2H092/MA17 2H092/NA25 2H092/PA01 5F110/AA30 5F110/BB01 5F110/CC07 5F110/DD02 5F110/EE03 5F110/EE37 5F110/EE44 5F110/FF02 5F110/FF03 5F110/FF09 5F110 /FF30 5F110/GG02 5F110/GG15 5F110/GG28 5F110/GG29 5F110/HK03 5F110/HK04 5F110/HK09 5F110/HK16 5F110/HK22 5F110/NN04 5F110/NN12 5F110/NN24 5F110/NN35 5F110/NN72 5F110 /NN73 2H192/AA24 2H192/CB05 2H192/CC72 2H192/DA12 2H192/DA63 2H192/EA74 2H192/HA63 2H192/HA86 |         |            |

| 代理人(译)         | 横山纯一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

要解决的问题:简化有源矩阵型液晶显示装置的辅助电容的制造工艺。 ŽSOLUTION:液晶显示装置包括以矩阵形式排列的薄膜晶体管和辅助电容,像素区域中的薄膜晶体管在基板上设置有栅电极,栅极绝缘膜覆盖栅电极,栅极绝缘膜上的操作层,操作层上的源电极和漏电极,以及覆盖源电极和漏电极的保护膜,并且具有由相同材料制成的辅助电容电极组成的辅助电容栅电极与栅电极设置在同一层中,像素电极连接在源电极上并与源电极的外圆周部分的侧壁和外圆周部分的侧壁接触。在其下方的操作层,以及包括与栅极绝缘膜和绝缘层连接的绝缘层的电介质与保护膜一起使用。Ž