(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2001 - 215467

(P2001 - 215467A)

(43)公開日 平成13年8月10日(2001.8.10)

| (51) Int.CI <sup>7</sup> | 識別記号   | F I           | テ-マコード <sup>*</sup> (参考) |

|--------------------------|--------|---------------|--------------------------|

| G 0 2 F 1/133            | 550    | G 0 2 F 1/133 | 550 2 H 0 9 2            |

|                          | 1/1368 | G 0 9 G 3/20  | 622 C 2 H 0 9 3          |

| G 0 9 G 3/20             | 622    |               | 3/36 5 C 0 0 6           |

|                          | 3/36   | G 0 2 F 1/136 | 500 5 C 0 8 0            |

審査請求 未請求 請求項の数 30 L (全 5 数)

(21)出願番号 特願2000 - 23669(P2000 - 23669)

(22)出願日 平成12年2月1日(2000.2.1)

(71)出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(72)発明者 千田 耕司

大阪府門真市大字門真1006番地 松下電器

産業株式会社内

(72)発明者 南野 裕

大阪府門真市大字門真1006番地 松下電器

産業株式会社内

(74)代理人 100097445

弁理士 岩橋 文雄 (外2名)

最終頁に続く

(54)【発明の名称】 液晶表示装置とその駆動方法

(57)【要約】

【課題】 本発明は、いわゆるAV機器や、OA機器などに適用されるアクティブマトリックス方式の液晶表示パネルに関するものであり、特に、シリコンTFTによる走査回路を内蔵した、アクティブマトリックス方式の液晶表示パネルに関するもので、ゲートパルス電位Vgをt0時に立ち下げるに起因した画質不良が発生しない液晶表示装置とその駆動方法の提供を目的とする。

【解決手段】 垂直走査回路でのゲート線に印加するパルスの出力アンプを形成するPチャネルTFTとnチャネルTFTで、前記PチャネルTFTの出力能力を前記nチャネルTFTの出力能力の50%以下にする。

本発明の一実施例での画素部での電位変化図

**【特許請求の範囲】**

【請求項1】基板上に、走査信号を伝達する複数のゲート線と、画像信号を伝達する複数の信号線とが設けられ、且つ、前記複数のゲート線と前記複数の信号線との各交差点に対応して、ゲート線及び信号線に接続された画素トランジスタと、前記画素トランジスタを介して、前記信号線に接続された画素電極と、共通電極と、垂直走査回路と、水平走査回路とを備えたアクティブマトリックス型液晶表示パネルにおいて、前記ゲート線に印加するパルスの立ち下げ時間を前記パルスの立上げ時間の2倍以上に長くすることを特徴とする液晶表示装置の駆動方法。

【請求項2】前記ゲート線に印加するパルスの立ち下げ時間を、 $0.2\mu s$ から $10\mu s$ の間の時間とすることを特徴とする請求項1に記載の液晶表示装置の駆動方法。

【請求項3】請求項1または2に記載の駆動方法を実現する液晶表示装置であって、垂直走査回路でのゲート線に印加するパルスの出力アンプを形成するPチャネルTFTとnチャネルTFTにおいて、前記PチャネルTFTの出力能力が前記nチャネルTFTの出力能力の50%以下であることを特徴とする液晶表示装置。

**【発明の詳細な説明】**

**【0001】**

【発明の属する技術分野】本発明は、いわゆるAV(Audio Visual)機器や、OA(Office Automation)機器などに適用されるアクティブマトリックス方式の液晶表示パネルに関するものであり、特に、ポリシリコンTFTによる走査回路を内蔵した、アクティブマトリックス方式の液晶表示パネルに関するものである。

**【0002】**

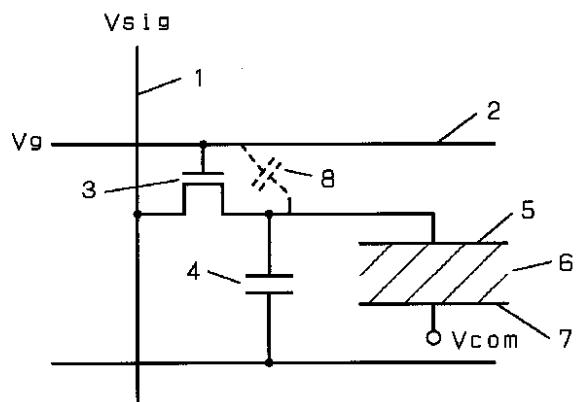

【従来の技術】図3は、ポリシリコンTFTによる走査回路を内蔵した、アクティブマトリックス方式の液晶表示パネルの画素の回路図である。図3において、1は信号線、2はゲート線、3は画素トランジスタ、4は付加容量、5は画素電極、6は液晶、7は共通電極、8はゲート線と画素トランジスタのドレイン間の寄生容量である。

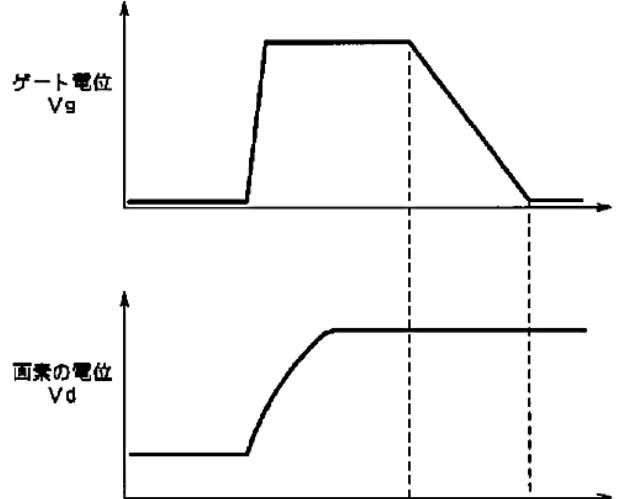

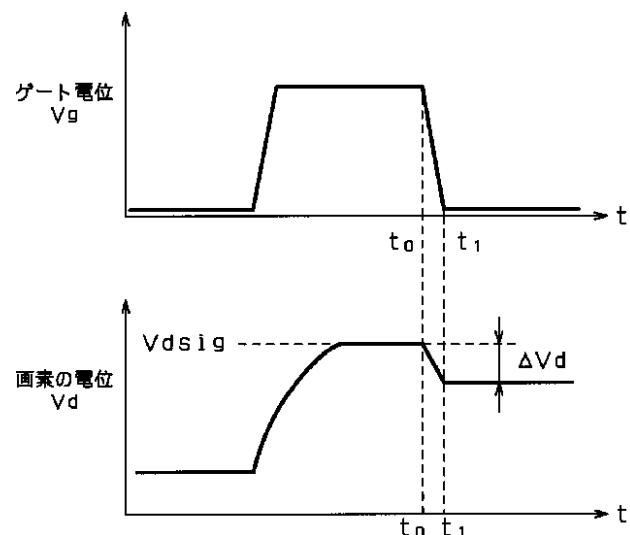

【0003】図2は、従来の液晶表示パネルの画素の回路でのゲートパルス電位Vgと画素電極電位Vdの時間的变化を示した図である。図2に示すように、ゲートパルス電位Vgをt0時に立ち下げるとき、ゲート線と画素トランジスタのドレイン間の寄生容量8により、画素電極電位Vdは、t1時のように下がる。その結果、画素へ書き込むべき画素電極電位Vdsigが、Vdだけ書き込み不足になり、それが、液晶表示ではザラザラした表示不良になる。

**【0004】**

【発明が解決しようとする課題】この様な従来の駆動方法で、ゲートパルス電位Vgをt0時に立ち下げるとき、ゲート線と画素トランジスタのドレイン間の寄生容量8によ

10

20

30

40

50

り、画素電極電位Vdは下がり、その結果、画素へ書き込むべき画素電極電位Vdsigが、Vdだけ書き込み不足になり、それが、液晶表示ではザラザラした表示不良になるという課題がある。

【0005】本発明は、上記課題を解決するもので、ゲートパルス電位Vgをt0時に立ち下げるときに起因した画質不良が発生しない液晶表示装置とその駆動方法の提供を目的とする。

**【0006】**

【課題を解決するための手段】上記目的を達成するためには、本発明は、垂直走査回路でのゲート線に印加するパルスの出力アンプを形成するPチャネルTFTとnチャネルTFTで、前記PチャネルTFTの出力能力を前記nチャネルTFTの出力能力の50%以下にすることで、ゲート線に印加するパルスの立ち下げ時間をパルスの立上げ時間の2倍以上に長くすることを特徴とするものである。

【0007】本発明のアクティブマトリックス型液晶表示パネル及びその駆動方法は、上記の構成により、ゲートパルス電位Vgを立ち下げるときに起因した画質不良が発生しない。

**【0008】**

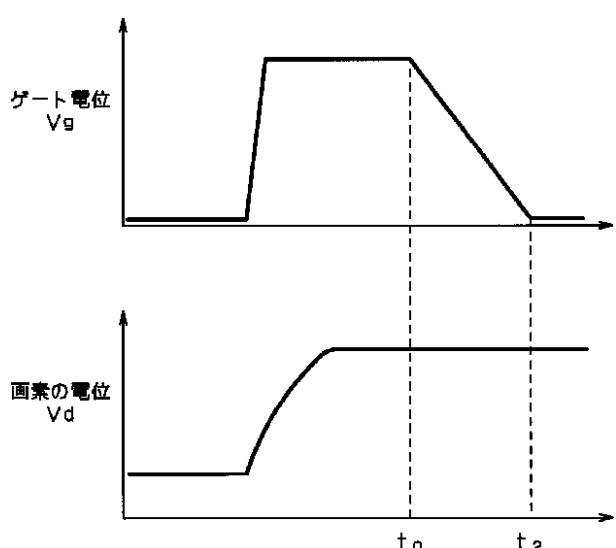

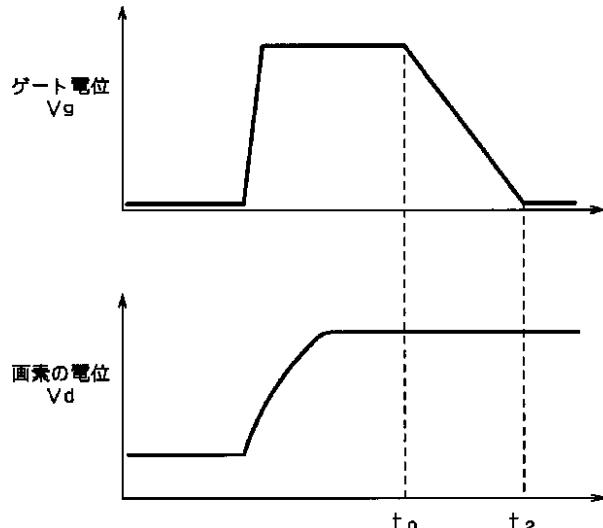

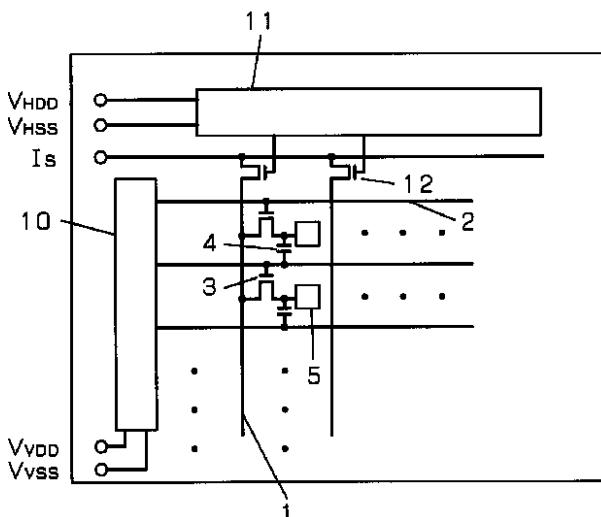

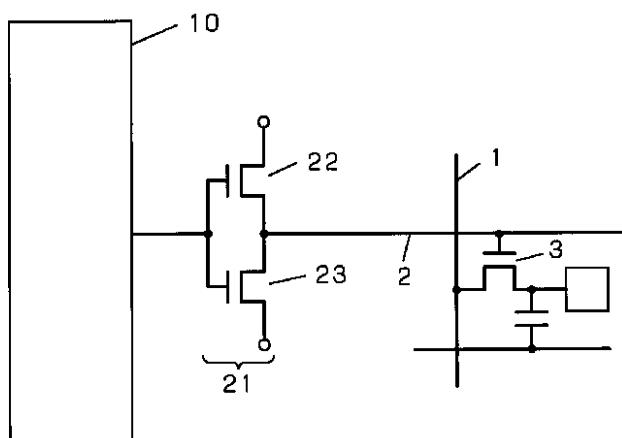

【発明の実施の形態】本発明の一実施例を図1、図3、図4、図5、を参照して説明する。なお、図1は本発明の一実施例に係るアクティブマトリックス型液晶表示パネルにおいて、画素の回路でのゲートパルス電位Vgと画素電極電位Vdの時間的变化を示した電位変化図である。また、図3は、ポリシリコンTFTによる走査回路を内蔵した、アクティブマトリックス方式の液晶表示パネルの画素の回路図である。図3において、1は信号線、2はゲート線、3は画素トランジスタ、4は付加容量、5は画素電極、6は液晶、7は共通電極である。さらに、図4は本発明の一実施例に係るアクティブマトリックス型液晶表示パネルの回路構成図である。図4において、10は垂直走査回路、11は水平走査回路、12はアナログスイッチである。図5は本発明の一実施例に係る垂直走査回路の回路の例である。

【0009】上記図面を用いて、図1に示すt0で電源を立ち下げる駆動方法について以下に説明する。図1に示すように、ゲートパルス電位Vgをt0時に立ち下げるが、図2に示す従来に比べて、立ち下げる時間を長くする。例えば、立ち下げ時間をパルスの立上げ時間の2倍以上とする。なお、通常の液晶表示駆動で、1H期間が $60\mu s$ になる場合には、立ち下げ時間を、 $0.2\mu s$ から $10\mu s$ 程度にする。その結果従来に比べて、ゲート線と画素トランジスタのドレイン間の寄生容量8に起因した電位変化を小さく出来るため、画素電極電位Vdは、図1のt2時に示すようにほとんど下がらない。

【0010】なお、上記で説明した本発明の一実施例のゲートパルス電位Vgを実現するための垂直走査回路の一実施例の回路を、図5に示す。図5において、垂直走査

回路10からの出力アンプ21をPチャネルTFT22とnチャネルTFT23で、PチャネルTFT22の出力能力をnチャネルTFT23の出力能力の50%以下にすることで、上記で説明した本発明の一実施例の立ち下げる時間を長くしたゲートパルス電位 $V_g$ を実現できる。

#### 【0011】

【発明の効果】以上の実施例から明らかなように本発明によれば、垂直走査回路でのゲート線に印加するパルスの出力アンプを形成するPチャネルTFTとnチャネルTFTで、PチャネルTFTの出力能力をnチャネルTFTの出力能力の50%以下にすることで、ゲート線に印加するパルスの立ち下げ時間をパルスの立上げ時間の2倍以上に長くすることで、ゲートパルス電位 $V_g$ を立ち下げるときに起因した画質不良が発生しないことができる。

#### 【図面の簡単な説明】

#### 【図1】本発明の一実施例での画素部での電位変化図

#### 【図2】従来の一実施例での画素部での電位変化図

#### 【図3】画素の等価回路図

【図1】

本発明の一実施例での画素部での電位変化図

【図4】本発明の一実施例による液晶表示パネルの回路構成図

【図5】本発明の一実施例による液晶表示パネルの垂直走査回路構成図

#### 【符号の説明】

- |    |             |

|----|-------------|

| 1  | 信号線         |

| 2  | ゲート線        |

| 3  | 画素トランジスタ    |

| 4  | 付加容量        |

| 10 | 5 画素電極      |

| 6  | 液晶          |

| 7  | 共通電極        |

| 10 | 10 垂直走査回路   |

| 11 | 11 水平走査回路   |

| 12 | 12 アナログスイッチ |

| 21 | 21 出力アンプ    |

| 22 | 22 PチャネルTFT |

| 23 | 23 nチャネルTFT |

【図2】

従来の一実施例での画素部での電位変化図

【図3】

- 1 信号線

2 ゲート線

3 画素トランジスタ

4 付加容量

5 画素電極

6 液晶

7 共通電極

8 寄生容量

- 1 信号線

2 ゲート線

3 画素トランジスタ

4 付加容量

5 画素電極

10 垂直走査回路

11 水平走査回路

12 アナログスイッチ

Is 画像信号入力端子

【図4】

- V<sub>HDD</sub> 水平走査電源

(ハイレベル) 端子

V<sub>HSS</sub> 水平走査電源

(ロウレベル) 端子

V<sub>VDD</sub> 垂直走査電源

(ハイレベル) 端子

V<sub>VSS</sub> 垂直走査電源

(ロウレベル) 端子

画素の等価回路図

本発明の一実施例による液晶表示パネルの回路構成図

【図5】

- 1 信号線

2 ゲート線

3 画素トランジスタ

10 垂直走査回路

21 出力アンプ

22 PチャネルTFT

23 NチャネルTFT

本発明の一実施例による垂直走査回路構成図

## フロントページの続き

(72)発明者 河島 秀弥

大阪府門真市大字門真1006番地 松下電器

産業株式会社内

F ターム(参考) 2H092 JA24 JA37 JB31 JB69 KA04

NA01

2H093 NA16 NB11 NC34 ND01

5C006 AA01 AF50 BB16 BC03 BC12

BC20 BF25 FA22 FA37 GA03

5C080 AA10 BB05 DD05 FF11 JJ02

JJ03 JJ04

|             |                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 液晶显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号     | <a href="#">JP2001215467A</a>                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2001-08-10 |

| 申请号         | JP2000023669                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2000-02-01 |

| 申请(专利权)人(译) | 松下电器产业有限公司                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人      | 千田耕司<br>南野裕<br>河島秀弥                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人         | 千田 耕司<br>南野 裕<br>河島 秀弥                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号      | G09G3/36 G02F1/133 G02F1/136 G02F1/1368 G09G3/20                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F1分类号       | G02F1/133.550 G09G3/20.622.C G09G3/36 G02F1/136.500 G02F1/1368                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-Term分类号   | 2H092/JA24 2H092/JA37 2H092/JB31 2H092/JB69 2H092/KA04 2H092/NA01 2H093/NA16 2H093/NB11 2H093/NC34 2H093/ND01 5C006/AA01 5C006/AF50 5C006/BB16 5C006/BC03 5C006/BC12 5C006/BC20 5C006/BF25 5C006/FA22 5C006/FA37 5C006/GA03 5C080/AA10 5C080/BB05 5C080/DD05 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 2H192/AA24 2H192/DA12 2H192/DA73 2H192/FB02 2H192/GD61 2H193/ZA04 2H193/ZA06 2H193/ZB02 2H193/ZB18 2H193/ZF22 |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

有源矩阵型液晶显示面板技术领域本发明涉及一种应用于所谓的AV设备，OA设备等的有源矩阵型液晶显示面板，特别是涉及一种通过多晶硅TFT具有扫描电路的有源矩阵型液晶显示面板。发明内容因此，本发明的目的在于提供一种液晶显示装置及其驱动方法，在该液晶显示装置及其驱动方法中，不会发生由于在t0时栅极脉冲电位Vg的下降而引起的画质不良。形成施加到垂直扫描电路中的栅极线的脉冲的输出放大器的P沟道TFT和n沟道TFT，并且将P沟道TFT的输出能力设定为n沟道TFT的输出能力的50%以下。要做。