(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-316670

(P2007-316670A)

(43) 公開日 平成19年12月6日(2007.12.6)

(51) Int.CI.

G02F 1/1368 (2006.01)

G09F 9/30 (2006.01)

F 1

G02F 1/1368

G09F 9/30 338

テーマコード(参考)

2 H 0 9 2

5 C 0 9 4

審査請求 有 請求項の数 2 O L (全 20 頁)

|            |                                     |          |                                                          |

|------------|-------------------------------------|----------|----------------------------------------------------------|

| (21) 出願番号  | 特願2007-212547 (P2007-212547)        | (71) 出願人 | 303018827<br>N E C 液晶テクノロジー株式会社<br>神奈川県川崎市中原区下沼部 1753 番地 |

| (22) 出願日   | 平成19年8月17日 (2007.8.17)              | (74) 代理人 | 100109313<br>弁理士 机 昌彦                                    |

| (62) 分割の表示 | 特願2002-268952 (P2002-268952)<br>の分割 | (74) 代理人 | 100124154<br>弁理士 下坂 直樹                                   |

| 原出願日       | 平成14年9月13日 (2002.9.13)              | (74) 代理人 | 100111637<br>弁理士 谷澤 靖久                                   |

|            |                                     | (72) 発明者 | 西郷 伸吾<br>神奈川県川崎市中原区下沼部 1753 番地<br>N E C 液晶テクノロジー株式会社内    |

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】信号線の少なくとも一部を層間絶縁膜を介して共通電極で被覆するようにした横方向電界型の液晶表示装置において、信号線と共に電極との間のショートを低減する。

【解決手段】表示部が走査線 1 1 及び信号線 1 2 により区画されて画素が設けられるが、共通配線と共に電極を接続するコンタクトホール 2 7 を画素毎に形成せず、間引きして千鳥状に配置し、例えば 4 画素毎に設ける構成とし、信号線と共に電極との間のショートを低減する。

【選択図】図4

## 【特許請求の範囲】

## 【請求項 1】

基板上に薄膜トランジスタと、前記薄膜トランジスタに接続され縦横に交差する複数の走査線及び信号線と、前記走査線と同層に形成される共通配線とを有し、前記薄膜トランジスタ上に形成される層間絶縁膜を介して、前記共通配線に接続され、前記信号線上の少なくとも一部を被覆するように形成された共通電極と、前記薄膜トランジスタに接続される画素電極との間に、前記基板と概ね平行な電界を発生する横電界型液晶表示装置において、前記複数の走査線及び信号線により区画されて規定される複数の画素に対し、前記共通配線と前記共通電極を接続するコンタクトホールが、複数画素に1つの割合で形成されており、精細度がQ S X G A以上であることを特徴とする液晶表示装置。

10

## 【請求項 2】

コンタクトホールが形成される1つの画素を中心にして他のコンタクトホールが形成される他の画素を見た場合に、他の画素は縦横方向には少なくとも1画素を空けて配置されることを特徴とする請求項1に記載の液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、液晶表示装置に関し、特に、信号線の少なくとも一部を層間絶縁膜を介して共通電極で被覆するようにした横方向電界型の液晶表示装置に関する。

## 【背景技術】

## 【0002】

画素電極を駆動制御するスイッチング素子として、薄膜トランジスタ(thin film transistor:TFT)やMIM(metal insulator metal)を用いた透過型の液晶表示装置が広く用いられている。特に、モニター用途として、プラウン管並の広視野角を実現できる横方向電界型(in plane switching:IPS)の液晶表示装置が用いられている。

20

## 【0003】

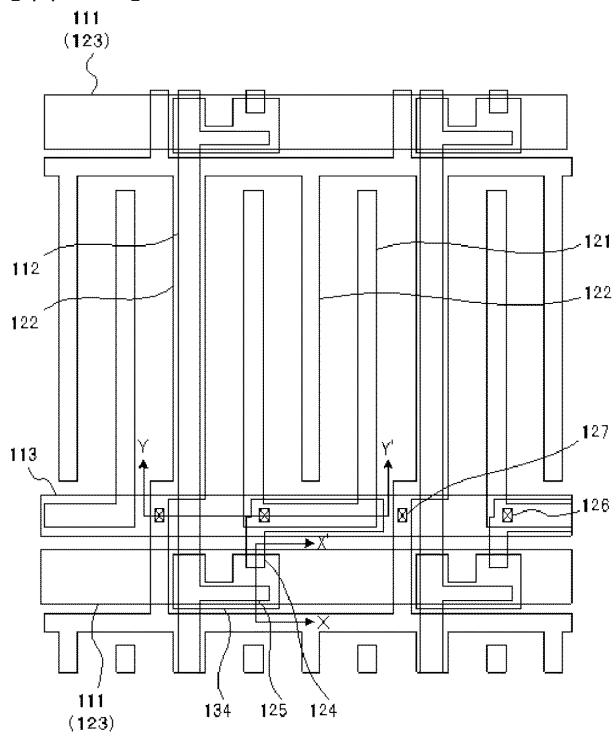

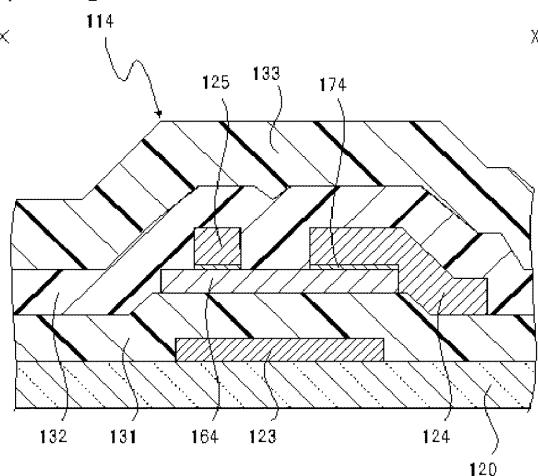

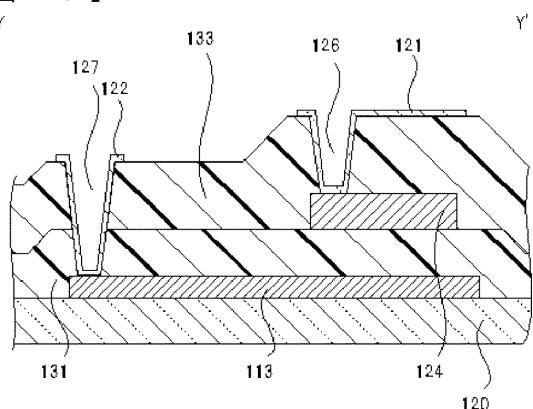

図26～図28は、特許文献1に開示されているTFTを用いた横方向電界型液晶表示装置におけるアクティブマトリクス基板の1画素部分の構成を示し、図26は平面図、図27は図26のX-X'線、図28は図26のY-Y'線に沿う断面図である。この横方向電界型液晶表示装置のアクティブマトリクス基板には、複数の画素電極と共に電極が櫛歯状に対向して形成され、この電極間に基板と概ね平行な電界を発生させ、液晶分子の配列を制御している。

30

## 【0004】

図26に示すように、走査信号を供給する走査線111と表示信号を供給する信号線112が直交して、また、共通電極122に電位を与える共通配線113が走査線111と平行に設けられている。一方、共通電極122と画素電極121が櫛歯状に対向して設けられ、走査線111と信号線112の交差部には、走査線111、信号線112、画素電極121に接続されてTFT114が設けられている。

40

## 【0005】

TFT114のゲート電極123は走査線111の一部として設けられ、ドレイン電極125は信号線112に接続され、ソース電極124はコンタクトホール126を介して画素電極121に、共通配線113はコンタクトホール127を介して共通電極122に接続されている。また、信号線112の少なくとも一部が共通電極122により覆われるように配置されている。

## 【0006】

図27に示すように、透明絶縁性基板120の上には、ゲート電極123、ゲート絶縁膜131、島状の半導体層134が設けられている。更に、半導体層134(アモルファスシリコン(a-Si)層164、n+型アモルファスシリコン(n+型a-Si)層174)を覆い、ソース電極124及びドレイン電極125が分離して設けられ、TFT1

50

14が形成されている。更に、TFT114を覆って、層間絶縁膜（保護膜132と有機絶縁膜133）が設けられている。また、図28に示すように、有機絶縁膜133に形成されたコンタクトホール126と、有機絶縁膜133及びゲート絶縁膜131に形成されたコンタクトホール127とを介して、それぞれ画素電極121はソース電極124に、共通電極122は共通配線113に接続されている。

#### 【0007】

次に、上記構成を有するアクティブマトリクス基板の製造工程を説明する。先ず、ガラス等の透明絶縁性基板120上に、Cr-Mo合金膜からなる金属膜を成膜し、パターニングしてゲート電極123、走査線111、共通配線113を形成する。次に、ゲート絶縁膜131、a-Si層164、n+型a-Si層174を順次成膜した後、パターニングして半導体層134を形成する。次に、Cr-Mo合金膜からなる金属膜を成膜し、ターニングしてソース電極124、ドレイン電極125、信号線112を形成し、これらをマスクとして、n+型a-Si層174をエッチング除去し、チャネルを形成する。

#### 【0008】

続いて、窒化シリコン膜からなる保護膜132を成膜し、パターニングする。次に、感光性の有機絶縁膜133を塗布し、パターニングした後、これをマスクとして、更にゲート絶縁膜131をパターニングし、コンタクトホール126、127を開口する。その後、有機絶縁膜133を覆って、インジウムスズ酸化膜（ITO）からなる透明導電膜を成膜し、パターニングして共通電極122、画素電極121を形成する。このようにして、共通電極122と共に配線113、画素電極121とソース電極124の接続がとられる。

#### 【0009】

このように、層間絶縁膜の一部に、比誘電率が低い有機絶縁膜133を用いるのは、開口率を向上するために共通電極122と信号線112を一部オーバーラップさせたとき、信号線と共に電極の容量結合を小さくし、クロストークを抑制するためである。また、アクティブマトリクス基板の平坦度を向上して、対向基板とのギャップのばらつきを低減し、輝度の均一性を向上させている。

#### 【0010】

なお、層間絶縁膜に有機絶縁膜を用いない場合は、窒化シリコン膜からなる保護膜132を厚く形成することで代用している。このときは、コンタクトホール126、127は1回のフォトリソ工程で開口される。

#### 【0011】

【特許文献1】WO98/47044号公報（第8-18頁、図1、3、4）

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0012】

しかしながら、前述したような信号線の少なくとも一部が層間絶縁膜を介して共通電極で被覆されたようにした横方向電界型液晶表示装置では、その構造上、層間絶縁膜にピンホールが発生すると、信号線と共に電極がショートし、縦ライン欠陥が発生しやすいという製造歩留上の課題がある。

#### 【0013】

本発明者の実験によると、信号線のパターニング工程で、フォトレジスト等の異物により信号線112からコンタクトホール127にかけて、信号線の金属膜のパターニング不良が発生し、コンタクトホール127を介して信号線112と共に電極122がショートすることが確認された。この現象は、特に、画素ピッチが狭くなる高精細パネルで顕著になることが判明した。

#### 【0014】

また、層間絶縁膜に有機絶縁膜を用いず、窒化シリコン膜のような無機膜のみで形成した場合、コンタクトホール126、127の開口工程で、少なくともドライエッティングを用いて開口を行うと、フォトレジストの異物や欠陥部分でプラズマが集中し、結果的に層

間絶縁膜がピンホール状にエッティングされ、このピンホールを介して信号線 112 と共に通電極 122 がショートすることが確認された。

#### 【0015】

本発明の目的は、信号線の少なくとも一部が層間絶縁膜を介して共通電極で被覆されるようにした横方向電界型液晶表示装置において、信号線と共に通電極間のショートによる縦ライン欠陥を低減し、製造歩留を向上することのできる液晶表示装置を提供することである。

#### 【課題を解決するための手段】

#### 【0016】

上記目的を達成するため、本発明に係る液晶表示装置は、基板上に薄膜トランジスタと、前記薄膜トランジスタに接続され縦横に交差する複数の走査線及び信号線と、前記走査線と同層に形成される共通配線とを有し、前記薄膜トランジスタ上に形成される層間絶縁膜を介して、前記共通配線に接続され、前記信号線上の少なくとも一部を被覆するように形成された共通電極と、前記薄膜トランジスタに接続される画素電極との間に、前記基板と概ね平行な電界を発生する横電界型液晶表示装置において、前記複数の走査線及び信号線により区画されて規定される複数の画素に対し、前記共通配線と前記共通電極を接続するコンタクトホールが、複数画素に1つの割合で形成されており、精細度が Q S X G A 以上であることを特徴とする。

#### 【0017】

また、この液晶表示装置において、コンタクトホールが形成される1つの画素を中心にして他のコンタクトホールが形成される他の画素を見た場合に、他の画素は縦横方向には少なくとも1画素を空けて配置されることを特徴とする。

#### 【発明の効果】

#### 【0018】

以上のような構成にすることにより、信号線の少なくとも一部が層間絶縁膜を介して共通電極で被覆されるようにした横方向電界型液晶表示装置において、共通配線と共に通電極を接続するコンタクトホールを介して、信号線と共に通電極がショートする確率を低減でき、製造歩留を向上することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

以下、この発明の実施の形態について図面を参照して説明する。

#### 【0020】

##### (第1の実施の形態)

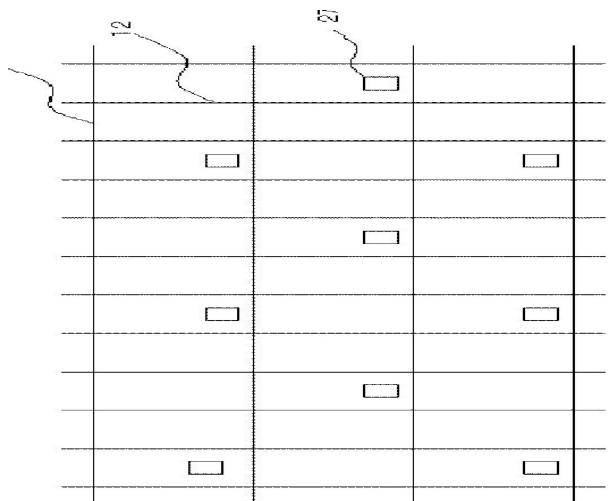

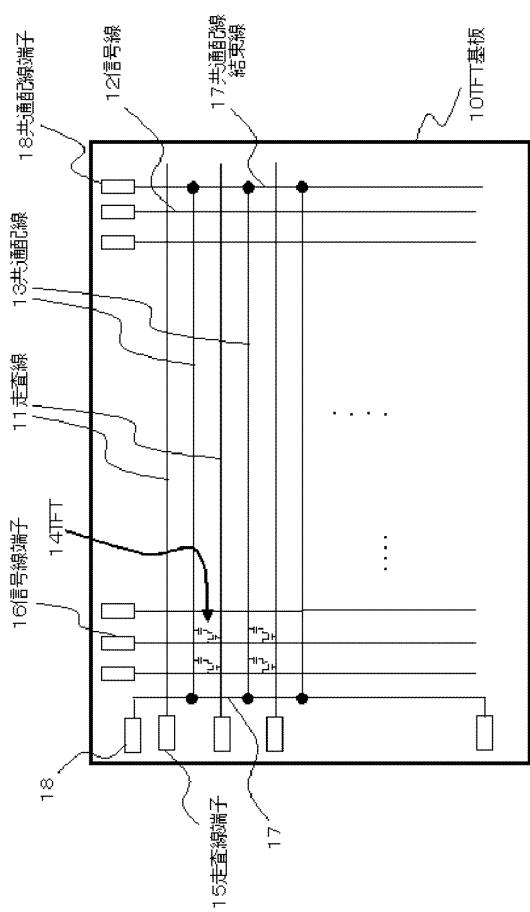

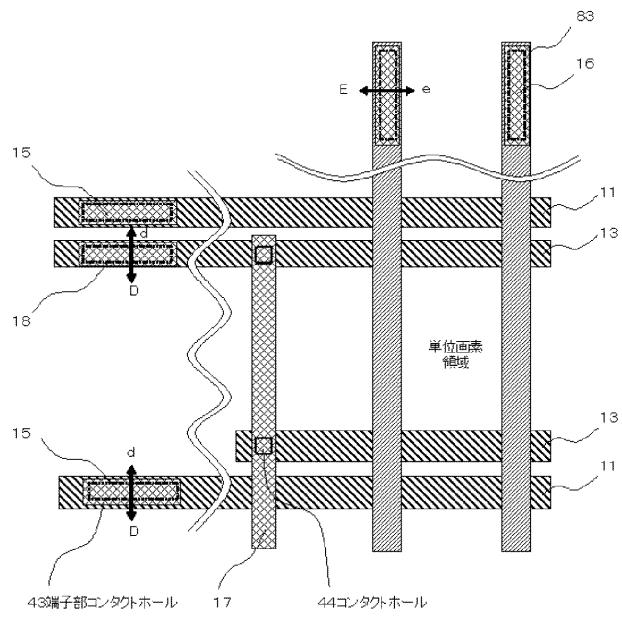

図1は、本発明の第1の実施の形態に係る横方向電界型液晶表示装置におけるTFT基板の構成を概念的に示す平面図である。図1に示すように、TFT基板10の対向基板側面には、複数の走査線11と信号線12が直交して設けられ、また、隣接する走査線11の間に共通配線13が平行に設けられている。走査線11と信号線12の交差部分には、TFT14が形成され、これらがマトリクス状に配置されている。走査線11と信号線12の端部には、それぞれ走査線端子15、信号線端子16が設けられ、外部駆動回路からの駆動信号を入力するようになっている。

#### 【0021】

共通配線13は、液晶を交流駆動するための基準となる共通の電位を与えるために相互に結束されており、各共通配線13の両端がそれぞれ接続された共通配線結束線17が、TFT基板10の短辺の両側に1本ずつ設けられている。この共通配線13と、TFT14のソース電極に接続された画素電極との間で容量が形成される。各共通配線結束線17の端部には、それぞれ共通配線端子18が設けられている。

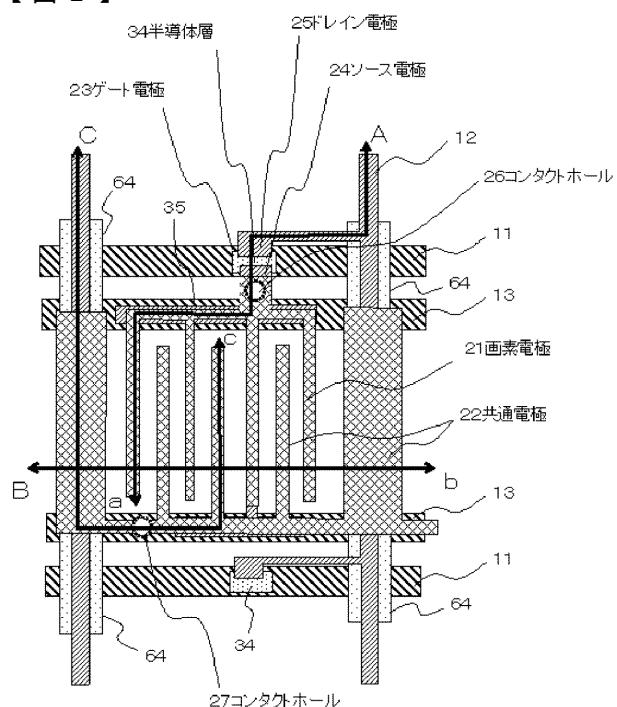

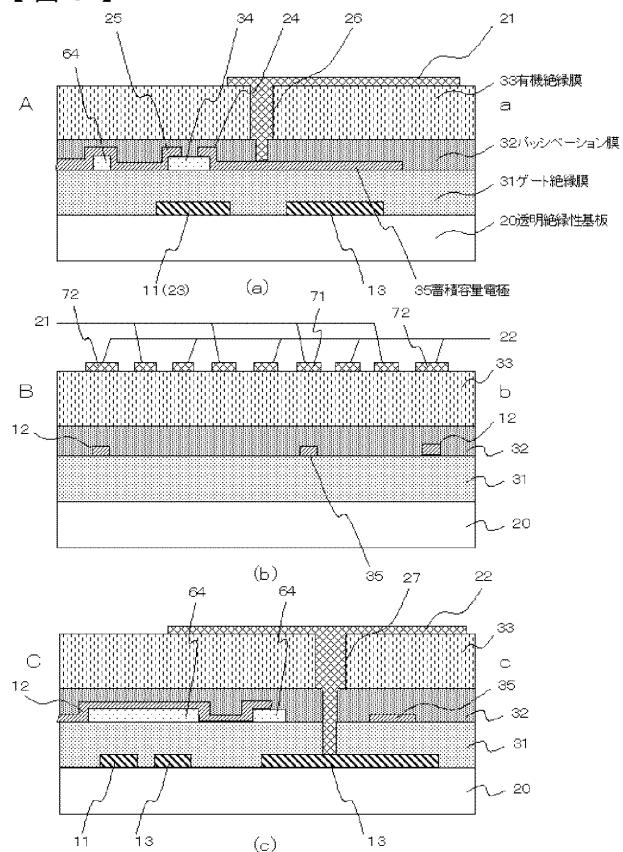

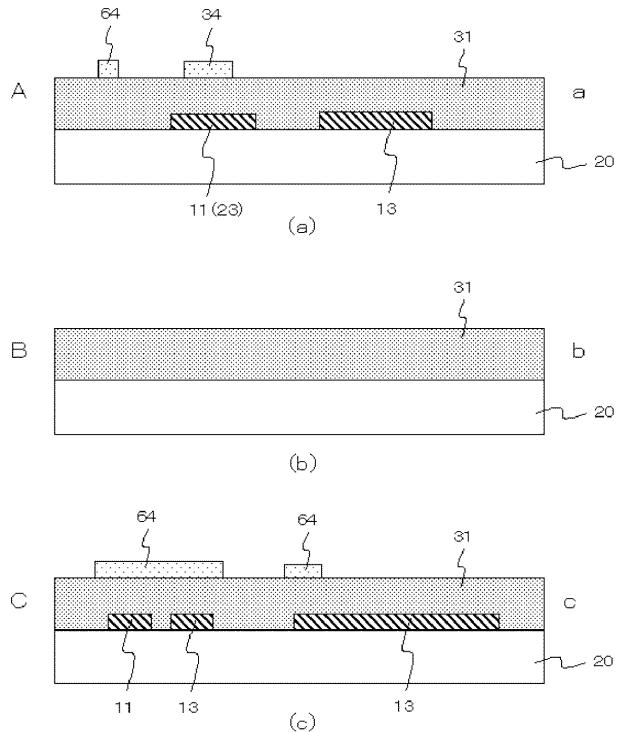

#### 【0022】

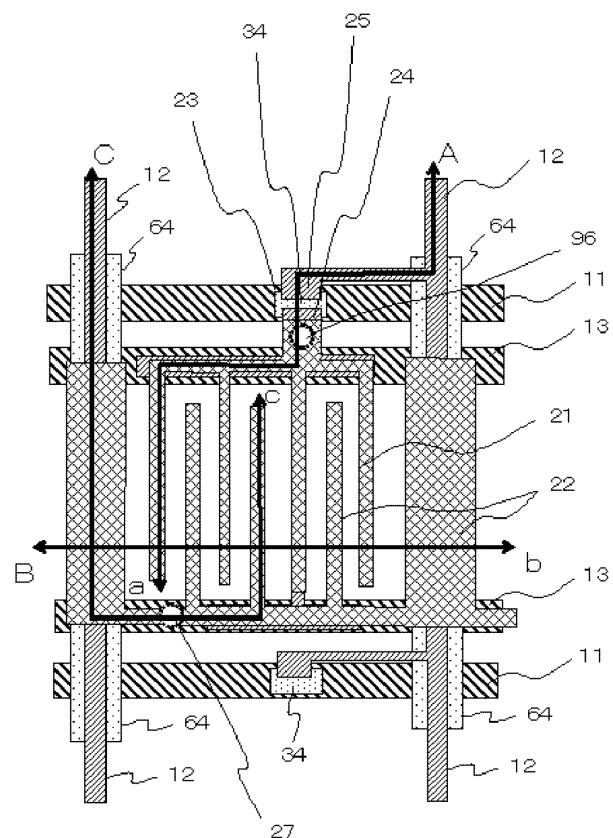

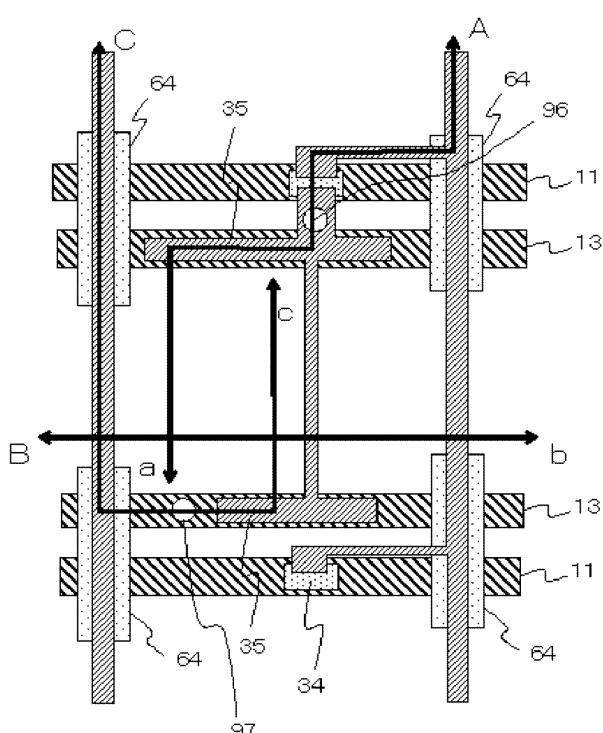

図2は、図1のTFT基板の1画素部を拡大して示す平面図、図3は、図2のA-a線、B-b線、C-c線に沿う断面図である。図2に示すように、TFT基板上に形成される走査線11と信号線12の交差区画には、櫛歯状に形成された画素電極21と共に通電極

10

20

30

40

50

22が交互に配置され、この電極間にTFT基板10と概ね平行な電界を発生させ、液晶分子の配列を制御している。また、この画素電極21と共に電極22は、図3に示すように、TFT14上に形成されたパッシベーション膜32と有機絶縁膜33からなる層間絶縁膜上に設けられている。

#### 【0023】

TFT14は、本実施形態では、逆スタガ型の薄膜トランジスタの例を示しており、TFT14のゲート電極23は走査線11の一部として形成され、ソース電極24には、層間絶縁膜に形成された画素電極用のコンタクトホール26を介して画素電極21が、共通配線13には、層間絶縁膜及びゲート絶縁膜31に形成された共通電極用のコンタクトホール27を介して共通電極22がそれぞれ接続され、ドレイン電極25には信号線12が接続されている。このTFT14には、走査線11、ゲート電極23を通して走査信号が、信号線12、ドレイン電極25を通して表示信号が入力され、画素電極21への電荷の書き込みが行われる。また、共通配線13と蓄積容量電極35の間で蓄積容量が形成される。

#### 【0024】

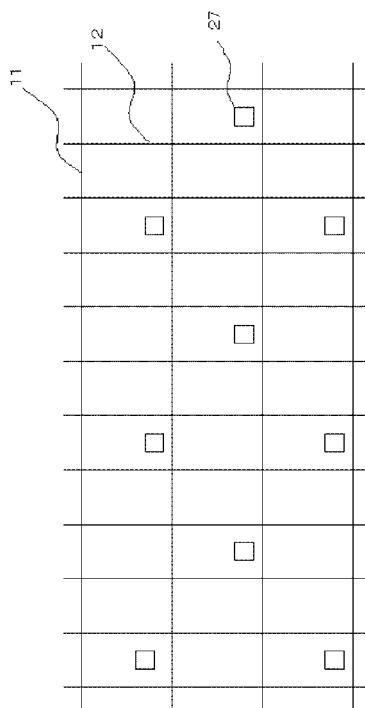

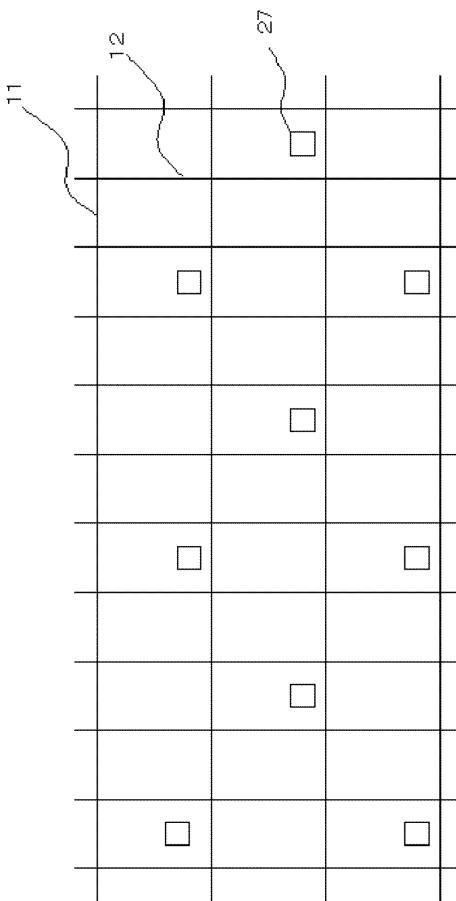

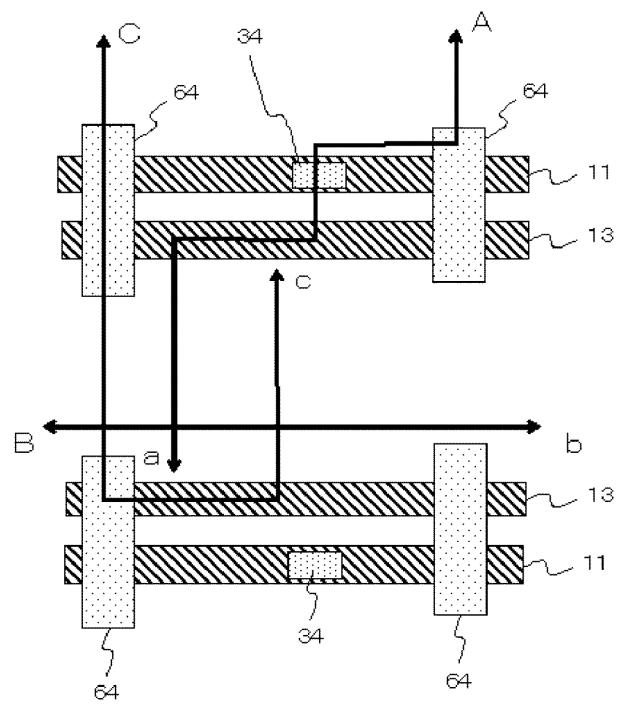

図4は、共通電極用のコンタクトホール27の配置を示す模式平面図である。図4に示すように、コンタクトホール27は、すべての画素には形成されず、千鳥状に間引きされて設けられている。ここでは、画素数に対して1/4に間引きされている例を示した。なお、画素電極用のコンタクトホール26は勿論すべての画素に設けられている。

#### 【0025】

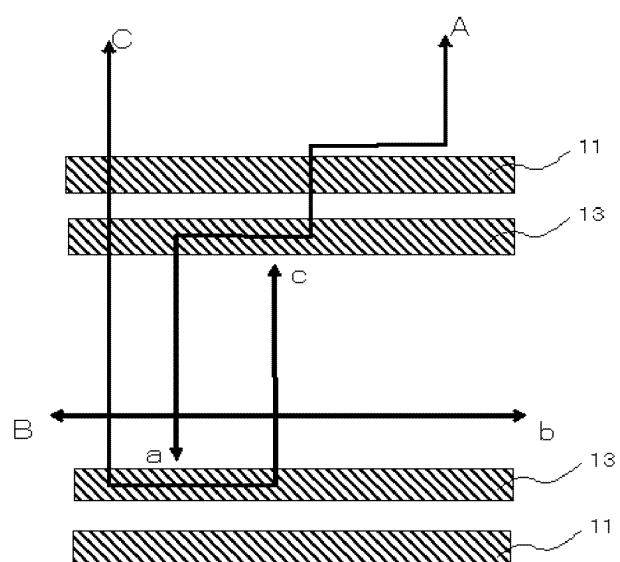

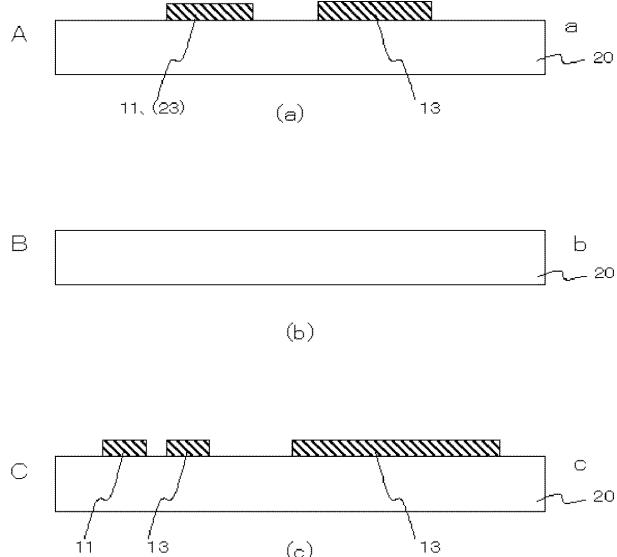

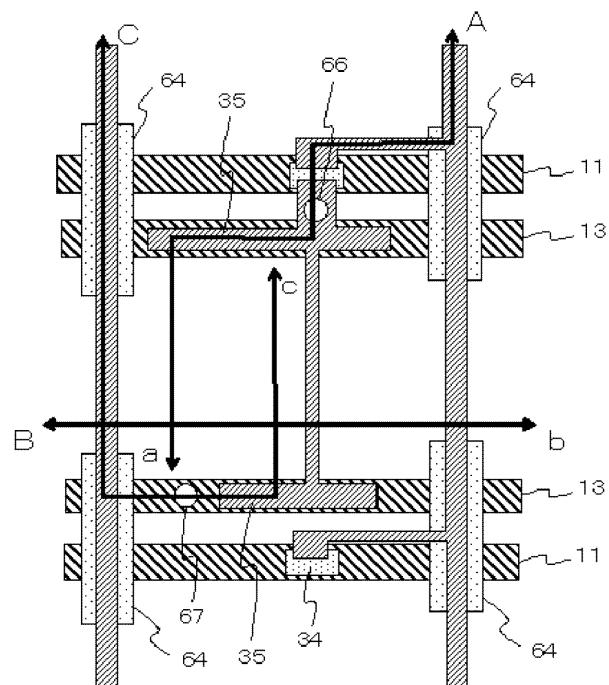

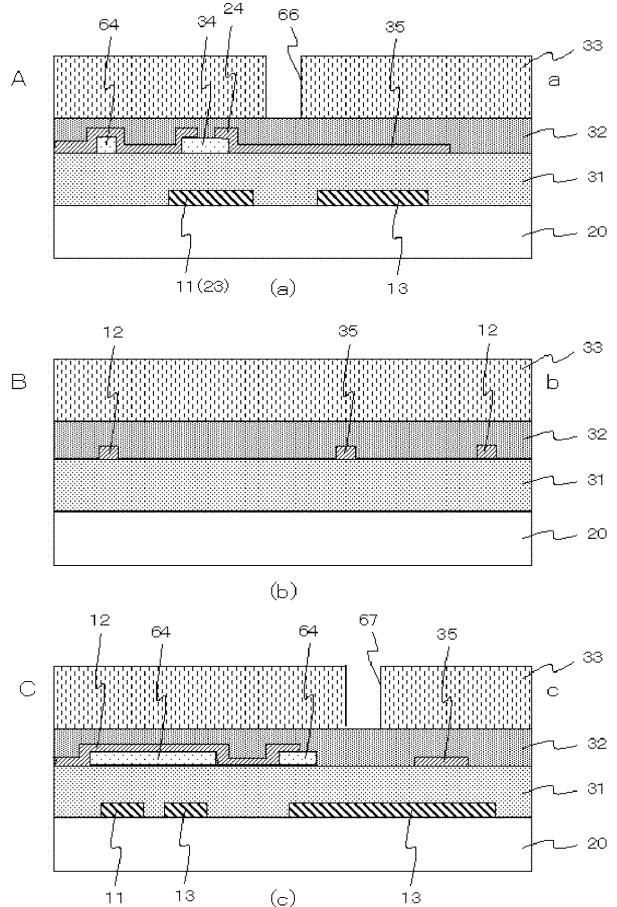

次に、第1の実施の形態のTFT基板の製造方法を説明する。図5、図7、図9、図11、図13、図2は、1画素部分の各製造工程を示す平面図、図6、図8、図10、図12、図14、図3は、それぞれ図5、図7、図9、図11、図13、図2のA-a線((a)図)、B-b線((b)図)、C-c線((c)図)に沿う工程断面図である。ここで、A-a線に沿う断面部はTFT部、画素電極用のコンタクトホール部、蓄積容量部を示し、B-b線に沿う断面部は画素部を示し、C-c線に沿う断面部は信号線部、共通電極用のコンタクトホール部、蓄積容量部を示す。

#### 【0026】

先ず、図5、図6に示すように、ガラス基板のような透明絶縁性基板20の上に、スパッタリングにより、Cr、Mo、Cr/A1積層膜、Mo/A1積層膜等からなる導電層を約100~300nmの膜厚で成膜し、フォトリソ工程により、ゲート電極23を兼ねる走査線11、共通配線13、及び走査線端子部(図示しない)、共通配線端子部(図示しない)を形成する。

#### 【0027】

次に、図7、図8に示すように、プラズマCVDにより、シリコン窒化膜からなるゲート絶縁膜31を約300~500nmの膜厚で、更に、アモルファスシリコン(a-Si)を約150~300nmの膜厚で、リンがドープされたアモルファスシリコン(n+型a-Si)を約30~50nmの膜厚で順次成膜し、フォトリソ工程によりTFT14の活性層となる半導体層34を形成する。走査線11、共通配線13と信号線の交差部にも耐圧向上用半導体層64を形成するのは両者の絶縁耐圧を高めるためである。

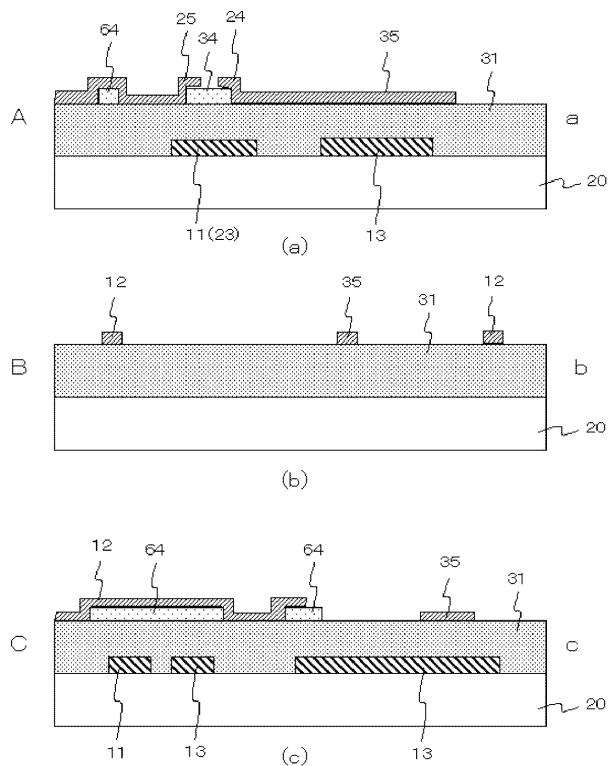

#### 【0028】

次に、図9、図10に示すように、スパッタリングにより、Cr、Mo、Cr/A1/Cr積層膜、Mo/A1/Mo積層膜等からなる導電層を約100~400nmの膜厚で成膜し、フォトリソ工程により、ソース電極24、ドレイン電極25、蓄積容量電極35、信号線12、信号線端子部(図示しない)をそれぞれ形成し、続いて、ソース、ドレイン電極24、25をマスクとして、半導体層34上部のn+型a-Siをエッチング除去し、チャネルを形成する。

#### 【0029】

その後、プラズマCVDにより、シリコン窒化膜等の無機膜からなるパッシベーション膜32を約100~300nmの膜厚で成膜する。

10

20

30

40

50

## 【0030】

次に、図11、図12に示すように、ポジ型感光性ノボラック系レジストを用いて膜厚が約1.5～3.5μmの有機絶縁膜33で成膜し、コンタクトホール形成部分に開口66、67を形成する。

## 【0031】

その後、図13、図14に示すように、フォトリソ工程により、パッシベーション膜32をエッチングして開口66、67に対応する箇所に、ソース電極24を露出させる画素電極用のコンタクトホール26と、信号線端子部を露出させるコンタクトホール（図示しない）を形成する。また同時に、パッシベーション膜32及びゲート絶縁膜31をエッチングして、共通配線13を露出させる共通電極用のコンタクトホール27と、走査線端子部、共通配線端子部を露出させるコンタクトホール（図示しない）と、各共通配線13の端部を露出させる共通配線結束線用のコンタクトホール（図示しない）を、それぞれ形成する。

10

## 【0032】

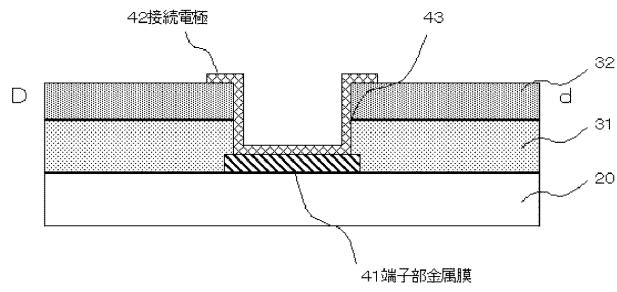

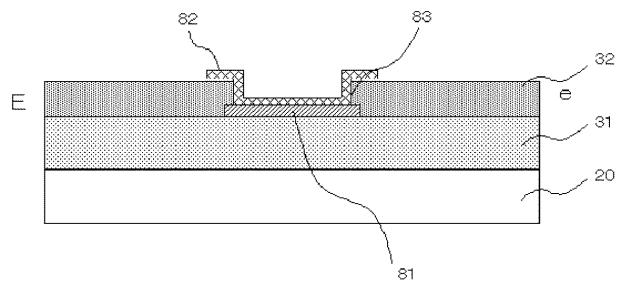

次に、図2、図3に示すように、スパッタリングにより有機絶縁膜33上にITO等からなる透明導電膜を成膜し、フォトリソ工程により画素電極21と共に電極22及び走査線端子部、信号線端子部、共通配線端子部上の接続電極（図示しない）、共通配線結束線（図示しない）を形成する。このとき、図3(b)に示すように、信号線12に対応して有機絶縁膜33上に共通電極22の一つ72が位置し、また、図3(a)に示すように、蓄積容量電極35に対応して有機絶縁膜33上に画素電極21の一つ71が位置するよう形成する。これにより、画素電極用のコンタクトホール26を介して、ソース電極24に接続する画素電極21が、共通電極用のコンタクトホール27を介して、共通配線13に接続する共通電極22が、また、走査線、信号線、共通配線端子部用のコンタクトホールを介して、走査線端子部、信号線端子部、共通配線端子部に接続する接続電極が、共通配線結束線用のコンタクトホールを介して、各共通配線13の端部に接続する共通配線結束線がそれぞれ形成される。（端子部の構造については、後述する。）次に、第1の実施の形態のTFT基板の端子部の構造について説明する。図15は、基板周辺の端子部の平面図であり、図16は図15のD-d線に沿う断面図で走査線端子及び共通配線端子を、図17は図15のE-e線に沿う断面図で信号線端子を示す。走査線端子、共通配線端子は走査線と同一の金属膜で形成される端子部金属膜41上に共通電極と同一の透明導電膜で形成される接続電極42が、信号線端子は信号線と同一の金属膜で形成される端子部金属膜81上に共通電極と同一の透明導電膜で形成される接続電極82が、それぞれゲート絶縁膜及びパッシベーション膜、パッシベーション膜に開口された端子部コンタクトホール43、83を介して接続された構造になっている。このように各端子部には有機絶縁膜は形成されていない。

20

30

30

## 【0033】

なお、各共通配線13は、共通配線結束線用のコンタクトホール44を介して共通配線結束線17に接続されている。コンタクトホール44の断面構造は図示していないが図16と同様な構造になっている。

40

## 【0034】

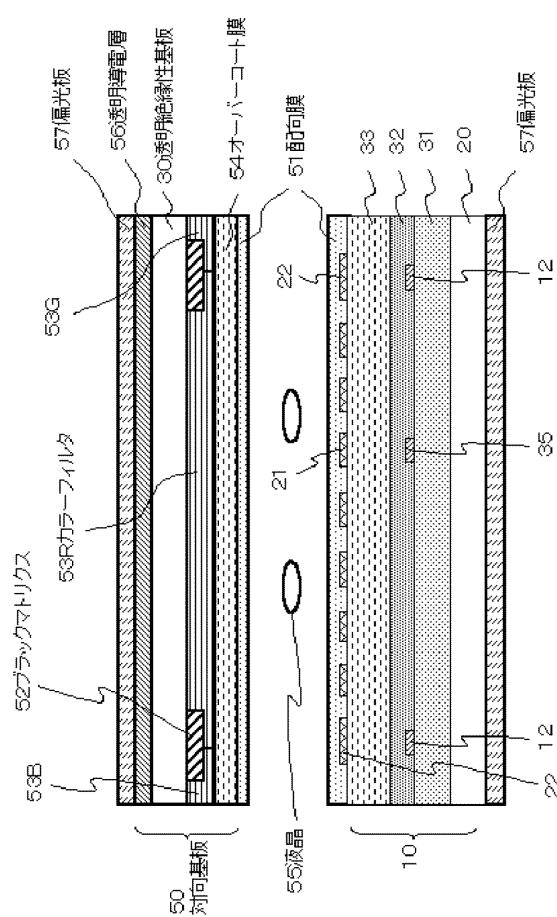

次に、第1の実施の形態のTFT基板と対向基板との間に液晶を挟持した液晶パネルの製造方法について簡単に説明する。図18は、この液晶パネルの1画素部分の断面図である。前述したTFT基板10にポリイミド系の配向剤からなる膜厚が30～60nmの配向膜51を形成し、配向処理をした後、エポキシ系樹脂接着剤からなるシール材（図示しない）をTFT基板10の周縁に沿って形成する。

## 【0035】

一方、あらかじめカラーフィルタが形成される面とは反対側の面に、膜厚が約80～150nmのITO等の透明導電層56を成膜したガラス基板のような透明絶縁性基板30に、ネガ型感光性アクリル系顔料分散レジスト或いはカーボン系レジストを用いて、膜厚が約1～3μm、光学濃度(OD値)が3以上、シート抵抗値が $1 \times 10^{10}$  / 以上

50

ブラックマトリクス 5 2 を形成する。次に、ネガ型感光性アクリル系顔料分散レジストを用いて、膜厚が約 1 . 0 ~ 1 . 5  $\mu\text{m}$  の赤色カラーフィルタ 5 3 R を形成する。同様に、青色カラーフィルタ 5 3 B 及び緑色カラーフィルタ 5 3 G の各色層を形成する。次に、ノボラック系レジストを用いて、膜厚が約 2 . 0 ~ 3 . 5  $\mu\text{m}$  の有機絶縁膜であるオーバーコート膜 5 4 を形成する。更に、この上にポリイミド系の配向剤からなる膜厚が 3 0 ~ 6  $\mu\text{m}$  の配向膜 5 1 を形成し、配向処理をして対向基板 5 0 とする。

#### 【 0 0 3 6 】

その後、シール材と面内スペーサ（図示しない）を介して、TFT 基板 1 0 の上に対向基板 5 0 を重ね合わせ、両基板の間に注入口（図示しない）からフッ素系化合物からなる液晶 5 5 を注入した後、UV 硬化型アクリレート系樹脂からなる封口材（図示しない）により注入口を封止し、所定ギャップのパネルを得る。10

#### 【 0 0 3 7 】

最後に、TFT 基板 1 0 の素子面とは反対側の面と対向基板 5 0 のカラーフィルタとは反対側の面に、ヨウ素系偏光フィルムからなる偏光板 5 7 をそれぞれ貼り付ける。これにより、前述の TFT 基板 1 0 を用いた広視野角、高開口率の液晶パネルが製造される。

#### 【 0 0 3 8 】

以上のように、信号線の少なくとも一部を層間絶縁膜を介して共通電極で被覆するようにした横方向電界型の液晶表示装置において、共通配線と共に電極を接続するコンタクトホールを画素毎に形成せず、間引きして形成するようにしたので、信号線形成工程で異物等によりパターニング不良が発生しても、このコンタクトホールを介して、信号線と共に電極がショートする確率を低減でき、製造歩留を向上することができる。特に、画素面積の小さい Q S X G A クラスの大型高精細パネルでは、この効果が顕著である。更に、前述のコンタクトホールを千鳥状に配置したので、表示の均一性を確保することができる。20

#### 【 0 0 3 9 】

##### （第 2 の実施の形態）

本発明の第 2 の実施の形態は、TFT 上の層間絶縁膜を無機膜のみで形成する場合に係わる。TFT 基板の構成は、図 1 の第 1 の実施の形態と同じである。

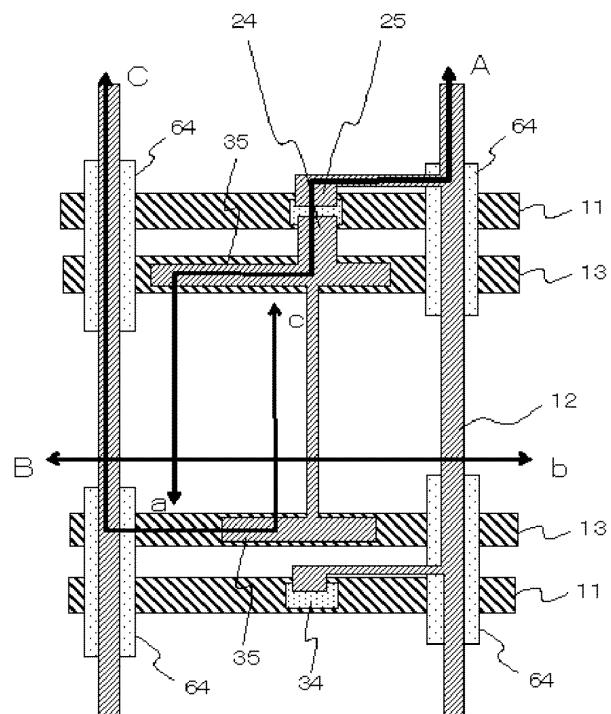

#### 【 0 0 4 0 】

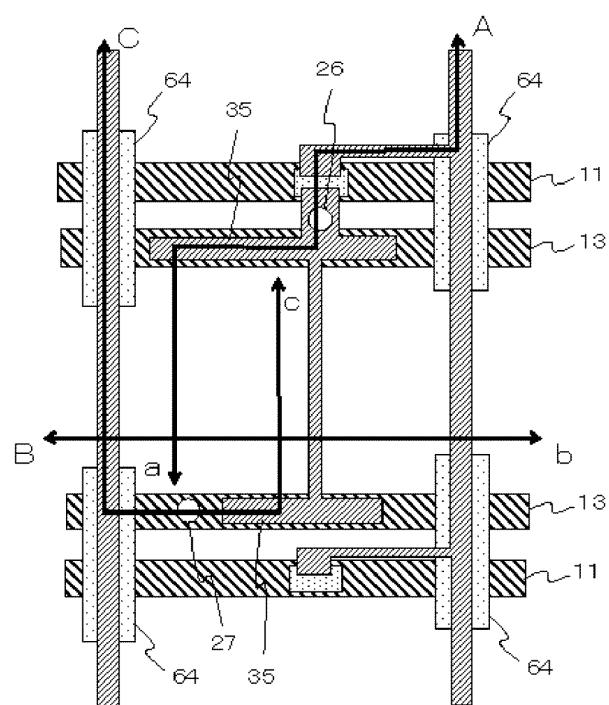

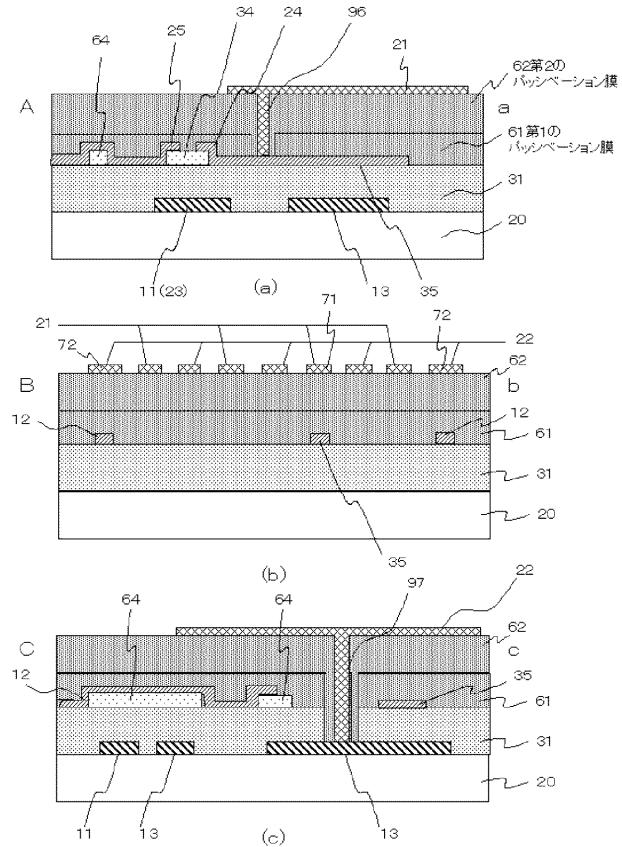

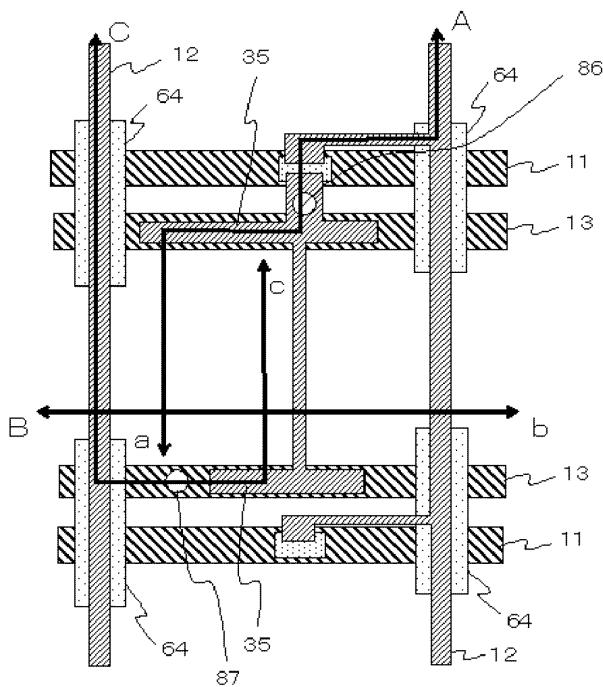

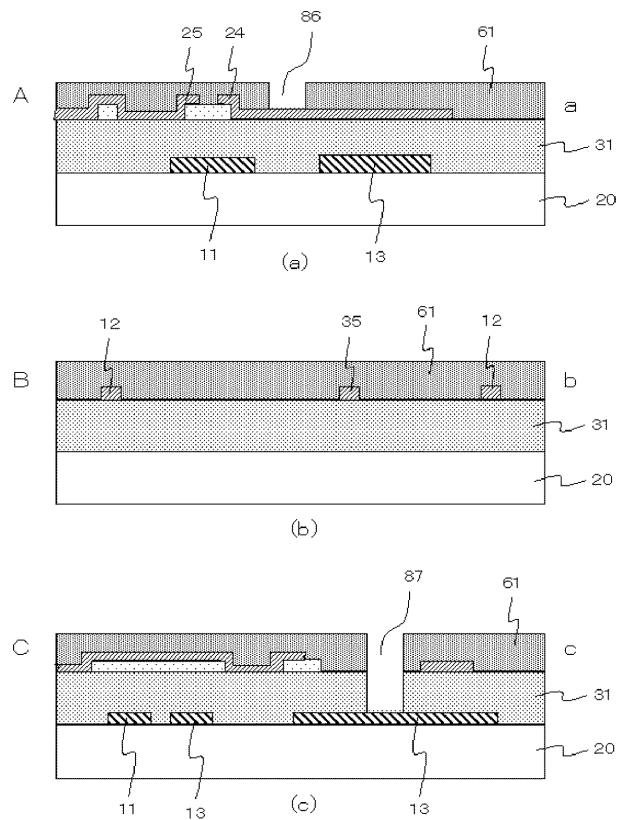

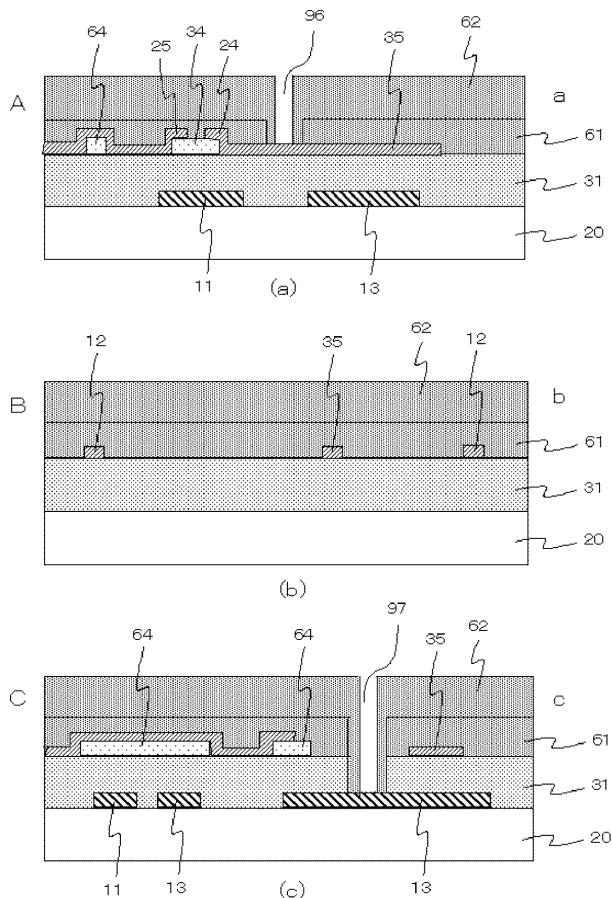

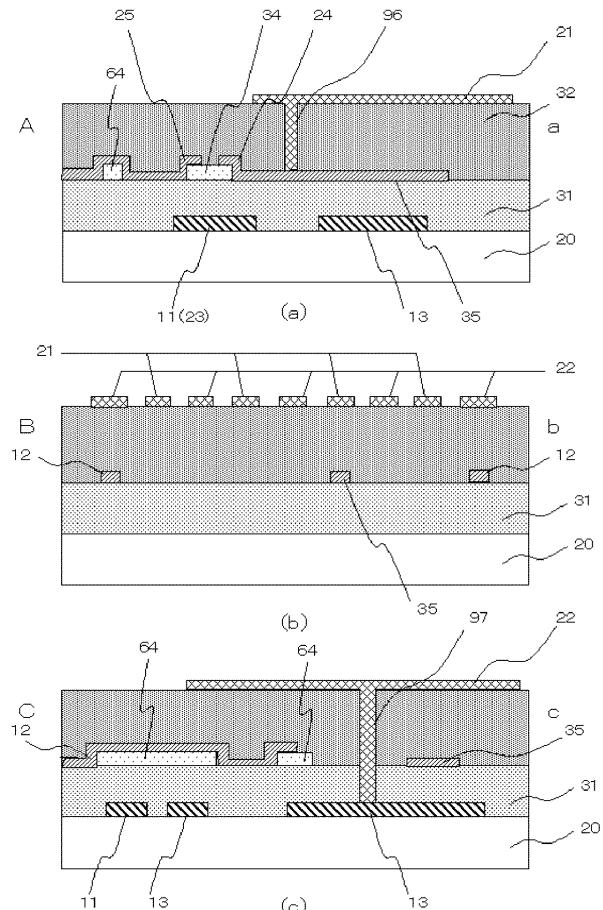

図 19 は、図 1 の TFT 基板の 1 画素部を拡大して示す平面図、図 20 は、図 19 の A - a 線、B - b 線、C - c 線に沿う断面図である。図 19 に示すように、TFT 基板上に形成される走査線 1 1 と信号線 1 2 の交差区画には、櫛歯状に形成された画素電極 2 1 と共に電極 2 2 が交互に配置され、この電極間に TFT 基板 1 0 と概ね平行な電界を発生させ液晶分子の配列を制御している。また、この画素電極 2 1 と共に電極 2 2 は、図 20 に示すように、TFT 1 4 上に形成された 2 層のパッシベーション膜 6 1 、6 2 からなる層間絶縁膜上に設けられている。30

#### 【 0 0 4 1 】

第 1 の実施の形態と全く同様に、本実施形態でも、TFT 1 4 は、逆スタガ型の薄膜トランジスタの例を示しており、TFT 1 4 のゲート電極 2 3 は走査線 1 1 の一部として形成され、ソース電極 2 4 には層間絶縁膜に形成された画素電極用のコンタクトホール 2 6 を介して画素電極 2 1 が、共通配線 1 3 には層間絶縁膜及びゲート絶縁膜 3 1 に形成された共通電極用のコンタクトホール 2 7 を介して共通電極 2 2 がそれぞれ接続され、ドレン電極 2 5 には信号線 1 2 が接続されている。本実施形態では、共通電極用のコンタクトホール 2 7 は、すべての画素に設けられている。40

#### 【 0 0 4 2 】

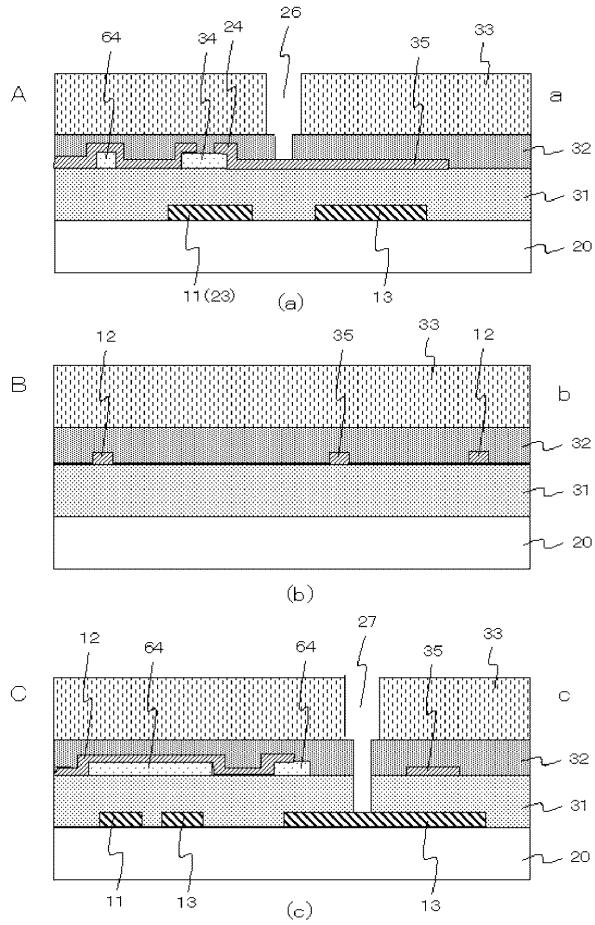

次に、第 2 の実施の形態の TFT 基板の製造方法を説明する。TFT 1 4 を形成する工程は、第 1 の実施の形態と全く同じ（図 5 ~ 図 10）なので、説明は省略する。図 21 、図 23 、図 19 は、1 画素部分のパッシベーション膜形成工程以降の製造工程を示す平面図、図 22 、図 24 、図 20 は、それぞれ図 21 、図 23 、図 19 の A - a 線（（ a ）図）、B - b 線（（ b ）図）、C - c 線（（ c ）図）に沿う工程断面図である。ここでも、A - a 線に沿う断面部は TFT 部、画素電極用のコンタクトホール部、蓄積容量部を示し50

、B-b線に沿う断面部は画素部を示し、C-c線に沿う断面部は信号線部、共通電極用のコンタクトホール部、蓄積容量部を示す。

#### 【0043】

図21、図22に示すように、プラズマCVDにより、シリコン窒化膜等の無機膜からなる第1のパッシベーション膜61を約300~500nmの膜厚で成膜し、フォトリソ工程により、第1のパッシベーション膜61をエッチングしてソース電極24を露出させる画素電極用の開口86と信号線端子部を露出させるコンタクトホール(図示しない)を形成する。また同時に、第1のパッシベーション膜61及びゲート絶縁膜31をエッチングして、共通配線13を露出させる共通電極用の開口87と、走査線端子部、共通配線端子部を露出させるコンタクトホール(図示しない)と、各共通配線13の端部を露出させる共通配線結束線用のコンタクトホール(図示しない)をそれぞれ開口する。このときのコンタクトホールのエッチングは、ドライエッチング若しくはウェットエッチングとドライエッチングの組み合せで行い、少なくともドライエッチングを含むことが特徴である。

#### 【0044】

次に、図23、図24に示すように、再度プラズマCVDにより、シリコン窒化膜等の無機膜からなる第2のパッシベーション膜62を、約300~500nmの膜厚で成膜し、フォトリソ工程により、上記工程と同一のマスクを用いて、第2のパッシベーション膜62をエッチングして、ソース電極24を露出させる画素電極用のコンタクトホール96と、信号線端子部を露出させるコンタクトホール(図示しない)を、第1のパッシベーション膜61及びゲート絶縁膜31をエッチングして、共通配線13を露出させる共通電極用のコンタクトホール97と、走査線端子部、共通配線端子部を露出させるコンタクトホール(図示しない)と、各共通配線13の端部を露出させる共通配線結束線用のコンタクトホール(図示しない)をそれぞれ開口する。このとき、露光量を調整し、上記工程のコンタクトホールの内側に開口を設けるようとする。また、このときのコンタクトホールのエッチングは、ウェットエッチング、ドライエッチングのどちらでもよく、両者の組み合せで行ってもよい。

#### 【0045】

次に、図19、図20に示すように、第1の実施の形態と全く同様に、スパッタリングにより、有機絶縁膜33上にITO等からなる透明導電膜を成膜し、フォトリソ工程により、画素電極21と共に電極22及び走査線端子部、信号線端子部、共通配線端子部上の接続電極(図示しない)、共通配線結束線(図示しない)を形成する。このとき、信号線12に対応して、第1、2のパッシベーション膜61、62上に共通電極22の一つ72が位置し、また、蓄積容量電極35に対応して有機絶縁膜33上に画素電極21の一つ71が位置するように形成する。これにより、画素電極用のコンタクトホール96を介して、ソース電極24に接続する画素電極21が、共通電極用のコンタクトホール97を介して、共通配線13に接続する共通電極22が、また、走査線、信号線、共通配線端子部用のコンタクトホールを介して、走査線端子部、信号線端子部、共通配線端子部に接続する接続電極が、共通配線結束線用のコンタクトホールを介して、各共通配線13の端部に接続する共通配線結束線が、それぞれ形成される。ここで、各端子部の構造は、パッシベーション膜が2層になっている以外は、第1の実施の形態(図16、図17)と全く同様である。

#### 【0046】

続くセル工程は、第1の実施の形態と全く同様に行い、本実施形態のTFT基板を用いた液晶パネルが製造される。

#### 【0047】

本発明者の実験によると、パッシベーション膜が単層で、コンタクトホール開口工程が1回の場合、信号線と共に電極のショートが多発した。この原因是、コンタクトホール開口時のドライエッチングに起因して、層間絶縁膜にピンホールが形成されるためと判明した。これは、コンタクトホール開口工程で、フォトレジストの異物や欠陥部にプラズマが集中するために発生すると推定される。パッシベーション膜を2層化し、コンタクトホー

ル開口工程を2回に分けることにより、第1のパッシベーション膜61にはピンホールが発生するが、第2のパッシベーション膜62にはピンホールが発生したとしても、同一箇所に発生する確率は極めて低い。即ち、第2のパッシベーション膜62の開口の際、ドライエッティングを用いると、同様にピンホールは形成されるが、第2のパッシベーション膜62をエッティングする時間は、当然第1のパッシベーション膜61と第2のパッシベーション膜62の全膜厚をエッティングしてしまう時間よりは短いので、パッシベーション膜の全膜厚分を貫通してピンホールが形成されることはない。勿論、第2のパッシベーション膜62をウェットエッティングする場合は、第2のパッシベーション膜62にはピンホールが発生することなく、ピンホールは第1のパッシベーション膜の膜厚分のみしか形成されない。従って、信号線の少なくとも一部を層間絶縁膜を介して共通電極で被覆するようにした横方向電界型の液晶表示装置において、本実施形態のような製造方法をとることにより、信号線と共に電極のショートを著しく低減することが可能である。

10

## 【0048】

また、本実施形態では、第1のパッシベーション膜61の開口と第2のパッシベーション膜62の開口を同一マスクを用いて行うので、フォトリソ工程は1工程増えるが、マスク数は増えないという利点がある。更に、第2のパッシベーション膜62の開口を第1のパッシベーション膜61の開口の内側に設けたので、第2のパッシベーション膜62の開口をウェットエッティングで行っても、コンタクトホールの形状を良好に保つことができる。即ち、第2のパッシベーション膜62の開口を第1のパッシベーション膜61の開口の外側に設けた場合、特に、ゲート絶縁膜に酸化シリコン膜等、窒化シリコン膜とは異なる膜を用いたときなどは、酸化シリコン膜にサイドエッチが入り、コンタクトホールの形状を階段形状に保てず、上に形成する透明導電膜の段切れを発生させてしまう。第2のパッシベーション膜62の開口を第1のパッシベーション膜61の開口の内側に設けることで、第1のパッシベーション膜61の開口部側壁が第2のパッシベーション膜62で保護されるため、このような不具合を防止することができる。

20

## 【0049】

## (第3の実施の形態)

本発明の第3の実施の形態は、第2の実施の形態と同様に、TFT上の層間絶縁膜を無機膜のみで形成する場合に係わる。本実施形態では、層間絶縁膜の無機膜は単層で形成されていることが、第2の実施の形態と異なるだけで、他の構成は第2の実施の形態と全く同様である。

30

## 【0050】

図19は、図1のTFT基板の1画素部を拡大して示す平面図(第2の実施の形態と同じ)、図25は、図19のA-a線、B-b線、C-c線に沿う断面図である。図25に示すように、このTFT基板の画素電極21と共に電極22は、TFT14上に形成された単層のパッシベーション膜32からなる層間絶縁膜上に設けられている。

40

## 【0051】

次に、第3の実施の形態のTFT基板の製造方法を説明する。第2の実施の形態と異なるところは、パッシベーション膜形成及びコンタクトホール開口工程だけである。即ち、プラズマCVDにより、シリコン窒化膜等の無機膜からなるパッシベーション膜32を、約700~1000nmの膜厚で成膜し、フォトリソ工程により、パッシベーション膜32をエッティングして、ソース電極24を露出させる画素電極用のコンタクトホール96と、信号線端子部を露出させるコンタクトホール(図示しない)を、パッシベーション膜32及びゲート絶縁膜31をエッティングして、共通配線13を露出させる共通電極用のコンタクトホール97と、走査線端子部、共通配線端子部を露出させるコンタクトホール(図示しない)と、各共通配線13の端部を露出させる共通配線結束線用のコンタクトホール(図示しない)をそれぞれ開口する。このときのコンタクトホールのエッティングは、ウェットエッティングとドライエッティングの組み合せで行い、ドライエッティングでエッティングする膜厚分(正確には、ドライエッティングする時間分の膜厚)よりパッシベーション膜32の膜厚を厚くすることが特徴である。

50

**【0052】**

このように、コンタクトホール開口時に、ドライエッチングでエッチングする時間分の膜厚よりパッシベーション膜を厚く形成することにより、前述と同様の理由で、パッシベーション膜にピンホールが形成されたとしても、ピンホールがその全膜厚を貫通することはなく、従って、信号線と共に電極のショートを著しく低減することが可能である。

**【0053】**

なお、第1の実施の形態では、感光性ノボラック系レジストのような有機絶縁膜を用いた例を示したが、勿論ポリイミド樹脂やアクリル樹脂を用いてもよいし、シリコン酸化膜やシリコン窒化膜等の無機系樹脂材料であってもよい。また、感光性でなく非感光性のものでもよい。この場合は、通常のフォトリソ工程と同様に、現像後にエッチング工程とレジスト剥離工程が必要になる。また、有機絶縁膜の形成工程とパッシベーション膜の開口工程は、別々のフォトリソ工程である例を示したが、同一のフォトリソ工程で開口してもよい。

**【0054】**

また、前述の実施の形態では、逆スタガチャネルエッチ型TFTを有する液晶表示装置について述べたが、チャネル保護型や順スタガ型TFTでもよく、また、スタガード型TFTのみならず、コブレーナ型のTFTについても適用できることは言うまでもない。また、a-Si TFTのみならず、ポリシリコン(p-Si) TFTにも適用できる。更に、スイッチング素子はMIMであってもよい。

**【0055】**

以上説明したように、本発明によれば、信号線の少なくとも一部を層間絶縁膜を介して共通電極で被覆するようにした横方向電界型の液晶表示装置において、表示性能を劣化させることなく、信号線と共に電極のショートを著しく低減し、製造歩留を向上することが可能である。

**【図面の簡単な説明】****【0056】**

【図1】本発明の第1の実施の形態に係る横方向電界型液晶表示装置におけるTFT基板の構成を概念的に示す平面図である。

【図2】図1のTFT基板の1画素部を拡大して示す平面図である。

【図3】図2のA-a線、B-b線、C-c線に沿う断面図である。

【図4】共通電極用のコンタクトホールの配置を示す模式図である。

【図5】図1のTFT基板を用いた液晶パネルの製造方法の一例を説明する、1画素部の工程平面図(第1工程)である。

【図6】図5のA-a線、B-b線、C-c線に沿う工程断面図である。

【図7】図1のTFT基板を用いた液晶パネルの製造方法の一例を説明する、1画素部の工程平面図(第2工程)である。

【図8】図7のA-a線、B-b線、C-c線に沿う工程断面図である。

【図9】図1のTFT基板を用いた液晶パネルの製造方法の一例を説明する、1画素部の工程平面図(第3工程)である。

【図10】図9のA-a線、B-b線、C-c線に沿う工程断面図である。

【図11】図1のTFT基板を用いた液晶パネルの製造方法の一例を説明する、1画素部の工程平面図(第4工程)である。

【図12】図11のA-a線、B-b線、C-c線に沿う工程断面図である。

【図13】図1のTFT基板を用いた液晶パネルの製造方法の一例を説明する、1画素部の工程平面図(第5工程)である。

【図14】図13のA-a線、B-b線、C-c線に沿う工程断面図である。

【図15】図1のTFT基板周辺の端子部の平面図である。

【図16】図15のD-d線に沿う断面図である。

【図17】図15のE-e線に沿う断面図である。

【図18】図1のTFT基板を用いた液晶パネルの1画素部分の断面図である。

10

20

30

40

50

【図19】本発明の第2の実施の形態に係る横方向電界型液晶表示装置におけるTFT基板の1画素部を拡大して示す平面図である。

【図20】図19のA-a線、B-b線、C-c線に沿う断面図である。

【図21】本発明の第2の実施の形態のTFT基板の1画素部の工程平面図(第4工程)である。

【図22】図21のA-a線、B-b線、C-c線に沿う工程断面図である。

【図23】本発明の第2の実施の形態のTFT基板の1画素部の工程平面図(第5工程)である。

【図24】図23のA-a線、B-b線、C-c線に沿う工程断面図である。

【図25】本発明の第3の実施の形態に係る横方向電界型液晶表示装置におけるTFT基板の1画素部を拡大して示す平面図(図19と同じ)のA-a線、B-b線、C-c線に沿う断面図である。

10

【図26】従来の横方向電界型液晶表示装置におけるTFT基板の1画素部を拡大して示す平面図である。

【図27】図26のX-X'線に沿う断面図である。

【図28】図26のY-Y'線に沿う断面図である。

#### 【符号の説明】

##### 【0057】

|     |                     |             |

|-----|---------------------|-------------|

| 10  | TFT基板               |             |

| 20  | 20、30、120           | 透明導電性基板     |

| 11  | 111                 | 走査線         |

| 12  | 112                 | 信号線         |

| 13  | 113                 | 共通配線        |

| 14  | 114                 | TFT         |

| 15  |                     | 走査線端子       |

| 16  |                     | 信号線端子       |

| 17  |                     | 共通配線結束線     |

| 18  |                     | 共通配線端子      |

| 21  | 71、121              | 画素電極        |

| 22  | 72、122              | 共通電極        |

| 23  | 123                 | ゲート電極       |

| 24  | 124                 | ソース電極       |

| 25  | 125                 | ドレイン電極      |

| 26  | 27、44、96、97、126、127 | コンタクトホール    |

| 31  | 131                 | ゲート絶縁膜      |

| 32  |                     | パッシベーション膜   |

| 33  | 133                 | 有機絶縁膜       |

| 34  | 134                 | 半導体層        |

| 35  |                     | 蓄積容量電極      |

| 41  | 81                  | 端子部金属膜      |

| 42  | 82                  | 接続電極        |

| 43  | 83                  | 端子部コンタクトホール |

| 50  |                     | 対向基板        |

| 51  |                     | 配向膜         |

| 52  |                     | ブラックマトリクス   |

| 53R | 53G                 | 53B         |

| 54  |                     | カラーフィルタ     |

| 55  |                     | オーバーコート膜    |

| 56  |                     | 液晶          |

| 57  |                     | 透明導電層       |

|     |                     | 偏光板         |

10

20

30

40

50

- 6 1 第1のパッシベーション膜

6 2 第2のパッシベーション膜

6 4 耐圧向上用半導体層

6 6、6 7、8 6、8 7 開口

1 3 2 保護膜

1 6 4 アモルファスシリコン(a-Si)層

1 7 4 n+型アモルファスシリコン(n+型a-Si)層

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

---

フロントページの続き

(72)発明者 早瀬 貴介

神奈川県川崎市中原区下沼部1753番地

社内

N E C液晶テクノロジー株式会

(72)発明者 堀之内 誠

神奈川県川崎市中原区下沼部1753番地

社内

N E C液晶テクノロジー株式会

(72)発明者 元島 秀人

神奈川県川崎市中原区下沼部1753番地

社内

N E C液晶テクノロジー株式会

(72)発明者 前田 明寿

神奈川県川崎市中原区下沼部1753番地

社内

N E C液晶テクノロジー株式会

F ターム(参考) 2H092 GA14 GA17 GA29 HA04 JA26 JA29 JA44 JA46 JB13 JB16

JB33 JB38 JB64 KA05 KB25 MA05 MA08 MA13 MA35 MA37

NA16

5C094 AA42 BA03 BA43 DB01 EA07

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2007316670A</a>                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2007-12-06 |

| 申请号            | JP2007212547                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2007-08-17 |

| [标]申请(专利权)人(译) | NEC液晶技术株式会社                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | NEC LCD科技有限公司                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 西郷伸吾<br>早瀬貴介<br>堀之内誠<br>元島秀人<br>前田明寿                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 西郷 伸吾<br>早瀬 貴介<br>堀之内 誠<br>元島 秀人<br>前田 明寿                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G02F1/1368 G09F9/30                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F1分类号          | G02F1/1368 G09F9/30.338                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/GA17 2H092/GA29 2H092/HA04 2H092/JA26 2H092/JA29 2H092/JA44 2H092/JA46 2H092/JB13 2H092/JB16 2H092/JB33 2H092/JB38 2H092/JB64 2H092/KA05 2H092/KB25 2H092/MA05 2H092/MA08 2H092/MA13 2H092/MA35 2H092/MA37 2H092/NA16 5C094/AA42 5C094/BA03 5C094/BA43 5C094/DB01 5C094/EA07 2H192/AA24 2H192/BB03 2H192/BC31 2H192/CB05 2H192/CB46 2H192/CC04 2H192/DA32 2H192/EA22 2H192/EA43 2H192/EA72 2H192/FA65 2H192/GA42 |         |            |

| 代理人(译)         | 台正彦<br>下坂 直树<br>谷泽恭久                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

## 摘要(译)

在横向电场液晶显示器中减小了信号线和公共电极之间的短路，其中信号线的至少一部分通过层间绝缘膜被公共电极覆盖。显示部分被扫描线11和信号线12分开以提供像素，但是没有为每个像素形成用于连接公共布线和公共电极的接触孔27，而是稀疏并且以锯齿形排列。例如，每4个像素提供一次，并且减少了信号线和公共电极之间的短路。[选图]图4