(19) 日本国特許庁(JP)

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4452513号 (P4452513)

(45) 発行日 平成22年4月21日(2010.4.21)

(24) 登録日 平成22年2月5日(2010.2.5)

(51) Int. Cl. F 1

**GO2F** 1/1343 (2006.01) GO2F 1/1343 **GO2F** 1/1368 (2006.01) GO2F 1/1368

請求項の数 11 (全 19 頁)

(21) 出願番号 特願2004-26 (P2004-26) (22) 出願日 平成16年1月5日 (2004.1.5)

(65) 公開番号 特開2004-213011 (P2004-213011A) (43) 公開日 平成16年7月29日 (2004.7.29) 審査請求日 平成17年11月25日 (2005.11.25)

(31) 優先権主張番号 2003-000266

(32) 優先日 平成15年1月3日(2003.1.3)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

SAMSUNG ELECTRONICS CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞416 416, Maetan-dong, Yeo ngtong-gu, Suwon-si, Gyeonggi-do 442-742 (KR)

(74)代理人 100094145

弁理士 小野 由己男

(74)代理人 100106367

弁理士 稲積 朋子

最終頁に続く

# (54) 【発明の名称】多重ドメイン液晶表示装置用薄膜トランジスタ表示板

## (57)【特許請求の範囲】

# 【請求項1】

絶縁基板、

前記絶縁基板上に形成されている第1配線、

前記絶縁基板上に形成され、前記第1配線と絶縁されて交差している第2配線、

前記第1配線と前記第2配線が交差して定義する画素領域ごとに形成され、切開部によって複数の小部分に分割されている第1及び第2画素電極、

前記第1配線と前記第2配線が交差して定義される画素領域ごとに形成され、前記第1及び第2画素電極の切開部の少なくとも一部と重畳する部分を有するとともに、前記第1及び第2画素電極の一部と重畳する方位制御電極と、

前記方位制御電極、前記第1配線及び前記第2配線に3端子が各々連結されている方位 制御電極用薄膜トランジスタを含み、

第1画素電極と第2画素電極が形成される層は、方位制御電極が形成される層と異なる薄膜トランジスタ表示板。

## 【請求項2】

前記第1画素電極、前記第1配線及び前記第2配線に3端子が各々連結されている第1 画素電極用薄膜トランジスタをさらに含む請求項1に記載の薄膜トランジスタ表示板。

### 【請求項3】

前記第2画素電極、前記第1配線及び前記第2配線に3端子が各々連結されている第2 画素電極用薄膜トランジスタをさらに含む請求項2に記載の薄膜トランジスタ表示板。

#### 【請求項4】

前記第1画素電極用薄膜トランジスタは、次段の前記第1配線、次段の前記第2配線及び前記第1画素電極と連結されており、

前記第2画素電極用薄膜トランジスタは、前段の前記第1配線、次段の前記第2配線及び前記第1画素電極と連結されており、

前記方位制御電極用薄膜トランジスタは、前段の前記第1配線、前段の前記第2配線及び前記方位制御電極と連結されている請求項3に記載の薄膜トランジスタ表示板。

# 【請求項5】

前記第2配線と絶縁されて交差している第3配線をさらに含む請求項3に記載の薄膜トランジスタ表示板。

【請求項6】

前記第1画素電極用薄膜トランジスタは、次段の前記第1配線、次段の前記第2配線及び前記第1画素電極と連結されており、

前記第2画素電極用薄膜トランジスタは、前段の前記第1配線、次段の前記第2配線及び前記第1画素電極と連結されており、

前記方位制御電極用薄膜トランジスタは、前段の前記第1配線、前記第3配線及び前記 方位制御電極と連結されている請求項5に記載の薄膜トランジスタ表示板。

# 【請求項7】

前記第1画素電極用薄膜トランジスタは、次段の前記第1配線、次段の前記第2配線及び前記第1画素電極と連結されており、

前記第2画素電極用薄膜トランジスタは、前段の前記第1配線、前記第3配線及び前記 第1画素電極と連結されており、

前記方位制御電極用薄膜トランジスタは、前段の前記第1配線、前段の前記第2配線及び前記方位制御電極と連結されている請求項5に記載の薄膜トランジスタ表示板。

#### 【請求項8】

前記方位制御電極は、前記第1画素電極の切開部及び前記第2画素電極の切開部と重畳 している請求項1に記載の薄膜トランジスタ表示板。

## 【請求項9】

前記第2画素電極の切開部は、前記第2画素電極を上下に両分する横方向切開部と横方向切開部を中心にして反転対称をなす第1斜線方向切開部を有し、前記第1画素電極は、前記横方向切開部を中心にして反転対称をなす第2斜線方向切開部を有する請求項1に記載の薄膜トランジスタ表示板。

#### 【請求項10】

前記第1及び第2画素電極は、前記横<u>方向</u>切開部を中心にして反転対称をなす請求項<u>9</u>に記載の薄膜トランジスタ表示板。

#### 【請求項11】

前記第2配線と絶縁されて交差しており、前記第1画素電極と前記第2画素電極との間に配置されている電極を有する第3配線をさらに含む請求項<u>9</u>に記載の薄膜トランジスタ表示板。

【発明の詳細な説明】

## 【技術分野】

# [0001]

本発明は液晶表示装置に関し、特に広視野角を得るために画素領域を複数のドメインに分割した垂直配向液晶表示装置に関する。

## 【背景技術】

#### [0002]

液晶表示装置は、一般に共通電極とカラーフィルター等が形成されている上部表示板と、薄膜トランジスタと画素電極等が形成されている下部表示板との間に液晶物質を注入し、画素電極と共通電極に互いに異なる電位を印加して電界を形成し液晶分子の配列を変更させ、これにより光の透過率を調節して画像を表現する装置である。

10

20

30

30

40

#### [00003]

ところが、液晶表示装置は視野角が狭いのが大きな短所である。このような短所を克服するために、視野角を広くするための様々な方案が模索されているが、その中でも液晶分子を上下表示板に対し垂直に配向し、画素電極とその対向電極である共通電極に一定の切開パターンを形成したり、突起を形成する方法が有力視されている。垂直配向に用いられる液晶物質は、負の誘電率異方性を示すTN液晶物質が普通である。このため、電界を印加すると長軸が電界に対して直角の方向、つまり電極と平行に傾くが、この傾きの方位は電極周辺の電界、つまりフリンジフィールドの方位に従う。この現象を有効に使うには、実効的に細長い電界ドメインを使うことが望ましい。

#### [0004]

切開パターンを形成する方法として、画素電極と共通電極に各々切開パターンを形成し、これらの切開パターンにより形成されるフリンジフィールドを利用して液晶分子が横になる方位を調節することで視野角を広くする方法がある。

#### [0005]

突起を形成する方法は、上下基板上に形成されている画素電極と共通電極上に各々、電極面または誘電体の突起を形成することで、突起により歪曲される電場を利用して液晶分子の横になる方位を調節する方式である。

# [0006]

その他の方法として、下部基板上に形成されている画素電極には切開パターンを形成し、上部基板に形成されている共通電極上には突起を形成し、切開パターンと突起により形成されるフリンジフィールドを利用して液晶の横になる方位を調節することでドメインを 形成する方式がある。

#### [0007]

視野角を広くする様々な方法の中で、共通電極に切開パターンを形成する方法は、共通電極をパターニングするために別途のマスクが必要である。よって、色フィルター上にオーバーコート膜がない構造では、色フィルターの顔料が液晶物質に影響を及ぼすことになるため、色フィルター上にオーバーコート膜を形成する必要がある。そのため、パターニングされた電極の縁で激しい前傾、段差が生じる等の問題がある。また、突起を形成する方法でも、突起を形成するための別途の工程を必要としたり、既存の工程を変形しなければならないため液晶表示装置の製造方法が複雑になる問題がある。さらに、突起や切開部によって開口率が減少する。

# 【発明の開示】

【発明が解決しようとする課題】

### [ 0 0 0 8 ]

本発明が目的とする技術的課題は、製造工程が単純で、安定した多重ドメインを形成する液晶表示装置を提供することにある。本発明の他の技術的課題は、安定した多重ドメインを形成するために切開部と方位制御電極及び結合電極の配置を最適化することである。

## 【課題を解決するための手段】

# [0009]

このような課題を解決するために本発明では、一つの画素領域に画素電極2個を分離して配置し、方位制御電極をこれら画素電極の切開部に配置させる。

#### [0010]

具体的には絶縁基板、前記絶縁基板上に形成されている複数の第1配線、前記絶縁基板上に形成され、前記第1配線と絶縁されて交差している複数の第2配線、前記第1配線と前記第2配線が交差して定義する画素領域ごとに形成され、切開部によって複数の小部分に分割されている第1及び第2画素電極、前記第1配線と前記第2配線が交差して定義する画素領域ごとに形成され、前記第1及び第2画素電極の切開部の少なくとも一部と重複する部分を有する方位制御電極、前記方位制御電極と前記第1配線及び前記第2配線に3端子が各々連結されている方位制御電極用薄膜トランジスタを含む薄膜トランジスタ表示板を用意する。

10

20

30

#### [0011]

この時、前記第1画素電極と前記第1配線及び前記第2配線に3端子が各々連結されている第1画素電極用薄膜トランジスタをさらに含むことができ、前記第1画素電極と前記第1配線及び前記第2配線に3端子が各々連結されている第2画素電極用薄膜トランジスタをさらに含むことができる。

#### [0012]

ここで、前記第1画素電極用薄膜トランジスタは、次段の前記第1配線と次段の前記第2配線及び前記第1画素電極に連結されており、前記第2画素電極用薄膜トランジスタは前段の前記第1配線と次段の前記第2配線及び前記第1画素電極に連結されており、前記方位制御電極用薄膜トランジスタは前段の前記第1配線と前段の前記第2配線及び前記方位制御電極に連結できる。

#### [0013]

また、前記第2配線と絶縁されて交差している第3配線をさらに含むことができる。この時、前記第1画素電極用薄膜トランジスタが次段の前記第1配線と次段の前記第2配線及び前記第1回素電極に連結されていて、前記第2画素電極に連結されていて、前記方位制御電極用薄膜トランジスタが前段の前記第1配線と前記第3配線及び前記方位制御電極に連結されいるか、或いは、前記第1画素電極に連結されていて、前記第1配線と前記第3配線及び前記第1配線と次段の前記第1配線とが記第1回素電極に連結されていて、前記第2画素電極用薄膜トランジスタは前段の前記第1配線と前記第3配線及び前記第1画素電極に連結されていて、前記第2画素電極に連結されていて、前記方位制御電極用薄膜トランジスタが前段の前記第1配線と前段の前記第2配線及び前記方位制御電極に連結されていることができる。

#### [0014]

また、前記方位制御電極は前記第1画素電極の切開部とのみ重畳しているが、前記第1 画素電極に連結され、前記第2画素電極の切開部と重複する結合電極をさらに含んだり、 前記方位制御電極は前記第1画素電極の切開部及び前記第2画素電極の切開部と重複でき る。

## [0015]

また、前記第2画素電極の切開部は、前記第2画素電極を上下に両分する横方向の切開部と横方向切開部を中心にして反転対称をなす第1斜線方向の切開部を有し、前記第1画素電極は前記横方向の切開部を中心にして反転対称をなす第2斜線方向切開部を有することができる。そして、前記第1及び第2画素電極は前記横方向切開部を中心にして反転対称をなすことができる。この時、前記第2配線と絶縁されて交差し、前記第1画素電極と前記第2画素電極との間に配置されている電極を有する第3配線をさらに含むことができる。

## 【発明の効果】

# [0016]

本発明では、方位制御電極を利用してドメインの安定性を向上させ、一つの画素領域内に互いに異なる電圧が印加される二つの画素電極を設けることで側面視認性を向上できる

# 【発明を実施するための最良の形態】

# [0017]

添付した図面を参照して本発明の実施例に対して本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。しかし、本発明は多様な形態で実現することができ、ここで説明する実施例に限定されない。

# [0018]

図面は、各種の層及び領域を明確に表現するために厚さを拡大して示している。明細書全体を通じて類似した部分については同一図面符号を付けている。層、膜、領域、板などの部分が他の部分の"上に"あるとする時、これは他の部分の"すぐ上に"ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の"すぐ上

10

20

30

40

に"あるとする時は、中間に他の部分がないことを意味する。

#### [0019]

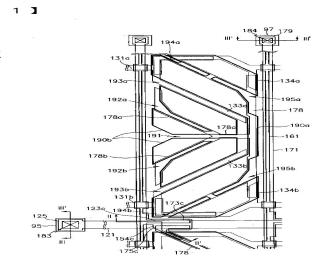

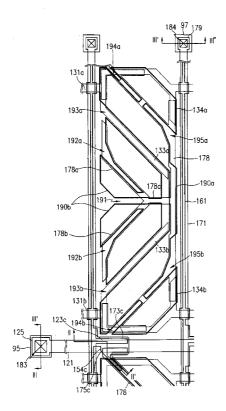

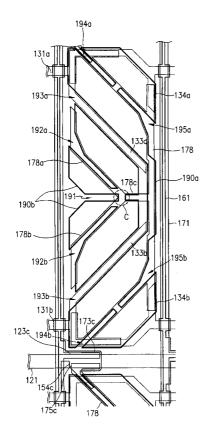

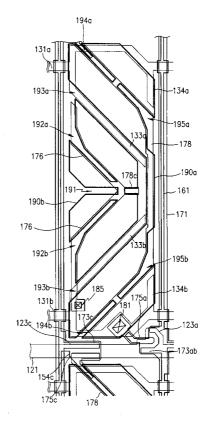

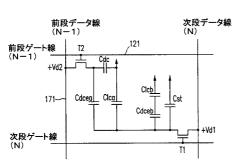

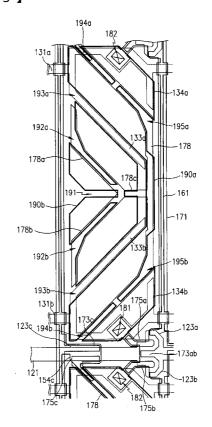

以下、図面を参照して本発明の実施例による多重ドメイン液晶表示装置について説明する。図1は本発明の第1の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図2と図3は各々図1のII-II'線とIII-III'線に沿った断面図であり、図4は本発明の第1実施例による液晶表示装置回路図である。

#### [0020]

本発明の第1の実施例による液晶表示装置は、薄膜トランジスタ表示板とこれと対向する色フィルター表示板及びこれらの間に注入されている液晶層で構成される。

## [0021]

薄膜トランジスタ表示板には、ゲート線121とデータ線171が交差して画素領域を定義しており、基準電位(Vcom)が印加される維持電極線131a、131bが主にゲート線121と平行に形成されている。この時、ゲート線121を通じて走査信号が伝達され、データ線171を通じて画像信号が伝達され、維持電極線131a、131bには基準電位が印加される。

#### [0022]

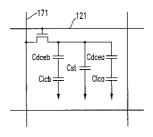

各画素領域には、ゲート線121に連結されているゲート電極123c、データ線17 1に連結されているソース電極173c及び方位制御電極178に連結されているドレーン電極175cを有する方位制御電極用薄膜トランジスタが一つずつ形成されている。

## [0023]

また、各画素領域には二つの画素電極190a、190bが形成され、方位制御電極178は二つの画素電極190a、190bと容量性結合をし、これらの間の静電容量はCdceaとCdcebと表示する。両画素電極190a、190bは、色フィルター表示板の共通電極270との間に液晶蓄電器を形成し、その静電容量は各々C1caとC1cbと表示する。また、方位制御電極178は維持電極線131a、131bとの間に維持蓄電器を形成し、その静電容量はCstと表示する。

#### [0024]

画素電極190a、190bは浮遊し、方位制御電極178との容量性結合によるカップリング電圧が印加される。

# [0025]

本発明による液晶表示装置の画素電極190a、190bは、切開部192a、192b、194a、194b、195a、195bを有し、この切開部192a、192b、194a、194b、195a、195bを通じて方位制御電極178による電界が横に広がるように方位制御電極178と切開部192a、192b、194a、194b、195a、195bが重なっている。切開部192a、192b、194a、194b、195a、195bを通じて広がる方位制御電極178の電界によって液晶分子が電気的プレチルトを有する、つまり電解により液晶分子が傾きを有するようになる。そして、電気的プレチルトを有する液晶分子は、画素電極の電界が印加されると、乱れることなく電気的プレチルトにより定められた方位へ速やかに配向される。

# [0026]

ところが、方位制御電極の電界によって液晶分子が電気的プレチルトを有するためには、共通電極に対する方位制御電極の電位差(以下、方位制御電極電圧という。)が共通電極に対する画素電極の電位差(以下、画素電極電圧という。)に比べて一定値以上大きいことが必要である。本発明による液晶表示装置では、画素電極を浮遊状態にし、方位制御電極との容量性結合によるカップリング電圧が印加されるようにすることで前記のような条件を容易に満足させることができる。その理由について図4を参照して説明する。

#### [0027]

方位制御電極電圧 V d c e はドレーン電極電圧 V d と同一であるので、電圧分配法則によって第 1 画素電極 1 9 0 a の電圧 V a は、V a = V d x C d c e a / ( C d c e a + C l c a ) であり、第 2 画素電極 1 9 0 b の電圧 V b は、V b = V d x C d e c b / ( C d

10

20

30

40

e c b + C l c b ) である。従って、方位制御電極電圧(V d e c = V d ) が常に二つの画素電極電圧 V a 、 V b より大きいことになる。

# [0028]

一方、一つの画素領域を二つに分けて両領域で少し差があるように電界が形成されれば、二つの領域の影響が互いに補償されて側面視認性が向上される。

### [0029]

この時、第1画素電極190aの電圧Vaを第2画素電極190bの電圧Vbより高く設定するのであれば、Cdcea/(Cdcea+Clca)>Cdceb/(Cdceb+Clcb)を満足するようにCdcea、Clca、Cdceb、Clcbを決めれば良い。これらの静電容量は、第1及び第2画素電極190a、190bと方位制御電極178が重畳する面積を変更することによって調節できる。

#### [0030]

以下、本発明の第1実施例による液晶表示装置に対して、もう少し具体的に説明する。 また、本発明の薄膜トランジスタ表示板に対しても、もう少し詳細に説明する。

### [0031]

絶縁基板110上にゲート線121が形成されており、ゲート線121と交差するようにデータ線171が形成されている。ゲート線121とデータ線171は互いに絶縁されており、これらが交差して形成する各画素領域にはゲート電極123c、ソース電極173c及びドレーン電極175cの3端子を有する方位制御用薄膜トランジスタが一つずつ形成されており、方位制御電極178と第1及び第2画素電極190a、190bが各々形成されている。

### [0032]

方位制御用薄膜トランジスタは、方位制御電極178に印加する信号電圧を切断・接続するためのものである。方位制御用薄膜トランジスタのゲート電極123c、ソース電極173c及びドレーン電極175cは、各々ゲート線121、データ線171及び方位制御電極178に連結されている。方位制御電極178は、液晶分子の電気的プレチルトを制御するための方位制御電圧の印加を受けて共通電極270との間に方位制御電界を形成する。ここで、方位制御電極178はデータ線171を形成する段階で、好ましくは同一導電層で、形成される。

# [0033]

第1及び第2画素電極190a、190bは、データ線171やゲート線121と連結されず浮遊しており、方位制御電極178と重なって容量性結合をしている。

#### [0034]

次は、薄膜トランジスタ表示板に対して各層構造まで考慮して詳細に説明する。

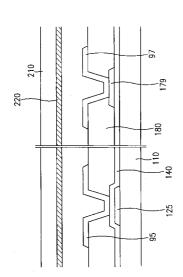

## [0035]

絶縁基板110上に横方向にゲート線121が形成されており、ゲート電極123cがゲート線121に連結されている。ゲート線121の一端にはゲートパッド125が連結されている。また、絶縁基板110上には第1及び第2維持電極線131a、131bと第1乃至第4維持電極133a、133b、134a、134bが形成されている。第1及び第2維持電極線131a、131bは、各画素領域では周辺部に沿って屈曲しているが、全体的には横方向(ゲート線方向)に延びている。そして、第1及び第2維持電極133a、133bは、各々第1及び第2維持電極線131a、131bから縦方向(データ線方向)に延びる途中で屈曲し斜線方向に延びている。第3及び第4維持電極134a、134bは、縦方向に延びる途中で屈曲し斜線方向に延びている。第1維持電縁131a、第1及び第3維持電極133a、134bからなる第1維持配線は互いに反転対称をなしている。ゲート配線121、123c、125及び維持電極配線131a、カリカでなしている。ゲート配線121、123c、125及び維持電極配線131a、第1及び第3番音では、134gの合金、モリブデン又はその合金等で構成され、必要によって物理、化学の特性が優れたCrまたはMo合金等からなる第1層と、抵抗が小さいA1またはAg合金等が

10

20

30

40

らなる第2層の二重層で形成することもできる。

#### [0036]

ゲート配線121、123c、125及び維持電極配線131a、131b、133a、133b、134a、134bは同一導電層で形成する事が望ましく、その上には、ゲート絶縁膜140が形成されている。

### [0037]

ゲート絶縁膜140上には、非晶質シリコンなどの半導体からなる半導体層151、154cが形成されている。半導体層151、154cは、薄膜トランジスタのチャンネルを形成するチャンネル部半導体層154cとデータ線171の下に位置するデータ線部半導体層151を含む。半導体層151、154cの上には、シリサイドまたはn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質で作製された抵抗性接触層161、163c、165cが各々形成されている。

#### [0038]

抵抗性接触層 1 6 1 、 1 6 3 c 、 1 6 5 c 及びゲート絶縁膜 1 4 0 上には、データ配線 1 7 1 、 1 7 3 c 、 1 7 5 c 、 1 7 9 が形成されている。データ配線 1 7 1 、 1 7 3 c 、 1 7 5 c 、 1 7 9 は縦方向に形成され、ゲート線 1 2 1 と交差して画素を定義するデータ線 1 7 1 、データ線 1 7 1 に連結されているソース電極 1 7 3 c 、ゲート電極 1 2 3 c の上でソース電極 1 7 3 c と対向しているドレーン電極 1 7 5 c 、外部回路との連結のために幅が拡張されているデータ線のデータパッド部 1 7 9 を含む。

# [0039]

また、ゲート線 1 2 1 とデータ線 1 7 1 が交差して形成する画素領域内には、方位制御電極 1 7 8 、 1 7 8 a 、 1 7 8 b 、 1 7 8 c が形成されている。この時、方位制御電極 1 7 8 、 1 7 8 a 、 1 7 8 b 、 1 7 8 c はドレーン電極 1 7 5 c と連結され、図 1 を図中右側から見ると下端が潰れたV字状外枠部 1 7 8 と Y 字状中央部 1 7 8 a 、 1 7 8 b 、 1 7 8 c で構成される。

## [0040]

データ配線171、173c、175c、179及び方位制御電極178、178a、178b、178cはアルミニウムやその合金、クロムやその合金、モリブデンやその合金などで構成され、必要によって物理、化学的特性が優れたCrまたはMo合金などからなる第1層と、抵抗が小さいA1またはAg合金などからなる第2層の二重層で形成することもできる。データ配線171、173c、175c、179の上には、窒化ケイ素などの無機絶縁膜または有機絶縁膜からなる保護膜180が形成されている。

#### [0041]

保護膜180上には、第1及び第2画素電極190a、190bが形成されている。第1画素電極190aは二対の斜線方向切開部194a、194bと195a、195bとを有し、第2画素電極190bは一対の斜線方向切開部192a、192bを有する。斜線方向切開部192a、192b、193a、193b、194a、194b、195a、195bは画素領域を上下に両分する線を中心にして反転対称をなしている。この時、切開部192a、192b、194a、194b、195a、195bは方位制御電極178、178a、178b、178cと重畳する。

# [0042]

一方、第1及び第2画素電極190a、190bにおいても、画素領域を上下に二分する線を対称軸とする反転対称をなしている。

# [0043]

第1画素電極190aと第2画素電極190bを分ける境界は、ゲート線121に対して45°をなす部分193a、193bと垂直をなす部分がある。このうち45°をなすこつの部分193a、193bが垂直をなす部分より長さが長い。また、45°をなすこつの部分193a、193bは互いに垂直をなし、維持電極133a、133bと重畳する。

# [0044]

10

20

30

本実施例では、第2画素電極190bが上下に分離されているが、第2画素電極190bを二つに分ける横方向切開部191はゲート線121と平行に形成されている。上下に分離された二つの第2画素電極190bは、横方向切開部191に対して反転対称をなしているので、互いに分離されているが実質的に同一な電位を有する。

# [0045]

また、保護膜180上には、保護膜180とゲート絶縁膜121を貫通する接触孔183を通じてゲート線121の始端部(ゲートパッド)125と連結される接触補助部材95と、保護膜180を貫通する接触孔184を通じてデータ線171の始端部(データパッド)179と連結される接触補助部材97が形成されている。ここで、画素電極190a、190bと接触補助部材95、97はITOで形成されている。画素電極190a、190b及び接触補助部材95、97はITOで形成することもできる。

[0046]

以上、画素電極 1 9 0 a、 1 9 0 bは、画素領域を複数のドメインに分割するための切開部パターン 1 9 1、 1 9 2 a、 1 9 2 b、 1 9 4 a、 1 9 4 b、 1 9 5 a、 1 9 5 bを有し、切開部 1 9 1、 1 9 2 a、 1 9 2 b、 1 9 4 a、 1 9 4 b、 1 9 5 a、 1 9 5 bは方位制御電極 1 7 8、 1 7 8 a、 1 7 8 b、 1 7 8 c と重なっている。即ち、液晶表示装置を上から見たとき方位制御電極 1 7 8、 1 7 8 a、 1 7 8 b、 1 7 8 b、 1 7 8 c が切開部 1 9 1、 1 9 2 a、 1 9 2 b、 1 9 4 a、 1 9 4 b、 1 9 5 a、 1 7 8 c と切開部 1 9 1、 1 9 2 a、 1 9 2 b、 1 9 4 a、 1 9 4 b、 1 9 5 bを重畳配列する。

[0047]

一方、方位制御電極178、178a、178b、178cは、ゲート配線121、123c、125と同じ層に形成することもできる。また、方位制御電極178、178a、178b、178c上部の保護膜180を除去し、トレンチを形成することもできる。

[0048]

次は、色フィルター表示板について詳細に説明する。

[0049]

ガラスなどの透明な絶縁物質からなる基板 2 1 0 の下面に光漏れを防止するためのブラックマトリックス 2 2 0 と赤、緑、青の色フィルター 2 3 0 及び I T O または I Z O などの透明な導電物質からなる共通電極 2 7 0 が形成されている。

[0050]

液晶層 3 に含まれている液晶分子は、画素電極 1 9 0 a、 1 9 0 bと共通電極 2 7 0 との間に電界が印加されない状態でその方向子(普通は長軸の方向)が下部基板 1 1 0 と上部基板 2 1 0 に対して垂直をなすように配向され、負の誘電率異方性を有する。下部基板 1 1 0 と上部基板 2 1 0 は、画素電極 1 9 0 a、 1 9 0 bが色フィルター 2 3 0 と対応して正確に重なるように整列される。

[0051]

このようにすれば、画素領域は切開部191、192a、192b、194a、194 b、195a、195b及び二つの画素電極190a、190bの境界193a、193 bにより複数の小ドメインに分割される。また、方位制御電極178、178a、178 b、178cにより分割されたドメイン内で液晶の配向がさらに安定する。なお、第1画 素電極190aと第2画素電極190bに互いに異なる電位が印加されるようにすること で側面視認性を向上できる。

[0052]

上記では、液晶分子が負の誘電率異方性を有し、基板110、210に対して垂直配向されている場合を例として挙げたが、正の誘電率異方性を有する液晶分子を基板110、 210に対して水平配向して液晶層3を形成することもできる。

[0053]

図1乃至3に示した薄膜トランジスタ表示板の構造は、5回の写真エッチング工程で製造しているが、第1実施例による薄膜トランジスタ表示板は4回の写真エッチング工程で

10

20

30

40

10

20

30

50

製造することもできる。この場合には、データ配線と方位制御電極が非晶質シリコン層、抵抗性接触層及び金属層の3重層で形成され、これらの三つの層の平面パターンが実質的に同一なパターンになるという特徴がある。これは、一つの感光膜を用いて非晶質シリコン層、抵抗性接触層及び金属層をパターニングするためである。このような製造工程に関しては、液晶表示装置に対する通常の知識を有する者に一般に知られていることであるので具体的な説明は省略する。

#### [0054]

上記のような液晶表示装置で、ドメインを分割する役割は画素電極の切開部が行い、方位制御電極と維持電極がドメインの安定性を強化する。従って、切開部と方位制御電極及び維持電極の配置によってドメイン分割の可否が決まることもあり、ドメインの安定性もこれらの配置によって大きく影響される。

#### [0055]

図5は本発明の第2実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。第2の実施例による液晶表示装置用薄膜トランジスタ表示板は、図1では横方向切開部191によって、上下に分離されていた第2画素電極190bが中央の連結部Cにより一つに連結されることを除けば第1の実施例と同様である。

## [0056]

第1及び第2の実施例では、画素電極190a、190bを浮遊させたが、これとは異なって、薄膜トランジスタを通じて電位を印加することもできる。以下、その方法について説明する。

#### [0057]

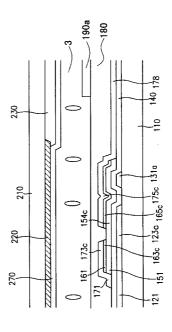

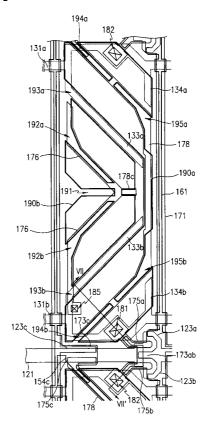

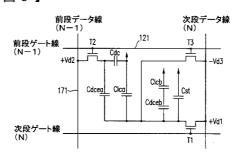

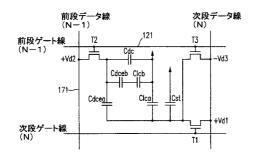

図6は本発明の第3の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図7は図6のVII-VII ′線に沿った断面図であり、図8は本発明の第3の実施例による液晶表示装置の回路図である。

## [0058]

本発明の第3の実施例による液晶表示装置も、薄膜トランジスタ表示板、これと対向する色フィルター表示板及びこれらの間に注入されている液晶層で構成されており、薄膜トランジスタ表示板のゲート配線121、データ線171、維持電極線131などの基本配線構造に関しても第1の実施例とほぼ同様である。しかし、第3の実施例では、各画素領域ごとに3個の薄膜トランジスタT1、T2、T3が配置され、方位制御電極178が第1画素電極190aとのみ容量性結合を行い、第1画素電極190aと第2画素電極190bを容量性で結合する結合電極176が形成されることが第1の実施例と異なる点である。

### [0059]

第3実施例による液晶表示装置で、各画素領域には図8下端の次段ゲート線に連結されているゲート電極123a、図8中、右端の次段データ線に連結されているソース電極173ab(T3と兼用)及び第1画素電極190aに連結されているドレーン電極175aを含む第1画素電極用薄膜トランジスタT1、前段のゲート線121に連結されているゲート電極123c、図8中、左端の前段データ線171に連結されているソース電極173c及び方位制御電極178に連結されているドレーン電極175cを有する方位制御電極用薄膜トランジスタT2、及び前段のゲート線121に連結されているゲート電極123b、図8中、右端の次段のデータ線171に連結されているソース電極173ab(前出)及び第1画素電極190aに連結されているドレーン電極175bを有する第2画素電極用薄膜トランジスタT3がそれぞれ一つずつ形成されている。

#### [0060]

方位制御電極178は第1画素電極190aと容量性結合しており、画素領域には第1 画素電極190aと連結されている結合電極176が形成されており、結合電極176は、第2画素電極190bと重複し第1画素電極190aと第2画素電極190bを容量性で結合する。

## [0061]

図8では、方位制御電極178と第1画素電極190aとの間の静電容量をCdcea、第1画素電極190aと第2画素電極190bとの間の静電容量をCdceb、第1及び第2画素電極190a、190bと色フィルター表示板の共通電極270との間の液晶容量をそれぞれClca及びClcb、第1画素電極190aと維持電極線131a、131bとの間の容量をCst、方位制御電極178と共通電極270の間の静電容量をCdcと表示する。

[0062]

本発明による液晶表示装置の画素電極 1 9 0 a 、 1 9 0 b は、切開部 1 9 1 、 1 9 2 a 、 1 9 2 b 、 1 9 4 a 、 1 9 4 b 、 1 9 5 a 、 1 9 5 b を有し、この切開部 1 9 1 、 1 9 2 a 2 a 、 1 9 2 b 、 1 9 4 a 、 1 9 4 b 、 1 9 5 a 、 1 9 5 b を通じて方位制御電極 1 7 8 及び結合電極 1 7 6 による電界が横に広がるように方位制御電極 1 7 8 及び結合電極 1 7 6 と切開部 1 9 1 、 1 9 2 a 、 1 9 2 b 、 1 9 4 a 、 1 9 4 b 、 1 9 5 a 、 1 9 5 b が重なっている。切開部 1 9 1 、 1 9 2 a 、 1 9 2 b 、 1 9 4 a 、 1 9 4 b 、 1 9 5 a 、 1 9 5 b が重なっている。切開部 1 9 1 、 1 9 2 a 、 1 9 2 b 、 1 9 4 a 、 1 9 4 b 、 1 9 5 a 、 1 9 5 b が重気的プレチルトを有するようになり、電気的プレチルトを有する液晶分子は、画素電極の電界が印加されると乱れることなく電気的プレチルトにより定められた方位に速かに配向される。

[0063]

また、第1画素電極190aと第2画素電極190bに互いに異なる電位が印加されるようにすることで側面視認性を向上させることができる。

[0064]

このような構造の液晶表示装置に点(ドット)反転駆動を適用すれば、図8の上端部を通る前段ゲート線121(番号N-1)のオン信号によって、図示されている前段のトランジスタT2とT3が共にオンになり、方位制御電極178には正(+)極性の階調電圧が充電され、第1画素電極190aには負(-)極性の階調電圧が充電される。従って、方位制御電極178の初期電圧Vdceは、左右二つのデータ線から印加される正極性階調電圧と負極性階調電圧間の差となる。以後、図8の下端部を通る次段のゲート線(番号N)にオン信号が印加されて次段のT1がオンになるときは、T2及びT3は両方オフとなり方位制御電極178が浮遊状態に置かれることになるので、方位制御電極電圧は第1画素電極190aに充電される電圧VaとVdce・Va分の差を維持しながら共に上昇する。

[0065]

このように、第3の実施例による構造では、方位制御電極電圧が第1画素電極190aの電圧より常にVdce-Vaの分高くなることで液晶配列の電気的プレチルト角が確保される。

[0066]

ここで、図8を参照してVdceを求めれば次の通りである。次の数式を求めるにおいてゲート電極とドレーン電極との間の寄生容量は考慮していない。

V d c e = V d 1 + [ - C 3 x V d 1 + ( C 2 + C 3 ) V d 2 + C 2 x V d 3 ]/ ( C 2 + C 3 )

C 1 = C l c a + C s t + ( C d c e b x C l c b ) / ( C d c e b + C l c b )

C2 = Cdcea

C 3 = C d c

ここで、各トランジスタT1、T2、T3に印加される電圧は、それぞれVd1、Vd 2及び - Vd3である。

[0067]

一方、第1画素電極190aの電圧をVaとし、第2画素電極190bの電圧をVbとすれば、図8で電圧分配法則により、Vb = Va × Cd c e b / (Cd c e b + Cl c b )となる。ここで、Cd c e b / (Cd c e b + Cl c b )は常に1より小さいのでVaがVbより常に、パターン設計で定まる一定比率高い電圧を有するようになる。

10

20

30

40

#### [0068]

このように、一つの画素領域内で異なる電圧の二つの画素電極を配置することにより、 二つの画素電極が互いに補償し側面視認性を向上させる。

#### [0069]

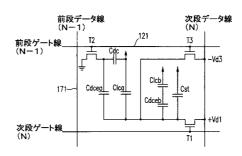

図9及び図10は、各々本発明の第4及び第5の実施例による液晶表示装置の回路図である。第4実施例は、図9のように、方位制御電極用薄膜トランジスタT2のソース電極が接地されていることが第3の実施例と異なる。ソース電極を接地させることはソース電極を維持電極線に連結することで可能となる。このためには、保護膜とゲート絶縁膜を貫通して、維持電極線を露出する接触孔と保護膜を貫通してソース電極を露出する接触孔を通じて両者を連結するソース電極連結部を保護膜上に形成することが必要である。

[0070]

ここで、図9を参照して V d c e を求めれば次の通りである。次の数式を求めるにおいて、ゲート電極とドレーン電極との間の寄生容量は考慮していない。

V d c e = V d 1 + [ - C 3 x V d 1 + C 2 x V d 3 ] / ( C 2 + C 3 )

$C1 = C1ca + Cst + (Cdceb \times C1cb) / (Cdceb + C1cb)$

C2 = Cdcea

C 3 = C d c

第5の実施例は、図10のように、第2画素電極用薄膜トランジスタT3のソース電極が接地されていることが第3の実施例と異なる。ソース電極を接地させることは、ソース電極を維持電極線に連結することで可能となる。このためには、保護膜とゲート絶縁膜を貫通して、維持電極線を露出する接触孔と保護膜を貫通してソース電極を露出する接触孔を通じて両者を連結するソース電極連結部を保護膜上に形成することが必要である。

[0071]

ここで、図10を参照してVdceを求めれば次の通りである。次の数式を求めるにおいてゲート電極とドレーン電極との間の寄生容量は考慮していない。

$V d c e = V d 1 + [ - C 3 \times V d 1 + ( C 2 + C 3 ) \times V d 2 ) ] / ( C 2 + C 3 )$

$C1 = C1ca + Cst + (Cdceb \times C1cb) / (Cdceb + C1cb)$

C 2 = C d c e a

C 3 = C d c

図11は本発明の第6の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図12は本発明の第6の実施例による液晶表示装置回路図である。

[0072]

第6の実施例による液晶表示装置用薄膜トランジスタ表示板は、第2画素電極用薄膜トランジスタが省略されたことが第3の実施例と異なる。

[0073]

ここで、図12を参照してVdceを求めると次の通りである。次の数式を求めるにおいてゲート電極とドレーン電極間の寄生容量は考慮していない。

V d c e = ( C 1 + C 3 ) [ ( 2 - C 3 / C 2 ) V d 1 + V d 2 ] / 2 C 2 + C 1

C 1 = C l c a + C s t + ( C d c e b x C l c b ) / ( C d c e b + C l c b )

C2 = Cdcea

C 3 = C d c

第3乃至第6の実施例による液晶表示装置では、結合電極176を利用して第1画素電極190aと第2画素電極190bを容量性で結合する。しかし、方位制御電極178を利用して第1画素電極190bを容量性で結合することもできる。以下、その方法について説明する。

[0074]

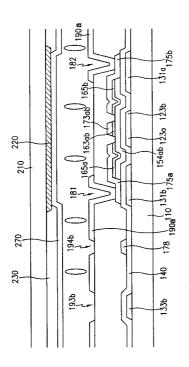

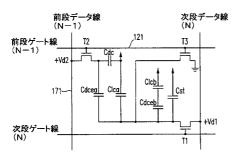

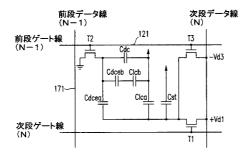

図13は本発明の第7の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図14は本発明の第7の実施例による液晶表示装置回路図である。

[0075]

本発明の第7の実施例による液晶表示装置も、薄膜トランジスタ表示板、これと対向す

10

20

30

40

る色フィルター表示板及びこれらの間に注入されている液晶層で構成される。薄膜トランジスタ表示板のゲート配線121、データ線171、維持電極線131などの基本配線構造及び3個の薄膜トランジスタT1、T2、T3も第3の実施例とほぼ同様である。

#### [0076]

しかし、第7の実施例では結合電極が省略され、方位制御電極178、178a、178bが第1画素電極190aは勿論、第2画素電極190bとも容量性で結合することが第3の実施例と異なる。

## [0077]

図14では、方位制御電極178、178a、178bと第1画素電極190aとの間の静電容量をCdcea、方位制御電極178、178a、178bと第2画素電極190bとの間の静電容量をCdceb、第1及び第2画素電極190a、190bと色フィルター表示板の共通電極270との間の液晶容量をそれぞれClca及びClcb、第1画素電極190aと維持電極線131a、131bとの間の容量をCst、方位制御電極178、178a、178bと共通電極270との間の静電容量をCdcと表示する。

## [0078]

第7の実施例による液晶表示装置の画素電極 1 9 0 a、 1 9 0 bも切開部 1 9 1、 1 9 2 a、 1 9 2 b、 1 9 4 a、 1 9 4 b、 1 9 5 a、 1 9 5 bを有し、この切開部 1 9 1、 1 9 2 a、 1 9 2 b、 1 9 4 a、 1 9 4 b、 1 9 5 a、 1 9 5 bを通じて方位制御電極 1 7 8、 1 7 8 a、 1 7 8 bによる電界が横に広がれるように方位制御電極 1 7 8、 1 7 8 a、 1 7 8 bと切開部 1 9 1、 1 9 2 a、 1 9 4 a、 1 9 4 b、 1 9 5 a、 1 9 5 bが重なっている。切開部 1 9 1、 1 9 2 a、 1 9 2 b、 1 9 4 a、 1 9 4 b、 1 9 5 a、 1 9 5 bを通じて広がる方位制御電極 1 7 8、 1 7 8 a、 1 7 8 bの電界によって液晶分子が電気的プレチルトを有するようになり、電気的プレチルトを有する液晶分子は画素電極の電界が印加されると乱れることなく電気的プレチルトにより定められた方位に速やかに配向される。

## [0079]

また、第1画素電極190aと第2画素電極190bに互いに異なる電位が印加されるようにすることで側面視認性を向上できる。

## [0800]

このような構造の液晶表示装置に点反転駆動を適用すれば、前段ゲート線(番号N-1)のオン信号によりT2とT3が共にオンとなり、方位制御電極178、178a、178bに正(+)極性の階調電圧が充電され、第1画素電極190aには負(-)極性の階調電圧が充電される。従って、方位制御電極178の初期電圧Vdceは、左右二つのデータ線から印加される正極性階調電圧と負極性階調電圧間の差異となる。以後、次段のゲート線(番号N)にオン信号が印加されT1がオンになる時は、T2及びT3は両方オフとなり方位制御電極178が浮遊状態に置かれるようになるので、方位制御電極電圧は、第1画素電極Va画素電極に充電される電圧とVdce・Va分の差を維持しながら共に上昇する。

## [0081]

このように、第7の実施例による構造では、方位制御電極電圧が第1画素電極190aの電圧より常にVdce-Va分高くなることで、液晶配列の電気的プレチルト角が確保される。

## [0082]

ここで、図14を参照してVdceを求めれば次の通りである。次の数式を求めるにおいて、ゲート電極とドレーン電極間の寄生容量は考慮していない。

V d c e = V d 1 + [ - C 3 x V d 1 + ( C 2 + C 3 ) V d 2 + C 2 x V d 3 ]/ ( C 2 + C 3 )

C1 = Clca + Cst

C2 = Cdcea

C 3 = C d c + ( C d c e b x C l c b ) / ( C d c e b + C l c b )

10

20

30

40

(13)

一方、方位制御電極 1 7 8  $\times$  1 7 8 a  $\times$  1 7 8 b の電圧を V d c e  $\times$  第 2 画素電極 1 9 0 b の電圧を V b とすれば、図 1 4 で、電圧分配法則により V b = V d c e  $\times$  C d c e b / (C d c e b + C l c b ) となる。このように、一つの画素領域内に異なる電圧の二つの画素電極を配置することで、二つの画素電極が互いに補償し側面視認性を向上させる。【 0 0 8 3 】

図 1 5 及び図 1 6 は各々本発明の第 8 及び第 9 の実施例による液晶表示装置回路図である。

# [0084]

第8の実施例は、図15のように、方位制御電極用薄膜トランジスタT2のソース電極が接地されていることが第7の実施例と異なる。ソース電極を接地させることは、ソース電極を維持電極線に連結することで可能となる。このためには、保護膜とゲート絶縁膜を貫通して維持電極線を露出する接触孔と保護膜を貫通してソース電極を露出する接触孔を通じて両者を連結するソース電極連結部を保護膜上に形成することが必要である。

#### [0085]

ここで、図15を参照してVdceを求めれば次の通りである。次の数式を求めるにおいてゲート電極とドレーン電極間の寄生容量は考慮していない。

$V d c e = V d 1 + [ - C 3 \times V d 1 + C 2 \times V d 3 ] / ( C 2 + C 3 )$

C1 = Clca + Cst

C2 = Cdcea

C 3 = C d c + (C d c e b x C l c b)/(C d c e b + C l c b)

第9の実施例は、図16のように、第2画素電極用薄膜トランジスタT3のソース電極が接地されていることが第7の実施例と異なる。ソース電極を接地させることは、ソース電極を維持電極線に連結することで可能となる。このためには、保護膜とゲート絶縁膜を貫通して維持電極線を露出する接触孔と保護膜を貫通してソース電極を露出する接触孔を通じて両者を連結するソース電極連結部を保護膜上に形成することが必要である。

## [0086]

ここで、図16を参照してVdceを求めれば次の通りである。次の数式を求めるにおいてゲート電極とドレーン電極間の寄生容量は考慮していない。

V d c e = V d 1 + [ - C 3 x V d 1 + ( C 2 + C 3 ) V d 2 ) ]/ ( C 2 + C 3 )

C1 = Clca + Cst

C2 = Cdcea

C 3 = C d c + ( C d c e b x C l c b ) / ( C d c e b + C l c b )

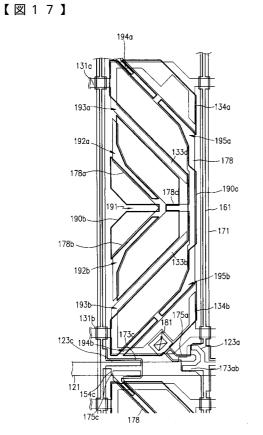

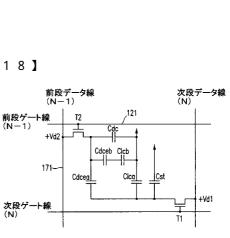

図17は本発明の第10の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図18は本発明の第10の実施例による液晶表示装置回路図である。第10の実施例による液晶表示装置用薄膜トランジスタ表示板は、第2画素電極用薄膜トランジスタが省略されたことが第7の実施例と異なり、それ以外の構造は同様である。

# [0087]

ここで、図18を参照してVdceを求めれば次の通りである。次の数式を求めるにおいてゲート電極とドレーン電極間の寄生容量は考慮していない。

V d c e = ( C 1 + C 3 ) [ ( 2 - C 3 / C 2 ) V d 1 + V d 2 ] / ( 2 C 2 + C 1 )

C1 = Clca + Cst

C2 = Cdcea

C 3 = C d c + ( C d c e b x C l c b ) / ( C d c e b + C l c b )

以上、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されず、請求の範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態も本発明の権利範囲に属するものである。

## 【図面の簡単な説明】

### [0088]

【図1】本発明の第1の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。

10

20

30

30

50

- 【図2】図1のII-II'線に沿った断面図である。

- 【図3】図1のIII-III ′線に沿った断面図である。

- 【図4】本発明の第1の実施例による液晶表示装置回路図である。

- 【図5】本発明の第2の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。

- 【図6】本発明の第3の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。

- 【図7】図6のVII-VII′線に沿った断面図である。

- 【図8】本発明の第3実施例による液晶表示装置回路図である。

- 【図9】本発明の第4実施例による液晶表示装置回路図である。

- 【図10】本発明の第5実施例による液晶表示装置回路図である。

- 【図11】本発明の第6の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。

- 【図12】本発明の第6の実施例による液晶表示装置回路図である。

- 【図13】本発明の第7の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。

- 【図14】本発明の第7実施例による液晶表示装置回路図である。

- 【図15】本発明の第8実施例による液晶表示装置回路図である。

- 【図16】本発明の第9実施例による液晶表示装置回路図である。

- 【図17】本発明の第10の実施例による液晶表示装置用薄膜トランジスタ表示板の配置 20 図である。

- 【図18】本発明の第10の実施例による液晶表示装置の回路図である。

【符号の説明】

[0089]

3 液晶層

- 110、210 基板

- 121 ゲート線

- 1 2 3 c ゲート電極

- 1 4 0 ゲート絶縁膜

- 151、154c 半導体層

- 171 データ線

- 173c ソース電極

- 175 c ドレーン電極

- 176 結合電極

- 178 方位制御電極

- 180 保護膜

- 190a、190b 画素電極

- 191、192a、192b、194a、194b、195a、195b切開部

- 230 色フィルター

- 270 共通電極

40

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図16】

前段データ線 (N-1)

171-

次段ゲート線 (N)

次段データ線 (N)

T3

# 【図14】

【図15】

# 【図18】

## フロントページの続き

(72) 発明者 洪 性 奎

大韓民国京畿道城南市盆唐区野塔洞512番地東亜ビラ513棟403号

(72)発明者 梁 英 チョル

大韓民国京畿道軍浦市衿井洞住公アパート2団地220棟1201号

(72)発明者 金 鍾 来

大韓民国ソウル市松坡区文井洞44-7番地現代パークビル401号

(72)発明者 申 キョン 周

大韓民国京畿道龍仁市器興邑甫羅里289-12番地サンジョンソンビマウル102棟504号

(72)発明者 金 熙 燮

大韓民国京畿道化城市台安邑半月里865-1番地新霊通現代アパート110棟304号

# 審査官 前川 慎喜

(56)参考文献 特開2001-235752(JP,A)

特開2001-235751(JP,A)

特開2002-258307(JP,A)

特開2001-249350(JP,A)

特開2002-122887(JP,A)

特開2002-055343(JP,A)

(58)調査した分野(Int.CI., DB名)

G02F 1/13 - 1/141

| 专利名称(译)        | 用于多域液晶显示器件的薄膜晶体管显示器面板                                                                                                                                                                                                                              |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | JP4452513B2                                                                                                                                                                                                                                        | 公开(公告)日 | 2010-04-21 |

| 申请号            | JP2004000026                                                                                                                                                                                                                                       | 申请日     | 2004-01-05 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                           |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 洪性奎<br>梁英チョル<br>金鍾来<br>申キョン周<br>金熙燮                                                                                                                                                                                                                |         |            |

| 发明人            | 洪性奎<br>梁英▲チョル▼<br>金鍾来<br>申▲キョン▼ 周                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368 G02F1/1337 G02F1/1333 G02F1/1362 G02F1/139 H01L29/04 H01L31/20                                                                                                                                                               |         |            |

| CPC分类号         | G02F1/133707 G02F1/134336 G02F1/136213 G02F1/1393 G02F2001/134345 G02F2001/134354                                                                                                                                                                  |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/JA26 2H092/JB05 2H092/JB06 2H092/JB41 2H092/JB69 2H092/NA01 2H092 /NA27 2H092/QA09 2H192/AA24 2H192/BA25 2H192/BC23 2H192/BC24 2H192/CB05 2H192/CB45 2H192/CC04 2H192/CC42 2H192/DA12 2H192/EA22 2H192/EA43 2H192/FA65 2H192/JA13 |         |            |

| 优先权            | 1020030000266 2003-01-03 KR                                                                                                                                                                                                                        |         |            |

| 其他公开文献         | JP2004213011A                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                   |         |            |

# 摘要(译)

要解决的问题:提供一种液晶显示装置,其制造工艺简单并且形成稳定的多畴。解决方案:具有切口部分的第一和第二像素电极形成在由栅极线和数据线的交叉限定的像素区域中,并且方向控制电极与这两个像素电极的切口部分重叠形成了。在取向控制电极连接到所述薄膜晶体管被连接到从第一像素电极之间形成的电容的栅极线和数据线,定向控制电极和方位控制电极和第二像素电极并且调整重叠区域,使得由预定量形成的静电电容的大小增加。通过这样做,改善了域的稳定性,并且通过形成在一个像素区域中施加不同电压的两个像素电极,可以提高侧面可视性。 点域1