(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-293048

(P2008-293048A)

(43) 公開日 平成20年12月4日(2008.12.4)

| (51) Int.Cl.                 | F 1            | テーマコード (参考) |

|------------------------------|----------------|-------------|

| <b>G09F 9/30 (2006.01)</b>   | G09F 9/30 338  | 2H092       |

| <b>G02F 1/1368 (2006.01)</b> | G09F 9/30 330Z | 5C094       |

| <b>G02F 1/1345 (2006.01)</b> | G02F 1/1368    |             |

|                              | G02F 1/1345    |             |

審査請求 有 請求項の数 4 O L (全 16 頁)

|            |                              |            |                                                                                                                             |

|------------|------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号  | 特願2008-217572 (P2008-217572) | (71) 出願人   | 000001443<br>カシオ計算機株式会社<br>東京都渋谷区本町1丁目6番2号                                                                                  |

| (22) 出願日   | 平成20年8月27日 (2008.8.27)       | (72) 発明者   | 中村 やよい<br>東京都八王子市石川町2951番地の5<br>カシオ計算機株式会社八王子技術センター<br>内                                                                    |

| (62) 分割の表示 | 特願2006-142342 (P2006-142342) |            |                                                                                                                             |

| の分割        |                              |            |                                                                                                                             |

| 原出願日       | 平成18年5月23日 (2006.5.23)       | F ターム (参考) | 2H092 GA32 JA26 JA28 JA34 JA37<br>JA41 JA46 JA47 JB22 JB31<br>JB79 NA14 NA25<br>5C094 AA15 BA03 BA27 BA43 DA09<br>DB01 EA10 |

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】スイッチング用薄膜トランジスタを静電気から保護するための静電気保護用薄膜トランジスタを備えた液晶表示装置において、額縁面積を小さくする。

【解決手段】走査ライン駆動用ドライバ搭載領域11内に、走査ライン用静電気保護ライン31、第1、第2の走査ライン用静電気保護用薄膜トランジスタ32、33および接続用薄膜トランジスタ34を設けると、これらを配置するためのそれ専用の配置領域が不要となり、それに応じて額縁面積を小さくすることができる。また、データライン駆動用ドライバ搭載領域14内に、データライン用静電気保護ライン41、データライン用静電気保護用薄膜トランジスタ42および第1、第2の接続用薄膜トランジスタ43、44を設けると、これらを配置するためのそれ専用の配置領域が不要となり、それに応じて額縁面積を小さくすることができる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

基板上の表示領域に、マトリクス状に配置された複数の表示素子と、前記各表示素子に接続されたスイッチング用薄膜トランジスタと、前記各スイッチング用薄膜トランジスタに走査信号を供給するための走査ラインと、前記各スイッチング用薄膜トランジスタにデータ信号を供給するためのデータラインとが設けられ、前記基板上の前記表示領域の外側の走査ライン駆動用ドライバ搭載領域内に、前記走査ラインに接続された走査ライン用静電気保護回路が設けられていることを特徴とする表示装置。

**【請求項 2】**

請求項 1 に記載の発明において、前記走査ライン用静電気保護回路は、走査ライン用静電気保護ラインと、該走査ライン用静電気保護ラインと前記各走査ラインとの間に配置された走査ライン用静電気保護素子とを有することを特徴とする表示装置。 10

**【請求項 3】**

請求項 2 に記載の発明において、前記走査ライン用静電気保護素子は、前記走査ラインに生じた静電気によって導通し、該静電気を前記走査ラインから前記走査ライン用静電気保護ラインに向けて流すダイオード接続型の薄膜トランジスタであることを特徴とする表示装置。

**【請求項 4】**

請求項 3 に記載の発明において、前記走査ライン用静電気保護素子は、さらに、前記走査ライン用静電気保護ラインと前記各走査ラインとの間に前記ダイオード接続型の薄膜トランジスタと並列に配置されたフローティングゲート型の薄膜トランジスタを有することを特徴とする表示装置。 20

**【請求項 5】**

請求項 2 に記載の発明において、前記走査ライン用静電気保護回路は、前記基板上の表示領域の周囲に設けられた方形枠状の共通ラインと前記走査ライン用静電気保護ラインとの間に設けられ、前記走査ライン用静電気保護ラインが高電位となったときに導通する接続用素子を有することを特徴とする表示装置。

**【請求項 6】**

請求項 1 に記載の発明において、前記基板上の前記表示領域の外側のデータライン駆動用ドライバ搭載領域内に、前記データラインに接続されたデータライン用静電気保護回路が設けられていることを特徴とする表示装置。 30

**【請求項 7】**

基板上の表示領域に、マトリクス状に配置された複数の表示素子と、前記各表示素子に接続されたスイッチング用薄膜トランジスタと、前記各スイッチング用薄膜トランジスタに走査信号を供給するための走査ラインと、前記各スイッチング用薄膜トランジスタにデータ信号を供給するためのデータラインとが設けられ、前記基板上の前記表示領域の外側のデータライン駆動用ドライバ搭載領域内に、前記データラインに接続されたデータライン用静電気保護回路が設けられていることを特徴とする表示装置。

**【請求項 8】**

請求項 6 または 7 に記載の発明において、前記データライン用静電気保護回路は、データライン用静電気保護ラインと、該データライン用静電気保護ラインと前記各データラインとの間に配置されたデータライン用静電気保護素子とを有することを特徴とする表示装置。 40

**【請求項 9】**

請求項 8 に記載の発明において、前記データライン用静電気保護素子はフローティングゲート型の薄膜トランジスタであることを特徴とする表示装置。

**【請求項 10】**

請求項 6 または 7 に記載の発明において、前記データライン用静電気保護回路は、前記基板上の表示領域の周囲に設けられた方形枠状の共通ラインと前記データライン用静電気保護ラインとの間に設けられ、前記データライン用静電気保護ラインと前記共通ラインと

10

20

30

40

50

の間に導通可能な電位差が生じたときに導通する接続用素子を有することを特徴とする表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は表示装置に関する。

【背景技術】

【0002】

例えば、従来のアクティブマトリックス型の液晶表示装置には、スイッチング用薄膜トランジスタの静電気に起因する特性シフトや絶縁破壊等の不良を防止するために、マトリックス状に設けられた複数の走査ラインと複数のデータラインとの各交点近傍に画素電極および該画素電極に接続されたスイッチング用薄膜トランジスタが設けられた表示領域の外側に、走査ライン用静電気保護ラインおよび該走査ライン用静電気保護ラインと各走査ラインとの間に設けられた走査ライン用静電気保護用薄膜トランジスタと、データライン用静電気保護ラインおよび該データライン用静電気保護ラインと各データラインとの間に設けられたデータライン用静電気保護用薄膜トランジスタとを設けたものがある（例えば、特許文献1参照）。

【0003】

【特許文献1】特開2005-93459号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上記従来の液晶表示装置では、表示領域の外側に走査ライン用静電気保護ラインおよび走査ライン用静電気保護用薄膜トランジスタとデータライン用静電気保護ラインおよびデータライン用静電気保護用薄膜トランジスタとを設けているので、これらの配置領域を確保するため、額縁面積が大きくなってしまうという問題があった。

【0005】

そこで、この発明は、額縁面積を小さくすることができる表示装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するため、請求項1に記載の発明は、基板上の表示領域に、マトリックス状に配置された複数の表示素子と、前記各表示素子に接続されたスイッチング用薄膜トランジスタと、前記各スイッチング用薄膜トランジスタに走査信号を供給するための走査ラインと、前記各スイッチング用薄膜トランジスタにデータ信号を供給するためのデータラインとが設けられ、前記基板上の前記表示領域の外側の走査ライン駆動用ドライバ搭載領域内に、前記走査ラインに接続された走査ライン用静電気保護回路が設けられていることを特徴とするものである。

請求項7に記載の発明は、基板上の表示領域に、マトリックス状に配置された複数の表示素子と、前記各表示素子に接続されたスイッチング用薄膜トランジスタと、前記各スイッチング用薄膜トランジスタに走査信号を供給するための走査ラインと、前記各スイッチング用薄膜トランジスタにデータ信号を供給するためのデータラインとが設けられ、前記基板上の前記表示領域の外側のデータライン駆動用ドライバ搭載領域内に、前記データラインに接続されたデータライン用静電気保護回路が設けられていることを特徴とするものである。

【発明の効果】

【0007】

請求項1に記載の発明によれば、基板上の表示領域の外側の走査ライン駆動用ドライバ搭載領域内に走査ライン用静電気保護回路を設けているので、走査ライン用静電気保護回路を配置するためのそれ専用の配置領域が不要となり、それに応じて額縁面積を小さくす

10

20

30

40

50

ることができる。

請求項 7 に記載の発明によれば、基板上の表示領域の外側のデータライン駆動用ドライバ搭載領域内にデータライン用静電気保護回路を設けているので、データライン用静電気保護回路を配置するためのそれ専用の配置領域が不要となり、それに応じて額縁面積を小さくすることができる。

【発明を実施するための最良の形態】

【0008】

(第1実施形態)

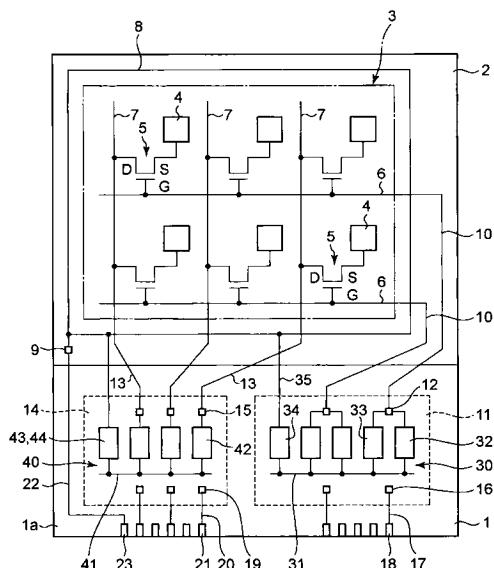

図1はこの発明の第1実施形態としての液晶表示装置の要部の等価回路的平面図を示す。この液晶表示装置は、アクティブ基板1と該アクティブ基板1の上方に位置する対向基板2とがほぼ方形枠状のシール材(図示せず)を介して貼り合わされ、シール材の内側における両基板1、2間に液晶(図示せず)が封入されたものからなっている。この場合、アクティブ基板1の下辺部は対向基板2から突出されている。以下、この突出された部分を突出部1aという。また、図1において一点鎖線で囲まれた方形状の領域は表示領域3となっている。

10

【0009】

アクティブ基板1上の表示領域3には、マトリックス状に配置された複数の画素電極4と、各画素電極4に接続されたソース電極Sを有するnMOS型のスイッチング用薄膜トランジスタ5と、行方向に延ばされ、各スイッチング用薄膜トランジスタ5のゲート電極Gに走査信号を供給するための走査ライン6と、各スイッチング用薄膜トランジスタ5のドレイン電極Dにデータ信号を供給するためのデータライン7とが設けられている。

20

【0010】

ここで、図1において、画素電極4は僅かに2個×3個だけ図示しているのは図面の明確化のためであり、実際には数百個×数百個もしくはそれ以上の個数が配列されている。アクティブ基板1上の表示領域3の周囲には方形枠状の共通ライン8およびこれに接続された共通接続パッド9が設けられている。共通接続パッド9は、対向基板2の下面に設けられた共通電極(図示せず)に基板間導通材(図示せず)を介して接続されている。

20

【0011】

走査ライン6の右端部は、表示領域3の右側および下側に設けられた走査用引き回し線10を介して、アクティブ基板1の突出部1a上の右側の点線で示す走査ライン駆動用ドライバ搭載領域11内の上側に設けられた走査用出力端子12に接続されている。データライン7の下端部は、表示領域3の下側に設けられたデータ用引き回し線13を介して、アクティブ基板1の突出部1a上の左側の点線で示すデータライン駆動用ドライバ搭載領域14内の上側に設けられたデータ用出力端子15に接続されている。

30

【0012】

走査ライン駆動用ドライバ搭載領域11内の下側には走査用入力端子16が設けられている。走査用入力端子16は、その下側に設けられた走査用引き回し線17を介して、その下側に設けられた走査用外部接続端子18に接続されている。データライン駆動用ドライバ搭載領域14内の下側にはデータ用入力端子19が設けられている。データ用入力端子19は、その下側に設けられたデータ用引き回し線20を介して、その下側に設けられたデータ用外部接続端子21に接続されている。共通接続パッド9は、その下側に設けられた共通引き回し線22を介して、その下側に設けられたが共通外部接続端子23に接続されている。

40

【0013】

なお、図面の明確化のために、図示は省略しているが、アクティブ基板1の走査ライン駆動用ドライバ搭載領域11上には走査用入力端子16および走査用出力端子12に対応する外部電極を有する走査ライン駆動回路部を内蔵する走査ライン駆動チップが搭載され、走査ライン駆動チップの外部電極と走査用入力端子16、および走査ライン駆動チップの外部電極と走査用出力端子12とはCOG(チップオングラス)法によりボンディングされている。ボンディング方法は半田付けによる方法でもよいし、異方性導電接着材によ

50

る方法でもよい。

【0014】

また、アクティブ基板1のデータライン駆動用ドライバ搭載領域14上には、データライン駆動回路部を内蔵するデータライン駆動チップが搭載され、データライン駆動チップの外部電極とデータ用入力端子19、およびデータライン駆動チップの外部電極とデータ用出力端子15とはCOG(チップオングラス)法によりボンディングされている。この場合も、ボンディング方法は半田付けによる方法でもよいし、異方性導電接着材による方法でもよい。

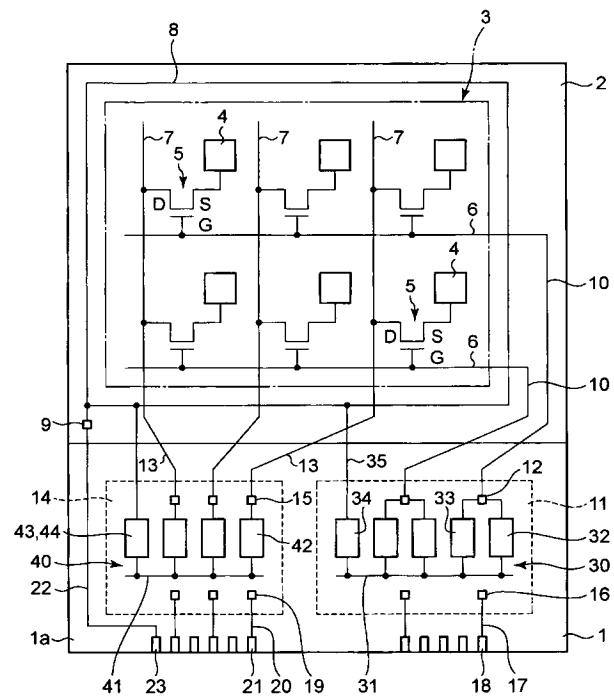

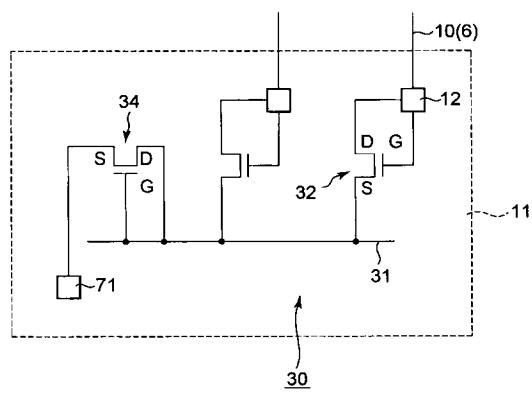

【0015】

次に、図2は走査ライン駆動用ドライバ搭載領域11に設けられた走査ライン用静電気保護回路30の部分の等価回路的平面図を示す。走査ライン駆動用ドライバ搭載領域11内には走査ライン用静電気保護ライン31が設けられている。走査ライン用静電気保護ライン31と各走査用出力端子12(つまり図1に示す走査ライン6に接続された走査用引き回し線10)との間には第1、第2の走査ライン用静電気保護用薄膜トランジスタ(走査ライン用静電気保護素子)32、33が並列に設けられている。

10

【0016】

この場合、第1の走査ライン用静電気保護用薄膜トランジスタ32はダイオード接続型のnMOS型であり、ゲート電極Gおよびドレイン電極Dは走査用出力端子12に接続され、ソース電極Sは走査ライン用静電気保護ライン31に接続されている。第2の走査ライン用静電気保護用薄膜トランジスタ33はフローティングゲート型であり、ゲート電極Gはどこも接続されておらず、フローティングゲートとなっており、ドレイン電極Dは走査用出力端子12に接続され、ソース電極Sは走査ライン用静電気保護ライン31に接続されている。

20

【0017】

走査ライン用静電気保護ライン31の一端部は、接続用薄膜トランジスタ34および接続用引き回し線35を介して、図1に示す共通ライン8に接続されている。この場合、接続用薄膜トランジスタ34のゲート電極Gおよびドレイン電極Dは走査ライン用静電気保護ライン31に接続され、ソース電極Sは接続用引き回し線35を介して共通ライン8に接続されている。

30

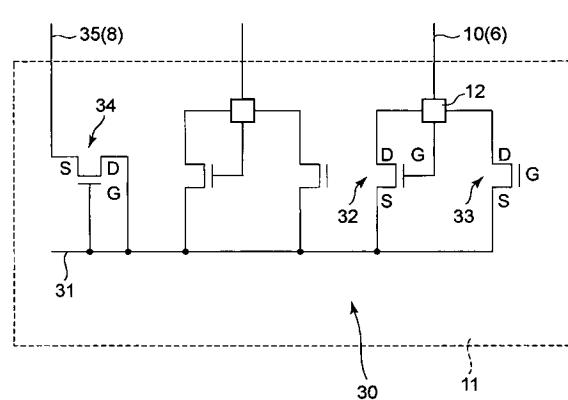

【0018】

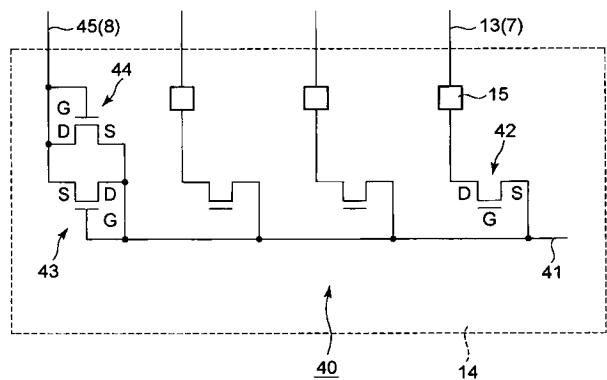

次に、図3はデータライン駆動用ドライバ搭載領域14に設けられたデータライン用静電気保護回路40の部分の等価回路的平面図を示す。データライン駆動用ドライバ搭載領域14内にはデータライン用静電気保護ライン41が設けられている。データライン用静電気保護ライン41と各データ用出力端子15(つまり図1に示すデータライン7に接続されたデータ用引き回し線13)との間にはフローティングゲート型のデータライン用静電気保護用薄膜トランジスタ(データライン用静電気保護素子)42が設けられている。

【0019】

この場合、データライン用静電気保護用薄膜トランジスタ42のゲート電極Gはどこも接続されておらず、フローティングゲートとなっており、ドレイン電極Dはデータ用出力端子15に接続され、ソース電極Sはデータライン用静電気保護ライン41に接続されている。

40

【0020】

データライン用静電気保護ライン41の一端部は、並列に設けられた第1、第2の接続用薄膜トランジスタ43、44(接続用素子)および接続用引き回し線45を介して、図1に示す共通ライン8に接続されている。この場合、第1の接続用薄膜トランジスタ43のゲート電極Gおよびドレイン電極Dはデータライン用静電気保護ライン41に接続され、ソース電極Sは接続用引き回し線45を介して共通ライン8に接続されている。第2の接続用薄膜トランジスタ44のゲート電極Gおよびドレイン電極Dは接続用引き回し線45を介して共通ライン8に接続され、ソース電極Sはデータライン用静電気保護ライン41に接続されている。

50

## 【0021】

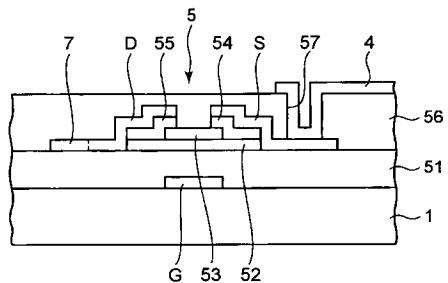

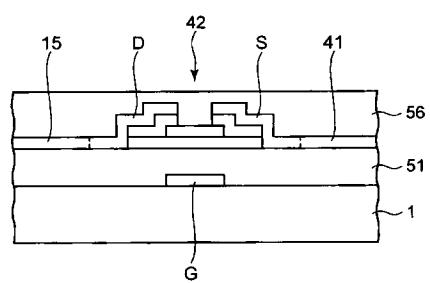

次に、この液晶表示装置の一部の具体的な構造について説明する。まず、図4はスイッチング用薄膜トランジスタ5および画素電極4の部分の断面図を示す。ガラス等からなるアクティブ基板1の上面の所定の箇所にはクロム等からなるゲート電極G、該ゲート電極Gに接続された走査ライン6(図1参照)および該走査ライン6に接続された走査用引き回し線10(図1参照)が設けられている。

## 【0022】

ゲート電極Gおよび走査ライン6等を含むアクティブ基板1の上面には窒化シリコンからなるゲート絶縁膜51が設けられている。ゲート電極G上におけるゲート絶縁膜51の上面の所定の箇所には真性アモルファスシリコンからなる半導体薄膜52が設けられている。半導体薄膜52の上面ほぼ中央部には窒化シリコンからなるチャネル保護膜53が設けられている。

10

## 【0023】

チャネル保護膜53の上面両側およびその両側における半導体薄膜52の上面にはn型アモルファスシリコンからなるオーミックコンタクト層54、55が設けられている。一方のオーミックコンタクト層54の上面およびその近傍のゲート絶縁膜51の上面の所定の箇所にはクロム等からなるソース電極Sが設けられている。他方のオーミックコンタクト層55の上面およびゲート絶縁膜51の上面の所定の箇所にはクロム等からなるドレイン電極D、該ドレイン電極Dに接続されたデータライン7および該データライン7に接続されたデータ用引き回し線13(図1参照)が設けられている。

20

## 【0024】

ここで、スイッチング用薄膜トランジスタ5は、ゲート電極G、ゲート絶縁膜51、半導体薄膜52、チャネル保護膜53、オーミックコンタクト層54、55、ソース電極Sおよびドレイン電極Dにより構成されている。

## 【0025】

スイッチング用薄膜トランジスタ5およびデータライン7等を含むゲート絶縁膜51の上面には窒化シリコンからなるオーバーコート膜56が設けられている。オーバーコート膜56の上面の所定の箇所にはITO等の透明導電材料からなる画素電極4が設けられている。画素電極4は、オーバーコート膜56の所定の箇所に設けられたコンタクトホール57を介してソース電極Sに接続されている。

30

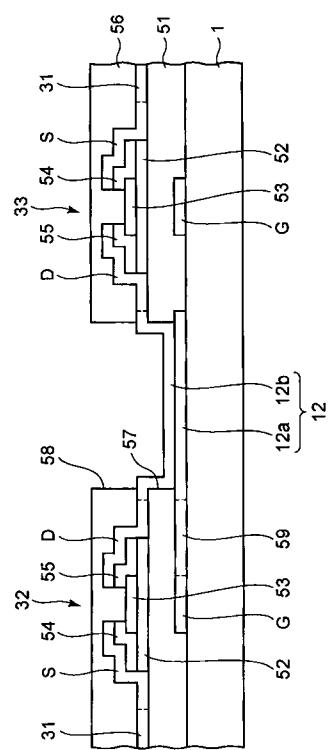

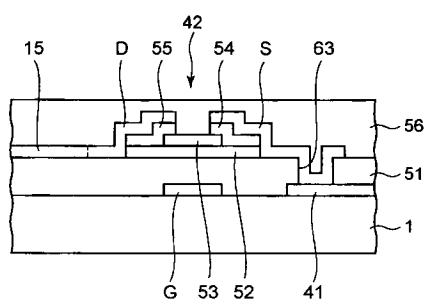

## 【0026】

次に、図5は走査ライン駆動用ドライバ搭載領域11内の第1、第2の走査ライン用静電気保護用薄膜トランジスタ32、33、走査用出力端子12および走査ライン用静電気保護ライン31の部分の断面図を示す。第1、第2の走査ライン用静電気保護用薄膜トランジスタ32、33は、図4に示すスイッチング用薄膜トランジスタ5とほぼ同じ構造であり、ゲート電極G、ゲート絶縁膜51、半導体薄膜52、チャネル保護膜53、オーミックコンタクト層54、55、ソース電極Sおよびドレイン電極Dからなっている。

## 【0027】

走査用出力端子12は、アクティブ基板1の上面に設けられたクロム等からなる下層金属層12aと、ゲート絶縁膜51に設けられたコンタクトホール57を介して露出された下層金属層12aの上面およびその周囲におけるゲート絶縁膜51の上面に設けられたクロム等からなる上層金属層12bとの2層構造となっており、オーバーコート膜56に設けられた開口部58を介して露出されている。走査ライン用静電気保護ライン31は、ゲート絶縁膜51の上面に設けられたクロム等の金属層からなっている。

40

## 【0028】

そして、第1の走査ライン用静電気保護用薄膜トランジスタ32のゲート電極Gは、アクティブ基板1の上面に設けられたクロム等からなる引き回し線59を介して、走査用出力端子12の下層金属層12aに接続され、ドレイン電極Dは走査用出力端子12の上層金属層12bに接続され、ソース電極Sは走査ライン用静電気保護ライン31に接続されている。第2の走査ライン用静電気保護用薄膜トランジスタ33のゲート電極Gはフロー

50

タイミングゲートとなっており(図2参照)、ドレイン電極Dは走査用出力端子12の上層金属層12bに接続され、ソース電極Sは走査ライン用静電気保護ライン31に接続されている。

【0029】

次に、図6は走査ライン駆動用ドライバ搭載領域11内の接続用薄膜トランジスタ34、走査ライン用静電気保護ライン31および共通引き回し線35の部分の断面図を示す。接続用薄膜トランジスタ34は、図4に示すスイッチング用薄膜トランジスタ5とほぼ同じ構造であり、ゲート電極G、ゲート絶縁膜51、半導体薄膜52、チャネル保護膜53、オーミックコンタクト層54、55、ソース電極Sおよびドレイン電極Dからなっている。共通引き回し線35は、アクティブ基板1の上面に設けられたクロム等の金属層からなっている。

10

【0030】

そして、ゲート絶縁膜51の上面に設けられた走査ライン用静電気保護ライン31の一端部は、ゲート絶縁膜51に設けられたコンタクトホール60を介して、アクティブ基板1の上面にゲート電極Gに接続されて設けられたクロム等からなる引き回し線61に接続され、且つ、接続用薄膜トランジスタ34のドレイン電極Dに接続されている。接続用薄膜トランジスタ34のソース電極Sは、ゲート絶縁膜51に設けられたコンタクトホール62を介して共通引き回し線35に接続されている。

20

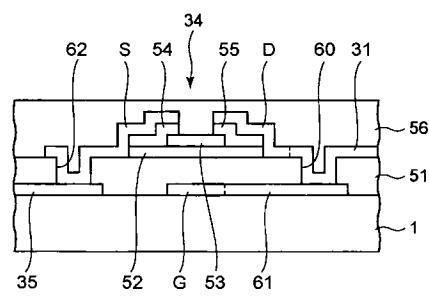

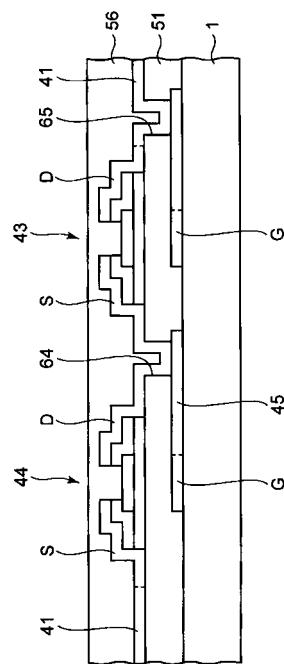

【0031】

次に、図7はデータライン駆動用ドライバ搭載領域14内のデータライン用静電気保護用薄膜トランジスタ42、データ用出力端子15およびデータライン用静電気保護ライン41の部分の断面図を示す。データライン用静電気保護用薄膜トランジスタ42は、図4に示すスイッチング用薄膜トランジスタ5とほぼ同じ構造であり、ゲート電極G、ゲート絶縁膜51、半導体薄膜52、チャネル保護膜53、オーミックコンタクト層54、55、ソース電極Sおよびドレイン電極Dからなっている。

20

【0032】

データ用出力端子15は、ゲート絶縁膜51の上面に設けられたクロム等の金属層からなっている。データライン用静電気保護ライン41は、アクティブ基板1の上面に設けられたクロム等の金属層からなっている。そして、データライン用静電気保護用薄膜トランジスタ42のゲート電極Gはフローティングゲートとなっており(図3参照)、ドレイン電極Dはデータ用出力端子15に接続され、ソース電極Sはゲート絶縁膜51に設けられたコンタクトホール63を介してデータライン用静電気保護ライン41に接続されている。

30

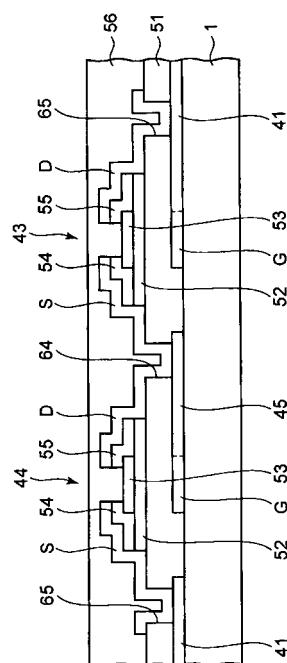

【0033】

次に、図8はデータライン駆動用ドライバ搭載領域14内の第1、第2の接続用薄膜トランジスタ43、44、データライン用静電気保護ライン41および共通引き回し線45の部分の断面図を示す。第1、第2の接続用薄膜トランジスタ43、44は、図4に示すスイッチング用薄膜トランジスタ5とほぼ同じ構造であり、ゲート電極G、ゲート絶縁膜51、半導体薄膜52、チャネル保護膜53、オーミックコンタクト層54、55、ソース電極Sおよびドレイン電極Dからなっている。共通引き回し線45は、アクティブ基板1の上面に設けられたクロム等の金属層からなっている。

40

【0034】

そして、第1の接続用薄膜トランジスタ43のゲート電極Gはデータライン用静電気保護ライン41に接続されている。第2の接続用薄膜トランジスタ44のゲート電極Gは共通引き回し線45に接続されている。第1の接続用薄膜トランジスタ43のソース電極Sおよび第2の接続用薄膜トランジスタ44のドレイン電極Dは、ゲート絶縁膜51に設けられたコンタクトホール64を介して共通引き回し線45に接続されている。第1の接続用薄膜トランジスタ43のドレイン電極Dおよび第2の接続用薄膜トランジスタ44のソース電極Sは、ゲート絶縁膜51に設けられた同一のコンタクトホール65(図8では図示の都合上別々となっている)を介して、データライン用静電気保護ライン41に接続さ

50

れている。

【0035】

ところで、この液晶表示装置では、図1に示すように、アクティブ基板1上の表示領域3の外側の突出部1a上の走査ライン駆動用ドライバ搭載領域11内に、走査ライン用静電気保護ライン31、第1、第2の走査ライン用静電気保護用薄膜トランジスタ32、33および接続用薄膜トランジスタ34を設けているので、これらを配置するためのそれ専用の配置領域が不要となり、それに応じて額縁面積を小さくすることができる。

【0036】

また、この液晶表示装置では、図1に示すように、アクティブ基板上1の表示領域3の外側の突出部1a上のデータライン駆動用ドライバ搭載領域14内に、データライン用静電気保護ライン41、データライン用静電気保護用薄膜トランジスタ42および第1、第2の接続用薄膜トランジスタ43、44を設けているので、これらを配置するためのそれ専用の配置領域が不要となり、それに応じて額縁面積を小さくすることができる。

10

【0037】

次に、上記構成の液晶表示装置の静電気保護動作について説明する。この場合、スイッチング用薄膜トランジスタ5の静電気による不良は、正の静電気が侵入した場合のみであるため、静電気が正の場合について説明する。

【0038】

ある1本の走査ライン6に外部から何らかの理由により正の静電気が侵入したとする。すると、当該走査ライン6に走査用引き回し線10および走査用出力端子12を介して接続された走査ライン用静電気保護用薄膜トランジスタ32がオン状態となり、当該走査ライン6から電流がそれに接続された走査ライン用静電気保護用薄膜トランジスタ32を介して走査ライン用静電気保護ライン31に流れ、走査ライン用静電気保護ライン31が高電位となる。

20

【0039】

走査ライン用静電気保護ライン31が高電位になると、残りの走査ライン6に接続された第2の走査ライン用静電気保護用薄膜トランジスタ33が導通状態となり、走査ライン用静電気保護ライン31から電流が第2の走査ライン用静電気保護用薄膜トランジスタ33を介して残りの走査ライン6に流れ、すべての走査ライン6が同電位となる。

30

【0040】

また、走査ライン用静電気保護ライン31が高電位になると、接続用薄膜トランジスタ34がオン状態となり、走査ライン用静電気保護ライン31から電流が接続用薄膜トランジスタ34を介して共通ライン8に流れ、さらに、共通接続パッド9および基板間導通材を介して対向基板2の対向電極に流れる。かくして、走査ライン6に外部から何らかの理由により侵入した正の静電気は放電され、スイッチング用薄膜トランジスタ5の静電気に起因する特性シフトや絶縁破壊等の不良が防止される。

【0041】

この場合、ダイオード接続型の接続用薄膜トランジスタ34がドレイン電極Dからソース電極Sへの一方向のみ導通可能であるため、走査ライン用静電気保護素子ライン31の電位が共通ライン8の電位よりも高い場合には、走査ライン用静電気保護素子ライン31から電流が接続用薄膜トランジスタ34を介して共通ライン8に流れるが、その逆方向には流れないので、消費電力が増加しないようにすることができる。

40

【0042】

一方、ある1本のデータライン7に外部から何らかの理由により正の静電気が侵入したとする。すると、当該データライン7に接続されたデータライン用静電気保護用薄膜トランジスタ42が導通状態となり、当該データライン7から電流がそれに接続されたデータライン用静電気保護用薄膜トランジスタ42を介してデータライン用静電気保護ライン41に流れ、データライン用静電気保護ライン41が高電位となる。

【0043】

データライン用静電気保護ライン41が高電位になると、残りのデータライン7に接続

50

されたデータライン用静電気保護用薄膜トランジスタ42が導通状態となり、データライン用静電気保護ライン41から電流がデータライン用静電気保護用薄膜トランジスタ42を介して残りのデータライン7に流れ、すべてのデータライン7が同電位となる。

【0044】

また、データライン用静電気保護ライン41が高電位になると、第1の接続用薄膜トランジスタ43がオン状態となり、データライン用静電気保護ライン41から電流が第1の接続用薄膜トランジスタ43および共通引き回し線45を介して共通ライン8に流れ、さらに、共通接続パッド9および基板間導通材を介して対向基板2の対向電極に流れる。かくして、データライン7に外部から何らかの理由により侵入した正の静電気は放電され、スイッチング用薄膜トランジスタ5の静電気に起因する特性シフトや絶縁破壊等の不良が防止される。

10

【0045】

ところで、データライン用静電気保護ライン41の電位が共通ライン8の電位よりも大きい場合には、第1の接続用薄膜トランジスタ43がオン状態となり、データライン用静電気保護ライン41から電流が共通ライン8に流れる。一方、共通ライン8の電位がデータライン用静電気保護ライン41の電位よりも大きい場合には、第2の接続用薄膜トランジスタ44がオン状態となり、共通ライン8から電流がデータライン用静電気保護ライン41に流れる。そして、データライン用静電気保護ライン41と共通ライン8との電位差が小さい場合には、どちらの方向へも電流が流れにくく、消費電力が増加しにくいようになることができる。

20

【0046】

ところで、図7に示すように、データライン用静電気保護ライン41はアクティブ基板1の上面に形成されている。このため、同図7に示すように、データライン用静電気保護用薄膜トランジスタ42のソース電極Sは、ゲート絶縁膜51のコンタクトホール63を介してデータライン用静電気保護ライン41に接続されている。したがって、コンタクトホール63が必要となる。次に説明する第2実施形態は、コンタクトホール63を不要としたものである。

30

【0047】

(第2実施形態)

図9はこの発明の第2実施形態としての液晶表示装置の図7同様の断面図を示す。この液晶表示装置においては、データライン用静電気保護用薄膜トランジスタ42のソース電極Sは、ゲート絶縁膜51の上面に設けられたデータライン用静電気保護ライン41に接続されている。したがって、図7に示すようなコンタクトホール63は不要となる。

【0048】

なお、この第2実施形態の液晶表示装置においては、図8同様の断面図である図10に示すように、データライン用静電気保護ライン41をゲート絶縁膜51の上面に設けても、第1の接続用薄膜トランジスタ43のソース電極Sおよび第2の接続用薄膜トランジスタ44のドレイン電極Dを共通引き回し線45に接続するためのコンタクトホール64およびデータライン用静電気保護ライン41を第1の接続用薄膜トランジスタ43のゲート電極Gに接続するためのコンタクトホール65は必要である。

40

【0049】

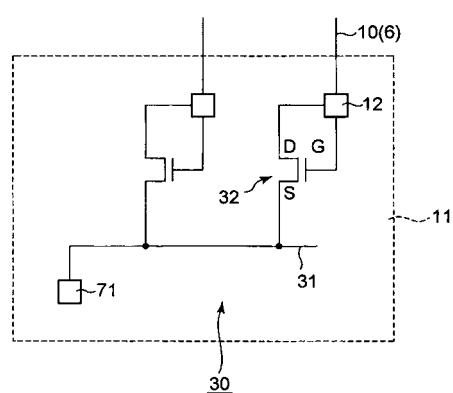

(第3実施形態)

図11はこの発明の第3実施形態としての液晶表示装置の図2同様の等価回路的平面図を示す。この液晶表示装置において、図2に示す場合と異なる点は、第2の走査ライン用静電気和諧用薄膜トランジスタ33を省略し、接続用薄膜トランジスタ34のソース電極Sを走査ライン駆動用ドライバ搭載領域11内に設けられたVg1端子71に接続した点である。

【0050】

この場合、Vg1端子71には非選択状態の走査ライン6に印加される負電圧（例えば、Vg1 = -20~-15V）が供給される。この非選択状態の走査ライン6の電位Vg

50

1 (-20~-15V) は共通ライン8の電位(例えば、V<sub>com</sub>=-5~+5V)よりも低い。したがって、走査ライン用静電気保護ライン31から電流が接続用薄膜トランジスタ34を介してV<sub>g1</sub>端子71に流れるようにしてもよい。

【0051】

(第4実施形態)

図12はこの発明の第4実施形態としての液晶表示装置の図11同様の等価回路的平面図を示す。この液晶表示装置において、図11に示す場合と異なる点は、接続用薄膜トランジスタ34を省略し、走査ライン用静電気保護ライン31の一端部をV<sub>g1</sub>端子71に接続した点である。このように、走査ライン用静電気保護ライン31から電流がV<sub>g1</sub>端子71に直接流れるようにしてもよい。

10

【0052】

(その他の実施形態)

図3に示す場合において、第1の接続用薄膜トランジスタ43のソース電極Sおよび第2の接続用薄膜トランジスタ44のゲート電極G、ドレイン電極Dを、図11に示す場合と同様に、V<sub>g1</sub>端子71に接続するようにしてもよい。また、図3に示す場合において、第1、第2の接続用薄膜トランジスタ43、44を省略し、図12に示す場合と同様に、データライン用静電気保護ライン41の一端部をV<sub>g1</sub>端子71に接続するようにしてもよい。

20

【0053】

また、上記実施形態では、走査ライン駆動用ドライバ搭載領域11とデータライン駆動用ドライバ搭載領域14とを分離しているが、走査ライン駆動用ドライバとデータライン駆動用ドライバとを1チップ化したものが市販されており、このような1チップドライバを用いる場合には、走査ライン駆動用ドライバ搭載領域とデータライン駆動用ドライバ搭載領域は連続して形成し、その領域内に走査ライン用静電気保護回路およびデータライン用静電気保護回路とを連続あるいは、分離して形成してもよい。

20

【0054】

また、上記実施形態では、走査ライン駆動用ドライバ搭載領域11とデータライン駆動用ドライバ搭載領域14とをアクティブ基板1の一辺である突出部1aに形成したものとしているが、アクティブ基板の複数の辺を突出部とし、各突出部に走査ライン駆動用ドライバ搭載領域とデータライン駆動用ドライバ搭載領域を形成し、それぞれに、静電気保護回路を設けるようにしてもよい。

30

【0055】

また、上述した各実施形態において、静電気保護回路は、その全体をドライバ搭載領域内に形成する必要はなく、静電気保護回路の一部がドライバ搭載領域よりはみ出るようにしてもよい。

【0056】

また、上記各実施形態では、表示装置として液晶表示装置の場合で説明したが、有機EL、フィールドエミッショントライス等、他の表示素子を有する表示装置に対しても適用することができる。

40

【図面の簡単な説明】

【0057】

【図1】この発明の第1実施形態としての液晶表示装置の要部の等価回路的平面図。

【図2】図1に示す走査ライン駆動用ドライバ搭載領域に設けられた走査ライン用静電気保護回路の部分の等価回路的平面図。

【図3】図1に示すデータライン駆動用ドライバ搭載領域に設けられたデータライン用静電気保護回路の部分の等価回路的平面図。

【図4】図1に示す薄膜トランジスタおよび画素電極の部分の断面図。

【図5】図2に示す走査ライン駆動用ドライバ搭載領域内の一剖面の断面図。

【図6】図2に示す走査ライン駆動用ドライバ搭載領域内の他の部分の断面図。

【図7】図3に示すデータライン駆動用ドライバ搭載領域内の一剖面の断面図。

50

【図 8】図 3 に示すデータライン駆動用ドライバ搭載領域内の他の部分の断面図。

【図 9】この発明の第 2 実施形態としての液晶表示装置の図 7 同様の断面図。

【図 10】同第 2 実施形態としての液晶表示装置の図 8 同様の断面図。

【図 11】この発明の第 3 実施形態としての液晶表示装置の図 2 同様の等価回路的平面図。

【図 12】この発明の第 4 実施形態としての液晶表示装置の図 11 同様の等価回路的平面図。

【符号の説明】

【0058】

- |       |                           |    |

|-------|---------------------------|----|

| 1     | アクティブ基板                   | 10 |

| 2     | 対向基板                      |    |

| 3     | 表示領域                      |    |

| 4     | 画素電極                      |    |

| 5     | スイッチング用薄膜トランジスタ           |    |

| 6     | 走査ライン                     |    |

| 7     | データライン                    |    |

| 8     | 共通ライン                     |    |

| 9     | 共通接続パッド                   |    |

| 10    | 走査用引き回し線                  |    |

| 11    | 走査ライン駆動用ドライバ搭載領域          | 20 |

| 12    | 走査用出力端子                   |    |

| 13    | データ用引き回し線                 |    |

| 14    | データライン駆動用ドライバ搭載領域         |    |

| 15    | データ用出力端子                  |    |

| 30    | 走査ライン用静電気保護回路             |    |

| 31    | 走査ライン用静電気保護ライン            |    |

| 32    | 第 1 の走査ライン用静電気保護用薄膜トランジスタ |    |

| 33    | 第 2 の走査ライン用静電気保護用薄膜トランジスタ |    |

| 34    | 接続用薄膜トランジスタ               |    |

| 35    | 共通引き回し線                   | 30 |

| 40    | データライン用静電気保護回路            |    |

| 41    | データライン用静電気保護ライン           |    |

| 42    | データライン用静電気保護用薄膜トランジスタ     |    |

| 43、44 | 接続用薄膜トランジスタ               |    |

| 45    | 共通引き回し線                   |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

**【手続補正書】**

【提出日】平成20年9月9日(2008.9.9)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

第1の基板と第2の基板とが重なり合う重合領域に表示領域が設けられるとともに、前記第1の基板が前記第2の基板の一辺より突出した突出部を有し、

前記第1の基板における前記表示領域に、マトリクス状に配置された画素電極と、前記画素電極に接続されたスイッチング用薄膜トランジスタと、前記スイッチング用薄膜トランジスタに走査信号を供給するための走査ラインと、前記スイッチング用薄膜トランジスタにデータ信号を供給するためのデータラインとが設けられた表示装置であって、

前記突出部に、走査ライン駆動用ドライバまたはデータライン駆動用ドライバが搭載されるとともに前記走査ラインに接続された走査ライン用静電気保護回路または前記データラインに接続されたデータライン用静電気保護回路が設けられ、

前記走査ライン用静電気保護回路を介して前記走査ラインに接続される導電ラインまたは前記データライン用静電気保護回路を介して前記データラインに接続される導電ラインが前記表示領域を囲うように前記重合領域に設けられていることを特徴とする表示装置。

**【請求項2】**

前記画素電極と対向配置され、各表示画素で共通の電位に設定される共通電極を更に備え、

前記導電ラインが前記共通電極と同電位に設定されていることを特徴とする請求項1に記載の表示装置。

**【請求項3】**

前記走査ライン駆動用ドライバまたは前記データライン駆動用ドライバが搭載される領域に、前記走査ライン用静電気保護回路または前記データライン用静電気保護回路が設けられていることを特徴とする請求項1または2に記載の表示装置。

**【請求項4】**

前記重合領域における前記導電ラインは、前記第1の基板に形成されていることを特徴とする請求項1から3の何れかに記載の表示装置。

**【手続補正2】**

【補正対象書類名】明細書

【補正対象項目名】0006

【補正方法】変更

**【補正の内容】****【0006】**

上記目的を達成するため、請求項1に記載の発明は、第1の基板と第2の基板とが重なり合う重合領域に表示領域が設けられるとともに、前記第1の基板が前記第2の基板の一辺より突出した突出部を有し、前記第1の基板における前記表示領域に、マトリクス状に配置された画素電極と、前記画素電極に接続されたスイッチング用薄膜トランジスタと、前記スイッチング用薄膜トランジスタに走査信号を供給するための走査ラインと、前記スイッチング用薄膜トランジスタにデータ信号を供給するためのデータラインとが設けられた表示装置であって、前記突出部に、走査ライン駆動用ドライバまたはデータライン駆動用ドライバが搭載されるとともに前記走査ラインに接続された走査ライン用静電気保護回路または前記データラインに接続されたデータライン用静電気保護回路が設けられ、前記走査ライン用静電気保護回路を介して前記走査ラインに接続される導電ラインまたは前記データライン用静電気保護回路を介して前記データラインに接続される導電ラインが前記

表示領域を囲うように前記重合領域に設けられていることを特徴とするものである。

また、請求項 2 に記載の発明は、請求項 1 に記載の表示装置において、前記画素電極と対向配置され、各表示画素で共通の電位に設定される共通電極を更に備え、前記導電ラインが前記共通電極と同電位に設定されていることを特徴とするものである。

また、請求項 3 に記載の発明は、請求項 1 または 2 に記載の表示装置において、前記走査ライン駆動用ドライバまたは前記データライン駆動用ドライバが搭載される領域に、前記走査ライン用静電気保護回路または前記データライン用静電気保護回路が設けられていることを特徴とするものである。

また、請求項 4 に記載の発明は、請求項 1 から 3 の何れかに記載の表示装置において、前記重合領域における前記導電ラインは、前記第 1 の基板に形成されていることを特徴とするものである。

【手続補正 3】

【補正対象書類名】明細書

【補正対象項目名】0 0 0 7

【補正方法】変更

【補正の内容】

【0 0 0 7】

この発明によれば、額縁面積を小さくすることができる。

|                |                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <u>JP2008293048A</u>                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2008-12-04 |

| 申请号            | JP2008217572                                                                                                                                                                                                                                                                                                                   | 申请日     | 2008-08-27 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 中村 やよい                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 中村 やよい                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09F9/30 G02F1/1368 G02F1/1345                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09F9/30.338 G09F9/30.330.Z G02F1/1368 G02F1/1345 G09F9/30.330                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号      | 2H092/GA32 2H092/JA26 2H092/JA28 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JA46 2H092/JA47 2H092/JB22 2H092/JB31 2H092/JB79 2H092/NA14 2H092/NA25 5C094/AA15 5C094/BA03 5C094/BA27 5C094/BA43 5C094/DA09 5C094/DB01 5C094/EA10 2H192/AA24 2H192/BC31 2H192/CB05 2H192/CB71 2H192/FA73 2H192/FB22 2H192/FB32 2H192/FB34 2H192/GA15 |         |            |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                               |         |            |

## 摘要(译)

要解决的问题：为了减小在液晶显示装置中的边框面积，该液晶显示装置设置有用于保护开关薄膜晶体管免受静电影响的静电保护薄膜晶体管。解决方案：在扫描线驱动驱动器安装区域11中提供了扫描线静电保护线31，第一和第二扫描线静电保护薄膜晶体管32、33以及连接薄膜晶体管34。不需要用于放置的专用放置区域，并且可以相应地减小框架区域。此外，如果在数据线驱动驱动器安装区域14设置有数据线静电保护线41，数据线静电保护薄膜晶体管42以及第一连接薄膜晶体管43和第二连接薄膜晶体管44，则它们被布置。因此，不需要专用的布局区域，并且可以相应地减小框架区域。[选型图]图1