(19)日本国特許庁( J P )

# 公開特許公報 ( A ) (11)特許出願公開番号

特開2001 - 255544

(P2001 - 255544A)

(43)公開日 平成13年9月21日(2001.9.21)

| (51) Int.CI <sup>7</sup> | 識別記号   | F I            | テ-マコード <sup>*</sup> (参考) |

|--------------------------|--------|----------------|--------------------------|

| G 0 2 F 1/1343           |        | G 0 2 F 1/1343 | 2 H 0 9 2                |

|                          | 1/1368 | G 0 9 F 9/30   | 337 5 C 0 9 4            |

| G 0 9 F 9/30             | 337    |                | 5 F 1 1 0                |

|                          | 9/35   | 9/35           |                          |

| H 0 1 L 29/786           |        | G 0 2 F 1/136  | 500                      |

|                          |        | H 0 1 L 29/78  | 612 A                    |

審査請求 未請求 請求項の数 10 L (全 6 数)

(21)出願番号 特願2000 - 66900(P2000 - 66900)

(71)出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(22)出願日 平成12年3月10日(2000.3.10)

(72)発明者 大関 茂樹

埼玉県深谷市幡羅町一丁目9番地2号 株式会社東芝深谷工場内

(74)代理人 100062764

弁理士 樋澤 裏 (外2名)

最終頁に続く

(54)【発明の名称】 液晶表示装置

## (57)【要約】

【課題】 画素の欠陥発生を防止できる液晶表示装置を提供する。

【解決手段】 アレイ基板21とアレイ基板21に対向する対向基板との間に液晶を配設する。アレイ基板21の透光性を有する絶縁基板22の一主面上に直交して複数の走査線24および信号線25を電気的に絶縁して配設する。絶縁基板22上に配設した補助電極32の対辺に外部に引き出した引き出し電極36a, 36bをそれぞれ設ける。補助電極32と、補助電極32上の補助容量部33と、補助容量部33上の補助容量線34とで補助容量35を形成する。補助電極32と補助容量線34との間の界面準位が大きい場合でも、補助容量部33の高周波特性を損なわない。画素欠陥の発生を防止でき、歩留まり良く製造できる。

**【特許請求の範囲】**

【請求項1】透光性を有する絶縁基板、この絶縁基板の一主面上に互いに交差して配設されそれぞれ導電層で形成され互いに絶縁された複数本の信号線および走査線、前記絶縁基板上に配設され半導体層で形成された活性層と前記絶縁基板上に配設され前記走査線に電気的に接続されたゲート電極とこれらゲート電極および前記活性層の間に位置する絶縁層で形成されたゲート絶縁膜とを有し前記信号線および走査線の交点に対応して配設される薄膜トランジスタ、前記走査線を形成する導電層で形成された補助容量線と前記活性層を形成する半導体層で形成された補助電極とこれら補助容量線および補助電極の間に位置し前記ゲート絶縁膜を形成する絶縁層で形成された補助容量部とを有する補助容量、前記薄膜トランジスタにより制御されマトリクス状に配設される透明導体層である画素電極、および前記補助電極の対向する対辺それぞれに設けられ外部に引き出された複数の引き出し電極を備えたアレイ基板と、

このアレイ基板に対向する対向基板と、

前記アレイ基板と対向基板との間に配設される液晶とを具備していることを特徴とした液晶表示装置。

**【発明の詳細な説明】**

**【0001】**

【発明の属する技術分野】本発明は、薄膜トランジスタをスイッチング素子とする液晶表示装置に関する。

**【0002】**

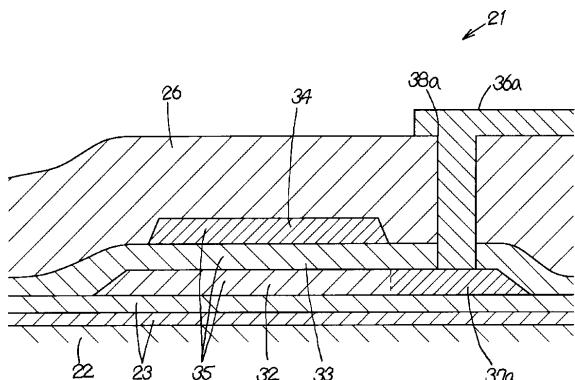

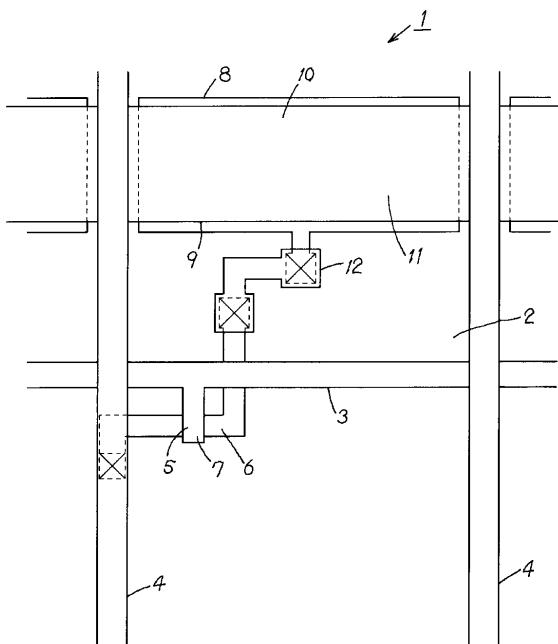

【従来の技術】従来、この種の液晶表示装置としては、例えば、図4に示す構成が知られている。

【0003】この図4に示す液晶表示装置は、アクティブマトリクス型であり、アレイ基板1と、このアレイ基板1に対向し図示しない対向電極を有する図示しない対向基板とを有している。そして、これらアレイ基板1と対向基板との間には、図示しない液晶組成物の液晶が配設されている。

【0004】また、このアレイ基板1には、透光性を有する絶縁基板2の一主面上に、導電層で形成された複数本の走査線3と信号線4とがそれぞれ平行に互いに直交して図示しない層間絶縁膜により絶縁されて配設されている。そして、これら走査線3と信号線4との交点に対応した位置には、薄膜トランジスタ(Thin Film Transistor)5が形成されている。

【0005】この薄膜トランジスタ5は、絶縁基板2上に半導体層である活性層6が配設され、これら活性層6を含む絶縁基板2上に絶縁層で形成された図示しないゲート絶縁膜が配設され、このゲート絶縁膜上に走査線3に直交するゲート電極7がこの走査線3に電気的に接続されて形成されている。

【0006】また、絶縁基板2上には、活性層6を形成する半導体層で補助電極8が形成されており、この補助電極8上には、ゲート絶縁膜を形成する絶縁層で補助容

量部9が形成されている。さらに、この補助容量部9上には、走査線3を形成する導電層で補助容量線10が形成されている。そして、これら補助電極8、補助容量部9および補助容量線10で補助容量11が形成されている。

【0007】さらに、補助電極8には、外部に向けて引き出された引き出し電極12が1カ所設けられており、薄膜トランジスタ5には、この薄膜トランジスタ5により制御されマトリクス状に配設された透明導体層である図示しない画素電極が電気的に接続されている。

【0008】そして、走査線3の電位によって薄膜トランジスタ5が順次駆動される際には、信号線4に印加する電圧を変化させることにより、これら走査線3と各信号線4との交点にある画素の電位が制御され、液晶の状態が変化して出画を行っている。

【0009】さらに、上記図4に示す液晶表示装置を駆動する際には、画素の補助容量11の周波数応答特性が悪いと、この補助容量11の補助容量部9で所定の容量が保持できないため、画素の欠陥を引き起こしてしまう場合がある。また、補助容量11の補助電極8に活性層6として、ポリシリコンやアモルファスシリコンなどの半導体を用いた場合には、補助電極8と補助容量線10との間の界面準位の影響を受けるため、高周波での応答特性の劣化を招きやすい。

【0010】そして、この応答特性の劣化には、補助電極8の形状も起因しているので、コンタクトのために低抵抗化された補助電極8の引き出し電極12から遠い箇所ほど高周波の応答特性が劣化しやすい。

【0011】また、画素電極の数が多くなるほど一画素当たりの書き込み時間が短くなるため、補助容量11の補助容量部9の周波数が高く、すなわちアレイ基板1の高精細化が進むほど、高周波での応答特性の劣化が顕著に現れてしまう。

**【0012】**

【発明が解決しようとする課題】以上のように、上記図4に示す液晶表示装置は、補助容量11の補助電極8からの引き出し電極12が1カ所であるため、補助電極8と補助容量線10との間の界面準位が大きく、また、コンタクトのために低抵抗化された補助電極8の引き出し電極12から遠い箇所では、補助容量11の高周波特性が悪く、画素の欠陥を生じてしまう場合があるという問題を有している。

【0013】本発明は、このような点に鑑みなされたもので、画素の欠陥発生を防止できる液晶表示装置を提供することを目的とする。

**【0014】**

【課題を解決するための手段】本発明は、透光性を有する絶縁基板、この絶縁基板の一主面上に互いに交差して配設されそれぞれ導電層で形成され互いに絶縁された複数本の信号線および走査線、前記絶縁基板上に配設され半導体層で形成された活性層と前記絶縁基板上に配設さ

れ前記走査線に電気的に接続されたゲート電極とこれらゲート電極および前記活性層の間に位置する絶縁層で形成されたゲート絶縁膜とを有し前記信号線および走査線の交点に対応して配設される薄膜トランジスタ、前記走査線を形成する導電層で形成された補助容量線と前記活性層を形成する半導体層で形成された補助電極とこれら補助容量線および補助電極の間に位置し前記ゲート絶縁膜を形成する絶縁層で形成された補助容量部とを有する補助容量、前記薄膜トランジスタにより制御されマトリクス状に配設される透明導体層である画素電極、および前記補助電極の対向する対辺それぞれに設けられ外部に引き出された複数の引き出し電極を備えたアレイ基板と、このアレイ基板に対向する対向基板と、前記アレイ基板と対向基板との間に配設される液晶とを具備しているものである。

【0015】そして、この構成では、アレイ基板の補助容量の補助電極の対向する対辺それから複数の引き出し電極を引き出したことにより、活性層を形成する半導体層で形成した補助電極と、走査線を形成する導体層で形成した補助容量線との間の界面準位が大きい場合であっても、これら補助容量線および補助電極の間に位置する補助容量部を有する補助容量の高周波特性を損なわない。このため、画素欠陥の発生が防止されるので、歩留まりが向上される。

#### 【0016】

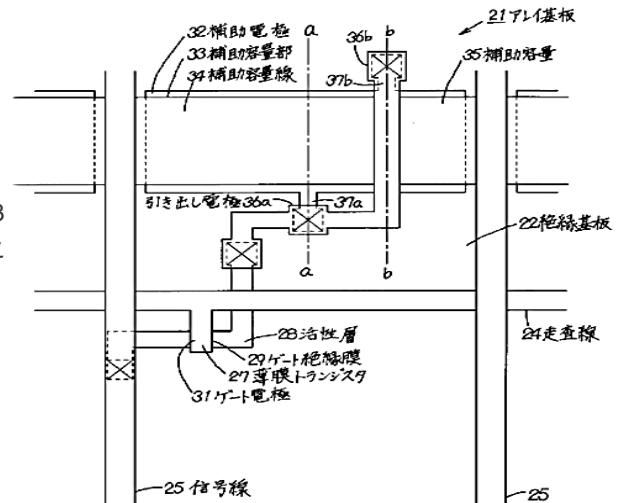

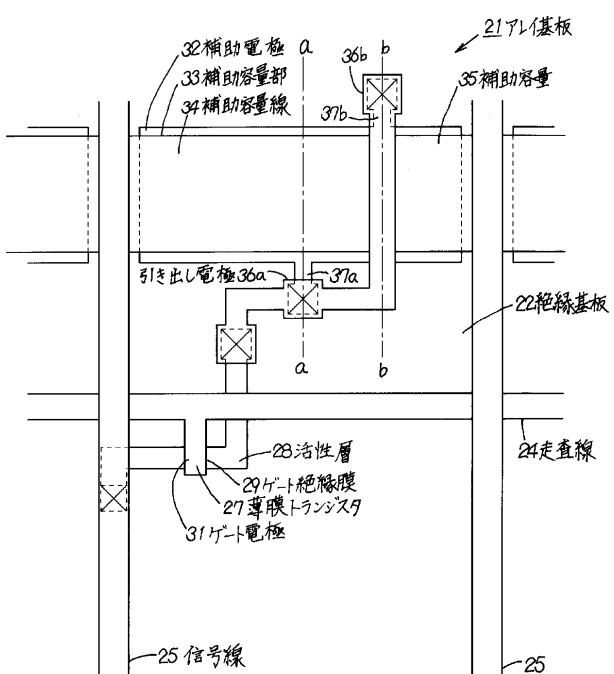

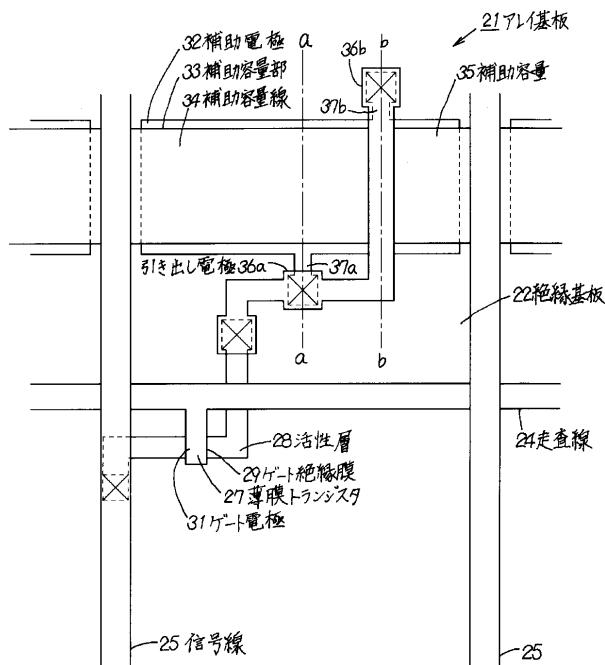

【発明の実施の形態】以下、本発明の液晶表示装置の一実施の形態の構成を図1ないし図3を参照して説明する。

【0017】図1ないし図3に示す液晶表示装置は、アクティブマトリクス型TFT液晶表示装置であり、アレイ基板21を備えている。そして、このアレイ基板21に対向して図示しない対向基板が配設されており、これらアレイ基板21と対向基板との間には図示しない液晶組成物の液晶が配設されている。

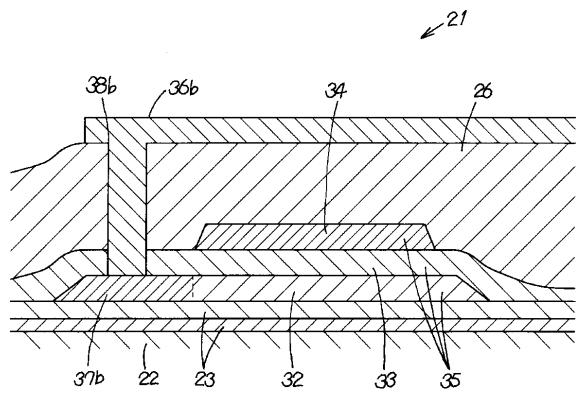

【0018】また、アレイ基板21は、透光性を有する絶縁基板22を備えており、この絶縁基板22の一主面上には、この絶縁基板22からの不純物の拡散を防止するためのアンダーコート膜23が成膜されている。

【0019】さらに、このアンダーコート膜23上には、導電層で形成された複数本の走査線24と信号線25とがそぞれ平行に互いに直交して層間絶縁膜26により絶縁されて配設されている。そして、これら走査線24と信号線25との交点に対応した位置には、スイッチング素子としての薄膜トランジスタ(Thin Film Transistor)27が形成されている。

【0020】また、アンダーコート膜23上には、多結晶シリコンとしてのポリシリコンなどの半導体層で略扁平長方形状の島状の活性層28が成膜されている。また、これら活性層28を含む絶縁基板22上には、 $\text{SiO}_2$ 膜などの絶縁層でゲート絶縁膜29が配設されている。

【0021】さらに、このゲート絶縁膜29上には、走査線24に直交するゲート電極31が、薄膜トランジスタ27のゲート領域に電気的に接続され、すなわち走査線24に直交するように突出して形成され走査線24に電気的に接続されて形成されている。そして、これら活性層28、ゲート絶縁膜29およびゲート電極31により薄膜トランジスタ27が形成されている。

【0022】また、アンダーコート膜23上には、活性層28を形成する半導体層であるポリシリコンで島状の補助電極32が形成されている。さらに、この補助電極32上には、ゲート絶縁膜29を形成する絶縁層である $\text{SiO}_2$ 膜で補助容量部33が形成されている。

【0023】そして、この補助容量部33上には、走査線24を形成する導電層で補助容量線34が成膜されている。そして、これら補助電極32、補助容量部33および補助容量線34で補助容量35が形成されている。

【0024】さらに、補助電極32の長手方向における対向する両側、すなわち対辺には、これら対辺から1カ所ずつ、計2ヶ所の引き出し電極36a, 36bがそれぞれ形成されている。これら引き出し電極36a, 36bの基端には、活性層28の側辺にそれぞれ接続された引き出し電極領域37a, 37bがそれぞれ形成されている。

【0025】そして、絶縁基板22の表面略全域には、層間絶縁膜26が形成されており、この層間絶縁膜26には、引き出し電極領域37a, 37bと連通したコンタクトホール38a, 38bが開口されている。

【0026】また、層間絶縁膜26上の略全域には、アルミニウム(AI)などの図示しない金属膜が形成されており、この金属膜は、信号線25を形成するとともに、薄膜トランジスタ27の図示しないソース領域またはドレイン領域のいずれか一方を形成して信号線25に電気的に接続されて電極を形成している。

【0027】さらに、この薄膜トランジスタ27のソース領域またはドレイン領域のいずれか他方には、絶縁基板22上にマトリクス状に配設された透明導体層である図示しない画素電極がそれぞれ電気的に接続されている。

【0028】次に、上記一実施の形態の製造工程について説明する。

【0029】まず、絶縁基板22上にアンダーコート膜23を成膜する。このアンダーコート膜23は、化学気相反応法やスパッタリング法などで形成された $\text{SiO}_2$ が用いられている。なお、このアンダーコート膜23は、 $\text{SiO}_2$ 以外にも $\text{Si}_3\text{N}_4$ や、 $\text{Si}_3\text{N}_4$ と $\text{SiO}_2$ との2層の薄膜などで形成してもよい。

【0030】次いで、このアンダーコート膜23上に活性層28および補助電極32を形成する。これら活性層28および補助電極32は、例えば、プラズマCVD法、LPCVD法、またはスパッタリング法などの成膜方法によりアモルファスシリコン膜を形成した後、このアモルファスシリコン膜にレーザーニールを施して多結晶化されて

いる。

【0031】なお、これら活性層28および補助電極32は、例えば、アモルファスシリコンの種から固相成長により形成する方法や、 $\text{SiO}_4 \cdot \text{SiF}_4 \cdot \text{B}_2$ などを原料ガスとしたプラズマCVD法で直接形成する方法などで形成してもよい。また、これら活性層28および補助電極32は、ポリシリコンの代わりに、アモルファスシリコンなどを用いることもできる。そして、このアモルファスシリコンは、例えば、プラズマCVD法、LPCVD法、スパッタリング法などで成膜する。

【0032】さらに、これら活性層28および補助電極32をエッティングで島状に形成する。これら活性層28および補助電極32に対するエッティングは、例えば、 $\text{CF}_4 \cdot \text{O}_2$ ガスを用いたケミカルドライエッティング(CDE)などで行う。ここで、このケミカルドライエッティング(CDE)時におけるエッティングの条件は、 $\text{O}_2 / \text{CF}_4$ 流量比を4、エッティング圧力を40Pa、マイクロ波電源パワーを800W、基板温度を60°とする。

【0033】そして、補助電極32の長手方向における対向する両側、すなわち対辺に、引き出し電極36a, 36bをそれぞれ形成する。

【0034】次いで、活性層28上にゲート絶縁膜29を形成するとともに、補助電極32上に補助容量部33を形成する。これらゲート絶縁膜29および補助容量部33は、テトラエチルオルソシリケート(TEOS)・ $\text{O}_2$ を原料ガスとしたプラズマCVD法で形成する。

【0035】なお、これらゲート絶縁膜29および補助容量部33は、プラズマCVD法以外に、常圧CVD法、LPCVD法、ECRプラズマCVD法、リモートプラズマCVD法などの他のCVD法や、スパッタリング法などの方法で形成することもできる。さらに、これらゲート絶縁膜29および補助容量部33は、(TEOS)・ $\text{O}_2$ ガス以外の $\text{SiH}_4 \cdot \text{O}_2$ ガスなどを原料ガスとして形成することもできる。

【0036】さらに、これらゲート絶縁膜29および補助容量部33を形成した後に、これらゲート絶縁膜29および補助容量部33の膜質をさらに向上させる場合には、例えば、窒素雰囲気中で、600°、5時間の条件でこれらゲート絶縁膜29および補助容量部33をアニールする。

【0037】そして、ゲート絶縁膜29上にゲート電極31を成膜するとともに、補助容量部33上に補助容量線34を成膜する。これらゲート電極31および補助容量線34は、モリブデン-タンクステン合金(MoW)やアルミニウム(Al)など、低抵抗金属や不純物が導入された多結晶シリコンなどで形成されている。

【0038】さらに、これらゲート電極31および補助容量線34を、所定の形状にパターニングした後にマスクして自己整合する。

【0039】次いで、引き出し電極36a, 36bの引き出し電極領域37a, 37bに、n型不純物であるリン(P)を、例

えば、 $5 \times 10^{16} / \text{cm}^2$ の条件でイオン注入して、コントラクトがとれるようにそれぞれ低抵抗化する。このとき、このイオン注入により導入されるリンを、レーザーアニールや熱アニール等のアニールで活性化しておく。

【0040】その後、補助容量35をP型にする場合には、ボロン(B)などのp型不純物を引き出し電極領域37a, 37bそれぞれにイオン注入する。

【0041】そして、絶縁基板22の表面略全域に層間絶縁膜26を形成する。このとき、この層間絶縁膜26に引き出し電極領域37a, 37bと連通するコントラクトホール38a, 38bを開口する。

【0042】さらに、層間絶縁膜26上の略全域に、金属膜を形成する。この金属膜は、パターニングされてソース領域に電気的に接続されている。

【0043】次に、上記一実施の形態の作用を説明する。

【0044】まず、絶縁基板22の一主面上にアンダーコート膜23を形成する。

【0045】次いで、このアンダーコート膜23上に活性層28および補助電極32を形成した後に、これら活性層28および補助電極32をエッティングする。

【0046】さらに、補助電極32の対向する対辺に引き出し電極36a, 36bをそれぞれ形成する。

【0047】その後、これら引き出し電極36a, 36bの先端が外部に引き出されるように、これら引き出し電極36a, 36bそれぞれの引き出し電極領域37a, 37b、活性層28および補助電極32上にゲート絶縁膜29および補助容量部33を形成する。

【0048】次いで、これらゲート絶縁膜29および補助容量部33上にゲート電極31および補助容量線34を成膜する。

【0049】さらに、絶縁基板22上の略全域に層間絶縁膜26を形成し、この層間絶縁膜26上の略全域に金属膜を形成する。

【0050】上述したように、上記一実施の形態によれば、アレイ基板21の補助容量35を形成する補助電極32の対向する対辺から1カ所ずつ、計2カ所の引き出し電極36a, 36bを引き出したことにより、補助電極32の対辺が長い場合や、この補助電極32にポリシリコンを用いた結果、補助電極32と補助容量線34との間の界面準位が多い場合であっても、補助容量35の補助容量部33における高周波での応答特性の劣化を防止できる。よって、この補助容量35の補助容量部33で所定の容量が保持できる。

【0051】ここで、補助容量35の高周波での応答特性の劣化には補助電極32の形状が起因しており、この補助電極32に形成された引き出し電極36a, 36bから遠い箇所ほど高周波の応答特性が劣化しやすいが、この補助電極32の対辺にそれぞれ引き出し電極36a, 36bを形成したことにより、補助容量35の補助容量部33の高周波での応答特性の劣化を防止できる。

【0052】このため、走査線24の電位によって薄膜トランジスタ27を順次駆動させる際に、信号線25に印加する電圧を変化させ、これら走査線24と各信号線25との交点にある画素の電位を制御した場合に生じる画素欠陥の発生を防止できる。この結果、アレイ基板21を歩留まり良く製造できるので、製造コストを削減でき、さらには、需要者に対する信頼性を向上できる。

【0053】さらに、画素電極の数が多くなるほど一画素当たりの書き込み時間が短くなるが、補助電極32の対辺にそれぞれ引き出し電極36a, 36bを形成したことにより、補助容量32の周波数を高くした場合であっても対応できるので、より高精細化できる。

【0054】なお、上記一実施の形態では、補助電極32の対向する対辺から1カ所ずつ引き出し電極36a, 36bを引き出した構成について説明したが、このような構成に限定されることはなく、補助電極32の対辺それぞれに少なくとも1つ以上の複数の引き出し電極36a, 36b, ...を形成した構成であれば、上記一実施の形態と同様な作用効果を奏すことができる。

【0055】

【発明の効果】本発明によれば、補助容量の補助電極の対向する対辺それから複数の引き出し電極を引き出したため、補助電極と補助容量線との間の界面準位が大きい場合でも、補助容量部の高周波特性を損なわないの\*

\*で、画素欠陥の発生を防止でき、歩留まり良く製造できる。

#### 【図面の簡単な説明】

【図1】本発明の液晶表示装置の一実施の形態の一部を示す平面図である。

【図2】同上液晶表示装置のアレイ基板のa-a断面図である。

【図3】同上アレイ基板のb-b断面図である。

【図4】従来の液晶表示装置の一部を示す平面図である。

#### 【符号の説明】

|          |          |

|----------|----------|

| 21       | アレイ基板    |

| 22       | 絶縁基板     |

| 24       | 走査線      |

| 25       | 信号線      |

| 27       | 薄膜トランジスタ |

| 28       | 活性層      |

| 29       | ゲート絶縁膜   |

| 31       | ゲート電極    |

| 20       | 32 補助電極  |

| 33       | 補助容量部    |

| 34       | 補助容量線    |

| 35       | 補助容量     |

| 36a, 36b | 引き出し電極   |

【図1】

【図2】

【図3】

【図4】

フロントページの続き

F ターム(参考) 2H092 GA24 HA06 HA28 JA24 JA28

JB57 JB63 JB64 JB65 JB68

JB69 KA04 KA05 KA12 MA08

MA18 MA19 NA23 NA29 NA30

5C094 AA31 AA42 BA03 BA43 CA19

DB02 EA04 EA07 FB12 FB15

5F110 AA26 BB01 CC01 DD13 DD14

DD17 EE03 EE06 EE09 FF02

FF28 FF29 FF30 FF31 FF32

FF36 GG02 GG13 GG15 GG43

GG45 GG47 HL03 NN73 PP03

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2001255544A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2001-09-21 |

| 申请号            | JP2000066900                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2000-03-10 |

| [标]申请(专利权)人(译) | 株式会社东芝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 东芝公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 大関茂樹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 大関 茂樹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G02F1/1343 G02F1/136 G02F1/1368 G09F9/30 G09F9/35 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | G02F1/1343 G09F9/30.337 G09F9/35 G02F1/136.500 H01L29/78.612.A G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H092/GA24 2H092/HA06 2H092/HA28 2H092/JA24 2H092/JA28 2H092/JB57 2H092/JB63 2H092/JB64 2H092/JB65 2H092/JB68 2H092/JB69 2H092/KA04 2H092/KA05 2H092/KA12 2H092/MA08 2H092/MA18 2H092/MA19 2H092/NA23 2H092/NA29 2H092/NA30 5C094/AA31 5C094/AA42 5C094/BA03 5C094/BA43 5C094/CA19 5C094/DB02 5C094/EA04 5C094/EA07 5C094/FB12 5C094/FB15 5F110/AA26 5F110/BB01 5F110/CC01 5F110/DD13 5F110/DD14 5F110/DD17 5F110/EE03 5F110/EE06 5F110/EE09 5F110/FF02 5F110/FF28 5F110/FF29 5F110/FF30 5F110/FF31 5F110/FF32 5F110/FF36 5F110/GG02 5F110/GG13 5F110/GG15 5F110/GG43 5F110/GG45 5F110/GG47 5F110/HL03 5F110/NN73 5F110/PP03 2H092/JA42 2H192/AA24 2H192/CB02 2H192/CB44 2H192/DA12 2H192/DA43 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

## 摘要(译)

提供一种能够防止像素缺陷的发生的液晶显示装置。液晶布置在阵列基板和面对阵列基板的对向基板之间。多条扫描线(24)和信号线(25)在阵列基板(21)的半透明绝缘基板(22)的一个主面上电正交。引到外部的引出电极36a,36b设置在布置在绝缘基板22上的辅助电极32的相对侧。辅助电极32,辅助电极32上的辅助电容部分33和辅助电容部分33上的辅助电容线34形成辅助电容35。即使辅助电极32与辅助电容线34之间的界面状态较大,也不会损害辅助电容部33的高频特性。可以防止像素缺陷的发生,并且可以高成品率进行制造。