# (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4201191号 (P4201191)

(45) 発行日 平成20年12月24日(2008.12.24)

(24) 登録日 平成20年10月17日(2008.10.17)

| (21) 出願番号<br>(22) 出願日<br>(65) 公開番号 | 特願2004-52558 (P2004-52558)<br>平成16年2月26日 (2004.2.26)<br>特開2004-264845 (P2004-264845A) |           |      | (73) 特許権者 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号 |                  |          |        |

|------------------------------------|---------------------------------------------------------------------------------------|-----------|------|--------------------------------------------------------|------------------|----------|--------|

|                                    |                                                                                       |           | G09G | 3/20                                                   | 680G<br>講求項の数 31 | (全 16 頁) | 最終頁に続く |

|                                    |                                                                                       |           | G09G | 3/20                                                   | 624Z             |          |        |

| G09G                               | 3/20                                                                                  | (2006.01) | GO9G | 3/20                                                   | 6 1 2 T          |          |        |

| G02F                               | 1/133                                                                                 | (2006.01) | GO2F | 1/133                                                  | 550              |          |        |

| G09G                               | 3/36                                                                                  | (2006.01) | GO9G | 3/36                                                   |                  |          |        |

| (51) Int.Cl.                       |                                                                                       |           | FΙ   |                                                        |                  |          |        |

審査請求日 平成18年1月25日 (2006.1.25) (31) 優先権主張番号 0304587.9

(32) 優先日 平成15年2月28日 (2003. 2. 28)

平成16年9月24日 (2004.9.24)

(33) 優先権主張国 英国 (GB)

前置審查

(43) 公開日

(74)代理人 100078282

弁理士 山本 秀策

(74)代理人 100062409

弁理士 安村 高明

(74)代理人 100107489

弁理士 大塩 竹志

|(72)発明者 クリス ジェイ. ブラウン

イギリス国 オーエックス1 1エスエヌ , オックスフォード, シアレイク ク

ローズ 24

審査官 福村 拓

最終頁に続く

# (54) 【発明の名称】ディスプレイおよびセンサ装置

# (57)【特許請求の範囲】

# 【請求項1】

アクティブマトリクスディスプレイおよびセンサ装置であって、

複数の口ウおよび複数のカラムにディスプレイ画素が配列されており、前記各ディスプレイ画素のそれぞれは、液晶素子を有するとともに、表示されるイメージデータ信号を受信するディスプレイデータ入力および該ディスプレイデータ入力からの前記イメージデータ信号の入力をイネーブルするスキャン信号を受信するスキャン入力を有し、前記各カラムに配列された前記各ディスプレイ画素の前記ディスプレイデータ入力は、複数のカラムデータ線のそれぞれに接続され、前記各口ウに配列された前記各ディスプレイ画素の前記スキャン入力は、複数のロウスキャン線のそれぞれに接続されている、ディスプレイ画素アレイと、

前記イメージデータ信号を前記各カラムデータ線に供給するデータ信号生成器と、

前記スキャン信号を前記各ロウスキャン線に供給するスキャン信号生成器と、

外部刺激に応答して、前記ディスプレイ画素内での前記液晶素子のキャパシタンスの変化に基づいて生成される画素センサ信号を出力するように前記カラムデータ線に接続されている出力構成と、

前記イメージデータ信号が書き込みされていない前記カラムデータ線から前記画素センサ信号が前記出力構成によって出力されるように、前記データ信号生成器、前記スキャン信号生成器および前記出力構成のうちの少なくとも 1 つを制御するコントローラとを備え

10

20

.

該コントローラによって前記出力構成から出力される前記画素センサ信号が前記ディスプレイ画素の光学的に変動した領域<u>のみ</u>で生成されることを特徴とするアクティブマトリクスディスプレイおよびセンサ装置。

# 【請求項2】

前記データ信号生成器、前記スキャン信号生成器、前記出力構成、および前記ディスプレイ画素アレイの電子部品が、ディスプレイ基板の上に形成されている、請求項1に記載の装置。

# 【請求項3】

前記データ信号生成器は前記ディスプレイ画素アレイの第1の端に沿って配置され、前記出力構成は該ディスプレイ画素アレイの該第1の端の反対の第2の端に沿って配置されている、請求項2に記載の装置。

10

#### 【請求項4】

前記ディスプレイ画素のそれぞれは、電子スイッチを含む、請求項1に記載の装置。

# 【請求項5】

前記ディスプレイ画素のそれぞれは、格納キャパシタを含む、請求項1に記載の装置。

#### 【請求項6】

前記電子スイッチのそれぞれは、薄膜トランジスタを含む、請求項4に記載の装置。

# 【請求項7】

前記薄膜トランジスタのそれぞれは、前記スキャン入力に接続されているゲート、前記ディスプレイデータ入力に接続されているソース、および前記イメージ生成素子に接続されているドレインを有する、請求項 6 に記載の装置。

20

#### 【請求項8】

前記コントローラは、前記ディスプレイ基板上に形成されている、請求項1に記載の装置。

# 【請求項9】

装置全体のアクティブデバイスが薄膜トランジスタとして形成される、請求項8に記載の装置。

# 【請求項10】

前記コントローラは、前記画素センサ信号のうちのいずれが前記出力構成によって出力されるかを決定するようにプログラム化されている、請求項1に記載の装置。

30

### 【請求項11】

前記コントローラは、前記装置の動作中に、前記画素センサ信号のうちのいずれが前記出力構成によって出力されるかを変更するように再プログラム可能である、請求項1に記載の装置。

# 【請求項12】

前記コントローラは、前記イメージデータ信号の書き込み段階と、前記画素センサ信号が前記出力構成によって出力される読み出し段階とが交互に実施されるように、前記データ信号生成器およびスキャン信号生成器ならびに前記出力構成を制御する、請求項1に記載の装置。

# 【請求項13】

40

50

前記書き込み段階のそれぞれの間に、1フレームの前記イメージデータ信号が前記ディスプレイ画素アレイに書き込まれる、請求項12に記載の装置。

# 【請求項14】

前記書き込み段階の間の垂直帰線消去期間に、前記読み出し段階が設定されている、請求項12に記載の装置。

# 【請求項15】

前記書き込み段階のそれぞれの間に、少なくとも 1 つの前記ディスプレイ画素の口ウに前記イメージデータ信号が書き込まれる、請求項 1 2 に記載の装置。

# 【請求項16】

前記読み出し段階において、少なくとも1つの前記ディスプレイ画素のロウから前記画

10

20

30

40

50

素センサ信号が出力された後に、前記書き込み段階の間に前記イメージデータ信号が前記ディスプレイ画素のロウに書き込まれる、請求項15に記載の装置。

### 【請求項17】

前記読み出し段階のそれぞれの間に、前記ディスプレイ画素アレイにおける全ての前記 ディスプレイ画素の前記画素センサ信号が出力される、請求項12に記載の装置。

# 【請求項18】

前記読み出し段階のそれぞれの間に、前記ディスプレイ画素アレイにおける一部の前記ディスプレイ画素の前記画素センサ信号が出力される、請求項12に記載の装置。

#### 【請求項19】

前記読み出し段階のそれぞれにおいて出力される前記画素センサ信号は、前記ディスプレイ画素アレイにおける同一の前記ディスプレイ画素からそれぞれ出力される、請求項18に記載の装置。

#### 【請求項20】

前記読み出し段階のそれぞれは、複数のフレーム期間において前記ディスプレイ画素アレイにおける全ての前記ディスプレイ画素の前記画素センサ信号が出力されるように、前記複数のフレーム期間のそれぞれの間に、前記ディスプレイ画素アレイにおける異なる部分の前記ディスプレイ画素の前記画素センサ信号をそれぞれ出力するように設定されている、請求項18に記載の装置。

#### 【請求項21】

前記ディスプレイ画素アレイにおける一部の前記ディスプレイ画素は、少なくとも1つの前記ディスプレイ画素の口ウを有する1または複数のディスプレイ画素のグループである、請求項18に記載の装置。

#### 【請求項22】

前記ディスプレイ画素のグループが複数であって、各グループが、前記ディスプレイ画素アレイの前記カラムの方向に実質的に均等に間隔を開けて設定されている、請求項21 に記載の装置。

#### 【請求項23】

前記各グループは、相互に隣接する複数の前記ディスプレイ画素の口ウを含む、請求項22に記載の装置。

# 【請求項24】

前記コントローラは、前記データ信号生成器および前記スキャン信号生成器ならびに前記出力構成の動作を、前記イメージデータ信号を前記ディスプレイ画素アレイに書き込み、同時に、前記ディスプレイ画素からセンサ信号を読み出すように制御する、請求項1に記載の装置。

# 【請求項25】

前記データ信号生成器は、前記カラムデータ線のうちの第1のカラムデータ線に前記イメージデータ信号を供給するように構成され、前記出力構成は、同時に、該第1のカラムデータ線とは異なる第2のカラムデータ線からセンサ信号を読み出すように構成される、請求項24に記載の装置。

#### 【請求項26】

前記画素センサ信号が、前記液晶素子の電荷である、請求項1に記載の装置。

#### 【請求項27】

前記出力構成は、前記カラムデータ線に接続されている複数のセンスアンプを含む、請求項1に記載の装置。

#### 【請求項28】

前記センスアンプの数は、前記カラムデータ線の数より少なく、該センスアンプのそれ ぞれは、第1のマルチプレクサによって、該カラムデータ線のセットのいずれか1つに接 続可能である、請求項27に記載の装置。

# 【請求項29】

前記出力構成は、前記センスアンプの出力に接続された複数のアナログ/デジタル変換

器を含む、請求項27に記載の装置。

#### 【請求項30】

前記アナログ / デジタル変換器の数は、前記センスアンプの数よりも少なく、該センスアンプのそれぞれは、第 2 のマルチプレクサによって、前記センスアンプ出力のセットのいずれか 1 つに接続可能である、請求項 2 9 に記載の装置。

# 【請求項31】

前記出力構成は、前記アナログ / デジタル変換器からの並列出力を直列出力に変換するシフトレジスタを含む、請求項 2 9 に記載の装置。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、アクティブマトリクスディスプレイおよびセンサ装置に関する。

【背景技術】

[0002]

アクティブマトリクス液晶ディスプレイ(AMLCD)は、入力機能を必要とする製品において用いられ得る。例えば、携帯電話および携帯情報端末(PDA)は、ユーザに対して、AMLCD上で情報を表示し、例えば、電話のキーパッドからのユーザによる入力を要求し得る。その代わりに、または、それに加えて、AMLCDは、環境条件、例えば、周囲光または温度に自動的に適応することが必要とされ得る。このような場合、センサは装置の外部からの入力を受け付けることが必要である。公知の構成において、このようなセンサ機能性は、追加の部品をディスプレイに付け加えることによって提供されてきた。例えば、タッチ入力を提供して、「タッチスクリーン」を形成するために、追加の層がディスプレイの前面に付け加えられる必要がある。従って、このような機能性を提供することは、このような装置をより複雑にし、コストを高めることになる。

[0003]

T Tanakaらの「Entry of Data and Command for an LCD by Direct Touch: An Integrated LCD Panel」(SID 1986)は、パッシブマトリクスディスプレイにタッチセンサ機能を提供する構成を開示する。この構成において、タッチ入力によって引き起こされる液晶層の任意のキャパシタンス変化は、パッシブマトリクススキャンおよびデータ線を用いて検出される。しかし、性能が制限され、ディスプレイを形成するパネルから切り離して適切なディスプレイドライバおよびセンサ回路を提供する必要があることによって、より複雑になり、コストが高くなる。

[0004]

US 6 028 581は、集積センサ構成を有するアクティブマトリクス液晶ディスプレイを開示する。この構成において、フォトダイオードは、各ピクセル(画素)において集積され、例えば手書き入力用のペンによる、タッチ入力を検出するか、またはディスプレイ上に形成されるイメージを検出するように構成される。しかし、このような構成は、アクティブマトリクスの変化を必要とし、実質的にフィルファクターを低減させ、従って、ディスプレイの画質を低減させる。

[0005]

JP5-250093は、入力ペンがディスプレイと接触している場合に、その座標を検出する構成を有するアクティブマトリクス液晶ディスプレイを開示する。入力ペンは、固定された電圧を生成し、ペンが接触している信号電極線上のデータを変化させる。変化した信号と入力データとの間の差は、接触の点を決定するために用いられる。入力ペンによって引き起こされる信号は、アドレシングマトリクスにおいて示され、これは、液晶層を必要としない。

【非特許文献1】T Tanakaら、「Entry of Data and Command for an LCD by Direct Touch: An Integrated LCD Panel」(SID 1986)

10

20

30

40

【特許文献1】米国特許第6028581号明細書

【特許文献2】特開平5-250093号公報

【発明の開示】

【課題を解決するための手段】

[0006]

(発明の要旨)

本発明のアクティブマトリクスディスプレイおよびセンサ装置は、複数のロウおよび複 数のカラムにディスプレイ画素が配列されており、前記各ディスプレイ画素のそれぞれは 、液晶素子を有するとともに、表示されるイメージデータ信号を受信するディスプレイデ ータ入力および該ディスプレイデータ入力からの前記イメージデータ信号の入力をイネー ブルするスキャン信号を受信するスキャン入力を有し、前記各カラムに配列された前記各 ディスプレイ画素の前記ディスプレイデータ入力は、複数のカラムデータ線のそれぞれに 接続され、前記各口ウに配列された前記各ディスプレイ画素の前記スキャン入力は、複数 のロウスキャン線のそれぞれに接続されている、ディスプレイ画素アレイと、前記イメー ジデータ信号を前記各カラムデータ線に供給するデータ信号生成器と、前記スキャン信号 を前記各ロウスキャン線に供給するスキャン信号生成器と、外部刺激に応答して、前記デ ィスプレイ画素内での前記液晶素子のキャパシタンスの変化に基づいて生成される画素セ ンサ信号を出力するように前記カラムデータ線に接続されている出力構成と、前記イメー ジデータ信号が書き込みされていない前記カラムデータ線から前記画素センサ信号が前記 出力構成によって出力されるように、前記データ信号生成器、前記スキャン信号生成器お よび前記出力構成のうちの少なくとも1つを制御するコントローラとを備え、該コントロ ーラによって前記出力構成から出力される前記画素センサ信号が前記ディスプレイ画素の 光学的に変動した領域のみで生成されることを特徴とする。

[0008]

前記データ信号生成器、<u>前記</u>スキャン信号生成器、<u>前記</u>出力構成、および<u>前記ディスプレイ画素</u>アレイの電子部品が、ディスプレイ基板の上に<u>形成されていてもよい。前記</u>データ信号生成器は前記<u>ディスプレイ画素</u>アレイの第1の端に沿って配置され、<u>前記</u>出力構成は<u>該ディスプレイ画素</u>アレイの<u>該</u>第1の端の反対の第2の端に沿って配置されてもよい。

[ 0 0 0 9 ]

前記ディスプレイ画素のそれぞれは、電子スイッチを含んでもよい。前記ディスプレイ画素のそれぞれは、格納キャパシタを含んでもよい。前記電子スイッチのそれぞれは、薄膜トランジスタを含んでもよい。前記薄膜トランジスタのそれぞれは、前記スキャン入力に接続されているゲート、前記ディスプレイデータ入力に接続されているソース、および前記イメージ生成素子に接続されているドレインを有してもよい。

[0010]

<u>前記</u>コントローラは、前記ディスプレイ基板上に形成されてもよい。装置全体のアクティブデバイスが薄膜トランジスタとして形成されてもよい。

[0011]

前記コントローラは、前記画素センサ信号のうちのいずれが前記出力構成によって出力されるかを決定するようにプログラム化されてもよい。前記コントローラは、前記装置の動作中に、前記画素センサ信号のうちのいずれが前記出力構成によって出力されるかを変更するように再プログラム可能であってもよい。前記コントローラは、前記イメージデータ信号の書き込み段階と、前記画素センサ信号が前記出力構成によって出力される読み出し段階とが交互に実施されるように、前記データ信号生成器およびスキャン信号生成器ならびに前記出力構成を制御するように構成してもよい。前記書き込み段階のそれぞれの間に、1フレームの前記イメージデータ信号が前記ディスプレイ画素アレイに書き込まれてもよい。前記書き込み段階の間の垂直帰線消去期間に、前記読み出し段階が設定されてもよい。

10

20

30

# [0012]

<u>前記</u>書き込み段階のそれぞれの間に、少なくとも1つの<u>前記ディスプレイ画素の口ウに前記イメージデータ信号が</u>書き込まれてもよい。<u>前記</u>読み出し段階<u>において</u>、<u>少なくとも1つの前記ディスプレイ画素</u>の口ウから前記<u>画素</u>センサ信号<u>が</u>出力<u>された後に</u>、<u>前記</u>書き込み段階の間に<u>前記</u>イメージデータ<u>信号</u>が前記<u>ディスプレイ画素の</u>ロウ<u>に書き込まれても</u>よい。

# [0013]

<u>前記</u>読み出し段階のそれぞれの間<u>に</u>、<u>前記ディスプレイ画素アレイにおける全ての前記</u> ディスプレイ画素の前記画素センサ信号が出力されてもよい。

[0014]

前記 読み出し段階のそれぞれの間に、前記ディスプレイ画素アレイにおける一部の前記 ディスプレイ 画素の前記画素 センサ信号が出力されてもよい。前記読み出し段階のそれぞれにおいて出力される前記画素センサ信号は、前記ディスプレイ画素アレイにおける同一の前記ディスプレイ 画素 からそれぞれ出力されてもよい。前記読み出し段階のそれぞれは、複数のフレーム期間において前記ディスプレイ画素アレイにおける全ての前記ディスプレイ画素の前記画素 センサ信号が出力されるように、前記複数のフレーム期間のそれぞれの間に、前記ディスプレイ画素アレイにおける異なる部分の前記ディスプレイ画素の前記画素 センサ信号をそれぞれ出力するように設定されてもよい。

[0015]

前記ディスプレイ画素アレイにおける一部の前記ディスプレイ画素は、少なくとも1つの前記ディスプレイ画素の口ウを有する1または複数のディスプレイ画素のグループであってもよい。前記ディスプレイ画素のグループが複数であって、各グループが、前記ディスプレイ画素アレイの前記カラムの方向に実質的に均等に間隔を開けて設定されていてもよい。前記各グループは、相互に隣接する複数の前記ディスプレイ画素の口ウを含んでもよい。

[0016]

<u>前記</u>コントローラは、<u>前記</u>データ<u>信号生成器</u>および<u>前記</u>スキャン信号生成器ならびに<u>前</u>記出力構成の動作を、<u>前記</u>イメージデータ信号を前記<u>ディスプレイ画素</u>アレイに書き込み、同時に、<u>前記ディスプレイ</u>画素からセンサ信号を読み出すように<u>制御してもよい</u>。前記データ信号生成器は、<u>前記カラム</u>データ線のうちの第1の<u>カラム</u>データ線に<u>前記</u>イメージデータ信号を供給するように構成され、<u>前記</u>出力構成は、同時に、該第1の<u>カラム</u>データ線とは異なる<u>第2のカラム</u>データ線からセンサ信号を読み出すように構成されても<u>よい</u>。

前記画素センサ信号が、前記液晶素子の電荷であってもよい。

[0018]

前記出力構成は、前記カラムデータ線に接続されている複数のセンスアンプを含んでもよい。前記センスアンプの数は、前記カラムデータ線の数より少なく、 $\overline{b}$ センスアンプのそれぞれ<u>は、</u>第1のマルチプレクサによって、該<u>カラム</u>データ線のセットのいずれか1つに接続可能であってもよい。前記出力構成は、前記センスアンプの出力に接続された複数のアナログ / デジタル変換器を含んでもよい。前記アナログ / デジタル変換器の数は、前記センスアンプの数よりも少なく、該センスアンプのそれぞれは、第2のマルチプレクサによって、前記センスアンプ出力のセットのいずれか1つに接続可能であってもよい。前出力構成は、前記アナログ / デジタル変換器からの並列出力を直列出力に変換するシフトレジスタを含んでもよい。

【発明の効果】

10

20

30

40

#### [0019]

本発明によれば、センサ機能性がアクティブマトリクスディスプレイ、例えば、アクティブマトリクス液晶ディスプレイに集積された装置を提供することが可能である。アクティブマトリクスを入力の手段として用いることによって、検知機能性を提供するために、アクティブマトリクスまたはドライバ回路を変更することが必要とされない。ピクセルアパーチャを低減する必要もないし、フィルファクターを低減する必要もないので、検知機能性を組み込むことによってディスプレイ品質が損なわれる必要はない。アクティブマトリクスおよびドライバ構成は、標準的な設計のものであってよく、さらなる検知機能性は、例えば、アクティブマトリクスの他の場合には用いられない側面に沿ってさらなる回路を集積することによって提供され得る。

[0020]

プログラマブルなコントローラを有する実施形態において、ソフトウェアによって、例えば、特定のアプリケーションの要件に従って、センサおよび / またはディスプレイ動作が制御され得る装置を提供することが可能である。従って、アプリケーションによる各種の動作モードにおいて、同じ1つの装置が用いられ、実際の動作モードを規定するソフトウェアまたはプログラムは、外部ソース、例えば、イメージデータを装置に供給するハードウェアおよびソフトウェアの処理から容易に提供され得る。またこのようなプログラミングが表示されたイメージに関連付けられ、動作中に変更されることも可能である。例えば、制御アイコンがディスプレイに送られる場合、さらなるハードウェアまたはさらなる層が提供される必要なしに、タッチディスプレイ機能を提供するように、アイコンの領域におけるタッチに応答するように、装置は同時に構成され得る。

【発明を実施するための最良の形態】

[0021]

図面を通じて、同一の参照符号は同一の部材を指す。

[0022]

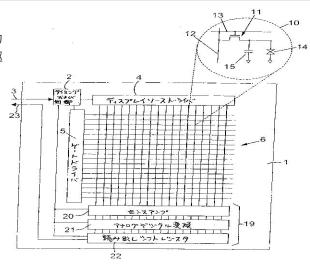

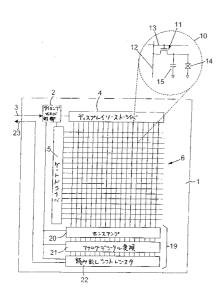

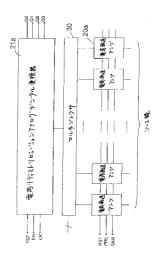

アクティブマトリクス液晶ディスプレイおよびセンサ装置は、図式的に1で表されたディスプレイ基板上に形成され、表示されるべきイメージデータとともにタイミングおよび制御信号を受信する入力3に接続されたタイミングおよび制御回路2を含む。回路2は、ディスプレイソースドライバ4の形のデータ信号生成器、およびゲートドライバ5の形のスキャン信号生成器に適切な信号を供給する。ドライバ4および5は、任意の適切なタイプ、例えば、標準または従来型のドライバであってよく、これ以上は説明されない。

[0023]

ディスプレイソースドライバ4は、6で示された画素(ピクセル)のアクティブマトリクスのカラムデータ線として機能する複数のマトリクスカラム電極に接続されているが、切り離され得る複数の出力を有する。ディスプレイソースドライバ出力は、ドライバが制御回路2によってイネーブルされる場合、例えば、データ線に接続されるのみである。カラム電極はアクティブマトリクス6の高さにわたって伸び、それぞれ、ピクセルのカラムのデータ入力に接続される。同様に、ドライバ5は、マトリクス6の幅にわたって伸びる口ウ電極に接続されている複数の出力を有する。各口ウ電極は、ロウスキャン線として機能し、それぞれのロウのピクセルのスキャン入力に接続されている。

[0024]

ピクセルのうちの1つを、10でより詳細に示す。ピクセルは、標準的なアクティブマトリクス液晶タイプのピクセルである。ピクセル10は、ポリシリコン薄膜トランジスタの形の電子スイッチ11を含む。ポリシリコン薄膜トランジスタから構成された電子スイッチ11のソースは、カラム電極12に接続され、ゲートは、ロウ電極13に接続され、ドレインは、液晶ピクセルイメージ生成素子14および並行格納キャパシタ15に接続される。

[0025]

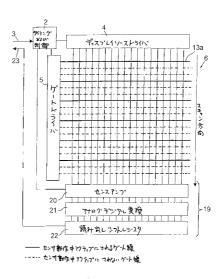

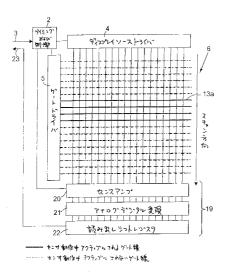

図1は、この構成の様々な部品の物理的なレイアウトを図式的に表す。全ての電子部品は、ディスプレイソースドライバ4がマトリクス6の上端に沿って配置され、ゲートドラ

10

20

30

40

イバ5がマトリクス6の左端に沿って配置された状態で、ディスプレイ基板1上に集積される。ドライバ4および5、ならびにマトリクス6と、これらの相対的な配置とは、標準的なものまたは従来のものであってよい。

# [0026]

この構成は、さらに、マトリクス6の下端に沿って配置された出力構成19を含む。構成19は、回路2からの制御信号によって、制御、例えばイネーブルされる複数のセンスアンプ20を含む。これらの複数のセンスアンプ20の出力は、それぞれ、カラム電極に接続される。センスアンプの出力は、アナログデジタル変換ブロック21に供給される。アナログデジタル変換ブロック21は、センスアンプ20によって検知されたアナログ値を並列デジタル出力に変換する。変換ブロック21の出力は、読み出しシフトレジスタ22に接続される。読み出しシフトレジスタ22は、並列出力データを直列出力データに変換して、この構成のセンス出力23に供給する。

#### [0027]

口ウおよびカラムについて言及する場合、水平の口ウおよび垂直のカラムに限定することを意図するものではなく、イメージデータが口ウ毎に入力される標準的な周知の様式について言及される。ディスプレイにおいて、通常は、ピクセルロウは水平に構成され、カラムは垂直に構成されるが、このような構成は必須ではなく、口ウを、例えば、垂直に構成して、カラムを水平に構成してもよい。

#### [0028]

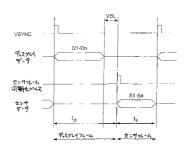

使用において、ディスプレイのイメージデータは、任意の適切なソースによって、この構成の入力3に供給され、ドライバ4および5の動作に従って、アクティブマトリクス6によって表示される。例えば、ディスプレイがロウごとにリフレッシュされる典型的な構成において、図2に示すように、各フレームリフレッシュサイクルの始まりを示すフレーム同期化パルスVSYNCとともに、直列に供給される。ピクセルイメージデータのロウは、ディスプレイソースドライバ4において、次々に入力され、スキャン信号は、適切なピクセルのロウに格納されるイメージデータをイネーブルするために、適切なロウ電極に供給される。従って、マトリクス6のピクセルロウは、ゲートドライバ5が通常一度に1つのロウにスキャン信号を供給し、上部ロウから開始して、フレームリフレッシュサイクルが完了したときに底部ロウで終了する状態で、一度に1つのロウずつリフレッシュされる。

# [0029]

図 2 に示す動作モードにおいて、各ディスプレイフレームは時間 t d を費やし、リフレッシュ部分を含む。リフレッシュ部分の間、ピクセルのマトリクス 6 を一度に 1 つのロウずつリフレッシュするためにディスプレイデータが用いられ、リフレッシュ部分後に、垂直帰線消去期間 V B L が続く。ディスプレイフレーム期間の終わりにおいて、センサフレーム同期化パルスは、装置の検知段階を形成する期間 t s のセンサフレームを開始するように供給される。

# [0030]

検知段階の間、ディスプレイソースドライバ4の出力は、カラム電極から切り離され、センスアンプ20は回路2によってイネーブルされる。その後、ゲートドライバ5はまた、マトリクス6の上部から底部へと、一度に1つずつ口ウ電極をスキャンし、センスアンプ20によって検知される信号は、変換ブロック21によってデジタルの形に変換され、シフトレジスタ22によって、一度に1つのロウずつ読み出される。シフトレジスタ22は、純粋な「1ビット」直列出力を生成するか、またはマルチビット直列ワード出力を生成し得る。

# [0031]

表示段階の間、ピクセル10がリフレッシュされるときに、ゲートドライバ5は、スキャン信号をロウ電極13に供給し、それにより薄膜トランジスタ11をオンにする。ディスプレイソースドライバ4は、イメージ生成素子の所望の表示状態を表す電圧を同時にカラム電極12に供給し、所望のイメージ外観を決定するための電荷が、カラム電極12か

10

20

30

40

10

20

30

40

50

ら格納キャパシタ15、および、イメージ生成液晶素子14へと転送される。イメージ生成液晶素子14も、キャパシタとして機能する。素子14にかけられる電圧は、素子に、公知の様態で所望のイメージのグレーレベルを表示させる。液晶ピクセルイメージ生成素子14は、表示動作を引き起こす光学的に変動可能な領域を含む。

# [0032]

10で示されるような標準的なディスプレイピクセルは、あらゆる実質的な変更を必要とすることなく、外部刺激を検知するために用いられ得る。例えば、T.Tanakaらの「Entry of Data and Command for an LCD by Direct Touch: An Integrated LCD Panel」(SID 1986)に開示されているように、各ディスプレイピクセルは、タッチ入力を検出するために用いられ得る。LCDアセンブリの上部ガラスプレートに印加される圧力は、圧力が印加される領域の周りの液晶の変形の原因となる。この変形は、液晶素子14のキャパシタンスの検出可能な変化を引き起こす。このキャパシタンスの変化は、液晶素子14の光学的に変動可能な領域によって、その内部で生成された信号を表す。

### [0033]

検知段階の間、ピクセル10を含むロウがロウ電極13の上のドライバ5からのスキャン信号によってイネーブルされるときに、素子14は、キャパシタ15と共に、トランジスタ11によって、カラム電極12に接続される。従って、ピクセル内の特徴の外部刺激の結果としてのあらゆる変化は、カラム電極12に接続されたセンスアンプ20のうちの1つに対してアクセス可能にされる。このことにより、刺激によって得られる特徴は、センスアンプによって、アナログ値に変換される。センスアンプによって検知された特徴は、ピクセル電圧、電流、格納された電荷またはキャパシタンス、あるいは、これらの任意の組合せであってもよい。

#### [0034]

動作のサイクルは、ディスプレイデータの次のフレームを用いてディスプレイのリフレッシュを開始させるVSYNCパルスから開始されて繰り返される。ディスプレイフレーム時間t<sub>α</sub>は、センサフレーム時間t<sub>。</sub>と等しくてもよいし、等しくなくてもよい。

# [0035]

図2は、前のディスプレイフレームの垂直帰線消去期間VBL後に発生するセンサフレームを示すが、センサフレームは、ディスプレイフレームの消去期間内に発生してもよい。ロウの全ては、センサフレームの間のセンサデータについてスキャンされ得る。あるいは、ピクセルのロウの異なる適切なサブセットは、複数のフレームのそれぞれの間、複数のディスプレイフレームの期間にわたってセンサデータについてマトリクス全体がスキャンされるように、スキャンされ得る。例えば、センサデータについてスキャンされるロウのパターンは、ディスプレイフレームレートに依存し得、スキャンされるロウのパターンは、タイミングおよび制御回路2内のソフトウェアによって決定され得る。このような構成は、センサフレームの間にマトリクス全体をスキャンする場合と比較して、表示されるイメージの質を向上させるために用いられ得、ディスプレイが、検知機能性を提供しない従来のディスプレイのフレームレートと同じ速さにフレームレートを維持することを可能にする。本明細書中で用いられる用語「適切なサブセット」は、空のセットおよび完全なセットを除く、完全なセットのサブセットであると定義される。

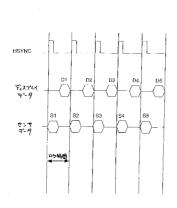

#### [0036]

図3は、表示および検知段階が、各口ウのリフレッシュ期間または口ウ時間の間に行われる、別の動作モードを示す図である。各口ウ時間の始まりは、水平同期化パルスHSYNCによって規定される。マトリクス6のピクセルの第1の口ウまたは上部口ウは、ゲートドライバ5のフレームの第1のスキャンパルスによってイネーブルされ、第1の口ウのピクセル10のトランジスタ11がオンにスイッチされ、その口ウの液晶素子14が、格納キャパシタ15と共に、それぞれのカラム電極12に接続される。回路2は、センスアンプ20をイネーブルし、ディスプレイソースドライバ出力は、検知動作を妨害しないように、電極12から切断されるか、または絶縁される。ディスプレイソースドライバ4が

イナクティブである場合、その出力が電極12から切り離されるようなディスプレイソースドライバである実施形態において、変更は必要なく、ドライバ4は標準的なタイプまたは公知のタイプのドライバであってよい。あるいは、ドライバ回路の設計に起因して、ドライバ出力が切り離されない場合、電極12からの出力を切り離す手段が提供され、回路2によって制御される。

# [0037]

図3において、第1のロウのセンサデータは、S1で開始する。検知段階の終わりにおいて、出力構成19は、回路2によって、マトリクス6のイネーブルされた第1のロウのピクセル特徴に応答しないようにされる。所望のピクセル光学特徴についての適切なアナログ電圧の形のディスプレイデータは、ディスプレイソースドライバ4によって、カラム電極12に供給され、各ピクセルについての適切な電荷は、素子14に転送される。その後、第1のロウのスキャン信号が、ゲートドライバ5によってディセーブルされ、ピクセル10のトランジスタ11がオフにスイッチされて、素子14をカラム電極12から切り離す。これで、マトリクス6の第1のロウのリフレッシュが完了する。

### [0038]

この動作サイクルは、マトリクス全体がセンサ信号についてスキャンされ、イメージデータのフレームを用いてリフレッシュされるまで、マトリクス6の各口ウについて、繰り返される。検知段階において、各ピクセルに格納されたディスプレイデータが壊れたり、破壊されたりする可能性があるので、検知段階は、マトリクス6の各口ウについて、ディスプレイリフレッシュ段階の前に行われる。

#### [0039]

図4は、イメージデータの各フレームによって、マトリクス6全体がリフレッシュされるが、検知段階の間N番目のピクセルのロウ(ただし、Nは1よりも大きい整数であり、図4に示す実施形態においては値3)のみが用いられる、他の動作モードを示す図である。この動作モードは、図2および3に示したモードのいずれかを用いて行われ得る。Nの値を選択することによって、検知機能の空間的解像度が、要件に従って選択され得る。多くの適用例において、必要とされる検知解像度は、必要とされる表示解像度よりも実質的に低い。検知段階の間にスキャンされるロウの数を低減することによって、電力消費および検知段階の間のマトリクス6のスキャンにかかる時間が低減される。

# [0040]

検知段階の間スキャンされる実際のロウのパターンは、タイミングおよび制御回路2内のソフトウェアによって決定され得る。例えば、Nの値は、装置の入力3に供給される信号のソースによって設定され得る。あるいは、検知の均一な解像度が必要とされない適用例において、検知段階のロウのパターンは回路2において入力され得、検知されるロウはマトリクス6にわたって間隔が均一に開けられていなくてもよい。

# [0041]

図5は、センサ信号について一部のピクセルロウのみがスキャンされる、他の動作モードを示す図である。1群、この場合は、4つのピクセルの連続的なロウまたは隣接するロウは、各センサフレームの間、検知のためにスキャンされる。上記と同様、スキャンされるロウの数は、回路2内のソフトウェアによって決定され得る。さらに、このモードは、図4に示すモードと組み合わされてもよく、この場合、互いから間隔を開けられた連続的なロウの群が、検知のためにスキャンされる。

# [0042]

図 4 および 5 において、センサ動作の間にスキャンされるロウは、例えば、 1 3 a のように、太線で示される。

# [0043]

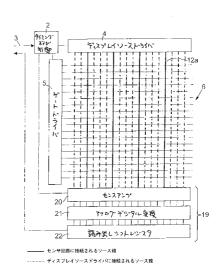

図 6 は、センサ動作の間、一部のピクセルのカラムのみがスキャンされる、さらなる動作モードを示す図である。上記と同様、スキャンされるカラムは、1 2 a のように太線で示されている。このモードにおいて、表示および検知動作は、同時に実行されるが、ピクセルの各カラムは、検知または表示を行い、両方行うことはない。表示に用いられている

10

20

30

40

10

20

30

40

50

ピクセルのカラムは、カラム電極によってディスプレイソースドライバ4に接続され、検知に用いられているピクセルのカラムは、ドライバ4の出力から切り離され、センスアンプ20に接続されている。特に、表示機能は検知機能を妨害し、検知機能は表示機能を妨害するので、ピクセルの各カラムはディスプレイドライバ出力およびセンスアンプに同時に接続されない方がよい。

### [0044]

上記と同様、検知のためのカラムのパターンは、回路 2 内のソフトウェアによって決定され得る。ドライバ4またはセンスアンプ 2 0 に接続されているソース線のパターンは、ロウ毎、かつ / または、フレーム毎に変化し得る。これらのパターンを制御する回路のプログラミングは、パターンを変化させるように、再プログラムすることによって、時刻毎に変化し得る。これは、検知および表示ピクセルの所望のパターンを得るために、ロウ毎またはフレーム毎に行われてもよい。

#### [0045]

上記の動作モードは、必ずしも相互排反でなくてもよく、組み合わせられてもよい。従って、あらゆる所望の表示または検知パターンを、不必要にピクセルをスキャンすることなく得ることができる。

# [0046]

これらの技術は、センサデータについてスキャンされるマトリクス6の領域を、表示されたイメージに関連付けるために用いられ得る。例えば、アイコンを表示して、アイコンが表示されている領域のみをセンサデータについてスキャンしてもよい。

#### [0047]

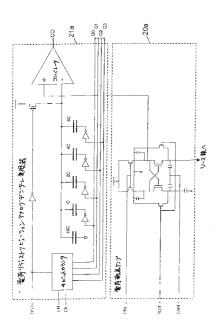

センスアンプ20およびアナログデジタル変換器21は、任意の適切な構成によって実施され、これらの適切な構成の例は、図7に示される。この例において、各センスアンプは、H.Morimuraらによる「A Novel Sensor Cell Architecture and Sensing Circuits Scheme for Capacitive Fingerprint Sensors」(IEEE Journal of Solid‐State Circuits、vol.35、no.5、2000年5月)に記載されているように、電荷転送アンプ20aとして実施されている。各変換器は、21aで示すように、電荷リディストリビューションアナログデジタル変換器として実施され得る。この変換器は、D.JohnsおよびK.Martinによる「Analogue Integrated Circuit Design」(Wiley、1997年)に開示されている。両方の文書の内容は、本明細書中で参考として援用され、従って、これらの構成は、さらに説明されない。

### [0048]

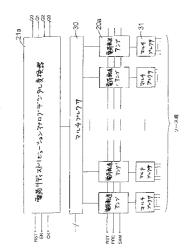

図8は、アナログデジタル変換器21aの数が電荷転送アンプ20aの数より少ない構成を示す図である。この場合、各変換器21aは、マルチプレクサ30を介して、いくつかの電荷転送アンプ20aの出力に接続される。マルチプレクサ30は、一度に1つずつのアンプ20aを変換器21aの入力に接続するように制御される。図9は、電荷転送アンプ20aの数がカラム電極12の数よりも少ないこの構成の変形例を示す図である。各電荷転送アンプ20aは、マルチプレクサ31がカラム電極を一度に1つずつ対応するアンプ20aの入力に接続するように構成されている状態で、さらなるマルチプレクサ30によってカラム電極12のセットに接続される。このような構成は、出力構成に必要な基板面積を低減させ、ディスプレイ解像度を低くし、ディスプレイサイズを大きくする必要を無くすために用いられ得る。

#### [0049]

出力構成19は、ドライバ4および5、ならびにアクティブマトリクス6をディスプレイ基板上に形成するための公知の技術のいずれかを用いて、基板1上に形成され得る。例えば、装置全体のアクティブデバイスは、ポリシリコン薄膜トランジスタとして形成され得る。従って、製造プロセスの間、工程をさらに追加することなく、または実質的に追加することなく、出力構成19を追加することが可能である。

#### [0050]

従って、集積されたセンサ機能性を標準的な実質的に変更されていないタイプのアクティブマトリクス液晶ディスプレイに追加する装置を提供することが可能である。ドライバ4 および 5 、ならびにアクティブマトリクスディスプレイ 6 は、標準的なタイプまたは公知のタイプのディスプレイであってよく、センサ機能性を提供するために変更、または実質的な変更を必要としない。従って、ディスプレイの外観は、センサ機能性によって影響される必要はなく、出力構成 1 9 を基板 1 の他の場合には用いられない部分に追加することによって効率的に提供される。スキャンパルスのタイミングおよびシーケンスを制御することによって、構成は、例えば、表示および検知段階の異なるモードを提供するなど、異なる様態で動作し得る。また、検知の解像度および頻度は、回路 2 に提供される制御信号によって設定され得る。

10

#### [0051]

センサ機能性をAMLCDなどのアクティブマトリクスディスプレイに組み込む装置が提供される。LCDピクセル10のアクティブマトリクス6には、標準的なディスプレイソースドライバ4およびゲートドライバ5が設けられる。ディスプレイソースドライバ4は、センスアンプ20を含む出力構成19にも接続されているカラム電極12に応答する必要なピクセル応答を生成するデータ信号を供給する。動作の表示段階の間、AMLCDは、マトリクス6が一度に1ロウずつ、フレームごとにリフレッシュされる状態で、動作する。フレーム間において、センスアンプ20がイネーブルされ、マトリクス6がまた、ゲートドライバ5によってスキャンされる。各ピクセルの特徴は、関連するセンスアンプ20によって検知され、構成の出力23で供給される外部刺激を表す。

20

#### [0052]

以上のように、本発明の好ましい実施形態を用いて本発明を例示してきたが、本発明は、この実施形態に限定して解釈されるべきものではない。本発明は、特許請求の範囲によってのみその範囲が解釈されるべきであることが理解される。当業者は、本発明の具体的な好ましい実施形態の記載から、本発明の記載および技術常識に基づいて等価な範囲を実施することができることが理解される。本明細書において引用した特許、特許出願および文献は、その内容自体が具体的に本明細書に記載されているのと同様にその内容が本明細書に対する参考として援用されるべきであることが理解される。

【図面の簡単な説明】

30

40

# [0053]

【図1】図1は、本発明の実施形態を構成するアクティブマトリクスディスプレイおよび センサ構成の模式的なブロック図である。

- 【図2】図2は、図1の装置の動作の第1のモードを示すタイミング図である。

- 【図3】図3は、図1の装置の動作の第2のモードを示すタイミング図である。

- 【図4】図4は、図1の装置の動作のさらなるモードを示す図1に類似する図である。

- 【図5】図5は、図1の装置の動作のさらなるモードを示す図1に類似する図である。

- 【図6】図6は、図1の装置の動作のさらなるモードを示す図1に類似する図である。

- 【図7】図7は、図1の装置のセンスアンプおよび変換器を示す回路図である。

- 【図8】図8は、図1の装置の出力構成の第1の例を示す模式的なブロック図である。

- 【図9】図9は、図1の装置の出力構成の第2の例を示す模式的なブロック図である。

【符号の説明】

# [0054]

- 2 タイミングおよび制御

- 4 ディスプレイソースドライバ

- 5 ゲートドライバ

- 20 センスアンプ

- 2.1 アナログデジタル変換

- 2.2 読み出しシフトレジスタ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

# フロントページの続き

(51) Int.CI. F I

G 0 9 G 3/20 6 8 0 H

(56)参考文献 特開平05-250093(JP,A)

特開平09-159995(JP,A)

特開平02-264581(JP,A)

特開昭61-006729(JP,A)

特開平09-080467(JP,A)

特開平02-226225(JP,A)

(58)調査した分野(Int.CI., DB名)

G 0 9 G 3 / 3 6

G02F 1/133

G 0 9 G 3 / 2 0

| 专利名称(译)        | 显示和传感器设备                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|--|

| 公开(公告)号        | JP4201191B2                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2008-12-24 |  |  |  |  |

| 申请号            | JP2004052558                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2004-02-26 |  |  |  |  |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |  |  |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |  |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |  |

| [标]发明人         | クリスジェイブラウン                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |  |

| 发明人            | クリス ジェイ. ブラウン                                                                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |  |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20 G02F1/1362 G06F3/033 G06F3/041                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |  |

| CPC分类号         | G06F3/0412 G02F1/13338 G02F1/13454                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |  |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.612.T G09G3/20.624.Z G09G3/20.680.G G09G3/20.680.H G06F3/033.350.A G06F3/041.320.A G06F3/041.412                                                                                                                                                                                                                                                                   |         |            |  |  |  |  |

| F-TERM分类号      | 2H093/NA16 2H093/NC22 2H093/NC24 2H093/NC52 2H093/ND60 2H093/NE01 2H193/ZA04 2H193 /ZH25 2H193/ZJ02 2H193/ZP01 5B087/AA02 5B087/AA09 5B087/CC11 5B087/CC33 5C006/AF44 5C006/AF73 5C006/AF81 5C006/BB16 5C006/BC02 5C006/BC20 5C006/BF03 5C006 /BF14 5C006/BF22 5C006/BF25 5C006/BF37 5C006/EC05 5C006/FA51 5C080/AA10 5C080/BB05 5C080/DD21 5C080/DD27 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 |         |            |  |  |  |  |

| 审查员(译)         | 福村 拓                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |  |

| 优先权            | 2003004587 2003-02-28 GB                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |  |  |

| 其他公开文献         | JP2004264845A                                                                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |  |  |  |  |

# 摘要(译)

提供了一种用于将传感器功能结合到诸如AMLCD的有源矩阵显示器中的装置。在LCD像素10的有源矩阵6中,提供标准显示源驱动器4和栅极驱动器5。显示源驱动器4提供数据信号,该数据信号响应于列电极12产生必要的像素响应,列电极12也连接到包括读出放大器20的输出装置19。 全在操作的显示阶段期间,AMLCD在矩阵6逐帧刷新的情况下操作,一次 一行。在帧之间,读出放大器20被启用,矩阵6也被栅极驱动器5扫描。每个像素的特征表示由相关联的读出放大器20感测并在配置的输出23处提供的外部刺激。点域1