## (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第3858590号 (P3858590)

(45) 発行日 平成18年12月13日(2006.12.13)

(24) 登録日 平成18年9月29日 (2006.9.29)

| (51) Int.C1. |       |                               | F 1            |          |                     |            |         |

|--------------|-------|-------------------------------|----------------|----------|---------------------|------------|---------|

| G02F         | 1/133 | (2006.01)                     | GO2F           | 1/133    | 550                 |            |         |

| G09G         | 3/20  | (2006.01)                     | GO2F           | 1/133    | 520                 |            |         |

| G09G         | 3/36  | (2006.01)                     | GO9G           | 3/20     | 622B                |            |         |

|              |       |                               | GO9G           | 3/20     | 623B                |            |         |

|              |       |                               | GO9G           | 3/20     | 624C                |            |         |

|              |       |                               |                |          | 請求項の数 24            | (全 18 頁)   | 最終頁に続く  |

| (21) 出願番号    |       | 特願2000-369608                 | (P2000-369608) | (73) 特許村 | <b>准者</b> 000005108 |            |         |

| (22) 出願日     |       | 平成12年11月30日 (2000.11.30)      |                |          | 株式会社日立              | <b>操作所</b> |         |

| (65) 公開番号    |       | 特開2002-169138 (P2002-169138A) |                |          | 東京都千代田区             | 区丸の内一丁目    | 6番6号    |

| (43) 公開日     |       | 平成14年6月14日 (2002.6.14)        |                | (74) 代理/ | 人 100100310         |            |         |

| 審査請求日        |       | 平成16年2月18日                    | (2004. 2. 18)  |          | 弁理士 井上              | 学          |         |

|              |       |                               |                | (72) 発明報 | 皆 古橋 勉              |            |         |

|              |       |                               |                |          | 神奈川県川崎市             | 7麻生区王禅寺    | ₹1099番地 |

|              |       |                               |                |          | 株式会社日立              | Z製作所 シス    | 、テム開発研究 |

|              |       |                               |                |          | 所内                  |            |         |

|              |       |                               |                | (72) 発明者 | 者 大石 純久             |            |         |

|              |       |                               |                |          | 神奈川県川崎市             | 7麻生区王禅寺    | ₹1099番地 |

|              |       |                               |                |          | 株式会社日立              | Z製作所 シス    | テム開発研究  |

|              |       |                               |                |          | 所内                  |            |         |

|              |       |                               |                |          |                     |            |         |

|              |       |                               |                |          |                     | <b>.</b>   | 1.数百に建了 |

|              |       |                               |                |          |                     | 再          | と終頁に続く  |

(54) 【発明の名称】液晶表示装置及び液晶表示装置の駆動方法

## (57)【特許請求の範囲】

#### 【請求項1】

ドレイン電圧とコモン電圧との電位差に応じて階調を表示する液晶パネルと、

前記表示データに対応した前記ドレイン電圧を生成し前記液晶パネルへ印加するドレインドライバ回路と、

前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路 と、

電位レベルが調整された基準コモン電圧と前記液晶パネルからフィードバックされたフィードバックコモン電圧とを比較演算し、比較演算の結果得られた前記コモン電圧を前記液晶パネルへ印加する電源回路とを備え、

前記電源回路は、前記液晶パネル内の<u>画素部の薄膜トランジスタ</u>のゲートをオフするためのゲートオフ電圧<u>であって前記コモン電圧と同期するゲートオフ電圧</u>を高インピーダンス化して前記ゲートドライバ回路に印加し、

前記電源回路は、前記ゲートオフ電圧を高電位レベル電圧と低電位レベル電圧とに分圧 する第1の抵抗と、前記高電位レベル電圧を増幅する第1の増幅回路と、前記低電位レベ ル電圧を増幅する第2の増幅回路と、前記高電位レベル電圧と前記低電位レベル電圧との 間に設けられ、前記ゲートドライバ回路へ印加する前記ゲートオフ電圧を高インピーダン ス化する第2の抵抗とを備えた液晶表示装置。

## 【請求項2】

前記液晶パネルに印加されるコモン電圧は、前記基準コモン電圧が高電位に遷移する場

合に、前記基準コモン電圧よりも更に高電位に遷移する請求項1に記載の液晶表示装置。

#### 【請求項3】

前記液晶パネルに印加されるコモン電圧は、前記基準コモン電圧が低電位に遷移する場合に、前記基準コモン電圧よりも更に低電位に遷移する請求項1に記載の液晶表示装置。

#### 【請求項4】

前記電源回路は、前記ゲートオフ電圧を前記基準コモン電圧と同位相で交流化し、前記ゲートドライバ回路に印加する請求項1に記載の液晶表示装置。

## 【請求項5】

前記電源回路は、前記ゲートドライバ回路へ印加する前記ゲートオフ電圧を抵抗により 分圧することによって、前記ゲートオフ電圧を高インピーダンス化する請求項1に記載の 液晶表示装置。

#### 【請求項6】

前記ドレイン電圧と前記コモン電圧との電位差が小さい場合の前記ゲートオフ電圧の振幅量は、前記ドレイン電圧と前記コモン電圧との電位差が大きい場合の前記ゲートオフ電圧の振幅量に比較して大きい請求項1に記載の液晶表示装置。

#### 【請求項7】

前記ゲートオフ電圧は、前記液晶パネル内の画素部の薄膜トランジスタが保持状態にある場合に、前記コモン電圧よりも低電位で、かつ、前記薄膜トランジスタが選択電圧レベルにならない電位である請求項1に記載の液晶表示装置。

#### 【請求項8】

前記電源回路は、基準コモン電圧の電位レベルを調整する演算回路と、前記<u>基準</u>コモン電圧と前記フィードバックコモン電圧とを比較演算する増幅回路と、比較演算されたコモン電圧の電流を増幅する電流増幅回路とを備える請求項1に記載の液晶表示装置。

#### 【請求項9】

前記フィードバックコモン電圧は、前記液晶パネルの上部側と中央部側の少なくとも1つから、前記電源回路へフィードバックされる請求項1に記載の液晶表示装置。

## 【請求項10】

前記電源回路は、前記走査ライン毎に、前記基準コモン電圧を交流化する請求項 1 に記載の液晶表示装置。

# 【請求項11】

液晶パネルと、

表示データに対応したドレイン電圧を生成し前記液晶パネルへ印加するドレインドライ バ回路と、

前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路と、

前記ドレイン電圧の基準となるコモン電圧を生成し前記液晶パネルへ印加する電源回路とを備え、

前記電源回路は、前記液晶パネル内の<u>画素部の薄膜トランジスタ</u>のゲートをオフするためのゲートオフ電圧<u>であって前記コモン電圧と同期するゲートオフ電圧</u>を高インピーダンス化して前記ゲートドライバ回路に印加し、

前記電源回路は、前記ゲートオフ電圧を高電位レベル電圧と低電位レベル電圧とに分圧 する第1の抵抗と、前記高電位レベル電圧を増幅する第1の増幅回路と、前記低電位レベ ル電圧を増幅する第2の増幅回路と、前記高電位レベル電圧と前記低電位レベル電圧との 間に設けられ、前記ゲートドライバ回路へ印加する前記ゲートオフ電圧を高インピーダン ス化する第2の抵抗とを備え、

前記液晶パネルと前記電源回路との間で伝送される前記コモン電圧は、<u>2種類</u>の異なる電圧波形を有する液晶表示装置。

## 【請求項12】

液晶パネルと、

表示データに対応したドレイン電圧を生成し前記液晶パネルへ印加するドレインドライ

20

10

30

40

(3)

バ回路と、

前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路 と、

前記液晶パネルの負荷定数又は前記表示データによるコモン電圧歪みの少なくとも 1 つに応じて、前記ドレイン電圧の基準となるコモン電圧を生成し、前記液晶パネルに印加する電源回路とを備え、

前記電源回路は、前記液晶パネル内の<u>画素部の薄膜トランジスタ</u>のゲートをオフするためのゲートオフ電圧<u>であって前記コモン電圧と同期するゲートオフ電圧</u>を高インピーダンス化して前記ゲートドライバ回路に印加し、

前記電源回路は、前記ゲートオフ電圧を高電位レベル電圧と低電位レベル電圧とに分圧 する第1の抵抗と、前記高電位レベル電圧を増幅する第1の増幅回路と、前記低電位レベ ル電圧を増幅する第2の増幅回路と、前記高電位レベル電圧と前記低電位レベル電圧との 間に設けられ、前記ゲートドライバ回路へ印加する前記ゲートオフ電圧を高インピーダン ス化する第2の抵抗とを備えた液晶表示装置。

#### 【請求項13】

液晶表示装置の駆動方法において、

表示データに対応したドレイン電圧を液晶パネルへ入力し、

前記ドレイン電圧の基準となるコモン電圧を電源回路から前記液晶パネルへ入力し、

前記液晶パネルから出力されたコモン電圧を前記電源回路へフィードバックし、

前記液晶パネル内の<u>画素部の薄膜トランジスタ</u>のゲートをオフするためのゲートオフ電圧<u>であって前記コモン電圧と同期するゲートオフ電圧</u>を高インピーダンス化して、前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路へ印加<u>し</u>

前記電源回路の備える第1の抵抗により前記ゲートオフ電圧を高電位レベル電圧と低電位レベル電圧とに分圧し、前記電源回路の備える第1の増幅回路により前記高電位レベル電圧を増幅し、前記電源回路の備える第2の増幅回路により前記低電位レベル電圧を増幅し、前記高電位レベル電圧と前記低電位レベル電圧との間に設けられた前記電源回路の備える第2の抵抗により前記ゲートドライバ回路へ印加する前記ゲートオフ電圧を高インピーダンス化する液晶表示装置の駆動方法。

#### 【請求項14】

液晶パネルと、

表示データに対応したドレイン電圧を生成し前記液晶パネルへ印加するドレインドライバ回路と、

前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路と、

前記液晶パネル内の<u>画素部の薄膜トランジスタ</u>のゲートをオフするためのゲートオフ電圧<u>であって前記液晶パネルに印加されるコモン電圧と同期するゲートオフ電圧</u>を高インピーダンス化し、前記ゲートドライバ回路に印加する電源回路とを備え、

<u>前記電源回路は、前記ゲートドライバ回路へ印加する前記ゲートオフ電圧を抵抗により</u> 分圧することによって、前記ゲートオフ電圧を高インピーダンス化する液晶表示装置。

## 【請求項15】

液晶パネルと、

表示データに対応したドレイン電圧を生成し前記液晶パネルへ印加するドレインドライ バ回路と、

前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路 と、

前記液晶パネルに印加されるコモン電圧と同期する高電位のゲートオフ電圧と低電位のゲートオフ電圧の間を抵抗により分圧することによって高インピーダンス化して前記ゲートドライバ回路に印加する電源回路とを備えた液晶表示装置。

## 【請求項16】

20

30

40

前記電源回路は、

<u>前記高電位レベル電圧と前記ゲートドライバ回路へ印加する前記ゲートオフ電圧との間</u>に設けられた第 1 のダイオードと、

<u>前記低電位レベル電圧と前記ゲートドライバ回路へ印加する前記ゲートオフ電圧との間</u>に設けられた第2のダイオードとを備えた請求項1に記載の液晶表示装置。

#### 【請求項17】

ドレイン電圧とコモン電圧との電位差に応じて階調を表示する液晶パネルと、

<u>前記表示データに対応した前記ドレイン電圧を生成し前記液晶パネルへ印加するドレイ</u>ンドライバ回路と、

<u>前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路</u> と、

電位レベルが調整された基準コモン電圧と前記液晶パネルからフィードバックされたフィードバックコモン電圧とを比較演算し、比較演算の結果得られた前記コモン電圧を前記液晶パネルへ印加する電源回路とを備え、

前記電源回路は、前記液晶パネル内の画素部の薄膜トランジスタのゲートをオフするためのゲートオフ電圧であって前記コモン電圧と同期するゲートオフ電圧を高インピーダンス化して前記ゲートドライバ回路に印加し、

前記ゲートドライバ回路は、前記走査ラインを選択した後に、当該走査ラインに低インピーダンスの前記ゲートオフ電圧を印加してから高インピーダンスの前記ゲートオフ電圧を印加する液晶表示装置。

#### 【請求項18】

前記ゲートドライバ回路は、前記ゲートオフ電圧を低インピーダンス化する第1のスイッチ回路と、前記ゲートオフ電圧を高インピーダンス化する第2のスイッチ回路を備えた 請求項17に記載の液晶表示装置。

## 【請求項19】

<u>前記第1のスイッチ回路は、ゲート幅の大きいN-MOS回路であり、</u>

<u>前記第2のスイッチ回路は、ゲート幅の小さいN-MOS回路である請求項18に記載</u>の液晶表示装置。

## 【請求項20】

液晶パネルと、

<u>表示データに対応したドレイン電圧を生成し前記液晶パネルへ印加するドレインドライ</u>バ回路と、

<u>前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路</u>と、

前記液晶パネル内の画素部の薄膜トランジスタのゲートをオフするためのゲートオフ電圧であって前記液晶パネルに印加されるコモン電圧と同期するゲートオフ電圧を高インピーダンス化し、前記ゲートドライバ回路に印加する電源回路とを備え、

前記電源回路は、前記ゲートオフ電圧を高電位レベル電圧と低電位レベル電圧とに分圧 する第1の抵抗と、前記高電位レベル電圧を増幅する第1の増幅回路と、前記低電位レベ ル電圧を増幅する第2の増幅回路と、前記高電位レベル電圧と前記低電位レベル電圧との 間に設けられ、前記ゲートドライバ回路へ印加する前記ゲートオフ電圧を高インピーダン ス化する第2の抵抗とを備えた液晶表示装置。

# 【請求項21】

前記電源回路は、

前記高電位レベル電圧と前記ゲートドライバ回路へ印加する前記ゲートオフ電圧との間 に設けられた第1のダイオードと、

<u>前記低電位レベル電圧と前記ゲートドライバ回路へ印加する前記ゲートオフ電圧との間</u>に設けられた第2のダイオードとを備えた請求項20に記載の液晶表示装置。

## 【請求項22】

液晶パネルと、

20

30

40

<u>表示データに対応したドレイン電圧を生成し前記液晶パネルへ印加するドレインドライ</u>バ回路と、

<u>前記ドレイン電圧を印加する液晶パネル中の走査ラインを選択するゲートドライバ回路</u>と、

前記液晶パネル内の画素部の薄膜トランジスタのゲートをオフするためのゲートオフ電圧であって前記液晶パネルに印加されるコモン電圧と同期するゲートオフ電圧を高インピーダンス化し、前記ゲートドライバ回路に印加する電源回路とを備え、

前記ゲートドライバ回路は、前記走査ラインを選択した後に、当該走査ラインに低インピーダンスの前記ゲートオフ電圧を印加してから高インピーダンスの前記ゲートオフ電圧を印加する液晶表示装置。

#### 【請求項23】

前記ゲートドライバ回路は、前記ゲートオフ電圧を低インピーダンス化する第1のスイッチ回路と、前記ゲートオフ電圧を高インピーダンス化する第2のスイッチ回路を備えた 請求項22に記載の液晶表示装置。

## 【請求項24】

前記第1のスイッチ回路は、ゲート幅の大きいN-MOS回路であり、

前記第2のスイッチ回路は、ゲート幅の小さいN-MOS回路である請求項22に記載 の液晶表示装置。

## 【発明の詳細な説明】

## [0001]

【発明の属する技術分野】

本発明は、液晶表示装置に係り、特に、TFT (Thin Film Transistor:薄膜トランジスタ)液晶表示パネルを交流化駆動方式で駆動する液晶表示装置に関する。

#### [00002]

## 【従来の技術】

コモン電圧の到達電圧を考慮した従来の技術として、特開平8-76083号公報には、液晶表示に必要な正又は負の駆動電圧に正又は負のプリチャージ電圧を加える液晶駆動装置が開示されている。また、特開平9-21995号公報には、所定の時定数で生成された微分信号をコモン駆動信号に重畳する液晶表示装置が開示されている。また、特開平10-253942号公報には、コモン電圧の到達電圧が遅延を生じている画素について、TFTがオフするタイミングのソース駆動回路の出力抵抗が高抵抗となる準備期間内に設定することにより、TFTがオフする直前のコモン電圧回路の負荷を実効的に減少させて、ソース駆動回路の出力抵抗が高抵抗となる瞬間にコモン電圧に、意図的にオーバシュートを発生させる液晶表示装置が開示されている。

## [0003]

ゲートオフ電圧の交流化を考慮した従来の技術として、特開2000-28992号公報には、Low電位を共通電位Vcomの高電位及び低電位と同期させて変化させ、かつ、Low電位と共通電位との電位差を、共通電位の高電位における電位差が共通電位の低電位における電位差より大にし、又は、Low電位を、共通電位Vcomの高電位及び低電位と同期させて変化させ、かつ、Low電位と共通電位Vcomとの電位差を等しくする液晶表示装置が開示されている。

## [0004]

#### 【発明が解決しようとする課題】

特開平8-76083号公報、特開平9-21995号公報及び特開平10-253942号公報に記載の技術では、横スメアと呼ばれる画質劣化まで考慮されていない。即ち、液晶パネルの負荷定数や表示内容によるコモン電圧歪みに応じて、液晶パネル内部のコモン電圧の最終到達電位が変化するため、表示領域毎に(例えば、中間輝度の背景のみの領域と白表示の短形が表示されている領域の左右の背景領域)電圧実効値が変化し、これにより表示領域毎に輝度が異なるといった、横スメアと呼ばれる画質劣化を生じる。

#### [0005]

特開2000-28992号公報に記載の技術でも、横スメアと呼ばれる画質劣化まで考慮されてい

10

20

30

40

20

30

40

50

ない。即ち、特開2000-28992号公報に記載の技術は、ゲートオフ電圧とコモン電圧とを同期させるため、表示内容に応じて交差容量や寄生容量に電流の流入出が発生し、これにより液晶パネルの入力部のドレイン電圧の電位レベルまでの収束性が鈍くなり、これにより液晶パネルに印加される表示領域毎に実効電圧値が低下し、これにより横スメアと呼ばれる画質劣化を生じる。

#### [0006]

本発明の目的は、横スメアを抑制し、画質を向上した液晶表示装置を提供することである

#### [0007]

#### 【課題を解決するための手段】

[0008]

本発明は、液晶パネル内のスイッチング素子のゲートをオフするためのゲートオフ電圧を高インピーダンス化する。これにより、液晶パネル内部のドレイン電圧の収束性を改善することができ、横スメアを抑制し、画質を向上することができる。

#### [0009]

#### 【発明の実施の形態】

本発明の第1の実施例を、図1~4を用いて、説明する。尚、本発明は、コモン反転駆動方式に好適であるが、ドット反転駆動方式にも適用できる。尚、以下の実施例における液晶表示装置の表示特性として、画素部の液晶に印加する電圧実効値が小さい場合に黒表示となり、電圧実効値が大きい場合に白表示となるノーマリブラック液晶で説明を進めることにする。

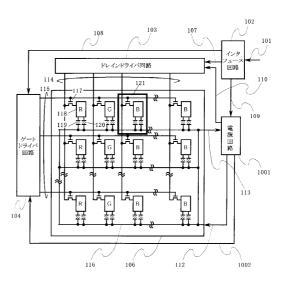

### [0010]

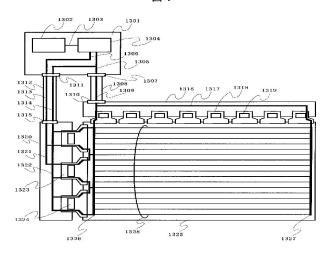

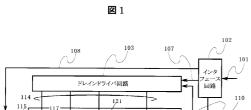

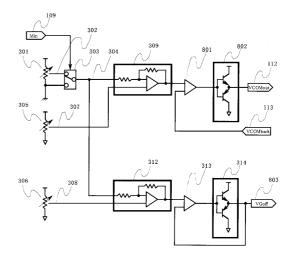

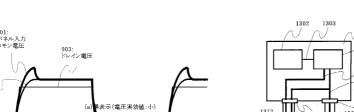

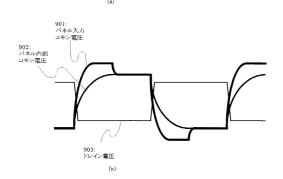

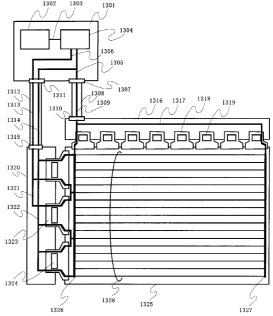

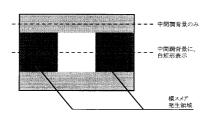

図1は、本発明の液晶表示装置のブロック図である。図2は、本発明の電源回路のうちコモン電圧とゲートオフ電圧を生成する回路図である。図3は、本発明のコモン電圧とゲートオフ電圧の電圧波形図である。図4は、本発明の液晶パネル内部のコモン電圧をフィードバックする箇所を更に詳細に説明するための図である。図5は、横スメアと呼ばれる画質劣化を説明するため図である。

## [0011]

図1の本液晶表示装置のブロック図において、101は外部装置から入力する表示データ と同期信号を転送するデータバスであり、102は液晶表示装置の駆動回路を制御するイ ンタフェース回路であり、103は表示データに対応した階調電圧(ドレイン電圧とも呼 ぶ。)を生成するドレインドライバ回路であり、104は表示するラインを順次選択する ゲートドライバ回路であり、105は液晶表示装置を駆動する各種電源電圧を生成する電 源回路であり、106は複数の画素部から構成される液晶パネルであり、107はインタ フェース回路102からドレインドライバ回路103に表示データと同期信号を転送する データバスであり、108はゲートドライバ回路104に同期信号を転送する信号線バス であり、109は電源回路105に交流化信号を転送する信号線であり、110は電源回 路105からドレインドライバ回路103に供給する基準階調電圧を伝送する電源バスで あり、111はゲートドライバ回路104を駆動する電源電圧を伝送する電源バスであり 、112は液晶パネル106に供給するコモン電圧を伝送するコモン電圧線であり、11 3は液晶パネル106内部のコモン電圧を電源回路105にフィードバックするコモン電 圧線であり、114はドレインドライバ回路103が出力するドレイン電圧を転送するド レイン線群であり、115はゲートドライバ回路104が出力する走査電圧(ゲート電圧 とも呼ぶ。)を伝送するゲート線群であり、116は液晶パネル106内部のコモン電極 であり、117はスイッチング動作を行なうTFTであり、118は画素電極であり、1 19は液晶であり、120は補償容量であり、121は画素部である。

#### [0012]

そして、コモン電極116は、液晶パネル106内部の全ての画素部で共通になっている。ドレイン線群114は、カラー表示の場合、水平解像度×3(赤(Red:R)、緑(Green:G)、青(Blue:B))の数だけ信号線数を有する。ゲート線群115

20

30

40

50

は、垂直解像度の数だけ信号線数を有する。コモン電極116は、電源回路105で生成するコモン電圧を、コモン電圧線112を介して液晶パネル106内部に伝送する。画素毎にR、G、Bのカラーフィルタを設けたカラー液晶パネルとしている。液晶119は、容量で等価モデルとしている。画素部121は、ドレイン線群114とゲート線群115とが交差する個所に位置し、TFT117、画素電極118、液晶119、補償容量120を有する。

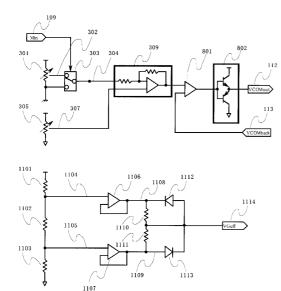

#### [0013]

図 2 の本発明のコモン電圧とゲートオフ電圧を生成する回路において、3 0 1 はコモン電 圧の振幅レベルを調整する可変抵抗であり、302は可変抵抗301で生成した直流電圧 の基準コモン電圧を伝送する電源線であり、303は電圧線302で伝送する基準コモン 電圧とグランドレベルの電圧を交流化信号109に応じて選択する電圧セレクタであり、 3 0 4 は電圧セレクタ 3 0 2 で生成された交流したコモン電圧の基準電圧であり、 3 0 5 はコモン電圧の電位レベルを調整する可変抵抗であり、306はゲートオフ電圧の電位レ ベルを調整する可変抵抗であり、307、308は各々前記可変抵抗305、306で生 成した調整電圧を伝送する電圧線であり、309は電圧線304と307で伝送される基 準コモン電圧と調整電圧を入力し、コモン電圧の電位レベルを調整する演算回路であり、 801は増幅回路(例えば、オペアンプ)であり、802は電流増幅回路(例えば、トラ ンジスタ)であり、312は電圧線304と308で伝送される基準コモン電圧と調整電 圧を入力しゲートオフ電圧の電位レベルを調整する演算回路であり、313は増幅回路で あり、314は電流増幅回路であり。803は電流増幅回路314の生成するゲートオフ 電圧を伝送する電圧線である。ゲートオフ電圧とは、スイッチング素子であるTFTのゲー トをオフするための電圧である。ゲートオフ電圧の印加により、TFTへの通電が停止され る。ゲートオン電圧は、スイッチング素子であるTFTのゲートをオンするための電圧であ る。ゲートオン電圧の印加により、TFTへの通電が開始される。

## [0014]

増幅回路801のフィードバック電圧は、液晶パネル106内部のコモン電圧をフィードバックするコモン電圧線113で伝送されるコモン電圧を適用する(フィードバック方式)。このフィードバック方式に、増幅回路801のフィードバック電圧として電流増幅回路802の出力であるコモン電圧を使用するブースト回路方式とを組み合わせても良い。増幅回路312のフィードバック電圧は、電流増幅回路314の出力である電圧線803で伝送するゲートオフ電圧を使用する(ブースト回路方式)。また、ゲートオフ電圧を伝送する電圧線803は、図1記載の電圧線111に含まれるものとする。

#### [0015]

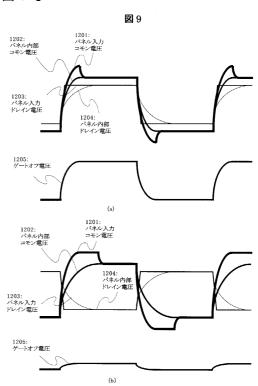

図3において、図3(A)は、黒表示(電圧実効値:小)を行なう際の電圧波形ある。901はコモン電圧線112で伝送するパネル入力コモン電圧であり、902は液晶パネル106内部のコモン電極線116のパネル内部コモン電圧であり、903はドレインドライバ回路103で生成し、ドレイン線群114で転送されるドレイン電圧である。図3(b)は、白表示(電圧実効値:大)を行なう際の電圧波形であり、図3(a)と同様箇所の電圧波形を示している。

#### [0016]

以下、本発明の液晶表示装置の詳細な動作を説明する。

## [0017]

本発明の液晶表示装置では、外部装置からデータバス101を介して表示データと同期信号を入力し、インタフェース回路102は、データバス107を介してドレインドライバ回路103に、信号バス108を介してゲートドライバ回路104に表示データと、制御信号を供給する。

#### [0018]

ドレインドライバ回路 1 0 3 では、入力される表示データに応じたドレイン電圧を生成し、ドレイン線群 1 1 4 に出力する。ゲートドライバ回路 1 0 4 では、ドレインドライバ回路 1 0 3 の出力するドレイン電圧を印加するラインを選択する為に、選択電圧となるゲー

20

30

40

50

トオン電圧をゲート線群115の対応するゲート線に印加する。ゲート線にゲートオン電圧が印加されたライン上の画素121では、対応するTFT117がオン状態になり、ドレイン線群114を介して転送されるドレイン電圧が画素電極118、液晶119、補償容量120に印加される。そして、この電圧印加動作が終了するとゲート線に非選択電圧となるゲートオフ電圧が印加され、TFT117がオフ状態になり、先の画素電極118、液晶119、補償容量120に印加されたドレイン電圧が保持される。これを全ライン繰り返すことで、表示データに対応した階調電圧が全画素に印加されることになる。

## [0019]

本実施例では、液晶に交流電圧を印加することで、焼き付き等の劣化を防止していると共に、画素毎に正極性の階調電圧と、負極性の階調電圧を交互に印加することで、フリッカと呼ばれるちらつきを防止する駆動方式を適用する。つまり、交流化信号109に応じて、コモン電圧を、1ライン毎に交流化し、コモン電圧が低電位レベルの場合、ドレイン電圧は、コモン電圧よりも高電位レベルにすることで、正極性のドレイン電圧を各画素121に印加する。また、コモン電圧が高電位レベルの場合、ドレイン電圧は、コモン電圧よりも低電位レベルにすることで、負極性の階調電圧を各画素121に印加する。これにより、ライン毎に正極性の階調電圧と、負極性の階調電圧を交互に印加することが可能になり、フリッカを防止することが可能になる。また、次フレームでは、各画素121に先に印加した極性の階調電圧と異なる極性の階調電圧を印加することで、焼き付き等の劣化を防止することが出来る。

## [0020]

尚、本発明の液晶表示装置において、特徴となるコモン電圧生成において、液晶パネル106に入力するコモン電圧を、液晶パネル106内部のコモン電圧をフィードバックして生成している。この動作に関して、図2、図3を用いて説明する。

#### [0021]

図2において、コモン電圧は、一定の振幅で、交流化信号109に応じて交流化する必要があることから、可変抵抗301と、電圧セレクタ302で、上記交流した基準コモン電圧を生成し、電源線304で伝送する。演算回路309では、この基準コモン電圧と、可変抵抗305で生成された調整電圧を入力して、コモン電圧の電位レベルを調整する。これにより、正極性のドレイン電圧と、負極性のドレイン電圧を液晶119に印加する際の実効電圧値を等しくすることが可能になる。

### [0022]

そして、増幅回路 3 1 0 と、電流増幅回路 3 1 1 で駆動能力を向上させたコモン電圧はコモン電圧線 2 0 3 を介して、液晶パネル 2 0 2 に伝送される。ここで、増幅回路 8 0 1 と電流増幅回路 3 1 1 は、液晶パネル 1 0 6 内部のコモン電圧をコモン電圧線 1 1 3 を介してフィードバックする増幅回路構成を取っている。従って、増幅回路 8 0 1 、電流増幅回路 8 0 2 で生成するコモン電圧は、演算回路 3 0 9 の生成するコモン電圧と、コモン電圧線 1 1 3 を介してフィードバックされたコモン電圧の電位差が比較された結果の電圧値が出力される。増幅回路 8 0 1 と電流増幅回路 8 0 2 の生成するコモン電圧に対して、液晶パネル 1 0 6 内部からフィードバックされるコモン電圧は、液晶パネル 1 0 6 内部の負荷容量、抵抗等の影響で、ある時定数を持った鈍った電圧波形になる。そこで、増幅回路 8 0 1 と電流増幅回路 8 0 2 とでは、液晶パネル 1 0 6 内部からフィードバックされるコモン電圧を、演算回路 3 0 9 の生成するコモン電圧レベルに遷移させようと動作する。

## [0023]

その結果、図3に記載する様に、液晶パネル106に入力する、つまり、コモン電圧線112を介して出力されるパネル入力コモン電圧901は、交流化のタイミングで、コモン電圧が負極性から正極性に遷移する際には正極性側に、コモン電圧が正極性から負極性に遷移する際には負極性側に、オーバーシュートした電圧波形となる。このオーバーシュートしたパネル入力コモン電圧901の効果で、パネル内部コモン電圧902は、より高電位(もしくは低電位)に遷移するので、結果的にパネル内部コモン電圧902の充電速度は向上することになる。そして、パネル内部コモン電圧902が所望するコモン電圧レベ

20

30

40

50

ルに遷移すると、パネル入力コモン電圧 9 0 1 も所望するコモン電圧レベルに遷移するので、前記演算回路 3 0 9 の生成するコモン電圧レベルと同一レベルで安定することになる

## [0024]

図3 (a) は、黒表示状態であり、液晶に電圧する電圧実効値が小さい状態であるから、パネル入力コモン電圧901とドレイン電圧903は、同位相で交流化されることになる。従って、パネル内部コモン電圧902は、液晶パネル106内部の容量や抵抗による負荷の影響を殆ど受けないことから、パネル入力コモン電圧901の電位レベルまで、高速に収束することになり、パネル入力コモン電圧901のオーバーシュート量もそれ程多くないことが判る。

## [0025]

これに対して、図3(b)は、白表示状態であり、液晶に電圧する電圧実効値が大きい状態であるから、パネル入力コモン電圧901とドレイン電圧903が逆位相で交流化されることになる。従って、パネル内部コモン電圧902は、液晶パネル106内部の容量や抵抗による負荷の影響を受けるとともに、ドレイン電圧903が、画素電極118、液晶119、付加容量120に充電される影響から、その収束性が悪化する。

#### [0026]

この電圧実効値の低下による表示輝度の変化が画質劣化として顕著に見える現象が図5に記載する様に、中間調背景に白矩形を表示した場合である。この表示状態の場合、中間輝度の背景のみの領域(ライン)と、白表示の矩形が表示されている領域(ライン)とでは、白矩形を表示するドレイン線群のドレイン電圧の振幅値が大きく異なってくる。従って、各々表示領域において、パネル内部コモン電圧の最終到達電位が変化してくる。その結果、中間輝度の背景のみの領域(ライン)と、白表示の矩形が表示されている領域の左右の背景領域では、ドレインドライバ回路から出力される中間調のドレイン電圧レベルは同ーレベルであるが、画素部の液晶に印加される電圧実効値が異なるので輝度が異なる表示が得られることになる。これが、横スメアと呼ばれる画質劣化である。

## [0027]

しかし、パネル入力コモン電圧は、パネル内部コモン電圧 9 0 2 が増幅回路 8 0 1 と電流 増幅回路 8 0 2 にフィードバックされているため、パネル内部コモン電圧 9 0 2 が演算回 路 3 0 9 の生成するコモン電圧レベルに到達するまで、オーバーシュート状態を保持し、 パネル内部コモン電圧 9 0 2 の収束性を改善することが可能になる。

# [0028]

図4を用いて、本発明の液晶パネル内部のコモン電圧をフィードバックする箇所を更に詳細に説明する。

#### [0029]

図4において、1301はインタフェース基板であり、1302はインタフェース回路であり(図1記載の102に相当)、1303は交流化信号であり(図1記載の109に相当)、1305はコモン電圧線であり(図1記載の112に相当)、1305はコモン電圧線であり(図1記載の112に相当)、1306はコモン電圧線であり(図1記載の113に相当)、1307はコネクタであり、1308はケーブルであり、1309はケーブル1308で転送する信号線の内コモン電圧線であり、1313はケーブル1312で転送する信号線の内コモン電圧線であり、1313はケーブル1312で転送する信号線の内コモン電圧線であり、1313はケーブル1312で転送する信号線の内コモン電圧線であり、1313はケーブル1315はコネクタであり、1316はドレインドライバLSIを実装するドレイン基板であり、1315はコネクタであり、1316はドレインドライバLSIを実装するドレインを通圧線であり、1315はコネクタであり、1316はドレインドライバLSIを実装するパッケージであり、1319はドレインドライバLSIを実装するパッケージであり、1310はゲートドライバLSIの本体であり、1325は液晶パネルであり、1326は液晶パネルであり、1325は液晶パネルであり、1326は液晶パネルであり、1325は次元であり、1325は液晶パネルであり、1326は液晶パネルであり、1325は次元であり、1325は液晶パネルであり、1325は次元であり、1325は液晶パネルであり、1325は次元であり、1325は液晶パネルであり、1325は次元であり、1325は液晶パネルであり、1325は次元であり、1325は液晶パネルであり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元であり、1325は次元でありに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに対しまれりに

27は液晶パネル1325上のコモンバスラインであり、1328は液晶パネル上のライン毎に横方向に配線されたコモン電圧線である。

#### [0030]

そして、コモン電圧線 1 3 0 9 は、コネクタ 1 3 0 7 を介してコモン電圧線 1 3 0 5 と接続される。コモン電圧線 1 3 1 7 は、コネクタ 1 3 1 0 を介してコモン電圧線 1 3 0 6 と接続される。コモン電圧線 1 3 1 7 は、コネクタ 1 3 1 0 を介してコモン電圧線 1 3 0 9 と接続される。コモン電圧線 1 3 2 1 は、コネクタ 1 3 1 5 を介してコモン電圧線 1 3 1 3 と接続される。本第 1 の実施例では、水平解像度 1 0 2 4 ドットのカラー液晶を想定し、ドレインドライバLSIの出力端子数が 3 8 4 本を想定しているので、ドレインドライバLSIは合計 8 個搭載されている(1 0 2 4 \* 3 ÷ 3 8 4 )。また、本第 1 の実施例の 垂直ライン数は 7 6 8 本、ゲートドライバLSIの出力端子数が 2 5 6 本を想定しているので、ゲートドライバLSIは合計 3 個搭載されている(7 6 8 \* 2 5 6)。

#### [0031]

本第1の実施例では、インタフェース基板1301上の電源回路1304で生成するコモン電圧を液晶パネルに供給する経路として、ケーブル1308、ケーブル1312を用いて、各々ドレイン基板1316、ゲート基板1320に転送する。この各基板上に転送されるコモン電圧は各々コモン電圧線1317、1322を介して液晶パネル1325上のコモンバスライン1327、1326に転送されることになる。この各基板から液晶パネルへのコモン電圧線の接続点はドレイン基板において、ドレイン基板1316では、最も左側のドレインドライバLSI1319のパッケージ1318を経由したものになる。最も右側のドレインドライバLSI1319のパッケージ1318を経由したものになる。また、ゲート基板1320では、各々のゲートドライバLSI1324のパッケージ1323を経由したものになる。尚、このゲート基板1320のコモン電圧線供給点において、上部と中央部に位置するゲートドライバLSI1324のパッケージ1323下を経由したものになる。一下でライバLSI1324のパッケージ1323を経由したものになる。一下でライバLSI1324のパッケージ1323を経由したものになる。一下でライバLSI1324のパッケージ1323を経由したコモン電圧線は、上記液晶パネルに供給されるコモン電圧をインタフェース基板1301上の電源回路1304にフィードバックする為の経路として利用する。

## [0032]

これにより、液晶パネル 1 3 2 5 内部のコモン電圧をコモン電圧生成回路(本実施例では図示せず)にフィードバックすることが可能となり、コモン電圧を液晶パネルに供給することが可能になる。

### [0033]

以上により、本発明の第1の実施例によれば、1ラインの書き込み動作が終了する時点で、パネル内部コモン電圧902は所望するコモン電圧レベルに収束するので、従来の技術で生じる様な液晶に印加される実効電圧値が低下するような現象が発生せず、高画質表示が可能になる。尚、パネル入力コモン電圧401のオーバーシュート電圧の高電位レベルと、低電位レベルは、前記増幅回路801と電流増幅回路802の電源電圧によって制約されるものである。従って、この電源電圧レベルを変更することで、パネル入力コモン電圧401のオーバーシュート電圧を印加している期間を変更することが可能になる。

## [0034]

また、本第1の実施例によれば、液晶パネル106内部の容量や抵抗による負荷の影響で、オーバーシュート電圧量が自動的に変化するので、液晶パネル106のバラツキ、表示内容による負荷変動等を吸収出来る効果があり、より高画質表示が可能になる。

## [0035]

また、ゲートオフ電圧の生成回路において、演算回路312では、電圧線304で伝送される基準コモン電圧と、可変抵抗306で生成された調整電圧を入力して、ゲートオフ電圧の電位レベルを調整し、増幅回路313と電流増幅回路314で、駆動能力を向上させたゲートオフ電圧を生成し、電圧線803を介してゲートドライバ回路104に伝送する。その結果、コモン電極116とゲート線群115の間に形成される容量の充放電電流を緩和することが可能になる。

# [0036]

10

20

30

30

50

次に、本発明の第2の実施例を、図6~9を用いて説明する。

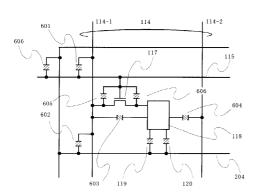

## [0037]

図6は、本発明の画素部の等価回路の詳細説明図である。図7は、本発明の液晶表示装置のブロック図である。図8は、本発明の電源回路のうちコモン電圧とゲートオフ電圧を生成する回路図である。図9は、本発明のコモン電圧とゲートオフ電圧の電圧波形図である

## [0038]

## [0039]

図 7 において、 1 0 0 1 は電源回路であり、 1 0 0 2 は電源回路 1 0 0 1 から、ゲートドライバ回路 1 0 4 を駆動する電源電圧を伝送する電源バスである。

#### [0040]

図8において、1101、1102、1103は分割抵抗であり、1104と、1105の電源線に基準となるゲートオフ電圧を出力する。1106と1107は、電源線1104と1105で伝送されるゲートオフ電圧の電流増幅回路であり、各々1108と1109の電源線にゲートオフ電圧を出力する。1110と1111は分割抵抗であり、1112と1113はダイオードである。

## [0041]

図9において、図9(a)は黒表示(電圧実効値:小)を行なう際の電圧波形であり、1201はコモン電圧線112で伝送するパネル入力コモン電圧であり、1202は液晶パネル106内部のコモン電極線116上のパネル内部コモン電圧であり、1203はドレインドライバ回路103の出力するドレイン電圧のうち、ドレインドライバ回路103近端のパネル入力ドレイン電圧であり、1204は液晶パネル106内部のパネル内部ドレイン電圧であり、1204は液晶パネル106内部のパネル内部ドレイン電圧であり、1205はゲートオフ電圧である。また、図9(b)は白表示(電圧実効値:大)を行なう際の電圧波形であり、図9(b)と同様箇所の電圧波形を示している

## [0042]

液晶表示装置の画素部121は各電極間の各処に、図6に記載する様な交差容量や、寄生容量が形成されている。ここで、ドレイン線群114とゲート線群115の交差部に形成される交差容量(Cgd1)601と、TFT117におけるドレイン線114-1とゲート線115-1がオーバーラップする際に形成される寄生容量(Cdg2)605が画質劣化を発生する要因になる。つまり、ゲートオフ電圧がコモン電圧と同位相で交流化すると、ドレイン電圧の電圧波形状態、つまり、表示内容によっては、前記交差容量601並びに寄生容量605に電流の流入出が発生することになる。

## [0043]

図 7 の液晶表示装置は、本発明の第 1 の実施例とほぼ同一であり、本発明の第 1 の実施例と異なる点は、電源回路 1 0 0 1 と、電源回路 1 0 0 1 が生成するゲートドライバ回路 1 0 4 に供給する電源電圧である。そこで、図 8 を用いて第 1 の実施例との違いを説明する

## [0044]

図7記載の、分割抵抗1101、1102、1103は、ゲートオフ電圧の高電位レベル

電圧と、低電位レベル電圧を生成し、その各々のゲートオフレベル電圧は、各々1106と1107の電流増幅回路で電流増幅される。この電流増幅された2種類のゲートオフ電圧を分圧抵抗1110と1111で分圧することで、液晶パネル106に供給するゲートオフ電圧を生成し、電源線1114を介して伝送する。尚、電源線1114は図10記載の電源線1002に含まれるものとする。ここで、電源線1114で伝送されるゲートオフ電圧は高インピーダンス状態にする為、分割抵抗1110、1111は高抵抗にする。また、ゲートオフ電圧が、電流増幅回路1106、1107で生成されるゲートオフ電圧の電位レベルよりも高電位又は、低電位に遷移しないようにダイオード1112と1113を設けておく。これにより、液晶パネル106内部でゲートオフ電圧が振られた時に、前記基準電圧レベルよりも大きな振幅にならにように制御することが可能になる。

[0045]

次に、その動作に関して説明する。

#### [0046]

図8において、各コモン電圧1201、1202の電圧波形は、本発明の第1の実施例と同様である。つまり、パネル入力コモン電圧1201は、液晶パネル内部の負荷状態や、表示内容に依存して、パネル内部コモン電圧1202の電圧が歪むことから、交流化タイミングでオーバーシュート電圧となる。この結果、液晶パネル106内部のコモン電圧の収束性は改善される。

# [0047]

更に、本発明の特徴であるゲートオフ電圧について説明する。先に記載した様に液晶パネル106に供給するゲートオフ電圧は高インピーダンス状態の駆動電圧になっている。従って、ゲートオフ電圧は、一方で、図6で記載したドレイン線114-1とゲート線115の交差容量601や、TFT117の寄生容量605の影響で、ドレイン電圧に追従する様に動作する。また、ゲートオフ電圧は、もう一方で、図6に記載したゲート線115とコモン電極204(図7記載のコモン電極116に相当)の交差容量607の影響でコモン電圧に追従することになる。

## [0048]

その結果、図9(a)に記載する様にドレイン電圧がコモン電圧と同位相になる場合、ゲートオフ電圧も、前記寄生容量、交差容量の影響でコモン電圧やドレイン電圧と同位相の振幅になる。また、図9(b)に記載する様にドレイン電圧がコモン電圧と逆位相になる場合、ゲートオフ電圧は、ドレイン電圧とコモン電圧の中間電位状態になる。

## [0049]

つまり、ゲートオフ電圧は高インピーダンス状態の駆動電圧にすると、ドレイン線 1 1 4 - 1 とゲート線 1 1 5 の負荷容量、すなわち交差容量 6 0 1 が結果的に小さくなるので、ドレイン電圧の収束性が改善され、従来例で記載した様な液晶に印加される実効電圧値が低下するような現象が発生せず、高画質表示が可能になる。

#### [0050]

また、本発明の実施例によれば、ゲートオフ電圧を高インピーダンス状態にすることで、 ドレイン線とゲート線の交差容量への充放電電流を削減することが可能になるので、消費 電力を低減する効果もある。

# [0051]

更にまた、本発明の実施例によれば、特にドレインドライバ回路近端のドレイン電圧と、 ドレインドライバ回路遠端のドレイン電圧との位相差を小さくすることが出来るので、液 晶パネルの縦方向に発生する縦輝度傾斜を抑制する効果もある。

#### [0052]

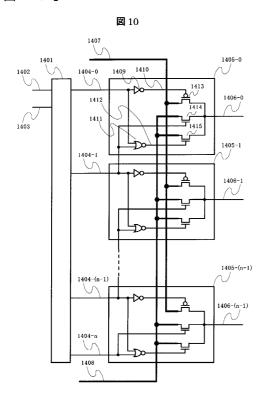

次に、本発明の第3の実施例を、図10,11を用いて説明する。

#### [0053]

第3の実施例は、本発明のゲートオフ電圧の高インピーダンス駆動を、ゲートドライバ L SIで実現する為の実施例である。図10は、本発明のゲートドライバのブロック図であ る。図11は、本発明のゲートドライバの動作を説明するためのタイミングチャート図で 10

20

30

40

(13)

ある。

[0054]

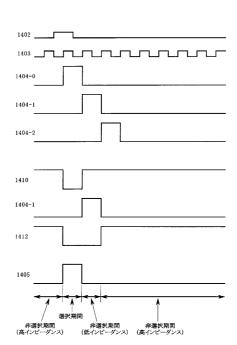

図 1 0 において、 1 4 0 1 はシフトレジスタであり、 1 4 0 2 はスタート信号であり、 1 4 0 3 はシフトクロックであり、 1 4 0 4 はシフトレジスタ 1 4 0 1 の出力信号である。 1 4 0 5 はゲート電圧選択回路であり、 1 4 0 6 は本ゲートドライバLSIの出力信号である。 1 4 0 7 はゲートオン電圧を供給する電源線であり、 1 4 0 8 はゲートオフ電圧を供給する電源線であり、 1 4 1 0 は反転回路 1 4 0 9 の出力信号であり、 1 4 1 1 はNOR回路であり、 1 4 1 2 はNOR回路 1 4 1 1 の出力信号であり、 1 4 1 3 はゲートオン電圧用のP - MOSであり、 1 4 1 4 はゲートオフ電圧用のN - MOSであり、 1 4 1 5 はゲートオフ電圧用のN - MOSである。

[0055]

図 1 1 は、図 1 0 記載のゲートドライバLSIの動作を説明するタイミングチャート図であり、各々の記号に対応した箇所の動作を示している。

[0056]

そして、N-MOS1414は、低インピーダンス化するため、MOSのゲート幅を大きい。N-MOS1415は、高インピーダンス化するために、MOSのゲート幅を小さい

[0057]

次に、図10、11を用いて、その動作を説明する。

[0058]

シフトレジスタ1401は、スタート信号1402と、シフトクロック1403に応じて出力信号1404を図15記載の様に順次出力する。ゲート選択回路1405のP-MOS1413では、反転回路1409の出力信号1410を受けて動作する。図15に記載する用に出力信号1410が「ロウ」レベルの時にゲートオン電圧を出力信号1405に反映する。ゲート選択回路1405のN-MOS1414では、シフトレジスタ1401の出力1404-1の様に次ラインの動作信号を受けて動作する。図11に記載する用に出力信号1404-1が「ハイ」レベルの時にゲートオフ電圧を出力信号1405に反映する。この時、このゲートオフ電圧は低インピーダンスになる。これは、液晶パネルのゲート線に印加している電圧をオン電圧からオフ電圧に高速に遷移させる必要があるからである。ゲート選択回路1405のN-MOS1415では、NOR回路1411の出力信号1412を受けて動作する。図11に記載する用に出力信号1412が「ハイ」レベルの時にゲートオフ電圧を出力信号1405に反映する。この時、このゲートオフ電圧は高インピーダンスになる。

[0059]

以上の様にゲートドライバLSIを構成することでも、ゲートオフ電圧の高インピーダンス化が可能になる。

[0060]

よって、本第3の実施例においても、上記第3の実施例と同様の効果を奏する。

[0061]

以上のように、本発明の第1の実施例によれば、電源回路のうち、コモン電圧生成回路に、液晶パネル内部のコモン電圧をフィードバックすることから、液晶パネルに出力するコモン電圧は、交流化のタイミングで、コモン電圧が負極性から正極性に遷移する際には正極性側に、コモン電圧が正極性から負極性に遷移する際には負極性側に、オーバーシュートした電圧波形となる。この結果、液晶パネル内部のコモン電圧は、より高電位(もしくは低電位)に遷移するので、収束性を改善できる効果があり、横スメアと呼ばれる画質劣化を防止でき、高画質表示が実現出来る効果がある。

[0062]

更に、本発明の第1の実施例によれば、コモン電圧生成回路に、液晶パネル内部のコモン電圧をフィードバックすることから、液晶パネルの負荷定数のバラツキや、表示内容によるコモン電圧歪みに応じた、コモン電圧を液晶パネルに供給することが可能になり、液晶

10

20

30

40

パネル内部コモン電圧の収束性改善と、高画質表示が実現出来る効果がある。

## [0063]

また、本発明の第2の実施例及び第3の実施例によれば、ゲートオフ電圧を高インピーダンス状態にすることで、ドレイン線とゲート線の交差容量への充放電電流を削減することが可能になるので、液晶パネル内部のドレイン電圧の収束性を改善する効果があり、横スメアと呼ばれる画質劣化を防止でき、高画質表示が実現出来る効果がある。

#### [0064]

更に、本発明の第2の実施例及び第3の実施例によれば、ゲートオフ電圧を高インピーダンス状態にすることで、ドレイン線とゲート線の交差容量への充放電電流を削減することが可能になるので、消費電力を低減する効果もある。

## [0065]

更にまた、本発明の第2の実施例及び第3の実施例によれば、特にドレインドライバ回路 近端のドレイン電圧と、ドレインドライバ回路遠端のドレイン電圧との位相差を小さくす ることが出来るので、液晶パネルの縦方向に発生する縦輝度傾斜を抑制する効果もある。

### [0066]

## 【発明の効果】

#### [0067]

本発明によれば、液晶パネル内部のドレイン電圧の収束性を改善することができ、表示画像に生じる横スメアを抑制し、画質を向上するという効果を奏する。

## 【図面の簡単な説明】

- 【図1】本発明の液晶表示装置のブロック図。

- 【図2】本発明の電源回路のうちコモン電圧とゲートオフ電圧を生成する回路図。

- 【図3】本発明のコモン電圧とゲートオフ電圧の電圧波形図。

- 【図4】本発明の液晶パネル内部のコモン電圧をフィードバックする箇所を更に詳細に説明するための図。

- 【図5】横スメアと呼ぶ画質劣化を説明するための図。

- 【図6】本発明の画素部の等価回路の詳細説明図。

- 【図7】本発明の液晶表示装置のブロック図。

- 【図8】本発明の電源回路のうちコモン電圧とゲートオフ電圧を生成する回路図。

- 【図9】本発明のコモン電圧とゲートオフ電圧の電圧波形図。

- 【図10】本発明のゲートドライバのブロック図。

- 【図11】本発明のゲートドライバの動作を説明するためのタイミングチャート図。

#### 【符号の説明】

1 0 1 ... データバス、1 0 2 ... インタフェース回路、1 0 3 ... ドレインドライバ回路、1 0 4 ... ゲートドライバ回路、1 0 5 ... 電源回路、1 0 6 ... 液晶パネル、1 0 7 ... データバス、1 0 8 ... 信号線バス、1 0 9 ... 信号線、1 1 0 ... 電源バス、1 1 1 ... 電源バス、1 1 2 ... コモン電圧線、1 1 3 ... コモン電圧線、1 1 4 ... ドレイン線群、1 1 5 ... ゲート線群、1 1 6 ... コモン電極、1 1 7 ... TFT、1 1 8 ... 画素電極、1 1 9 ... 液晶、1 2 0 ... 補償容量、1 2 1 ... 画素部。

10

20

【図1】

【図2】

ゲート ドライン 回路 113 106

【図3】

【図4】

**2** 3

図 4

# 【図5】

図 5

# 【図6】

図 6

# 【図7】

図 7

# 【図8】

図8

# 【図9】

# 【図10】

# 【図11】

## フロントページの続き

(51) Int.CI. FΙ

G 0 9 G 3/36

(72)発明者 川辺 和佳

神奈川県川崎市麻生区王禅寺1099番地 株式会社日立製作所 システム開発研究所内

(72)発明者 北島 雅明

千葉県茂原市早野3300番地 株式会社日立製作所 ディスプレイグループ内

(72)発明者 鈴木 雅彦

千葉県茂原市早野3300番地 株式会社日立製作所 ディスプレイグループ内

## 審査官 藤田 都志行

(56)参考文献 実開平07-033075(JP,U)

特開2000-028992(JP,A)

特開平11-119741(JP,A)

特開平11-316366(JP,A)

特開平09-218388(JP,A)

特開平11-119743(JP,A)

特開平11-133927(JP,A)

特開平11-014968(JP,A)

特開平06-202070(JP,A)

特開平06-289817(JP,A)

特開平04-191821(JP,A)

特開平06-194622(JP,A)

特開2000-147459(JP,A)

特開平07-270754(JP,A)

特開平02-03008(JP,A)

特開2000-194306(JP,A)

特開平11-175038(JP,A)

特開平03-177890(JP,A)

特開平10-339863(JP,A)

特開2000-075263(JP,A)

特開平08-146381(JP,A)

## (58)調査した分野(Int.CI., DB名)

G02F 1/133 550

G02F 1/133 520

G09G 3/20 622B

G09G 3/20 623B

G09G 3/20 624C

G09G 3/36

| 专利名称(译)        | 液晶显示装置和液晶显示装置的驱动                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 协方法     |            |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号        | JP3858590B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2006-12-13 |  |  |  |

| 申请号            | JP2000369608                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2000-11-30 |  |  |  |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| 当前申请(专利权)人(译)  | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| [标]发明人         | 古橋勉<br>大石純久<br>川辺和佳<br>北島雅明<br>鈴木雅彦                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |

| 发明人            | 古橋 勉<br>大石 純久<br>川辺 和佳<br>北島 雅明<br>鈴木 雅彦                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |  |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |  |  |  |

| CPC分类号         | G09G3/3677 G09G3/3648 G09G3/3655 G09G3/3696 G09G2320/0233                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| FI分类号          | G02F1/133.550 G02F1/133.520 G09G3/20.622.B G09G3/20.623.B G09G3/20.624.C G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |

| F-TERM分类号      | 2H093/NA53 2H093/NC01 2H093/NC02 2H093/NC09 2H093/NC11 2H093/NC18 2H093/NC34 2H093 /ND09 2H093/ND10 2H093/ND12 2H193/ZA04 2H193/ZB02 2H193/ZB08 2H193/ZD23 2H193/ZD32 2H193/ZF01 2H193/ZF02 2H193/ZF59 2H193/ZH26 2H193/ZH53 5C006/AA01 5C006/AA02 5C006 /AA11 5C006/AC21 5C006/AC22 5C006/AC25 5C006/AC26 5C006/BB16 5C006/BC03 5C006/BC11 5C006/BF03 5C006/BF34 5C006/FA36 5C080/AA10 5C080/BB05 5C080/DD01 5C080/DD30 5C080 /FF11 5C080/GG08 5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK02 5C080/KK43 |         |            |  |  |  |

| 代理人(译)         | 井上 学                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |  |

| 其他公开文献         | JP2002169138A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

# 摘要(译)

要解决的问题:通过控制显示图像上产生的横向污迹来提高图像质量。解决方案:根据本发明的液晶显示器包括:液晶面板106,用于根据漏极电压和公共电压之间的电位差显示灰度;漏极驱动电路103,用于产生漏极电压,对应于显示数据并应用它用于液晶面板,用于选择要施加漏极电压的液晶面板中的扫描线的栅极驱动电路104,以及用于执行参考公共电压之间的比较操作的电源电路105,其电位为调节和从液晶面板反馈的反馈公共电压,并将作为比较操作的结果获得的公共电压施加到液晶面板。