(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-181049

(P2008-181049A)

(43) 公開日 平成20年8月7日(2008.8.7)

(51) Int.Cl.

**G09F 9/30 (2006.01)**

**G02F 1/1345 (2006.01)**

**G02F 1/13 (2006.01)**

**G09F 9/00 (2006.01)**

F 1

GO9F 9/30 338

GO2F 1/1345

GO2F 1/13 101

GO9F 9/00 352

テーマコード(参考)

2H088

2H092

5C094

5G435

審査請求 未請求 請求項の数 10 O L (全 14 頁)

(21) 出願番号

特願2007-16148 (P2007-16148)

(22) 出願日

平成19年1月26日 (2007.1.26)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100095669

弁理士 上野 登

(72) 発明者 永井 敦

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内F ターム(参考) 2H088 FA12 FA13 FA16 FA30 HA02

HA082H092 GA41 GA57 JA24 JB32 JB77

MA575C094 AA43 BA03 BA43 DA20 FA04

GB10

5G435 AA17 AA19 BB12 KK05 KK10

(54) 【発明の名称】 TFTアレイ基板、液晶表示パネルおよび液晶表示装置

## (57) 【要約】

【課題】 映像表示に影響を与えることなく、信号配線を迅速かつ正確に判別することができるようとする。

【解決手段】 TFTアレイ基板10上に形成された複数の信号配線12の下に形成された半導体膜40に、スリット92や、切り欠き部94による識別表示を設けることによって、信号配線12にその識別のためのナンバー等が付されていなくとも、プローピングによりチェックすべき所定の信号配線12を迅速かつ確実に識別可能とした。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

ガラス基板上に形成された半導体膜上に複数の信号配線が形成された TFT アレイ基板であって、前記半導体膜に前記信号配線に関する識別表示が付されていることを特徴とする TFT アレイ基板。

**【請求項 2】**

前記信号配線はその延在方向で分割されていることを特徴とする請求項 1 に記載の TFT アレイ基板。

**【請求項 3】**

前記識別表示は前記信号配線が分割された個所の略近傍に付されていることを特徴とする請求項 2 に記載の TFT アレイ基板。 10

**【請求項 4】**

前記識別表示は前記半導体膜に切り欠きが形成されることにより付されていることを特徴とする請求項 1 ~ 3 に記載の TFT アレイ基板。

**【請求項 5】**

前記識別表示は前記半導体膜にスリットが形成されることにより付されていることを特徴とする請求項 1 ~ 4 に記載の TFT アレイ基板。

**【請求項 6】**

請求項 1 ~ 5 いずれかに記載の TFT アレイ基板を備えてなることを特徴とする液晶表示パネル。 20

**【請求項 7】**

請求項 6 に記載の液晶表示パネルを備えてなることを特徴とする液晶表示装置。

**【請求項 8】**

ガラス基板上に複数の信号配線および絵素電極が形成された TFT アレイ基板であって、前記信号配線はその延在方向で分割されており、前記信号配線と前記絵素電極との寄生容量が変化しないように前記信号配線にその識別表示が付されていることを特徴とする TFT アレイ基板。

**【請求項 9】**

請求項 8 に記載の TFT アレイ基板を備えてなることを特徴とする液晶表示パネル。

**【請求項 10】**

請求項 9 に記載の液晶表示パネルを備えてなることを特徴とする液晶表示装置。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、TFT (薄膜トランジスタ) アレイ基板、液晶表示パネルおよび液晶表示装置に関し、更に詳しくは、TFT アレイ基板上に形成された信号配線の評価試験等の作業効率向上に寄与する TFT アレイ基板、液晶表示パネルおよび液晶表示装置に関するものである。

**【背景技術】****【0002】**

液晶表示装置に使用される液晶表示パネルは、一般的に、TFT アレイ基板と、カラーフィルタ基板の間に液晶が充填されて構成される。液晶表示装置の設計において、この TFT アレイ基板の設計 (アレイ設計) は、表示装置の性能を決定する重要な要素である。

**【0003】**

液晶表示装置の開発段階において、アレイ設計後、その設計に基づき試作された TFT アレイ基板上に形成された信号配線は、その抵抗値等を測定することにより、設計通りに動作可能か評価される。一般的に、信号配線の両端付近には、映像表示に影響のない個所に信号配線のラインナンバーが付されている。そのため、信号配線の技術的配線抵抗評価は、このラインナンバーや、TFT アレイ基板側縁に取り付けられている TAB (Tape Automated Bonding) の位置を目安として、何本かの信号配線の両端をプローピングするこ 50

と等によりなされる

【0004】

一方、近年、大画面かつ高画質の液晶表示装置に対する需要が増し、上記TFTアレイ基板には、高い技術的特性が求められている。

【0005】

例えば特許文献1には、TFTアレイ基板上に形成される信号配線をその延在方向に2分割し、それぞれの信号配線と接続された各ソースドライバICより、2方向からソース信号(映像データ)が供給されるようにした液晶表示装置が記載されている。この液晶表示装置によれば、1絵素あたりのソース信号を入力するための時間を長くすることができ、液晶表示装置の画質向上につながる。

10

【0006】

【特許文献1】特開2001-343946号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

このような信号配線が分割されたTFTアレイ基板の信号配線をプローピングにより評価する場合、信号配線が分割された部分にプローブを接触させる必要がある。ところが、信号配線が分割されている個所は、液晶表示パネルのほぼ中央の映像表示部に相当するため、信号配線の分割部分にラインナンバーを付すことはできない。

【0008】

したがって、分割された信号配線をプローピングにより評価する際には、例えば、TFTアレイ基板をスライドさせながら測定すべき信号配線をTFTアレイ基板の側縁から中央に向かって顕微鏡で追っていき、その信号配線の分割部分を見出すといった作業が必要であった。このように、ラインナンバー等の信号配線を識別する目安となるもの付すことができない場合、プローピングによるTFTアレイ基板の評価作業の効率が非常に悪いという問題があった。

20

【0009】

そこで、本発明が解決しようとする課題は、映像表示に影響を与えることなく、所定の信号配線を迅速かつ正確に判別することができるTFTアレイ基板、液晶表示パネルおよび液晶表示装置を提供することにある。

30

【課題を解決するための手段】

【0010】

上記課題を解決するために本発明に係るTFTアレイ基板は、ガラス基板上に形成された半導体膜上に複数の信号配線が形成されたTFTアレイ基板であって、前記半導体膜に前記信号配線に関する識別表示が付されていることを要旨とするものである。

【0011】

また、この場合、前記信号配線はその延在方向で分割されていれば好適であり、前記識別表示は前記信号配線が分割された個所の略近傍に付されていればさらによい。

【0012】

また、前記識別表示は前記半導体膜に切り欠きやスリットが形成されることにより付されていることが好ましい。

【0013】

そして、このようなTFTアレイ基板を備えてなることを特徴とする液晶表示パネルや液晶表示装置をも要旨とするものである。

【0014】

さらに、上記課題を解決するために他の本発明に係るTFTアレイ基板は、ガラス基板上に複数の信号配線および絵素電極が形成されたTFTアレイ基板であって、前記信号配線はその延在方向で分割されており、前記信号配線と前記絵素電極との寄生容量が変化しないように前記信号配線にその識別表示が付されていることを要旨とするものである。

40

【0015】

50

また、このようなTFTアレイ基板を備えてなる液晶表示パネルや液晶表示装置をも要旨とするものである。

【発明の効果】

【0016】

本発明に係るTFTアレイ基板によれば、ガラス基板上に形成された半導体膜に信号配線の位置等を示す識別表示が付されているため、プロービング等によりTFTアレイ基板上の信号配線を評価する場合において、チェックすべき信号配線の特定が容易になり、TFTアレイ基板の評価を迅速かつ正確に行うことができる。しかも、この識別表示は、信号配線の断線防止目的等で信号配線の下に形成された半導体膜に付されるため、TFTアレイ基板の性能、品質等に影響を与えることはない。

10

【0017】

また、上記TFTアレイ基板が、その信号配線がその延在方向で分割されているもの（ソース信号（映像データ）が2方向から供給されるもの）であって、さらに、その分割部分の略近傍の半導体膜に識別表示が付されておれば、信号配線の分割部分における所定の信号配線の特定が容易となり、プロービング等によるTFTアレイ基板の技術的評価を迅速に行うことができる。

【0018】

また、上記識別表示が半導体膜に切り欠きやスリットにより付されていれば、信号配線を確実かつ容易に判別することができる。

20

【0019】

そして、このようなTFTアレイ基板を備えた液晶表示パネルおよび液晶表示装置は、液晶表示パネルや液晶表示装置組立後に点灯不良等が発見され、信号配線を分析しなければならない場合等、液晶表示パネルや液晶表示装置組立後の不良解析に極めて有用である。

30

【0020】

さらに、他の本発明に係るTFTアレイ基板によれば、その延在方向で分割された信号配線自体に識別表示が付されているため、信号配線をプロービング等する際に、信号配線を特定する目安とすることができます。そして、この識別表示は、信号配線と絵素電極との寄生容量が変化しないように付されているため、TFTアレイ基板の性能、品質等に影響を与えることはない。

30

【0021】

そして、このようなTFTアレイ基板を備えた液晶表示パネルおよび液晶表示装置は、液晶表示パネルや液晶表示装置組立後に点灯不良等が発見され、信号配線を分析しなければならない場合等、液晶表示パネルや液晶表示装置組立後の不良解析に極めて有用である。

40

【発明を実施するための最良の形態】

【0022】

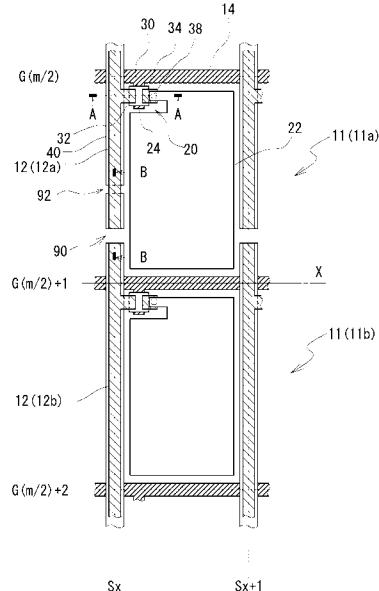

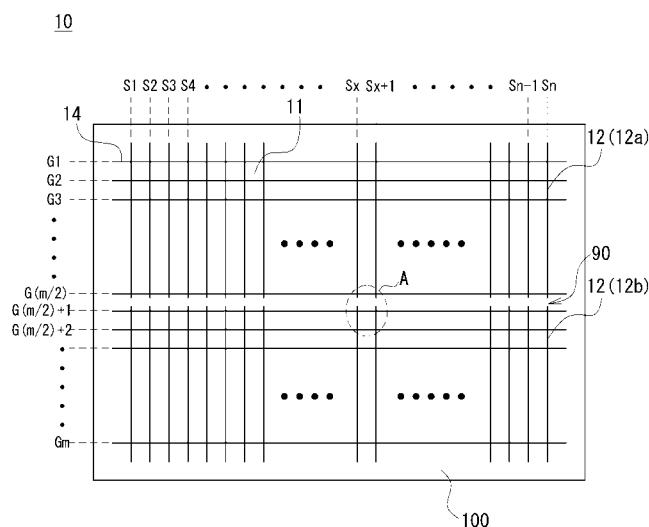

以下、本発明に係るTFTアレイ基板、液晶表示パネルおよび液晶表示装置の一実施形態を図面を用いて詳細に説明する。まず、本発明に係るTFTアレイ基板の第1実施形態を図1～9を用いて詳細に説明する。なお、以下の説明における上下左右方向とは、図1における上下左右方向をいうものとする。

【0023】

図1は、本発明の第1実施形態に係るTFTアレイ基板全体の概略構成図を示したものである。図1に示されるように、本実施形態に係るTFTアレイ基板10には、ガラス基板100上に複数の信号配線12（S1, S2, S3, …, Sn）および複数の走査配線14（G1, G2, G3, …, Gm）とがマトリクス状に設けられている。この信号配線12および走査配線14により区画された領域が絵素部11となる。

【0024】

ここで、図示されるように、信号配線12は、ガラス基板100の上下に縦断する方向に配設され、その延在方向の略中央で第1信号配線12aおよび第2信号配線12bに分

50

割（分割部 90）されている。このように信号配線 12 を分割した TFT アレイ基板 10 を備えた液晶表示装置では、ソース信号（映像データ）を TFT アレイ基板 10 の上下 2 方向から供給することとなる。

#### 【0025】

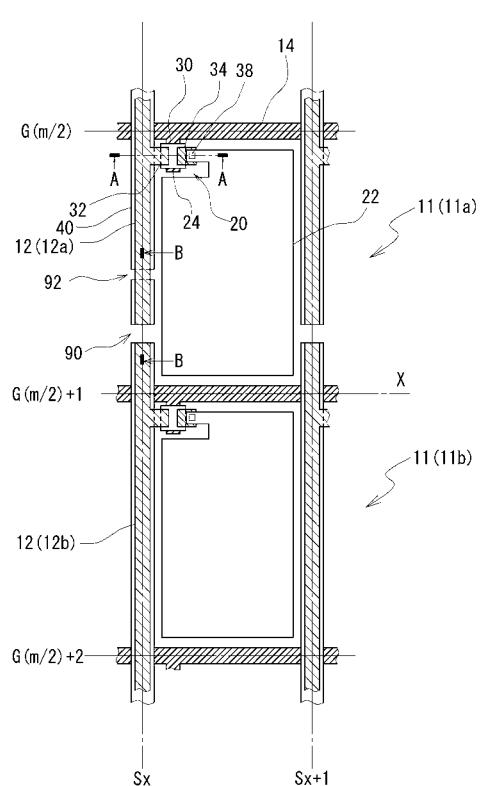

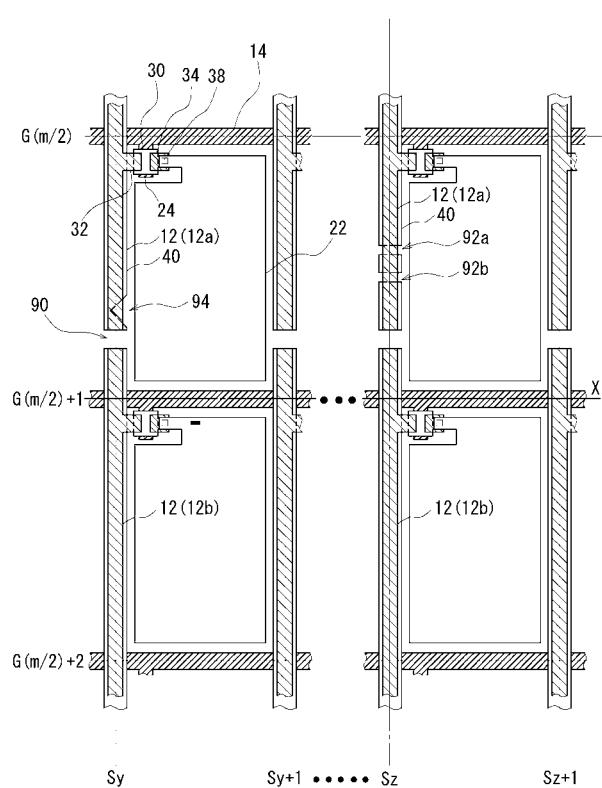

図 2 は、図 1 の信号配線 12 の分割部 90 付近（領域 A）における絵素部 11（11a, 11b）の拡大図である。なお、本図における X 軸が、TFT アレイ基板 10 を用いた場合の映像表示領域のセンターラインとなる。また、本図において、絵素部 11b の構成については、絵素部 11a と同様であるので番号を省略した。

#### 【0026】

図示される信号配線 12 と走査配線 14 は、その交差部において、信号配線 12 が上側、走査配線 14 が下側となるように交差しており、両者は電気的に絶縁されている。この信号配線 12 および走査配線 14 に囲まれる領域に絵素電極 22（透明導電膜）が形成されている。なお、保持容量を形成する為の保持容量配線は説明を簡単にする為省略してある。

#### 【0027】

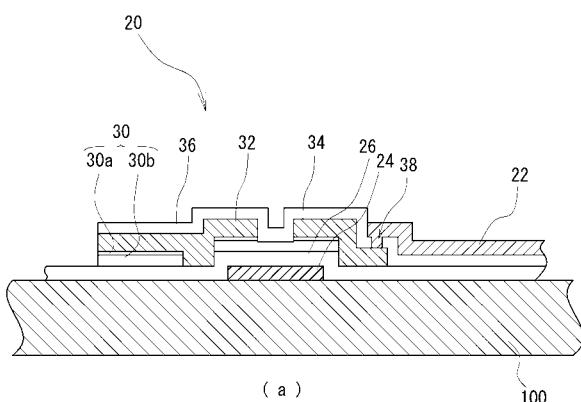

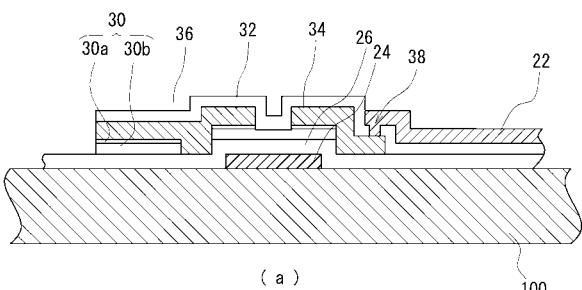

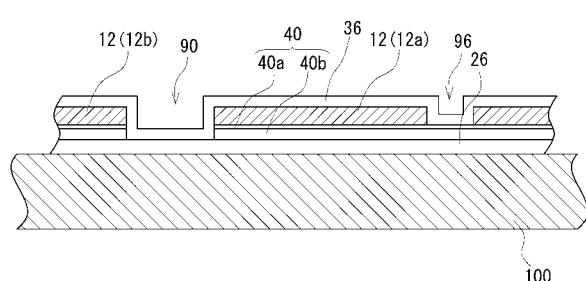

信号配線 12 と走査配線 14 の交差部には、この絵素電極 22 のスイッチング素子である TFT（薄膜トランジスタ）20 が設けられている。この TFT 20 の断面図（図 2 の A - A 断面図）を図 3 に示す。TFT 20 は、ガラス基板 100 上にゲート電極 24、第 1 の絶縁膜 26、半導体層 30（第 1 の半導体層 30a および第 2 の半導体層 30b）、ソース電極 32、ドレイン電極 34、第 2 の絶縁膜 36 とが積層されることにより形成されている。また、第 2 の絶縁膜 36 の表面からドレイン電極 34 に達するコンタクトホール 38 が形成され、このコンタクトホール 38 により、絵素電極 22 は、ドレイン電極 34 と電気的に接続されている。

#### 【0028】

ここで、信号配線 12 は、映像表示領域のセンターライン付近で分割されており、図 2 における絵素部 11a および 11b はそれぞれ別のソースドライバにより制御されることとなる。また、信号配線 12 の下には、半導体膜 40 が形成されている。本実施形態では、 $S \times$  番目 ( $x < n$ ) の信号配線 12 の分割部 90 付近の半導体膜 40 にスリット 92 が形成されている。なお、この半導体膜 40 は、信号配線 12 と同じ幅かそれ以下で形成されるものであるが、説明のため、図 2 では信号配線 12 より幅を大きくして記載している。

#### 【0029】

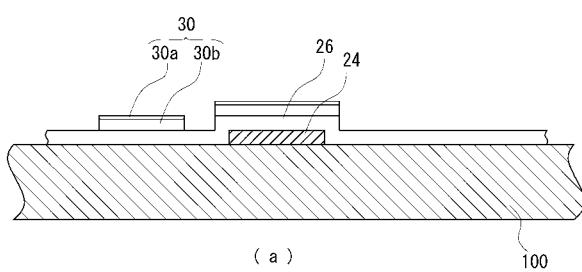

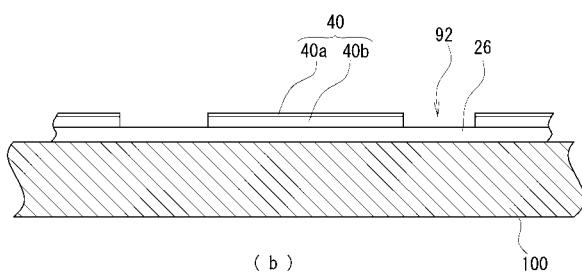

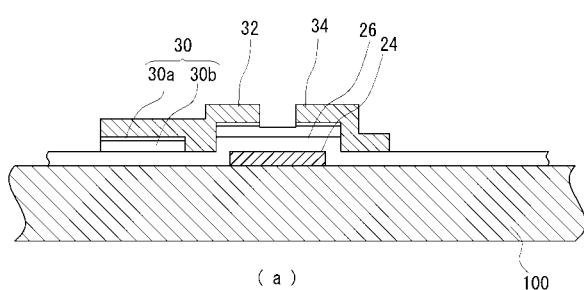

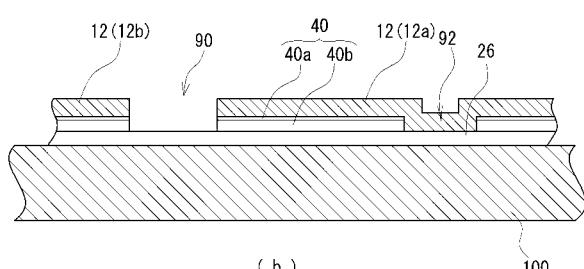

このように構成されるアレイ基板 10 の製造方法について図 4 ~ 8 を参照して以下説明する。図 4 ~ 8 は、アレイ基板 10 の製造工程における各工程の状態を模式的に示す断面図である。ここで図 4 ~ 8 の (a) は、図 2 における TFT 20 の A - A 断面、図 4 ~ 8 の (b) は、図 2 における分割部 90 付近の B - B 断面を各工程順に表している。

#### 【0030】

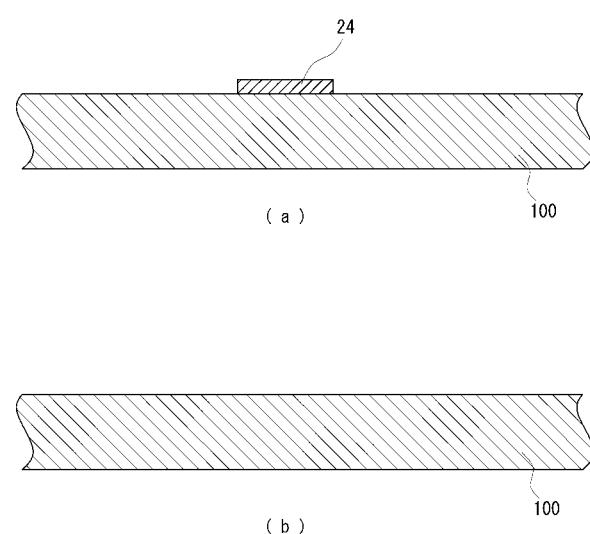

まず、図 4 に示すように、ガラス基板 100 の上に TFT 20 のゲート電極 24 を形成する。また、図 4 には図示されないが、ゲート電極 24 と一体的に走査配線 14 を形成する。

#### 【0031】

具体的には、まず、ガラス基板 100 の表面に、アルミニウム、クロム、タングステン、モリブデン等からなる単層又は多層の第 1 の導体膜を形成する。この第 1 の導体膜の形成には、スパッタリング法等が適用できる。そして、フォトリソグラフィ法によりレジストパターンを形成し、このレジストパターンをマスクとして第 1 の導体膜をエッチングする。最後に、パターン形成のために使用したレジストを剥離液で除去し、走査配線 14 およびゲート電極 24 を所定の形状に形成する。

#### 【0032】

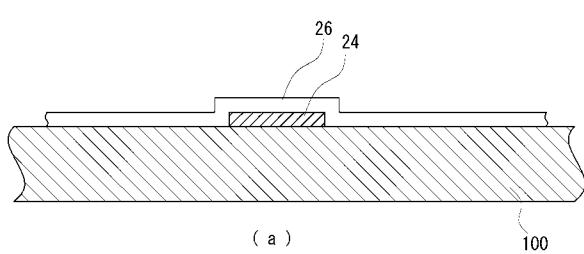

次に、図 5 に示すように、前記工程を経たガラス基板 100 の表面に第 1 の絶縁膜（いわゆるゲート絶縁膜）26 を形成する。この第 1 の絶縁膜 26 には、窒化シリコン（Si

10

20

30

40

50

$N \times$  ) 等が適用できる。また、膜形成方法としては、プラズマ CVD 法等を例示することができる。

#### 【 0 0 3 3 】

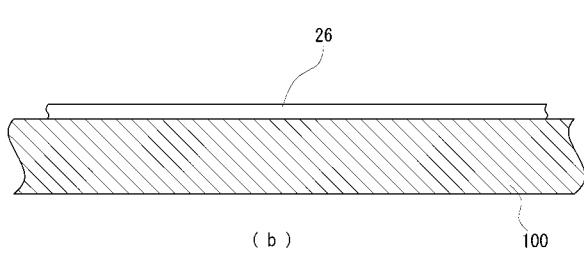

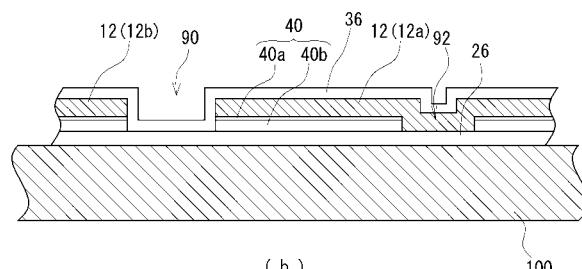

次に、図 6 ( a ) に示すように、 TFT20 において、第 1 の絶縁膜 26 の表面の所定の個所に、第 1 の半導体層 30a および第 2 の半導体層 30b からなる半導体層 30 を形成する。これと同時に、図 6 ( b ) に示すように、後工程で信号配線 12 が重畠して形成される個所に半導体膜 40 を形成する。この半導体膜 40 は、上記第 1 の半導体層 30a および第 2 の半導体層 30b と同じ物質で形成された第 1 の半導体膜 40a および第 2 の半導体膜 40b とからなる。第 1 の半導体層 30a および第 1 の半導体膜 40a には、アモルファスシリコン等が適用できる。また、第 2 の半導体層 30b および第 2 の半導体膜 40b には、 $n+$  型のアモルファスシリコン等が適用できる。10

#### 【 0 0 3 4 】

この半導体層 30 および半導体膜 40 の形成方法としては、プラズマ CVD 法によりアモルファスシリコン等を堆積させる方法が例示できる。そして、半導体層 30 および半導体膜 40 をフォトリソグラフィ法等を用いて、所定の形状にウエットエッティングによりパターニングする。ここで、本実施形態では、図 6 ( b ) に示すように、後工程で S × 番目の信号配線 12 が重畠する半導体膜 40 の一部をエッティングにより除去することで、半導体膜 40 にスリット 92 を形成し、S × 番目の信号配線 12 の識別表示とする。

#### 【 0 0 3 5 】

次に、図 7 に示すように、半導体層 30 および半導体膜 40 上に TFT20 のソース電極 32 および信号配線 12 を形成する。具体的には、まず、半導体層 30 および半導体膜 40 が形成されたガラス基板 100 上に第 2 の導体膜を形成する。この第 2 の導体膜としては、チタン、アルミニウム、クロム、モリブデン等からなる単層または多層の導体膜が例示できる。また、第 2 の導体膜の形成方法としては、プラズマ CVD 法などが適用できる。20

#### 【 0 0 3 6 】

そして、このように形成した第 2 の導体膜をフォトリソグラフィ法により、所定の形状にパターニングする。ここで、図 7 ( b ) に示すように、信号配線 12 には、図 2 に示した表示領域のセンターライン X 付近の第 2 の導体膜を一部除去し、分割部 90 を形成する。この工程を経て、ガラス基板 100 上には、信号配線 12 、ソース電極 32 、ドレイン電極 34 が形成される。30

#### 【 0 0 3 7 】

次に、図 8 に示すように、第 2 の絶縁膜 36 ( いわゆるパッシベーション膜 ) を形成する。この第 2 の絶縁膜 36 には、窒化シリコン ( SiNx ) 等が適用できる。また、膜形成方法としては、プラズマ CVD 法等を例示することができる。

#### 【 0 0 3 8 】

成膜後、フォトリソグラフィ法により、第 2 の絶縁膜 36 をパターニングする。具体的には、図 8 ( a ) に示すように、ドレイン電極 34 と絵素電極 22 を電気的に接続するためのコンタクトホール 38 を形成する。

#### 【 0 0 3 9 】

コンタクトホール 38 の形成後、ITO ( Indium Tin Oxide : インジウム酸化スズ ) からなる透明導電膜を形成する。この透明導電膜の形成方法としては、プラズマ CVD 法が例示できる。そして、フォトリソグラフィ法により、この透明導電膜を所定の形状にパターニングし、絵素電極 22 を得る。40

#### 【 0 0 4 0 】

また、本実施形態では、S × 番目の信号配線 12 が積層された半導体膜 40 に、スリット 92 による識別表示が形成されているのに加え、他の信号配線 12 については、半導体膜 40 に異なる識別表示が形成されている。例えば、図 9 に示すように、S y ( y < n ) 番目の信号配線 12 には切り欠き部 94 を、S z ( z < n ) 番目の信号配線 12 にはスリットを 2 つ ( 92a , 92b ) それぞれ半導体膜 40 に形成している。例えば、ソ-

STA B (Tape Automated Bonding) の最初、最後の信号に対する信号配線 12 に対して切り欠き部 94、ソース STA B 中心の信号に対する信号配線 12 にスリットを 2つ (92a, 92b) というようするのも有効である。なぜなら、一つの TAB に接続する端子から表示領域までの引き出し配線の長さが場所によって異なっており、それぞれの場所の配線抵抗評価をする場合があるからである。このように、本実施形態では、所定の信号配線 12 が積層された半導体膜 40 に、スリット 92 や切り欠き部 94 による識別表示を設け、その識別表示により所定の信号配線 12 が視覚により識別可能となっている。なお、この識別表示は、スリット 92 や切り欠き部 94 に限られるものではなく、丸や三角といったマークによるものや、半導体層 30 の長短によるものであってもよい。

## 【0041】

10

以上のような工程を経て、本発明の第 1 実施形態に係る TFT アレイ基板 10 を得ることができる。

## 【0042】

このような構成の TFT アレイ基板 10 によれば、ガラス基板 100 上に形成された半導体膜 40 に、所定の信号配線 12 を識別するため、スリット 92 や切り欠き部 94 等による識別表示が形成されている。そのため、プローピング等により信号配線 12 を評価する場合において、チェックすべき信号配線 12 を特定する際の目安となり、TFT アレイ基板 10 の評価等を迅速かつ正確に行うことができる。しかも、スリット 92 や切り欠き部 94 が形成された半導体膜 40 は、信号配線 12 の断線防止等を目的として形成されるものであり、電気的な役割を果たすものではないため、TFT アレイ基板 10 の性能、品質等に影響を与えることはない。

20

## 【0043】

また、上記 TFT アレイ基板 10 は、その信号配線 12 が延在方向で分割され、ソース信号が 2 方向から供給されたものである。そして、その信号配線 12 の分割部 90 付近の半導体膜 40 に識別表示が付されている。したがって、映像表示面であるため信号配線 12 の分割部分にラインナンバー等を付すことができず、その特定が困難であったこの種の TFT アレイ基板 10 であっても、容易に信号配線 12 を特定することができる。

30

## 【0044】

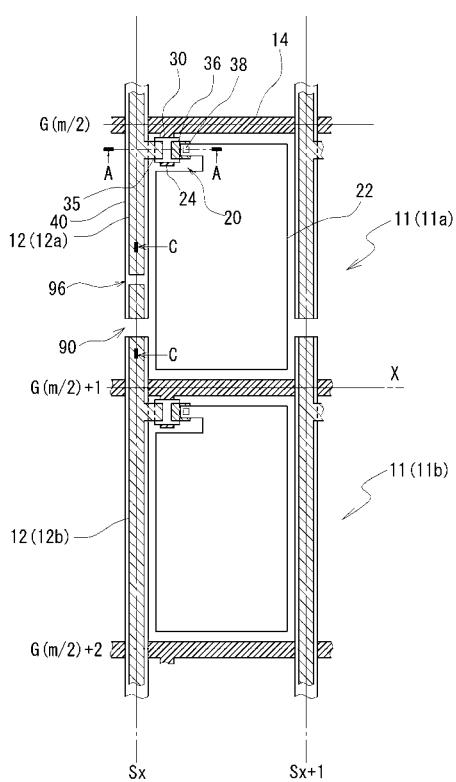

次に、図 10 および図 11 を参照して、本発明の第 2 実施形態に係る TFT アレイ基板 15 について説明する。図 10 は、信号配線 12 の分割部 90 付近における絵素部 11 の拡大図、図 11 は、図 10 における C-C 断面図を示している。なお、第 1 実施形態に係る TFT アレイ基板 10 と同じ構成である個所は、同一の符号を付してその説明を省略する。この TFT アレイ基板 15 は、上記第 1 実施形態に係る TFT アレイ基板 10 と以下の点で異なる。

## 【0045】

40

図示されるように、TFT アレイ基板 15 は、信号配線 12 の下に形成された半導体膜 40 ではなく、信号配線 12 自体に識別表示が形成されている。本実施形態では、S × 番目の信号配線 12 にスリット 96 による識別表示が付されている。この識別表示は、ソース信号の転送速度およびスイッチングの速度変化や、表示ムラが発生しないよう、信号配線 12 と絵素電極 22 との間に生じる寄生容量が変化しないような形状で付されている。つまり、識別表示の有無により、信号配線 12 と絵素電極 22 との間に生じる寄生容量が変化しないような形状であれば、第 1 実施形態と同様、信号配線 12 を切り欠いたり、丸や三角といったマークによる識別表示としてもよい。

## 【0046】

50

このような構成の TFT アレイ基板 15 によれば、信号配線 12 の分割部 90 付近には、その位置等を示すスリットや切り欠き部等の識別表示が形成されている。そのため、第 1 実施形態と同様に、プローピング等により信号配線 12 を評価する場合において、チェックすべき信号配線 12 を特定する目安となり、TFT アレイ基板 10 の評価等を迅速かつ正確に行うことができる。しかも、この識別表示は、信号配線 12 と絵素電極 22 の寄生容量に影響を与えないように付されているため、TFT アレイ基板 10 の性能、品質等

に影響を与えることはない。

【0047】

次に、上記第1実施形態に係るTFTアレイ基板10、または第2実施形態に係るTFTアレイ基板15を用いた液晶表示パネルについて説明する。

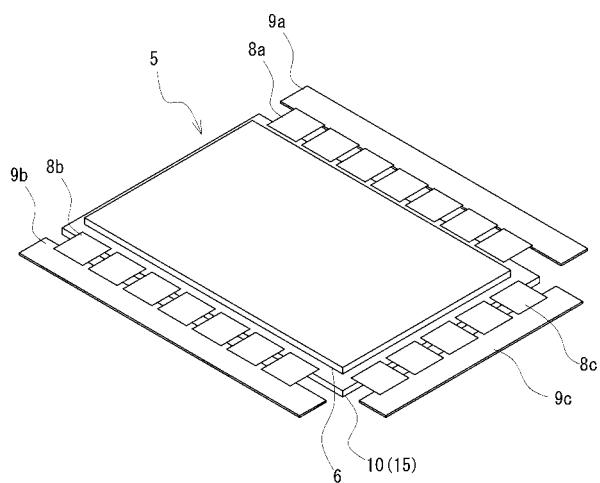

【0048】

図12は、後述するTAB8a, 8b, 8cやプリント基板9a, 9b, 9cが実装された状態の液晶表示パネル5を模式的に示した斜視図である。図に示すように、液晶表示パネル5は、主として、上記TFTアレイ基板10(15)とカラーフィルタ基板6により構成される。

【0049】

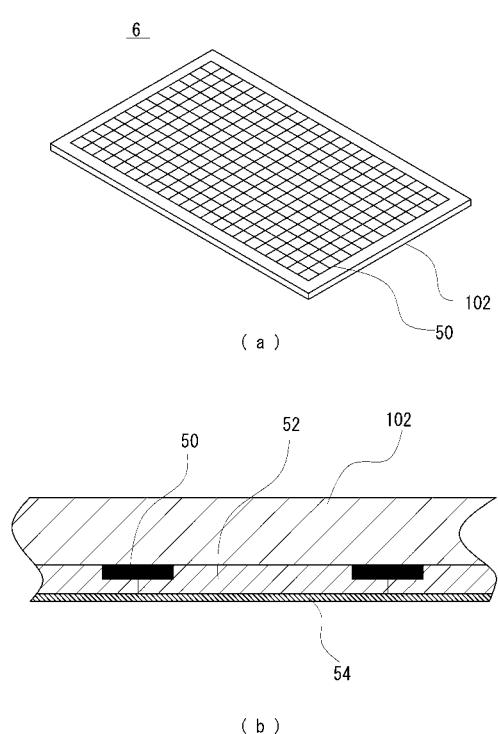

図13を参照してカラーフィルタ基板6の構成について説明する。図13(a)は、カラーフィルタ基板6の全体構造を模式的に示した斜視図、図13(b)は、カラーフィルタ基板6の断面構造を示した図である。図に示されるように、ガラス基板102の表面に格子状のブラックマトリクス50が形成され、各格子の内側に赤色、緑色、青色のいずれかの色からなる着色層52が所定の順序で形成されてなる。また、ブラックマトリクス50および着色層52の表面には、各着色層52共通の共通電極54が形成されている。

【0050】

このカラーフィルタ基板6の製造方法について説明する。まず、ガラス基板102の表面にBMLレジスト(黒色着色剤を含有する感光性樹脂組成物)等を塗布する。次いで、塗布したBMLレジストをフォトリソグラフィ法等を用いて所定のパターンに形成する。これにより、所定のパターンのブラックマトリクス50を得る。

【0051】

次に、ブラックマトリクス50を形成したガラス基板102の表面に、着色感材(所定の色の顔料を分散した溶液)を塗布する。そして、塗布した着色感材をフォトリソグラフィ法等を用いて所定のパターンの着色層52を得る。

【0052】

次に、着色層52の表面に透明導電膜を形成し、共通電極54を得る。この透明性導電膜としては、ITOが適用できる。また、膜成形方法としては、スパッタリング法が例示できる。以上の工程を経て、カラーフィルタ基板6を得る。

【0053】

このカラーフィルタ基板6と、TFTアレイ基板10(15)の表面にポリイミド等からなる図示されない配向膜が形成され、両者の間に液晶が充填されることにより液晶表示パネル5が得られる。

【0054】

また、この液晶表示パネル5には、ゲートドライバおよびソースドライバICがボンディングされた複数のTAB8a, 8b, 8cが実装されている。

【0055】

このTAB8a, 8b, 8cは、液晶表示パネル5の長辺および短辺の一方側に実装されている。そして、TAB8a, 8b, 8cには、コントローラ等が搭載されたプリント基板9a, 9b, 9cが接続されている。ここで、TFTアレイ基板10(15)上に形成された信号配線12a, 12bには、それぞれTFTアレイ基板10の相対する長辺に実装されたTAB8a, 8b上のソースドライバICより、ソース信号(映像データ)が供給される。一方、走査配線12cには、液晶表示パネル5の短辺の一方側に実装されたTAB8c上のゲートドライバICより走査信号が供給されることとなる。

【0056】

以上のように、本発明に係る液晶表示パネル5が構成される。以下、この液晶表示パネル5を適用した液晶表示装置について説明する。

【0057】

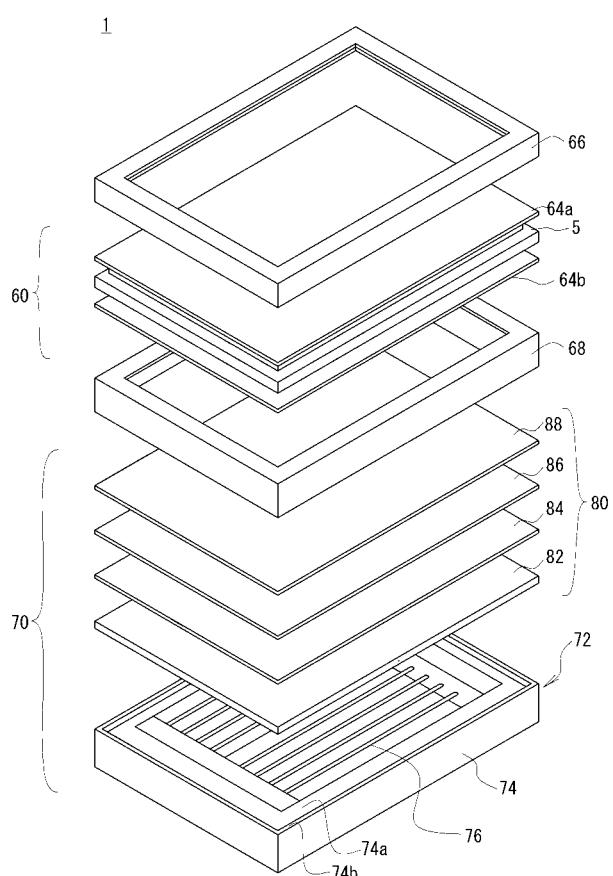

図14は、上記液晶表示パネル5を備えた液晶表示装置1の分解斜視図である。図に示すように、液晶表示装置1は、主に、液晶表示パネル部60と、これを背面側から照射す

10

20

30

40

50

るバックライトユニット70とで構成されている。

【0058】

液晶表示パネル部60は、上記液晶表示パネル5の両面に、偏光板64a, 64bが貼付されたもので構成されている。偏光板64a, 64bは、一軸延伸ポリビニルアルコールフィルムにヨウ素化合物を添加した偏光フィルムが基板フィルムに挟まれることで構成されている。液晶パネル部60は、枠状の外フレーム66と内フレーム68との間に挟まれた状態で、バックライトユニット70の上方に配置される。

【0059】

バックライトユニット70は、光源ユニット72と、光学シートユニット80とから構成される。光源ユニット72は、上面を開口した箱型形状の金属製のベーストレイ74内に、光源となる複数の管状ランプ76, 76...が平行に配置されて構成されている。

10

【0060】

この複数の管状ランプ76, 76...の上に配置される光学シートユニット80は、管状ランプ76の輝度分布を均一にするための拡散板82と、拡散板82上に配置されるレンズシート等の光学シート類84, 86, 88とで構成されている。

20

【0061】

拡散板82は、光学シート類84, 86, 88とほぼ同一の略矩形形状に形成されている。拡散板82は、やや厚みのある透明な板状をなし、載置したときに撓みが生じ難くなっている。そのため、この上に載置される複数の光学シート類84, 86, 88は、この拡散板82上で平面状に支持される。

【0062】

ベーストレイ74の周縁には、拡散板72と光学シート類74, 76, 78を載置するための載せ代となる周縁部74aが所定の厚みで形成されている。この周縁部74aには、外周に沿って起立部74bが立設されており、この内側に拡散板82と光学シート類84, 86, 88が載置される。

【0063】

以上ように、本発明に係る液晶表示装置1が構成され、パソコン用コンピュータや、テレビ受像機の表示装置として適用される。

【0064】

このような構成の本発明に係る液晶表示パネル5、およびこの液晶表示パネル5を用いた液晶表示装置1によれば、液晶表示装置製造工程において、液晶表示パネル5、および液晶表示装置1組立後に点灯不良等が発見された場合、TFTアレイ基板10(15)の信号配線12を分析しなければならない。この時、信号配線12に識別表示が付されているため、その識別表示が付されている信号配線12を基準として、不良が発生している個所の信号配線12を容易に見出すことができる。したがって、液晶表示パネルや液晶表示装置組立後における不良解析を迅速且つ確実なものとすることができる。

30

【0065】

以上、本発明の実施の形態について詳細に説明したが、本発明は上記実施の形態に何ら限定されるものではなく、本発明の要旨を逸脱しない範囲で種々の改変が可能である。

40

【0066】

例えば、上記実施形態では、液晶表示装置に適用される液晶表示パネルおよびTFTアレイ基板について説明したが、その他の表示装置、例えば、エレクトロルミネンスディスプレイ等にも本発明の技術的思想が適用可能である。

【図面の簡単な説明】

【0067】

【図1】本発明の第1実施形態に係るTFTアレイ基板全体の概略構成図である。

【図2】図1に示したTFTアレイ基板上の信号配線の分割部付近における絵素部の拡大図である(半導体膜に信号配線の識別表示としてスリットが形成されているもの)。

【図3】図2に示した絵素部におけるTFT(薄膜トランジスタ)の断面図である。

【図4】図1～3に示したTFTアレイ基板の製造工程において、ゲート電極を形成した

50

状態を示した断面図である。

【図 5】図 1～3 に示した TFT アレイ基板の製造工程において、第 1 の絶縁膜を形成した状態を示した断面図である。

【図 6】図 1～3 に示した TFT アレイ基板の製造工程において、半導体層および半導体膜を形成した状態を示した断面図である。

【図 7】図 1～3 に示した TFT アレイ基板の製造工程において、ソース電極、ドレイン電極、信号配線を形成した状態を示した断面図である。

【図 8】図 1～3 に示した TFT アレイ基板の製造工程において、第 2 の絶縁膜、絵素電極を形成した状態を示した断面図である。

【図 9】図 1 に示した TFT アレイ基板上の信号配線の分割部付近における絵素部の拡大図である（半導体膜に信号配線の識別表示として切り欠き部、および複数のスリットが形成されているもの）。

【図 10】本発明の第 2 実施形態に係る TFT アレイ基板上の信号配線の分割部付近における絵素部の拡大図である。

【図 11】図 10 に示した信号配線の分割部付近における TFT アレイ基板の断面図である。

【図 12】本発明の第 1 実施形態もしくは第 2 実施形態に係る TFT アレイ基板を適用した液晶表示パネルを説明するための外観斜視図である。

【図 13】(a) は、図 12 に示したカラーフィルタ基板の外観斜視図であり、(b) はカラーフィルタ基板の断面図である。

【図 14】図 12 に示した液晶表示パネルを適用した液晶表示装置を説明するための分解斜視図である。

#### 【符号の説明】

##### 【0068】

|     |                |

|-----|----------------|

| 1   | 液晶表示装置         |

| 5   | 液晶表示パネル        |

| 6   | カラーフィルタ基板      |

| 10  | TFT アレイ基板      |

| 12  | 信号配線           |

| 14  | 走査配線           |

| 20  | TFT (薄膜トランジスタ) |

| 22  | 絵素電極           |

| 24  | ゲート電極          |

| 26  | 第 1 の絶縁膜       |

| 30  | 半導体層           |

| 32  | ソース電極          |

| 34  | ドレイン電極         |

| 36  | 第 2 の絶縁膜       |

| 38  | コンタクトホール       |

| 40  | 半導体膜           |

| 90  | 分割部            |

| 92  | スリット           |

| 94  | 切り欠き部          |

| 96  | スリット           |

| 100 | ガラス基板          |

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

100

(a)

100

(b)

【図6】

100

(a)

100

(b)

【図7】

100

(a)

100

(b)

【図8】

100

(a)

100

(b)

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

|                |                                                                                                                                                                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | TFT阵列基板，液晶显示面板和液晶显示装置                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2008181049A</a>                                                                                                                                                                                                                                | 公开(公告)日 | 2008-08-07 |

| 申请号            | JP2007016148                                                                                                                                                                                                                                                 | 申请日     | 2007-01-26 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 永井敦                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 永井 敦                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09F9/30 G02F1/1345 G02F1/13 G09F9/00                                                                                                                                                                                                                        |         |            |

| FI分类号          | G09F9/30.338 G02F1/1345 G02F1/13.101 G09F9/00.352                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H088/FA12 2H088/FA13 2H088/FA16 2H088/FA30 2H088/HA02 2H088/HA08 2H092/GA41 2H092/GA57 2H092/JA24 2H092/JB32 2H092/JB77 2H092/MA57 5C094/AA43 5C094/BA03 5C094/BA43 5C094/DA20 5C094/FA04 5C094/GB10 5G435/AA17 5G435/AA19 5G435/BB12 5G435/KK05 5G435/KK10 |         |            |

| 代理人(译)         | 上野登                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                    |         |            |

### 摘要(译)

要解决的问题：快速准确地区分信号线而不影响图像显示。

ŽSOLUTION：在TFT阵列基板10上形成的多个信号布线12下面形成的半导体膜40通过狭缝92或凹口94设置有识别显示，从而即使在未分配用于识别的数字等时也是如此。在信号配线12中，可以快速准确地识别用探针检查的预定信号配线12。 Ž