(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2003 - 207805

(P2003 - 207805A)

(43)公開日 平成15年7月25日(2003.7.25)

| (51) Int.Cl <sup>7</sup> | 識別記号   | F I            | テマコード <sup>*</sup> (参考) |

|--------------------------|--------|----------------|-------------------------|

| G 0 2 F 1/1368           |        | G 0 2 F 1/1368 | 2 H 0 9 2               |

|                          | 1/1343 | 1/1343         | 5 F 1 1 0               |

| H 0 1 L 21/336           |        | H 0 1 L 29/78  | 617 N                   |

|                          | 29/786 |                | 616 A                   |

審査請求 未請求 請求項の数 6 O L (全 6 数)

(21)出願番号 特願2002 - 4961(P2002 - 4961)

(22)出願日 平成14年1月11日(2002.1.11)

(71)出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(72)発明者 山口 彩子

大阪府門真市大字門真1006番地 松下電器

産業株式会社内

(72)発明者 三井 健二

大阪府門真市大字門真1006番地 松下電器

産業株式会社内

(74)代理人 110000040

特許業務法人池内・佐藤アンドパートナー

ズ

最終頁に続く

(54)【発明の名称】 液晶表示装置

(57)【要約】

【課題】 アクティブマトリックス液晶表示装置において、蓄積容量部からのリーク電流を抑制し、かつ画素駆動用スイッチング素子全体のサイズを小さくする。

【解決手段】 画素スイッチング素子に用いられる、一つの半導体層に複数のゲート電極3を有するマルチゲート型MISトランジスタにおいて、ドレイン領域5及び蓄積容量部21に近いゲート電極3のチャネル長の寸法を他方のゲート電極3よりも長くする。

## 【特許請求の範囲】

【請求項1】マトリクス状に配列した画素電極とこれを駆動する周辺回路を同一基板上に集積化したアクティブマトリクスアレイ基板と、これと対向する対向基板と、前記両基板により保持される液晶層と、偏光板とを備えた液晶表示装置であって、前記偏光板の配置がノーマリィホワイトであり、前記画素電極と周辺回路を構成する薄膜トランジスタは、複数のゲート電極を有するマルチゲート型MISトランジスタであり、前記トランジスタは、ソースおよびドレイン領域とチャネル領域との間に低濃度不純物領域を備えたLDD構造を有し、前記複数のゲート電極において、少なくとも一つのゲート電極がその他のゲート電極と寸法が異なることを特徴とする液晶表示装置。

【請求項2】前記薄膜トランジスタは、画素スイッチング素子に用いられ、ドレイン領域及び蓄積容量部に近いゲート電極のチャネル長の寸法が他のゲート電極のチャネル長寸法よりも長いことを特徴とする請求項1記載の液晶表示装置。

【請求項3】ドレイン領域及び蓄積容量部に近いゲート電極のチャネル長の寸法が、0.1～10μmの範囲であり、他のゲート電極のチャネル長寸法が0.2～20μmの範囲である請求項2記載の液晶表示装置。

【請求項4】マトリクス状に配列した画素電極とこれを駆動する周辺回路を同一基板上に集積化したアクティブマトリクスアレイ基板と、これと対向する対向基板と、前記両基板により保持される液晶層と、偏光板とを備え、前記偏光板の配置がノーマリィホワイトである液晶表示装置に使用される前記薄膜トランジスタであって、このトランジスタは、複数のゲート電極を有するマルチゲート型MISトランジスタであり、これは、ソースおよびドレイン領域とチャネル領域との間に低濃度不純物領域を備えたLDD構造を有し、前記複数のゲート電極において、少なくとも一つのゲート電極がその他のゲート電極と寸法が異なることを特徴とする薄膜トランジスタ。

【請求項5】前記薄膜トランジスタは、画素スイッチング素子に用いられ、ドレイン領域及び蓄積容量部に近いゲート電極のチャネル長の寸法が他のゲート電極のチャネル長寸法よりも長いことを特徴とする請求項4記載の薄膜トランジスタ。

【請求項6】ドレイン領域及び蓄積容量部に近いゲート電極のチャネル長の寸法が、0.1～10μmの範囲であり、他のゲート電極のチャネル長寸法が0.2～20μmの範囲である請求項5記載の薄膜トランジスタ。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は、アクティブマトリクス型の液晶表示装置に関する。

## 【0002】

【従来の技術】液晶表示装置は、薄型かつ軽量であることにより、OA用、AV用に限らずあらゆる分野で使用されている。特に薄膜トランジスタ（以下TFTと称する）を用いた液晶表示装置は、階調表示に優れ、カラーディスプレイとしてCRTに迫る性能を実現し、更に高精細化が求められている。特に薄膜材料として多結晶シリコン（以下polysiliconと称する）は、表示部やセンサ部を構成するTFTに加えて、周辺駆動回路を構成するTFTを同一基板上に集積形成することが可能なため注目を集めている。

【0003】アクティブマトリクス液晶表示装置の画素をオン／オフするためのスイッチング素子として用いられるTFTについては、通常用いられるノーマリィホワイトの場合、特に画素輝点欠陥の原因となるリーク電流を抑制するため、従来から様々な構成が提案され実用化してきた。

【0004】例えば、LDD（Lightly Doped Drain）構造のTFT（以下LDD-TFTと称する）が知られている。このLDD-TFTは拡散層の周辺に低濃度不純物領域を設けて、ソース、ドレイン領域端部での電界集中を緩和することができ、オフセットゲート構造と同様にリーク電流抑制効果がある。

【0005】また、TFTのリーク電流を減少させるもう一つの方法として、2個以上のゲート電極を設けた、マルチゲート構成のTFTが従来から知られている。このマルチゲートTFTは、等価回路的には複数のTFTを直列接続した構成となっている。リーク電流は複数のTFTのうち、オフ電流値の最も低いTFTに依存するため、リーク電流を抑制することができる。さらに、上記両構造を組み合わせたマルチゲート構造のLDD-TFTは、それぞれの長所が生かされ相乗効果が得られる。

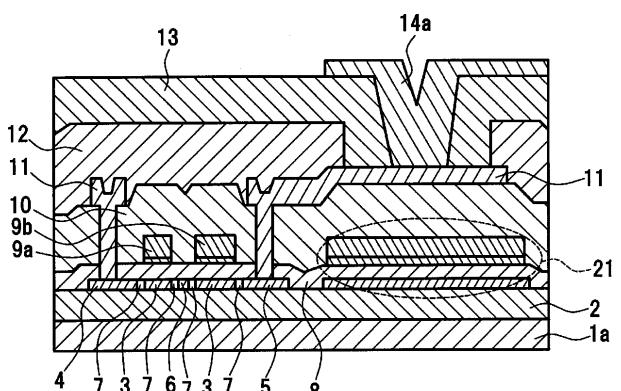

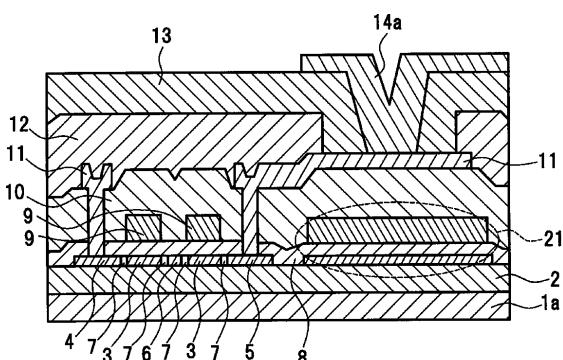

【0006】図4を参照して従来のマルチゲート構造のLDD-TFTを用いた画素駆動用スイッチング素子を簡潔に説明する。ガラス基板1a上に、所定の形状にパターニングされたpolysilicon膜が形成されている。このpolysilicon膜には互いに分離した一対のチャネル領域3が形成されており、両者は接続領域6により互いに接続されている。一方のチャネル領域3の端部にはソース領域4が形成されており、他方のチャネル領域3の端部にはドレイン領域5が形成されている。ソース領域4、接続領域6およびドレイン領域5と各チャネル領域3との間には各々ソース領域およびドレイン領域と同一導電型の低濃度不純物領域即ちLDD領域7が合計4箇所形成されている。各チャネル領域3の上にはゲート酸化膜8を介してゲート電極9がパターニング形成されTFTを構成している。TFTの上には層間絶縁膜10が成膜されている。さらにその上に信号電極11がパターニング形成されており、コンタクトホールを介してソ

ース領域4とドレイン領域5に電気接続されている。さらにその上に最終層間絶縁膜12を形成し、蓄積容量部21上の信号電極11にコンタクトホールを開口し、平坦化膜13を形成後、更に蓄積容量部上の信号電極12にコンタクトホールを開口し、画素電極(ITO)14aを形成し電気接続させる。

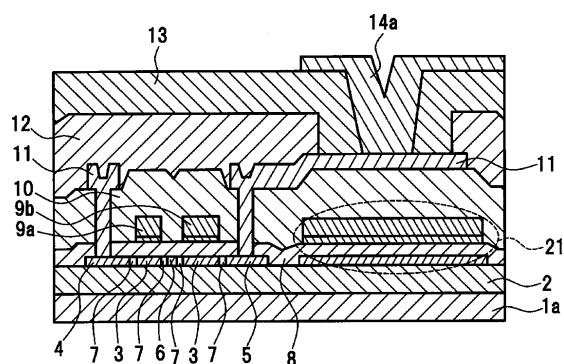

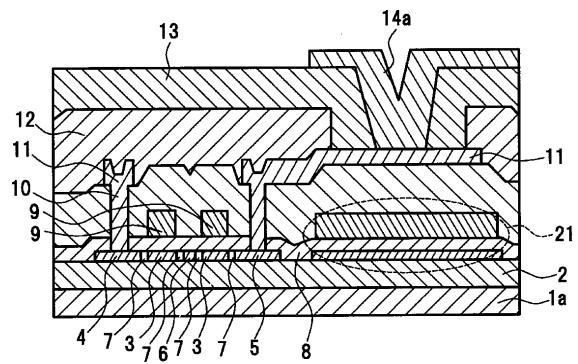

【0007】図5は、従来のチャネル長を短縮化し微細化したマルチゲート構造のLDD-TFTを用いた画素駆動用スイッチング素子を示す断面図である。図5において図4と同一部分には同一符号を付している。構成及び製造方法は、上記図4で説明した従来のマルチゲート構造のLDD-TFTを用いた画素駆動用スイッチング素子と同様であるが、図示のように、チャネル長を短縮化したことにより、画素駆動用スイッチング素子全体のサイズも縮小されていることが判る。

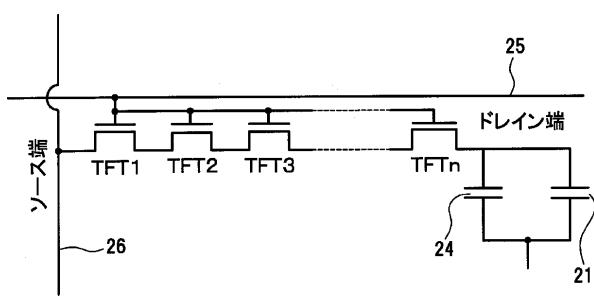

【0008】図3は、マルチゲート構造のLDD-TFTを採用したアクティブマトリクス型液晶表示装置の1画素分を切り取って示した等価回路図である。スイッチング素子はTFT1ないしTFTnの直列接続からなり、個々のゲート電極はそれぞれ共通にゲート配線に接続されている。TFT1のソース領域端部は信号線に接続されている一方、TFTnのドレイン領域端部は画素電極を介して液晶を駆動する。なお、液晶24と並列に蓄積容量部21も接続されている。

#### 【0009】

【発明が解決しようとする課題】アクティブマトリクス型液晶表示装置は高性能化、高精細化のためにTFTの微細化が必要となる。従来のマルチゲート構造のLDD-TFTは、リーク電流を低く抑制できる多大な効果を得ることができたが、TFTの微細化のためチャネル長を短縮化すると、不純物の水平方向拡散および電圧を印加したとき空乏層の広がりのため実効チャネル長が短くなり、リーク電流が極端に増大することとなり、特に、液晶層に印加された電圧が保持できず、蓄積容量部からの電流のリークが原因となる画素輝点欠陥が発生するという問題を有していた。

【0010】本発明は、このような事情に鑑みなされたもので、リーク電流の増大を防止し、かつスイッチング素子全体の小型化を実現可能な液晶表示装置の提供を、その目的とする。

#### 【0011】

【課題を解決するための手段】前記目的を達成するため、本発明の液晶表示装置は、マトリクス状に配列した画素電極とこれを駆動する周辺回路を同一基板上に集積化したアクティブマトリクスアレイ基板と、これと対向する対向基板と、前記両基板により保持される液晶層と、偏光板とを備えた液晶表示装置であって、前記偏光板の配置がノーマリィホワイトであり、前記画素電極と周辺回路を構成する薄膜トランジスタは、複数のゲート電極を有するマルチゲート型MISトランジスタであ

り、前記トランジスタは、ソースおよびドレイン領域とチャネル領域との間に低濃度不純物領域を備えたLDD構造を有し、前記複数のゲート電極において、少なくとも一つのゲート電極がその他のゲート電極と寸法が異なることを特徴とする。

【0012】本発明の液晶表示装置は、前記のような構成を有することから、リーク電流が増大することが防止でき、その結果、画素輝点欠陥の発生が防止され、かつ微細化が可能となる。

【0013】本発明の液晶表示装置において、前記薄膜トランジスタは、画素スイッチング素子に用いられ、ドレイン領域及び蓄積容量部に近いゲート電極のチャネル長の寸法が他のゲート電極のチャンネル長寸法よりも長いことが好ましい。例えば、ドレイン領域及び蓄積容量部に近いゲート電極のチャネル長の寸法は、0.1~10μmの範囲であり、他のゲート電極のチャンネル長寸法は0.2~20μmの範囲であり、好ましくは、ドレイン領域及び蓄積容量部に近いゲート電極のチャネル長の寸法は、1.0~4.0μmの範囲であり、他のゲート電極のチャンネル長寸法は2.0~8.0μmの範囲である。

【0014】また、本発明の薄膜トランジスタは、マトリクス状に配列した画素電極とこれを駆動する周辺回路を同一基板上に集積化したアクティブマトリクスアレイ基板と、これと対向する対向基板と、前記両基板により保持される液晶層と、偏光板とを備え、前記偏光板の配置がノーマリィホワイトである液晶表示装置に使用される前記薄膜トランジスタであって、このトランジスタは、複数のゲート電極を有するマルチゲート型MISトランジスタであり、これは、ソースおよびドレイン領域とチャネル領域の間に低濃度不純物領域を備えたLDD構造を有し、前記複数のゲート電極において、少なくとも一つのゲート電極がその他のゲート電極と寸法が異なることを特徴とする。

【0015】前記薄膜トランジスタは、画素スイッチング素子に用いられ、ドレイン領域及び蓄積容量部に近いゲート電極のチャネル長の寸法が他のゲート電極のチャンネル長寸法よりも長いことが好ましい。

#### 【0016】

40 【発明の実施の形態】以下、本発明の液晶表示装置の一例について、図面を参照しながら説明する。

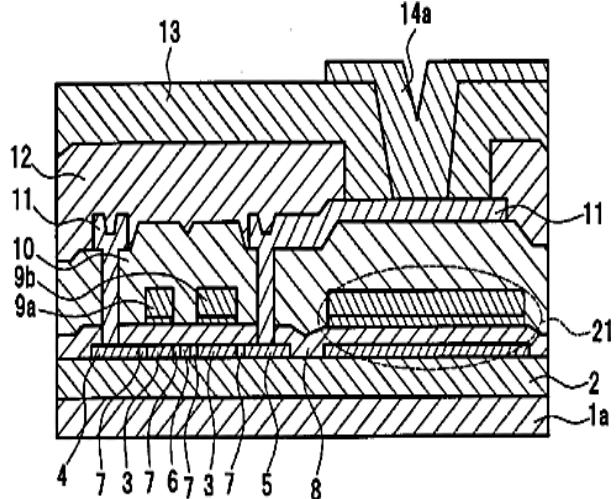

【0017】図1は、本発明のアクティブマトリクス型液晶表示装置において、特に重要なTFT周辺を拡大して表した部分断面図である。図示するTFTはn-ch型でありアクティブマトリクス型液晶表示装置の画素駆動用スイッチング素子を構成する。このTFTは例えば、以下のようにして製造できる。

【0018】まず、基板1aとして無アルカリガラス基板(例えば1737:コーニング社製)を用い、酸化シリコン薄膜からなるアンダーコート2(例えば、厚み4

0.0 nm)を形成する。この上に、非結晶シリコン薄膜をプラズマCVD法により形成(例えば、厚み50 nm)した後、エキシマレーザー光を照射して溶融・結晶化し多結晶シリコン薄膜を形成する。前記多結晶シリコン薄膜を画素駆動用スイッチング素子部と蓄積容量部に加工し、酸化シリコン薄膜からなるゲート絶縁膜8(例えば、厚み90 nm)形成する。前記ゲート絶縁膜9上にフォトトレジストマスクを形成し、イオン注入法にて第一の不純物注入を行い、高濃度不純物注入領域(拡散層領域)となるソース領域4、接続領域6およびドレイン領域5を形成する。第1の不純物注入は燐(P)イオンを、例えば、加速電圧12 KV, ドーズ量 $2.5 \times 10^{14} / \text{cm}^2$ の条件で注入する。第一の不純物注入後、フォトトレジストマスクを除去し、ゲート電極9a、9b(例えば、Mo(モリブデン)に高融点金属、例えばW(タンゲステン)を35%添加した合金)を形成(例えば、厚み300 nm)し、ドレイン領域5側のゲート電極9bがソース領域4側のゲート電極9aよりもチャネル長の長さが大きくなるようにパターニング形成する。

【0019】次に、ゲート電極9a、9bをマスクとして、第2の不純物注入を行い、ソース領域4と接続領域6とドレイン領域5と各チャネル領域3との間に、低濃度不純物注入領域(LDD領域)7を合計4箇所形成する。なお、LDD領域の数は4箇所に制限されず、種々条件に応じ適宜決定される。第2の不純物注入は、燐(P)イオンを、例えば、加速電圧70 KV, ドーズ量 $2.5 \times 10^{14} / \text{cm}^2$ の条件で注入する。その後、注入した不純物の活性化処理を行う。その後、酸化シリコンからなる層間絶縁膜10を形成(例えば、厚み400 nm)し、ソース及びドレイン領域上にコンタクトホールを開口し、信号電極11を形成し、電気接続する。その後、酸化シリコンからなる最終絶縁膜12を形成(例えば、厚み400 nm)し、蓄積容量上のドレイン領域5側の信号電極11上にコンタクトホールを開口し、透明なポジ型の感光性アルカリ樹脂(例えば、商品名: FVR、富士薬品工業(株)製)による平坦化膜13を形成した後、所定のフォトマスクを用いて、紫外線照射して、ドレイン電極上にコンタクトホールを開口し、画素電極(ITO)14aを形成し、ドレイン領域側5の信号電極11と電気接続させる。このようにして、アクティブマトリックスアレイ基板が製造できる。

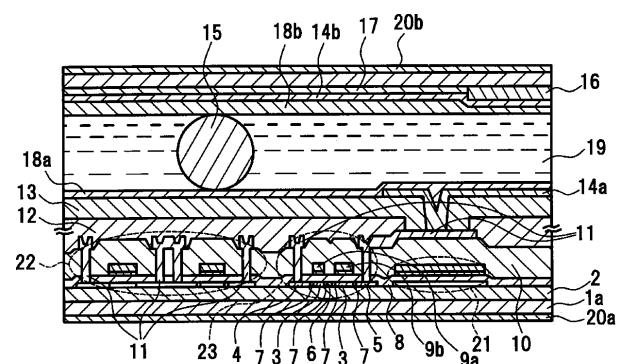

【0020】次に図2を参照して、マルチゲート構造LDD-TFTを用いて構成されたアクティブマトリックス型液晶表示装置の構成例を説明する。

【0021】基板1bにカラーフィルター層16として顔料分散タイプで赤、緑、青のストライプ配列のものとブラックマトリックス層17をフォトリソグラフィーで形成し、その上に、透明電極としてインジウム・錫・オキサイドで画素電極14bを形成することにより、対向基板が製造できる。

\*【0022】つぎに、画素電極14a, b上に、例えば、ポリイミドを-ブチロラクトンに5質量%溶解した溶液を印刷し、加熱(例えば、250)して硬化した後、レーヨン布等を用いた回転ラビング法による配向処理を行うことで配向層18a, bを形成する。

【0023】そして、対向基板1bの画素電極(ITO)14bの周辺部には、例えば、ガラスファイバーを1.0重量%混入した熱硬化型シール樹脂(例えば、商品名:ストラクトボンド、三井東圧化学(株)製)を印刷し、アクティブマトリックス側の基板1aには樹脂ビーズ15を100~200個/mm<sup>2</sup>の割合で散布し、対向側の基板1bと前記アクティブマトリックス側の基板1aを互いに張り合わせ、加熱(例えば、150)してシール樹脂を硬化した後、例えばフッ素エステル系ネマティック液晶19を真空注入し、紫外線硬化性樹脂で封口した後、紫外線光により硬化する。

【0024】こうして形成された対向側の基板1bの外側とアクティブマトリックス側の基板1aの外側に、偏光フィルム20a, bを貼付し(配置はノーマリィホワイト)、アクティブマトリックス型液晶表示装置が完成する。なお、図2において、22は回路構成部を示す。

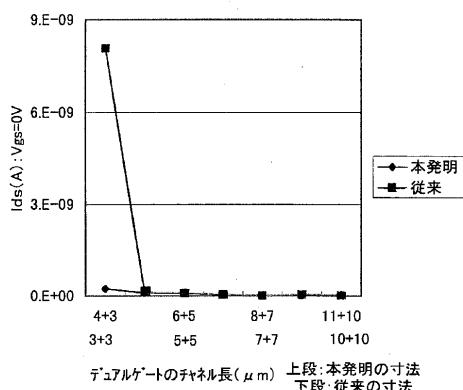

【0025】図6のグラフに、デュアルゲート電極のチャンネル長(μm)とドレイン電流の特性を示す。この図において、横軸がゲート電極のチャンネル長であり、例えば、4 μmと3 μmの二つのゲート電極の場合は、4+3と表示している。また、縦軸は、Vg=0 Vの時のドレイン電流である。このグラフに示すように、ゲート電極のチャンネル長が4 μm未満になると、従来ではドレイン電流(リーク電流)が大きくなるが、本発明は、ほとんどリーク電流が増大しない。

#### 【0026】

【発明の効果】以上説明したように、本発明の液晶表示装置は、液晶層に印加された電圧を保持する能力を高め、特に蓄積容量部からの電流のリークが原因となる画素輝点欠陥の発生を押さえることができる。また、従来と比べ、画素駆動用スイッチング素子全体のサイズを縮小することができ、この結果、アクティブマトリックス型液晶表示装置の高性能化および高精細化を実現できる。

#### 【図面の簡単な説明】

【図1】本発明の液晶表示装置の構造の一例を示す部分断面図である。

【図2】本発明の液晶表示装置の構造の一例を示す断面図である。

【図3】従来のマルチゲート構造LDD-TFTを用いた画素駆動用スイッチング素子で構成されたアクティブマトリックス型液晶表示装置における1画素分の等価回路図である。

【図4】従来のマルチゲート構造LDD-TFTを用いた画素駆動用スイッチング素子を示す断面図である。

【図5】従来のチャネル長を短縮化し微細化したマルチ

ゲート構造LDD-TFTを用いた画素駆動用スイッチング素子を示す断面図である。

【図6】ゲート電極のチャンネル長とドレイン電流との特性を示すグラフである。

【符号の説明】

1a, 1b : ガラス基板

2 : アンダーコート

3 : チャネル領域

4 : ソース領域

5 : ドレイン領域

6 : 接続領域

7 : LDD領域

8 : ゲート酸化膜

\* 9 : ゲート電極

10 : 層間絶縁膜

11 : 配線電極

12 : 最終絶縁膜

13 : 平坦化膜

14a, 14b : 画素電極 (ITO)

15 : 樹脂ビーズ

16 : カラーフィルター層

17 : ブラックマトリクス層

18a, 18b : 配硬膜

19 : 液晶

20a, 20b : 偏光フィルム

\*

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

フロントページの続き

F ターム(参考) 2H092 JA24 JA31 JA37 KA04 MA27

NA13 PA06

5F110 AA06 BB02 CC02 DD02 DD13

EE06 EE28 FF02 GG02 GG13

GG25 GG45 HJ01 HJ04 HJ13

HJ23 HL07 HL11 HM15 NN02

NN03 NN04 NN23 NN27 NN73

PP03 QQ11

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号     | <a href="#">JP2003207805A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2003-07-25 |

| 申请号         | JP2002004961                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2002-01-11 |

| 申请(专利权)人(译) | 松下电器产业有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人      | 山口彩子<br>三井健二                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人         | 山口 彩子<br>三井 健二                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号      | G02F1/1368 G02F1/1343 H01L21/336 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号       | G02F1/1368 G02F1/1343 H01L29/78.617.N H01L29/78.616.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号   | 2H092/JA24 2H092/JA31 2H092/JA37 2H092/KA04 2H092/MA27 2H092/NA13 2H092/PA06 5F110 /AA06 5F110/BB02 5F110/CC02 5F110/DD02 5F110/DD13 5F110/EE06 5F110/EE28 5F110/FF02 5F110/GG02 5F110/GG13 5F110/GG25 5F110/GG45 5F110/HJ01 5F110/HJ04 5F110/HJ13 5F110 /HJ23 5F110/HL07 5F110/HL11 5F110/HM15 5F110/NN02 5F110/NN03 5F110/NN04 5F110/NN23 5F110/NN27 5F110/NN73 5F110/PP03 5F110/QQ11 2H092/JB42 2H192/AA24 2H192/BC31 2H192 /CB02 2H192/CB13 2H192/CB52 2H192/CC02 2H192/DA12 2H192/EA22 2H192/EA43 2H192/EA67 2H192/FB02 |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

在有源矩阵液晶显示装置中，从存储电容器部分泄漏的电流被抑制，并且整体上减小了像素驱动开关元件的尺寸。在用于像素开关元件并且在一个半导体层中具有多个栅电极3的多栅MIS晶体管中，将栅电极3的漏极区5附近和存储电容器部21附近的沟道长度设置为另一尺寸。比栅电极3长。