(12)发明专利申请

(10)申请公布号 CN 111435200 A

(43)申请公布日 2020.07.21

(21)申请号 201910026996.6

(22)申请日 2019.01.11

(71)申请人 惠科股份有限公司

地址 518000 广东省深圳市宝安区石岩街道水田村民营工业园惠科工业园厂房1、2、3栋,九州阳光1号厂房5、7楼

(72)发明人 单剑锋

(74)专利代理机构 深圳中一专利商标事务所

44237

代理人 高星

(51)Int.Cl.

G02F 1/133(2006.01)

G02F 1/1362(2006.01)

G09G 3/36(2006.01)

权利要求书2页 说明书6页 附图7页

(54)发明名称

液晶显示装置、液晶显示面板及其驱动方法

(57)摘要

本申请属于液晶显示技术领域,提供了一种液晶显示装置、液晶显示面板及其驱动方法,该液晶显示面板包括:数据线,配置为传输数据;扫描线,配置为传输扫描信号;以及像素单元,由所述数据线和所述扫描线交错形成,所述像素单元包括第一子像素单元和第二子像素单元;其中,公共电极在所述数据线的延伸方向上延伸有公共电极金属线,所述公共电极金属线设于所述数据线的两侧,所述第一子像素单元的像素电极与所述公共电极金属线的重叠区域形成第一存储电容,所述第二子像素单元的像素电极与所述公共电极金属线的重叠区域形成第二存储电容。

1. 一种液晶显示面板,其特征在于,包括:

数据线,配置为传输数据;

扫描线,配置为传输扫描信号;以及

像素单元,由所述数据线和所述扫描线交错形成,所述像素单元包括第一子像素单元和第二子像素单元;

其中,公共电极在所述数据线的延伸方向上延伸有公共电极金属线,所述公共电极金属线设于所述数据线的两侧,所述第一子像素单元的像素电极与所述公共电极金属线的重叠区域形成第一存储电容,所述第二子像素单元的像素电极与所述公共电极金属线的重叠区域形成第二存储电容。

2. 如权利要求1所述的液晶显示面板,其特征在于,所述第一子像素单元的像素开口为所述公共电极与所述第一子像素单元的像素电极所围成的区域;所述第二子像素单元的像素开口为所述公共电极与所述第二子像素单元的像素电极所围成的区域。

3. 如权利要求1所述的液晶显示面板,其特征在于,所述第一存储电容的大小与所述第二存储电容的大小相同。

4. 如权利要求1所述的液晶显示面板,其特征在于,所述公共电极的充电周期时间大于第一开关管开启的时间和第二开关管开启的时间之和。

5. 一种液晶显示装置,其特征在于,所述液晶显示装置包括:

数据线,配置为传输数据

扫描线,配置为传输扫描信号;以及

像素单元,由所述数据线和所述扫描线交错形成,所述像素单元包括第一子像素单元和第二子像素单元;

其中,公共电极在所述数据线的延伸方向上延伸有公共电极金属线,所述公共电极金属线设于所述数据线的两侧,所述第一子像素单元的像素电极与所述公共电极金属线的重叠区域形成第一存储电容,所述第二子像素单元的像素电极与所述公共电极金属线的重叠区域形成第二存储电容;

扫描驱动单元,配置为输出扫描电压以驱动所述扫描线;

公共电极驱动单元,配置为输出共电极电压以驱动所述公共电极。

6. 如权利要求5所述的液晶显示装置,其特征在于,所述第一子像素单元的像素开口为所述公共电极与所述第一子像素单元的像素电极所围成的区域;所述第二子像素单元的像素开口为所述公共电极与所述第二子像素单元的像素电极所围成的区域。

7. 如权利要求5所述的液晶显示装置,其特征在于,所述第一存储电容的大小与所述第二存储电容的大小相同。

8. 如权利要求5所述的液晶显示装置,其特征在于,所述公共电极的充电周期时间大于第一开关管开启的时间和第二开关管开启的时间之和。

9. 一种基于权利要求1至4任一项所述的液晶显示面板的驱动方法,其特征在于,所述驱动方法包括:

开启第一开关管,对所述公共电极输出充电时序电压,对所述第一子像素单元进行充电;

开启第二开关管,关闭所述第一开关管,对所述公共电极输出充电时序电压,对所述第

二子像素单元进行充电；

关闭所述第一开关管，关闭所述第二开关管；

对所述公共电极输出调节电压。

10. 如权利要求9所述的驱动方法，其特征在于，所述第一开关管的开启时间和所述第二开关管的开启时间相同，所述充电时序电压的输出时间大于或等于所述第一开关管的开启时间和所述第二开关管的开启时间之和。

## 液晶显示装置、液晶显示面板及其驱动方法

### 技术领域

[0001] 本申请属于液晶显示技术领域,尤其涉及一种液晶显示装置、液晶显示面板及其驱动方法。

### 背景技术

[0002] 现行的液晶显示面板的像素设计,由于闸极电极跟源极电极存在寄生电容 $C_{gs}$ ,当像素充电后元件关闭时闸极电压的变化通过寄生电容 $C_{gs}$ 对于像素的液晶电容及储存电容电荷产生再分配作用,使得原像素充电后的电压产生kick back的现象,该现象会使得液晶面板产生闪烁。

[0003] 为了让有像素于TFT关闭时期有足够的储存电容可以维持像素电位,需设计储存电容 $C_{st}$ 储存电荷,维持像素电位。为了让有像素于TFT关闭时期有足够的储存电容可以维持像素电位,当像素在下个充电时间开启前,像素电荷会通过像素上的所有寄生电容漏电,使得像素电位产生压降。需透过设计足够大的储存电容 $C_{st}$ 储存电荷,维持像素电位,我们称为电压维持,而大的储存电容 $C_{st}$ 需要大的共电极金属电极面积,使得有效像素开口率下降。

[0004] 因此,传统的技术方案中存在存储电容大小和有效像素开口率不能兼容的问题。

### 发明内容

[0005] 本申请提供了一种液晶显示装置、液晶显示面板及其驱动方法,以解决传统的技术方案中存在的存储电容大小和有效像素开口率不能兼容的问题。

[0006] 本申请的一个实施例提供了一种液晶显示面板,包括:

[0007] 数据线,配置为传输数据;

[0008] 扫描线,配置为传输扫描信号;以及

[0009] 像素单元,由所述数据线和所述扫描线交错形成,所述像素单元包括第一子像素单元和第二子像素单元;

[0010] 其中,公共电极在所述数据线的延伸方向上延伸有公共电极金属线,所述公共电极金属线设于所述数据线的两侧,所述第一子像素单元的像素电极与所述公共电极金属线的重叠区域形成第一存储电容,所述第二子像素单元的像素电极与所述公共电极金属线的重叠区域形成第二存储电容。

[0011] 在其中一个实施例中,所述第一子像素单元的像素开口为所述公共电极与所述第一子像素单元的像素电极所围成的区域;所述第二子像素单元的像素开口为所述公共电极与所述第二子像素单元的像素电极所围成的区域。

[0012] 在其中一个实施例中,所述第一存储电容的大小与所述第二存储电容的大小相同。

[0013] 在其中一个实施例中,所述公共电极的充电周期时间大于第一开关管开启的时间和第二开关管开启的时间之和。

[0014] 本申请的一个实施例提供了一种液晶显示装置,所述液晶显示装置包括:

[0015] 数据线,配置为传输数据

[0016] 扫描线,配置为传输扫描信号;以及

[0017] 像素单元,由所述数据线和所述扫描线交错形成,所述像素单元包括第一子像素单元和第二子像素单元;

[0018] 其中,公共电极在所述数据线的延伸方向上延伸有公共电极金属线,所述公共电极金属线设于所述数据线的两侧,所述第一子像素单元的像素电极与所述公共电极金属线的重叠区域形成第一存储电容,所述第二子像素单元的像素电极与所述公共电极金属线的重叠区域形成第二存储电容;

[0019] 扫描驱动单元,配置为输出扫描电压以驱动所述扫描线;

[0020] 公共电极驱动单元,配置为输出共电极电压以驱动所述公共电极。

[0021] 在其中一个实施例中,所述第一子像素单元的像素开口为所述公共电极与所述第一子像素单元的像素电极所围成的区域;所述第二子像素单元的像素开口为所述公共电极与所述第二子像素单元的像素电极所围成的区域。

[0022] 在其中一个实施例中,所述第一存储电容的大小与所述第二存储电容的大小相同。

[0023] 在其中一个实施例中,所述公共电极的充电周期时间大于第一开关管开启的时间和第二开关管开启的时间之和。

[0024] 本申请的一个实施例还提供了一种基于上述的液晶显示面板的驱动方法,所述驱动方法包括:

[0025] 开启第一开关管,对所述公共电极输出充电时序电压,对所述第一子像素单元进行充电;

[0026] 开启第二开关管,关闭所述第一开关管,对所述公共电极输出充电时序电压,对所述第二子像素单元进行充电;

[0027] 关闭所述第一开关管,关闭所述第二开关管;

[0028] 对所述公共电极输出调节电压。

[0029] 在其中一个实施例中,所述第一开关管的开启时间和所述第二开关管的开启时间相同,所述充电时序电压的输出时间大于或等于所述第一开关管的开启时间和所述第二开关管的开启时间之和。

[0030] 本申请实施例将像素分为第一子像素单元和第二子像素单元,并且共用电极与像素电极形成储存电容,将像素电极跨到用以形成储存电容的共用的共电极金属上方,在增大储存电容的同时增加像素开口,增大储存电容可以减少kick back的现象形成的闪烁,增加像素开口则增加了液晶显示器的出光量,可以获得节能、节省成本或者高亮度的显示效果。

## 附图说明

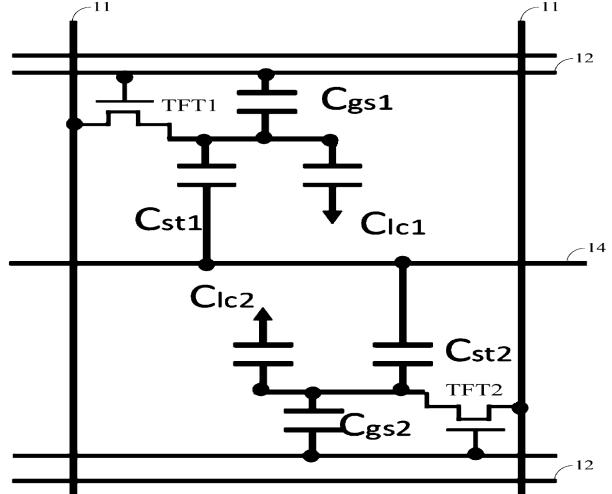

[0031] 图1为本申请实施例提供的液晶显示面板的像素单元结构示意图;

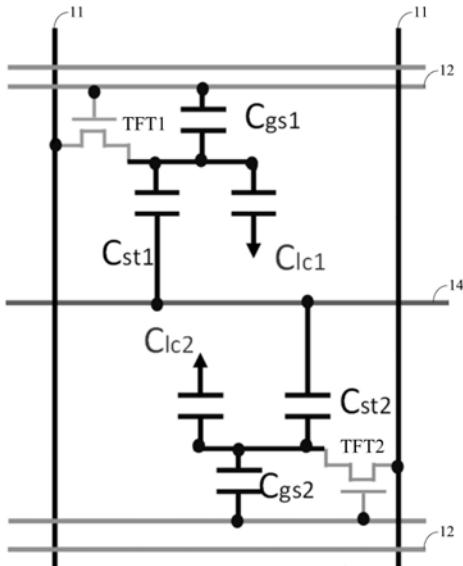

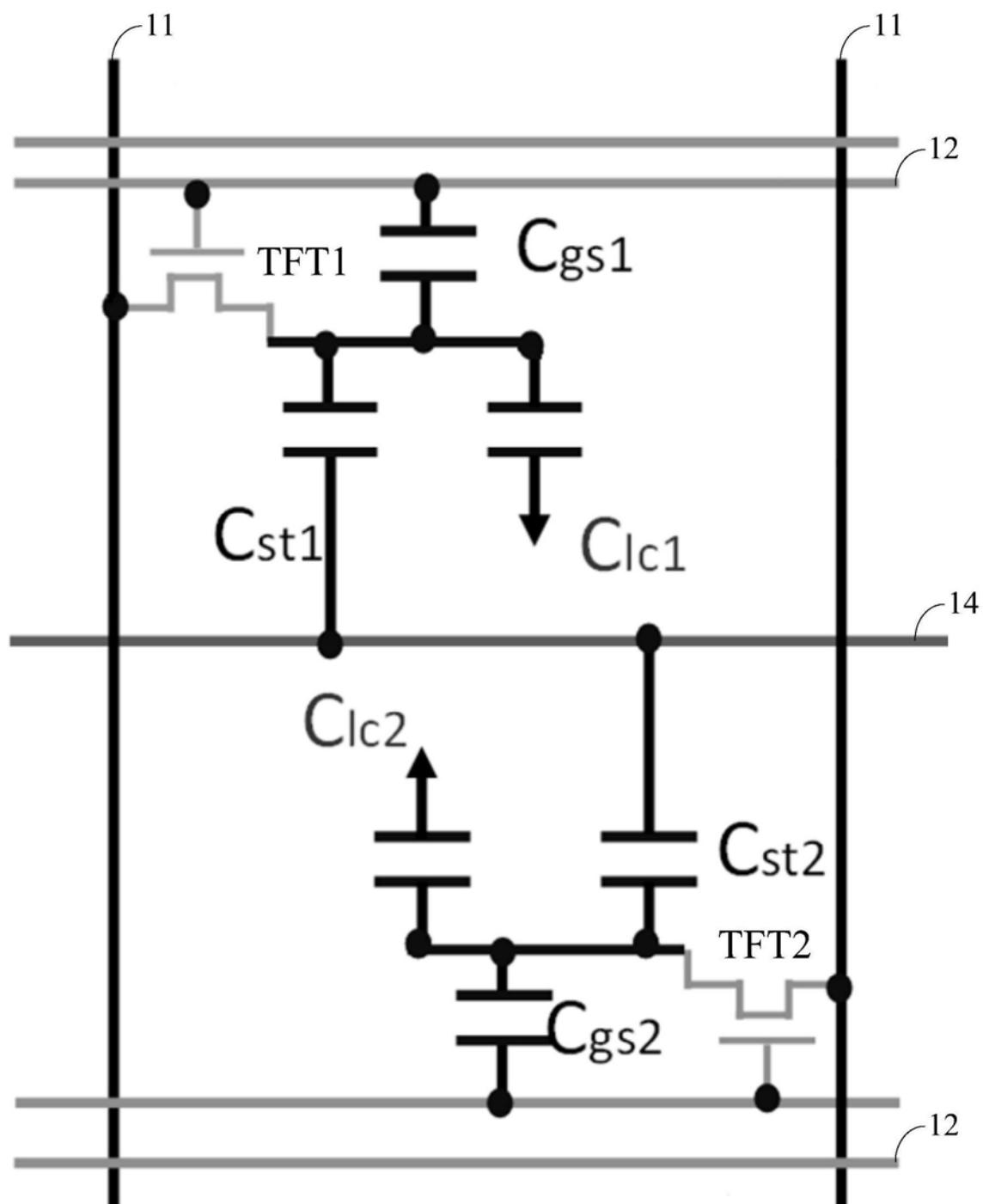

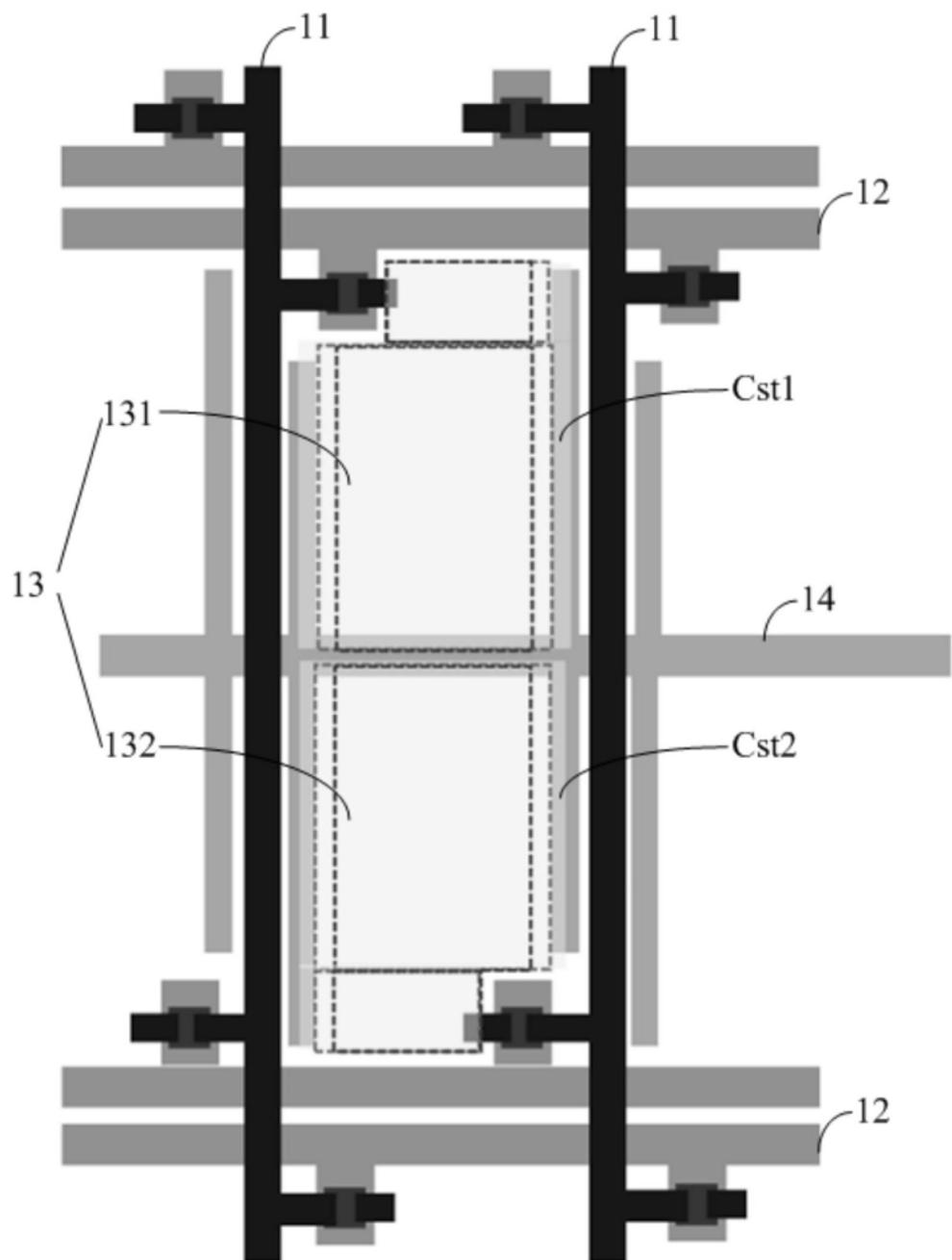

[0032] 图2为本申请实施例提供的液晶显示面板的像素单元具体结构示意图;

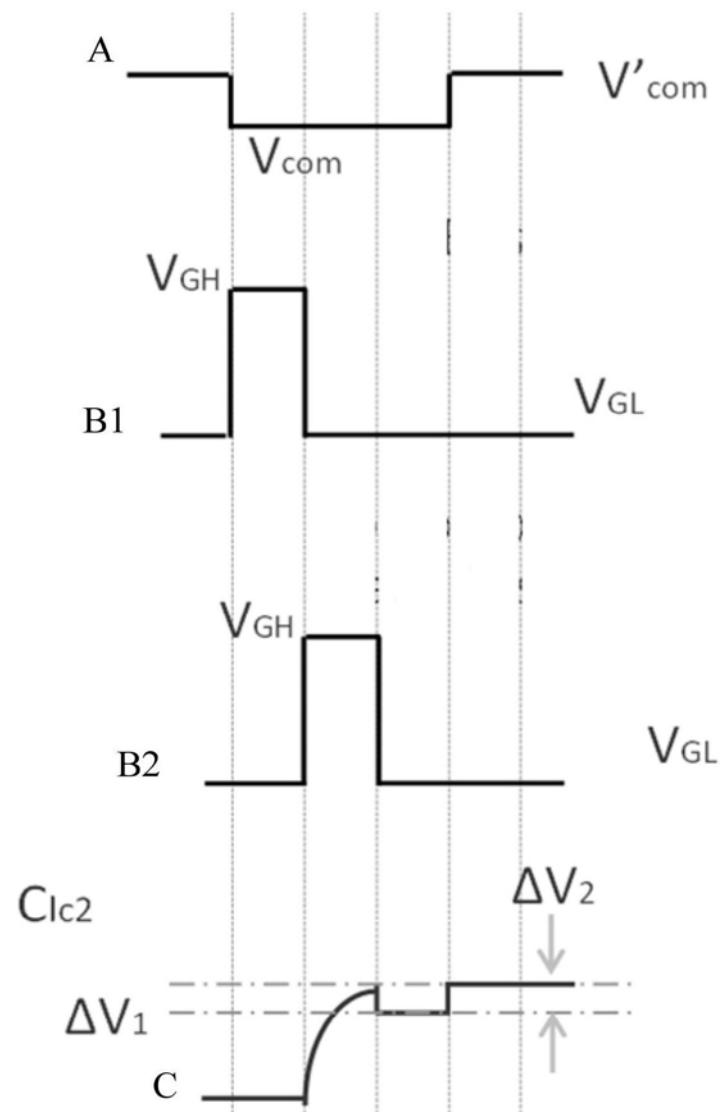

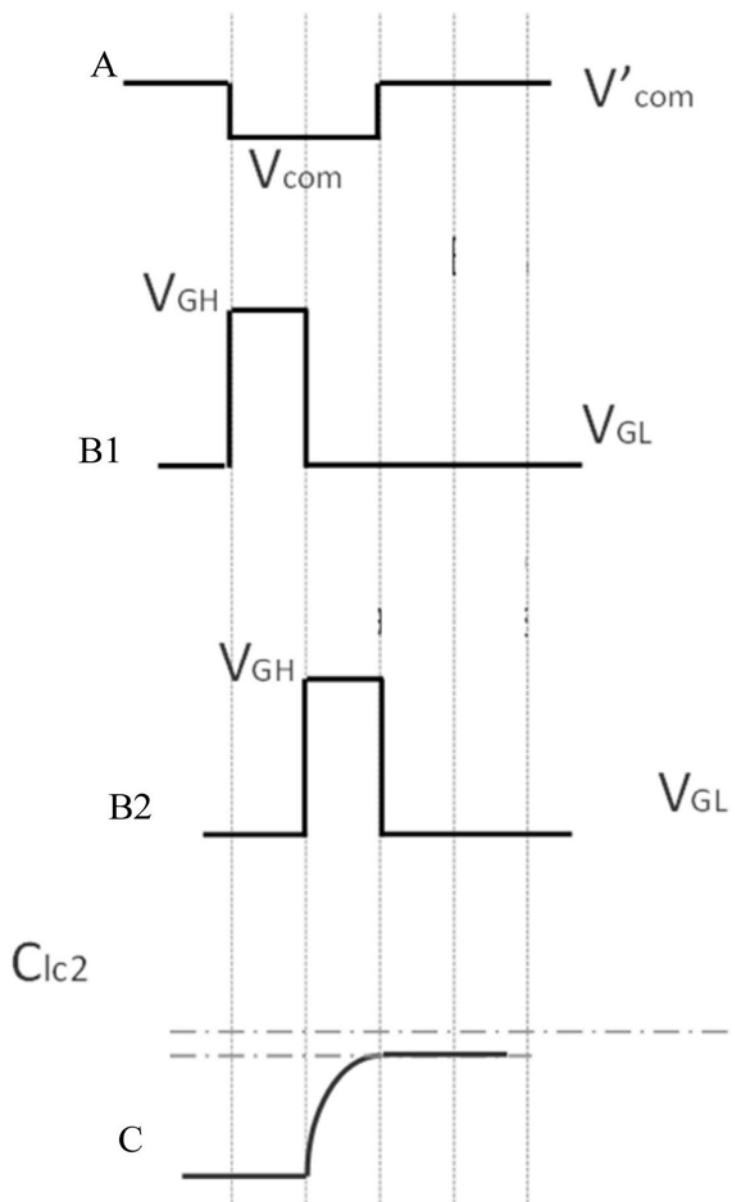

[0033] 图3为本申请第一实施例液晶显示面板的第一子像素单元的像素电极、公共电

极及扫描线的电压信号示意图；

[0034] 图4为本申请第一实施例液晶显示面板的第二子像素单元的像素电极、公共电极及扫描线的电压信号示意图；

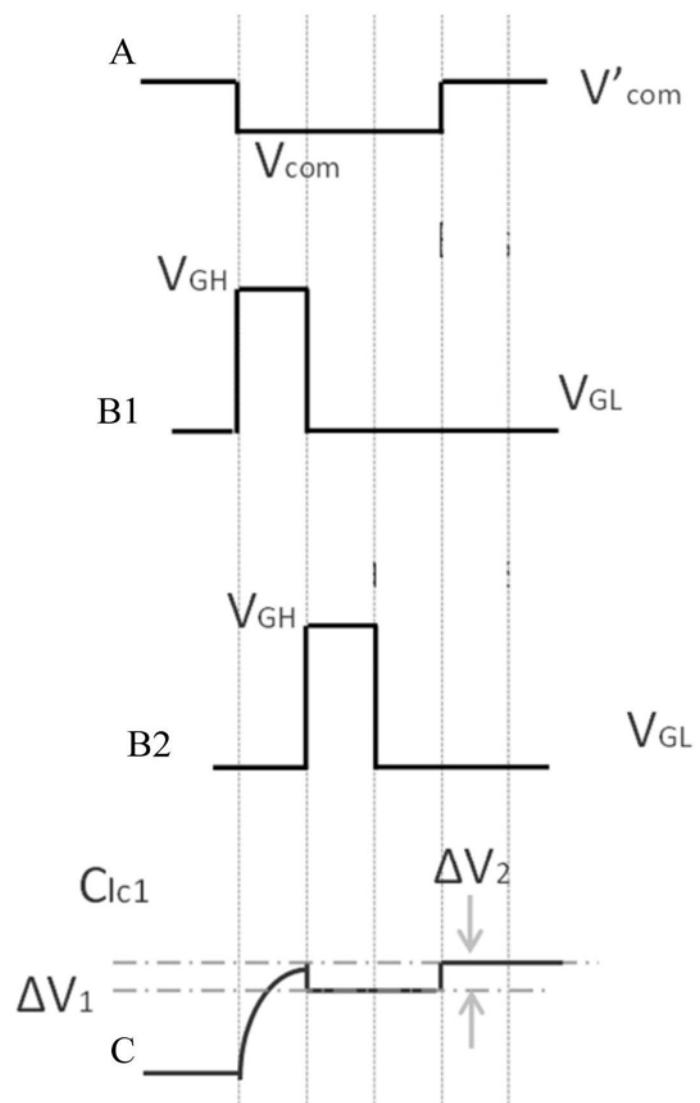

[0035] 图5为本申请第二实施例液晶显示面板的第一子像素单元的像素电极、公共电极及扫描线的电压信号示意图；

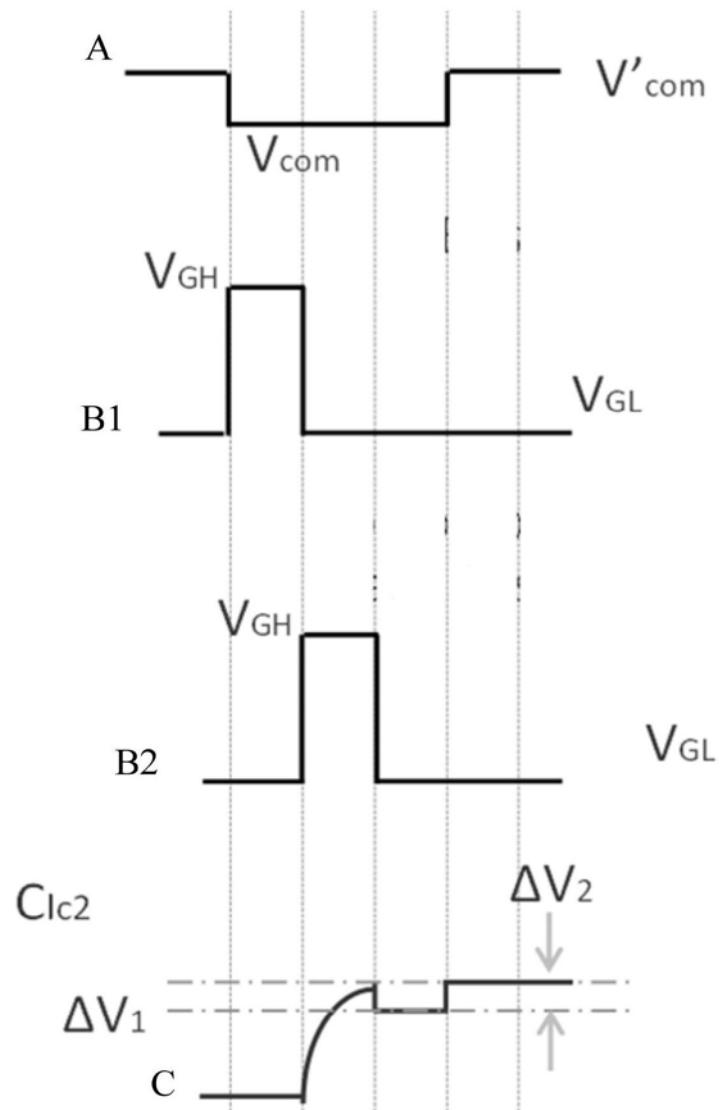

[0036] 图6为本申请第二实施例液晶显示面板的第二子像素单元的像素电极、公共电极及扫描线的电压信号示意图；

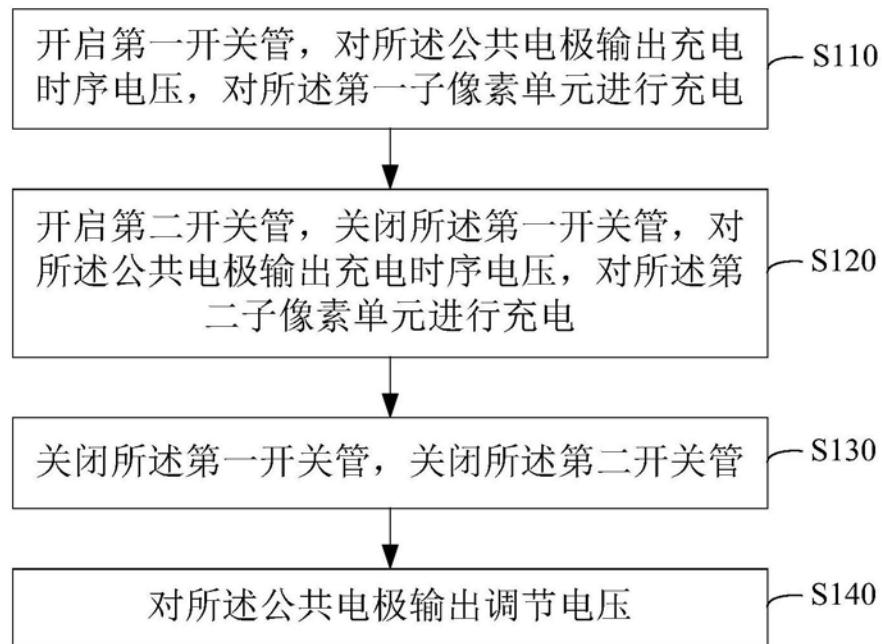

[0037] 图7为申请实施例提供的液晶显示面板的驱动方法的具体流程图。

## 具体实施方式

[0038] 为了使本技术领域的人员更好地理解本申请方案,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚地描述,显然,所描述的实施例是本申请一部分的实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本申请保护的范围。

[0039] 本申请的说明书和权利要求书及上述附图中的术语“包括”以及它们任何变形,意图在于覆盖不排他的包含。例如包含一系列步骤或单元的过程、方法或系统、产品或设备没有限于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元,或可选地还包括对于这些过程、方法、产品或设备固有的其它步骤或单元。此外,术语“第一”、“第二”和“第三”等是用于区别不同对象,而非用于描述特定顺序。

[0040] 如图1所示,本实施例提供一种驱动电路,该液晶显示面板包括数据线11、扫描线12、以及像素单元13。其中,数据线11配置为传输数据,扫描线12配置为传输扫描信号,像素单元13由数据线11和扫描线12交错形成,像素单元13包括第一子像素单元131和第二子像素单元132。

[0041] 第一子像素单元131包括第一液晶电容C1c1、第一存储电容Cst1、第一寄生电容Cgs1和第一开关管TFT1;第一液晶电容C1c1配置为给第一子像素单元131中的液晶分子提供偏转电压,第一存储电容Cst1配置为给第一液晶电容C1c1提供电压维持电荷,第一寄生电容Cgs1形成于所述扫描线12和第一子像素单元131的像素电极之间,第一开关管TFT1配置为给第一液晶电容C1c1以及第一存储电容Cst1提供数据信号。第二子像素单元132包括第二液晶电容C1c2、第二存储电容Cst2、第二寄生电容Cgs2和第二开关管TFT2;第二液晶电容C1c2配置为给第二子像素单元132中的液晶分子提供偏转电压,第二存储电容Cst2配置为给第二液晶电容C1c2提供电压维持电荷,第二寄生电容Cgs2形成于所述扫描线12和第二子像素单元132的像素电极之间,第二开关管TFT2配置为给第二液晶电容C1c2以及第二存储电容Cst2提供数据信号。

[0042] 其中,第一子像素单元131的像素电极与公共电极14形成第一存储电容Cst1,第二子像素单元132的像素电极与公共电极14形成第二存储电容Cst2;公共电极14的金属像素位于数据线11的电极的两侧,第一子像素单元131的像素电极和第二子像素单元132的像素电极位于公共电极14的两侧。

[0043] 如图2所示,图2为本申请实施例提供的显示面板的结构示意图,数据线11和扫描线12呈垂直交错排布设置,公共电极14设置于相邻的扫描线12之间且与扫描线12平行排

布,第一子像素单元131的像素电极设置于相邻的扫描线12和公共电极14之间且与公共电极14的重叠区域形成第一存储电容,第二子像素单元132的像素电极设置于相邻的扫描线12和公共电极14之间且与公共电极14的重叠区域形成第二存储电容。第一子像素单元131的像素开口为公共电极14与第一子像素单元131的像素电极所围成的区域;第二子像素单元132的像素开口为公共电极14与第二子像素单元132的像素电极所围成的区域。

[0044] 为避免数据线11上的讯号电压影响到像素电极上的像素电压,造成串扰而现象影响画质,像素电极需与数据线11一般设计有安全距离,以减少该串扰现象,但该安全距离会导致开口率降低,据此,本申请实施例中公共电极14在数据线11延伸方向上延伸有公共电极金属线,该公共电极金属线设于数据线11的两侧,使电场形成于数据线11与公共电极金属线之间,减少了电场形成于讯号电极与像素电极之间,从而减少或消除像素电极需与数据线11之间的安全距离,增加了开口率。

[0045] 第一开关管TFT1的栅极连接扫描线12,第一开关管TFT1的漏极连接数据线11,第一开关管TFT1的源极连接第一子像素单元131的像素电极,以此形成该第一开关管TFT1;第二开关管TFT2的栅极连接扫描线12,第二开关管TFT2的漏极连接数据线11,第二开关管TFT2的源极连接第二子像素单元132的像素电极,以此形成该第二开关管TFT2。

[0046] 如图7所示,本申请还提供了一种上述液晶显示面板的驱动方法,该驱动方法包括:

[0047] 步骤S110,开启第一开关管TFT1,对公共电极输出充电时序电压,对第一子像素单元131进行充电;

[0048] 步骤S120,开启第二开关管TFT2,关闭第一开关管TFT1,对公共电极输出充电时序电压,对第二子像素单元132进行充电;

[0049] 步骤S130,关闭第一开关管TFT1,关闭第二开关管TFT2;

[0050] 步骤S140,对公共电极输出调节电压。

[0051] 在应用中,第一开关管TFT1和第二开关管TFT2通过通过栅极驱动芯片控制。其中,第一开关管TFT1的开启时间和第二开关管TFT2的开启时间相同,充电时序电压的输出时间大于或等于第一开关管的开启时间和第二开关管的开启时间之和。

[0052] 图3-6为像素电极的充电时序、公共电极14电压驱动时序及闸极电压驱动时序配合说明,公共电极14电压驱动时序由像素正常充电时序公共电极14电压Vcom与高于正常充电时序公共电极14电压Vcom的调节电压V' com构成,扫描线12的电压驱动为元件开启电压VGH与元件关闭电压VGL构成。

[0053] 扫描线12依次输出元件开启电压VGH进行扫描,即第一子像素单元131所对应的扫描线12输出元件开启电压VGH,第一子像素单元131所对应的扫描线12输出元件关闭电压VGL,随之,第二子像素单元132所对应的扫描线12输出元件开启电压VGH,第一子像素单元131所对应的扫描线12输出元件关闭电压VGL。第一子像素单元131所对应的扫描线12输出元件开启电压VGH时,第一开关管TFT1导通,开始对第一液晶电容C1c1、第一存储电容Cst1和第一寄生电容Cgs1进行充电,当第一子像素单元131所对应的扫描线12输出元件关闭电压VGL后,第一开关管TFT1关断,第一液晶电容C1c1、第一存储电容Cst1和第一寄生电容Cgs1充电结束;第二子像素单元132所对应的扫描线12输出元件开启电压VGH时,第二开关管TFT2导通,开始对第二液晶电容C1c2、第二存储电容Cst2和第二寄生电容Cgs2进行充电,

当第二子像素单元132所对应的扫描线12输出元件关闭电压VGL后,第二开关管TFT2关断,第二液晶电容Clc2、第二存储电容Cst2和第二寄生电容Cgs2充电结束。第一开关管TFT1关断后,扫描线12的电压变化通过与扫描线12连接的第一寄生电容Cgs1进行再分配,会导致第一子像素单元131中的像素电极上的像素电压降低,同样,第二开关管TFT2关断后,扫描线12的电压变化通过与扫描线12连接的第二寄生电容Cgs2进行再分配,会导致第二子像素单元132中的像素电极上的像素电压降低。在第一子像素单元131和第二子像素单元132充电的同时,公共电极14输出共电极电压,配合对第一存储电容Cst1和第二存储电容Cst2进行充电,当第一开关管TFT1关断和第二开关管TFT2关断后,公共电极14电压驱动输出调节电压V' com对第一子像素单元131的像素电压和第二子像素单元132的像素电压进行调节,由于调节电压V' com大于共电极电压,调节电压V' com通过第一存储电容Cst1和第二存储电容Cst2分别维持第一子像素单元131的像素电压和第二子像素单元132的像素电压。

[0054] 为保证第一子像素单元131和第二子像素单元132的正常充电,公共电极14的充电周期时间大于第一开关管TFT1开启的时间和第二开关管TFT2开启的时间之和,且正常充电时序共电极电压的周期时间需覆盖第一开关管TFT1开启周期的时间和第二开关管TFT2开启周期的时间。在实际应用中,第一开关管TFT1开启周期的时间和第二开关管TFT2开启周期的时间相同,即公共电极14的充电周期时间为第一开关管TFT1开启周期的时间或第二开关管TFT2开启周期的时间的N倍,其中,N≥2。

[0055] 原则上,存储电容的电容值越大越好,但由于液晶显示面板设计面积等的限制,存储电容的大小也受到限制。

[0056] 在一实施例中,当N=2时,第一存储电容Cst1的大小应满足以下要求:

$$V_{pixel} = V_{data}$$

$$\Delta V1 = (V_{GH} - V_{GL}) * C_{gs1} / (C_{gs1} + C_{st1} + C_{lc1})$$

$$\Delta V2 = (V_{com} - V'_{com}) * C_{st1} / (C_{gs1} + C_{st1} + C_{lc1})$$

$$\text{需满足 } \Delta V1 + \Delta V2 = 0$$

$$C_{st1} = (V_{GH} - V_{GL}) * C_{gs1} / (V'_{com} - V_{com})$$

[0062] 其中,V<sub>pixel</sub>为第一子像素单元131中像素电极的电压值,V<sub>data</sub>为数据线11的电压值,Clc1、Cst1、Cgs1分别为第一液晶电容Clc1、第一存储电容Cst1和第一寄生电容Cgs1的电容值,ΔV1为第一子像素单元131中像素电极的压降,ΔV2第一子像素单元131中像素电极的回调电压差。

[0063] 同样,第二存储电容Cst2的大小应满足以下要求:

$$V_{pixel} = V_{data}$$

$$\Delta V1 = \Delta V'1 + \Delta V''1$$

$$\Delta V'1 = (V_{GH} - V_{GL}) * C_{gs2} / (C_{gs2} + C_{st2} + C_{lc2})$$

$$\Delta V''1 = (V'_{com} - V_{com}) * C_{st2} / (C_{gs2} + C_{st2} + C_{lc2})$$

$$\text{需满足 } \Delta V1 = 0$$

$$C_{st2} = (V_{GH} - V_{GL}) * C_{gs2} / (V'_{com} - V_{com})$$

[0070] 其中,V<sub>pixel</sub>为第二子像素单元132中像素电极的电压值,V<sub>data</sub>为数据线11的电压值,Clc2、Cst2、Cgs2分别为第二液晶电容Clc2、第二存储电容Cst2和第二寄生电容Cgs2的电容值,ΔV'1为第二子像素单元132中像素电极的预估压降,ΔV''1第二子像素单元132

中像素电极的预估回调电压差。

[0071] 在另一实施例中,当N=3时,第一存储电容Cst1的大小应满足以下要求:

[0072]  $V_{pixel} = V_{data}$

[0073]  $\Delta V1 = (V_{GH} - V_{GL}) * C_{gs1} / (C_{gs1} + C_{st1} + C_{lc1})$

[0074]  $\Delta V2 = (V_{com} - V'_{com}) * C_{st1} / (C_{gs1} + C_{st1} + C_{lc1})$

[0075] 需满足  $\Delta V1 + \Delta V2 = 0$

[0076]  $C_{st1} = (V_{GH} - V_{GL}) * C_{gs1} / (V'_{com} - V_{com})$

[0077] 其中,  $V_{pixel}$  为第一子像素单元131中像素电极的电压值,  $V_{data}$  为数据线11的电压值,  $C_{lc1}$ 、 $C_{st1}$ 、 $C_{gs1}$  分别为第一液晶电容  $C_{lc1}$ 、第一存储电容  $C_{st1}$  和第一寄生电容  $C_{gs1}$  的电容值,  $\Delta V1$  为第一子像素单元131中像素电极的压降,  $\Delta V2$  第一子像素单元131中像素电极的回调电压差。

[0078] 同样,第二存储电容Cst2的大小应满足以下要求:

[0079]  $V_{pixel} = V_{data}$

[0080]  $\Delta V1 = (V_{GH} - V_{GL}) * C_{gs2} / (C_{gs2} + C_{st2} + C_{lc2})$

[0081]  $\Delta V2 = (V_{com} - V'_{com}) * C_{st2} / (C_{gs2} + C_{st2} + C_{lc2})$

[0082] 需满足  $\Delta V1 + \Delta V2 = 0$

[0083]  $C_{st2} = (V_{GH} - V_{GL}) * C_{gs2} / (V'_{com} - V_{com})$

[0084] 其中,  $V_{pixel}$  为第二子像素单元132中像素电极的电压值,  $V_{data}$  为数据线11的电压值,  $C_{lc2}$ 、 $C_{st2}$ 、 $C_{gs2}$  分别为第二液晶电容  $C_{lc2}$ 、第二存储电容  $C_{st2}$  和第二寄生电容  $C_{gs2}$  的电容值,  $\Delta V1$  为第二子像素单元132中像素电极的预估压降,  $\Delta V2$  第二子像素单元132中像素电极的预估回调电压差。

[0085] 以上所述实施例仅用以说明本申请的技术方案,而非对其限制;尽管参照前述实施例对本申请进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例技术方案的精神和范围,均应包含在本申请的保护范围之内。

图1

图2

图3

图4

图5

图6

图7

|                |                               |         |            |

|----------------|-------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置、液晶显示面板及其驱动方法           |         |            |

| 公开(公告)号        | <a href="#">CN111435200A</a>  | 公开(公告)日 | 2020-07-21 |

| 申请号            | CN201910026996.6              | 申请日     | 2019-01-11 |

| [标]申请(专利权)人(译) | 惠科股份有限公司                      |         |            |

| 申请(专利权)人(译)    | 惠科股份有限公司                      |         |            |

| 当前申请(专利权)人(译)  | 惠科股份有限公司                      |         |            |

| [标]发明人         | 单剑锋                           |         |            |

| 发明人            | 单剑锋                           |         |            |

| IPC分类号         | G02F1/133 G02F1/1362 G09G3/36 |         |            |

| 代理人(译)         | 高星                            |         |            |

| 外部链接           | <a href="#">SIP0</a>          |         |            |

## 摘要(译)

本申请属于液晶显示技术领域，提供了一种液晶显示装置、液晶显示面板及其驱动方法，该液晶显示面板包括：数据线，配置为传输数据；扫描线，配置为传输扫描信号；以及像素单元，由所述数据线和所述扫描线交错形成，所述像素单元包括第一子像素单元和第二子像素单元；其中，公共电极在所述数据线的延伸方向上延伸有公共电极金属线，所述公共电极金属线设于所述数据线的两侧，所述第一子像素单元的像素电极与所述公共电极金属线的重叠区域形成第一存储电容，所述第二子像素单元的像素电极与所述公共电极金属线的重叠区域形成第二存储电容。