(12)发明专利申请

(10)申请公布号 CN 111341282 A

(43)申请公布日 2020.06.26

(21)申请号 202010311206.1

(22)申请日 2020.04.20

(30)优先权数据

108138304 2019.10.23 TW

(71)申请人 友达光电股份有限公司

地址 中国台湾新竹市

(72)发明人 柯健专 蔡孟杰

(74)专利代理机构 隆天知识产权代理有限公司

72003

代理人 傅磊 黄艳

(51)Int.Cl.

G09G 3/36(2006.01)

权利要求书1页 说明书4页 附图2页

(54)发明名称

像素电路

(57)摘要

一种像素电路，具有数据晶体管、第一P型晶体管、第一N型晶体管、液晶电容、第二P型晶体管及第二N型晶体管。数据晶体管具有接收数据电压及栅极信号且耦接第一节点。第一P型晶体管及第一N型晶体管串联耦接于第一脉冲信号与第二脉冲信号之间，并且共同耦接第一节点及第二节点。液晶电容，耦接于第二节点与共同电压信号之间。第二P型晶体管及第二N型晶体管串联耦接于第一脉冲信号与第二脉冲信号之间，并且共同耦接第一节点及第二节点。

1. 一种像素电路,包括:

一数据晶体管,具有接收一数据电压的第一端、耦接第一节点的第二端及接收一栅极信号的控制端;

一第一P型晶体管,具有接收一第一脉冲信号的第一端、耦接第二节点的第二端及耦接该第一节点的控制端;

一第一N型晶体管,具有耦接该第二节点的第一端、接收一第二脉冲信号的第二端及耦接该第一节点的控制端;

一液晶电容,耦接于该第二节点与一共同电压信号之间;

一第二P型晶体管,具有接收该第一脉冲信号的第一端、耦接该第一节点的第二端及耦接该第二节点的控制端;以及

一第二N型晶体管,具有耦接该第一节点的第一端、接收该第二脉冲信号的第二端及耦接该第二节点的控制端。

2. 如权利要求1所述的像素电路,其中该共同电压信号相同于该第一脉冲信号及该第二脉冲信号的其中之一。

3. 如权利要求1所述的像素电路,其中该第一脉冲信号及该第二脉冲信号互为反相。

4. 如权利要求1所述的像素电路,其中该第一P型晶体管的导通临界电压不同于该第二P型晶体管的导通临界电压,该第一N型晶体管的导通临界电压不同于该第二N型晶体管的导通临界电压。

5. 如权利要求4所述的像素电路,其中该第一P型晶体管的导通临界电压小于该第二P型晶体管的导通临界电压,该第一N型晶体管的导通临界电压小于该第二N型晶体管的导通临界电压。

6. 如权利要求1所述的像素电路,其中该第一P型晶体管的尺寸不同于该第二P型晶体管的尺寸,该第一N型晶体管的尺寸不同于该第二N型晶体管的尺寸。

7. 如权利要求6所述的像素电路,其中该第一P型晶体管的尺寸大于该第二P型晶体管的尺寸,该第一N型晶体管的尺寸大于该第二N型晶体管的尺寸。

8. 如权利要求1所述的像素电路,其中该数据晶体管、该第一P型晶体管、该第一N型晶体管、该第二P型晶体管及该第二N型晶体管分别为一低温多晶硅晶体管。

9. 如权利要求1所述的像素电路,其中形成该液晶电容的液晶层操作于一常黑显示模式或一常白显示模式。

10. 如权利要求1所述的像素电路,其中该像素电路由该第一节点、该第二节点、该数据晶体管、该第一P型晶体管、该第一N型晶体管、该液晶电容、该第二P型晶体管及该第二N型晶体管所构成。

## 像素电路

### 技术领域

[0001] 本发明涉及一种像素电路,且特别涉及一种液晶像素电路。

### 背景技术

[0002] 像素内存储器(Memory in Pixel,MIP)技术,为一种高阶显示器技术,其主要目的之一在于降低面板的耗电量,其技术效果有点类似电泳显示器(EPD)的双稳态(Bistability),亦即在画面不变换、或仅少部分变换的情况下,可达到极低或最低耗电的表现。不过MIP像素是通过像素本身内的存储单元,减少电压变换时的耗能,并且液晶是通过极性反转来驱动,因此像素需要根据驱动要求作电路设计。

### 发明内容

[0003] 本发明提供一种像素电路,在没有反相器电路的情况下,仍可以极性反转的方式维持着液晶两端的电压,因此可在没有进行数据写入的时候,维持像素电路的正常操作。

[0004] 本发明的像素电路,包括数据晶体管、第一P型晶体管、第一N型晶体管、液晶电容、第二P型晶体管及第二N型晶体管。数据晶体管具有接收数据电压的第一端、耦接第一节点的第二端及接收栅极信号的一控制端。第一P型晶体管具有接收第一脉冲信号的第一端、耦接第二节点的第二端及耦接第一节点的控制端。第一N型晶体管,具有耦接第二节点的第一端、接收第二脉冲信号的第二端及耦接第一节点的控制端。液晶电容,耦接于第二节点与共同电压信号之间。第二P型晶体管具有接收第一脉冲信号的第一端、耦接第一节点的第二端及耦接第二节点的控制端。第二N型晶体管,具有耦接第一节点的第一端、接收第二脉冲信号的第二端及耦接第二节点的控制端。

[0005] 基于上述,本发明实施例的像素电路,其通过第二P型晶体管及第二N型晶体管交替地传送第一脉冲信号及第二脉冲信号到第一节点,以维持第一节点的电压。因此,即使没有进行数据写入,第一节点的逻辑电平仍会维持,进而维持像素电路所显示的颜色。再者,当像素电路是由第一节点、第二节点、数据晶体管、第一P型晶体管、第一N型晶体管、液晶电容、第二P型晶体管及第二N型晶体管所构成时,可以减少像素电路的电路面积,以应用于单位面积更高的每英寸像素(Pixels Per Inch,PPI)的显示面板。

[0006] 为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合说明书附图作详细说明如下。

### 附图说明

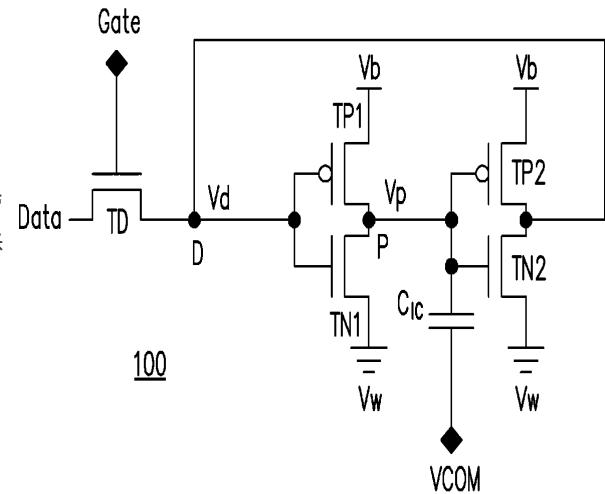

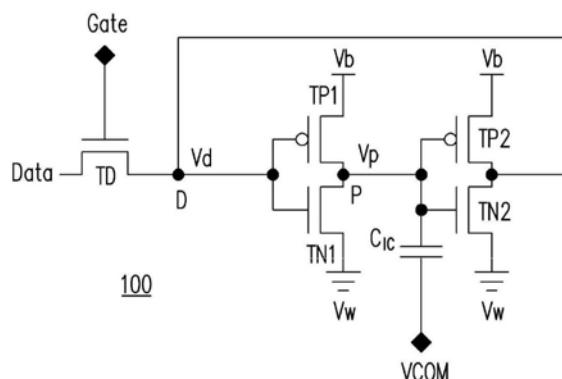

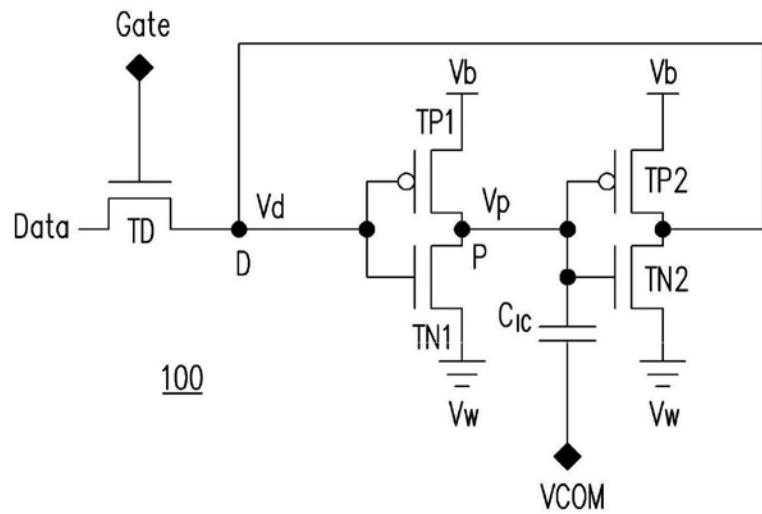

[0007] 图1为依据本发明一实施例的像素电路的电路示意图。

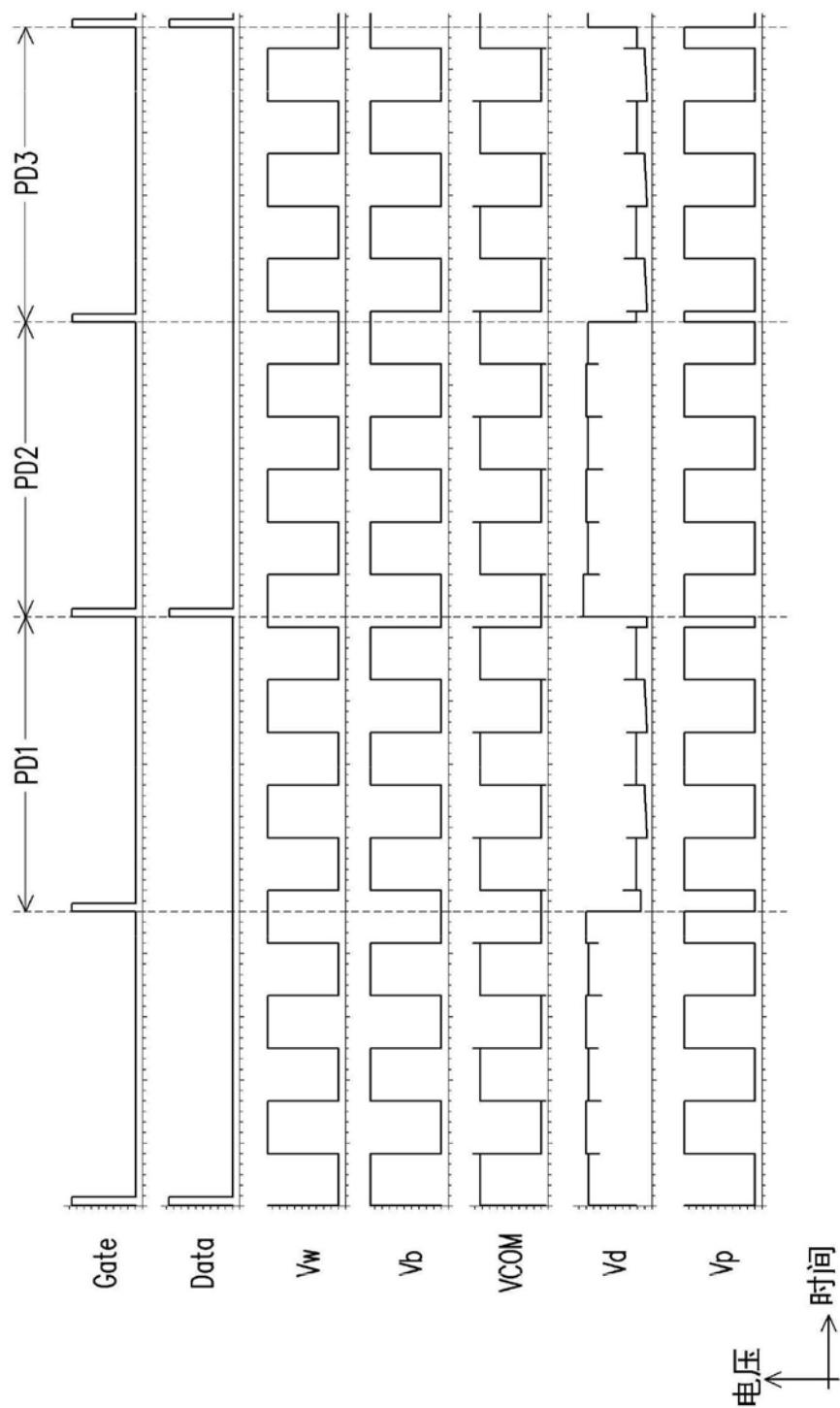

[0008] 图2是依据本发明一实施例的像素电路的驱动波形示意图。

[0009] 附图标记说明:

[0010] 100:像素电路

[0011] C<sub>1c</sub>:液晶电容

- [0012] D:第一节点

- [0013] Data:数据电压

- [0014] DP1~DP3:显示期间

- [0015] Gate:栅极信号

- [0016] P:第二节点

- [0017] TD:数据晶体管

- [0018] TN1:第一N型晶体管

- [0019] TN2:第二N型晶体管

- [0020] TP1:第一P型晶体管

- [0021] TP2:第二P型晶体管

- [0022] Vb:第一脉冲信号

- [0023] VCOM:共同电压信号

- [0024] Vd、Vp:电压

- [0025] Vw:第二脉冲信号

### 具体实施方式

[0026] 除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

[0027] 应当理解,尽管术语“第一”、“第二”、“第三”等在本文中可以用于描述各种元件、部件、区域、层及/或部分,但是这些元件、部件、区域、及/或部分不应受这些术语的限制。这些术语仅用于将一个元件、部件、区域、层或部分与另一个元件、部件、区域、层或部分区分开。因此,下面讨论的“第一元件”、“部件”、“区域”、“层”或“部分”可以被称为第二元件、部件、区域、层或部分而不脱离本文的教导。

[0028] 这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所使用的,除非内容清楚地指示,否则单数形式“一”、“一个”和“该”旨在包括多个形式,包括“至少一个”。“或”表示“及/或”。如本文所使用的,术语“及/或”包括一个或多个相关所列项目的任何和所有组合。还应当理解,当在本说明书中使用时,术语“包括”及/或“包括”指定所述特征、区域、整体、步骤、操作、元件的存在及/或部件,但不排除一个或多个其它特征、区域整体、步骤、操作、元件、部件及/或其组合的存在或添加。

[0029] 图1为依据本发明一实施例的像素电路的电路示意图。请参照图1,在本实施例中,像素电路100包括第一节点D、第二节点P、数据晶体管TD、第一P型晶体管TP1、第一N型晶体管TN1、液晶电容C<sub>1c</sub>、第二P型晶体管TP2及第二N型晶体管TN2。其中,数据晶体管TD、第一P型晶体管TP1、第一N型晶体管TN1、第二P型晶体管TP2及第二N型晶体管TN2可以分别为低温多晶硅(LTPS)晶体管。在本发明的一实施例中,像素电路100可以由第一节点D、第二节点P、数据晶体管TD、第一P型晶体管TP1、第一N型晶体管TN1、液晶电容C<sub>1c</sub>、第二P型晶体管TP2及第二N型晶体管TN2所构成。

[0030] 数据晶体管TD具有接收数据电压Data的第一端、耦接第一节点D的第二端及接收

栅极信号Gate的控制端。第一P型晶体管TP1具有接收第一脉冲信号Vb的第一端、耦接第二节点P的第二端及耦接第一节点D的控制端。第一N型晶体管TN1具有耦接第二节点P的第一端、接收第二脉冲信号Vw的第二端及耦接第一节点D的控制端。其中，第一脉冲信号Vb及第二脉冲信号Vw互为反相。

[0031] 液晶电容C<sub>1c</sub>耦接于第二节点P与共同电压信号VCOM之间，其中形成液晶电容C<sub>1c</sub>的液晶层的液晶材料可操作于常黑显示模式 (normally black mode) 或常白显示模式 (normally white mode)，并且共同电压信号VCOM相当于第一脉冲信号Vb及第二脉冲信号Vw的其中之一。第二P型晶体管TP2具有接收第一脉冲信号Vb的第一端、耦接第一节点D的第二端及耦接第二节点P的控制端。第二N型晶体管TN2具有耦接第一节点D的第一端、接收第二脉冲信号Vw的第二端及耦接第二节点P的控制端。

[0032] 在本发明的实施例中，第一P型晶体管TP1的导通临界电压可以不同于第二P型晶体管TP2的导通临界电压，并且第一N型晶体管TN1的导通临界电压可以不同于第二N型晶体管TN2的导通临界电压。例如，第一P型晶体管TP1的导通临界电压可以小于第二P型晶体管TP2的导通临界电压，并且第一N型晶体管TN1的导通临界电压可以小于第二N型晶体管TN2的导通临界电压。

[0033] 在本发明的实施例中，第一P型晶体管TP1的尺寸可以不同于第二P型晶体管TP2的尺寸，并且第一N型晶体管TN1的尺寸可以不同于第二N型晶体管TN2的尺寸。例如，第一P型晶体管TP1的尺寸可以大于第二P型晶体管TP2的尺寸，并且第一N型晶体管TN1的尺寸可以大于第二N型晶体管TN2的尺寸。

[0034] 当第一P型晶体管TP1的导通临界电压小于第二P型晶体管TP2的导通临界电压且第一N型晶体管TN1的导通临界电压小于第二N型晶体管TN2的导通临界电压时，第一P型晶体管TP1及第一N型晶体管TN1可快速地反应第一节点D的电压Vd的改变，以快速地改变第二节点P的电压Vp。

[0035] 当第一P型晶体管TP1的尺寸大于第二P型晶体管TP2的尺寸且第一N型晶体管TN1的尺寸大于第二N型晶体管TN2的尺寸时，第一P型晶体管TP1及第一N型晶体管TN1可通过较高的电流快速地改变第二节点P的电压Vp。

[0036] 图2是依据本发明一实施例的像素电路的驱动波形示意图。请参照图1及图2，其中显示期间DP1～DP3的时间长度可彼此相同或不同，并且显示期间DP1～DP3的每一个至少包含一个画面 (frame) 期间，亦即像素电路100可以多个画面期间中仅更新 (或数据写入) 一次。在本实施例中，形成液晶电容C<sub>1c</sub>的液晶层的液晶材料例如是操作于常黑显示模式 (normally black mode)，共同电压信号VCOM例如相当于第一脉冲信号Vb。

[0037] 以显示期间PD1为例，栅极信号Gate致能时数据电压Data为低电压电平，亦即第一节点D的电压Vd被设置成 (或写入) 低电压电平。此时，第一P型晶体管TP1导通，第一N型晶体管TN1截止，以致于第二节点P的电压Vp会相当于第一脉冲信号Vb。由于共同电压信号VCOM相当于第一脉冲信号Vb，因此液晶电容C<sub>1c</sub>的两端不存在压差，亦即液晶层中的液晶没有扭转，因此像素电路100呈现黑色 (或较暗色)。

[0038] 并且，当第一脉冲信号Vb为高电压电平时，第二P型晶体管TP2截止，第二N型晶体管TN2导通，而为低电压电平的第二脉冲信号Vw被传送到第一节点D，以致于第一节点D的电压Vd持续设置成低电压电平；当第一脉冲信号Vb为低电压电平时，第二P型晶体管TP2导通，

第二N型晶体管TN2截止，而为低电压电平的第一脉冲信号Vb被传送到第一节点D，以致于第一节点D的电压Vd仍被设置成低电压电平。

[0039] 以显示期间PD2为例，栅极信号Gate致能时数据电压Data为高电压电平，亦即第一节点D的电压Vd被设置成(或写入)高电压电平。此时，第一P型晶体管TP1截止，第一N型晶体管TN1导通，以致于第二节点P的电压Vp会相同于第二脉冲信号Vw。由于共同电压信号VCOM是相同于第一脉冲信号Vb，因此液晶电容C<sub>1c</sub>的两端会存在压差，亦即液晶层中的液晶会被扭转，因此像素电路100呈现白色(或较亮色)。

[0040] 并且，当第二脉冲信号Vw为高电压电平时，第二P型晶体管TP2截止，第二N型晶体管TN2导通，而为高电压电平的第二脉冲信号Vw被传送到第一节点D，以致于第一节点D的电压Vd持续设置成高电压电平；当第二脉冲信号Vw为低电压电平时，第二P型晶体管TP2导通，第二N型晶体管TN2截止，而为高电压电平的第一脉冲信号Vb被传送到第一节点D，以致于第一节点D的电压Vd仍被设置成高电压电平。此外，显示期间PD3的动作相同于显示期间DP1，在此则不再赘述。

[0041] 综上所述，本发明实施例的像素电路，其通过第二P型晶体管及第二N型晶体管交替地传送第一脉冲信号及第二脉冲信号到第一节点，以维持第一节点的电压。因此，即使没有进行数据写入，第一节点的逻辑电平仍会维持，进而维持像素电路所显示的颜色。再者，当像素电路是由第一节点、第二节点、数据晶体管、第一P型晶体管、第一N型晶体管、液晶电容、第二P型晶体管及第二N型晶体管所构成时，可以减少像素电路的电路面积，以应用于单位面积分辨率更高的每英寸像素(Pixels Per Inch,PPI)的显示面板。

[0042] 虽然本发明已以实施例公开如上，然其并非用以限定本发明，任何所属技术领域中技术人员，在不脱离本发明的构思和范围内，当可作些许的变动与润饰，故本发明的保护范围当视权利要求所界定者为准。

图1

图2

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路                                           |         |            |

| 公开(公告)号        | <a href="#">CN111341282A</a>                   | 公开(公告)日 | 2020-06-26 |

| 申请号            | CN202010311206.1                               | 申请日     | 2020-04-20 |

| [标]申请(专利权)人(译) | 友达光电股份有限公司                                     |         |            |

| 申请(专利权)人(译)    | 友达光电股份有限公司                                     |         |            |

| 当前申请(专利权)人(译)  | 友达光电股份有限公司                                     |         |            |

| [标]发明人         | 柯健专<br>蔡孟杰                                     |         |            |

| 发明人            | 柯健专<br>蔡孟杰                                     |         |            |

| IPC分类号         | G09G3/36                                       |         |            |

| 代理人(译)         | 傅磊<br>黄艳                                       |         |            |

| 优先权            | 108138304 2019-10-23 TW                        |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a> |         |            |

## 摘要(译)

一种像素电路，具有数据晶体管、第一P型晶体管、第一N型晶体管、液晶电容、第二P型晶体管及第二N型晶体管。数据晶体管具有接收数据电压及栅极信号且耦接第一节点。第一P型晶体管及第一N型晶体管串联耦接于第一脉冲信号与第二脉冲信号之间，并且共同耦接第一节点及第二节点。液晶电容，耦接于第二节点与共同电压信号之间。第二P型晶体管及第二N型晶体管串联耦接于第一脉冲信号与第二脉冲信号之间，并且共同耦接第一节点及第二节点。