(12)发明专利申请

(10)申请公布号 CN 111312181 A

(43)申请公布日 2020.06.19

---

(21)申请号 201811521101.8

(22)申请日 2018.12.12

(71)申请人 咸阳彩虹光电科技有限公司

地址 712000 陕西省咸阳市秦都区高科一路一号

(72)发明人 刘子涵 王柏钧

(74)专利代理机构 西安嘉思特知识产权代理事务所(普通合伙) 61230

代理人 张捷

(51)Int.Cl.

G09G 3/36(2006.01)

---

权利要求书1页 说明书9页 附图2页

(54)发明名称

一种像素矩阵驱动装置、液晶显示器及像素矩阵驱动方法

(57)摘要

本发明公开了一种像素矩阵驱动装置，包括：时序控制器，用于接收第一极性数字信号，并将第一极性数字信号对应的极性位置进行位置重排，获得第二极性数字信号；源极驱动电路，用于对第二极性数字信号进行极性转换和位置恢复，获得第一极性转换信号。本发明实施例通过时序控制器实现对第一极性数字信号的位置重排，以得到第二极性数字信号，并通过源极驱动电路对进行位置重排后的第二极性数字信号进行极性转换和位置恢复，使得输出的第一极性转换信号输出至显示面板的对应位置，使得该像素矩阵驱动装置不仅适用于传统的极性反转方式，还适用于交错式极性反转方式，进而减少了显示面板的水平等距横纹的现象，还能够降低驱动芯片工作时的温度。

A

CN 111312181 A

CN

1. 一种像素矩阵驱动装置,其特征在于,包括:

时序控制器,用于接收第一极性数字信号,并将所述第一极性数字信号对应的极性位置进行位置重排,获得第二极性数字信号;

源极驱动电路,用于对所述第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号。

2. 根据权利要求1所述的驱动装置,其特征在于,所述时序控制器包括若干储存单元,每个储存单元包括N个储存器,且所述第一极性数字信号包括若干个子极性数字信号,每个所述储存器用于根据预设规则接收1个子极性数字信号。

3. 根据权利要求2所述的驱动装置,其特征在于,所述源极驱动电路包括:

极性转换单元,用于对所述第二极性数字信号进行极性转换,获得第二极性转换信号;

开关恢复单元,用于根据所述第一极性数字信号的位置,对所述第二极性转换信号进行位置恢复,获得第一极性转换信号。

4. 根据权利要求3所述的驱动装置,其特征在于,所述极性转换单元包括N个极性转换模块,所述极性转换模块包括正极性转换模块和负极性转换模块;其中,当第X级所述极性转换模块为正极性转换模块时,则第X+1级所述极性转换模块为负极性转换模块,其中,N、X均为正整数,且 $1 \leq X \leq N$ 。

5. 根据权利要求4所述的驱动装置,其特征在于,开关恢复单元包括N个开关恢复模块,所述第二极性转换信号包括若干个子极性转换信号,所述开关恢复模块用于根据所述第一极性数字信号的位置,对所述子极性转换信号进行位置恢复。

6. 根据权利要求5所述的驱动装置,其特征在于,第X级所述开关恢复模块包括若干开关,所述开关的输入端连接第X级所述极性转换模块,所述开关的输出端用于控制不同的第一极性数字信号的极性。

7. 根据权利要求5所述的驱动装置,其特征在于,所述源极驱动电路还包括数据锁存单元和电平转换单元,所述数据锁存单元包括N个数据锁存器,所述电平转换单元包括N个电平转换器,第X级所述数据锁存器和第X级所述电平转换器依次连接于第X级所述储存器和第X级所述极性转换模块之间。

8. 根据权利要求5所述的驱动装置,其特征在于,所述源极驱动电路还包括输出缓存单元,所述输出缓存单元包括N个输出缓存器,第X级所述输出缓存器连接于第X级所述极性转换模块和第X级所述开关恢复模块之间。

9. 一种像素矩阵驱动方法,其特征在于,包括:

接收第一极性数字信号,并将所述第一极性数字信号对应的极性位置进行位置重排,获得第二极性数字信号;

对所述第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号。

10. 一种液晶显示器,其特征在于,包括权利要求1至权利要求9任一项所述的像素矩阵驱动装置。

## 一种像素矩阵驱动装置、液晶显示器及像素矩阵驱动方法

### 技术领域

[0001] 本发明属于显示领域,具体涉及一种像素矩阵驱动装置、液晶显示器及像素矩阵驱动方法。

### 背景技术

[0002] 随着显示技术的发展,液晶显示器(Liquid Crystal Display,简称LCD)由于具有轻、薄及低辐射等优点,逐渐取代阴极射线管(Cathode Ray Tube,简称CRT)显示装置,在计算机、智能电话、手机、汽车导航装置、电子书等信息终端中成为最常见的显示装置。

[0003] 液晶面板显示驱动信号中,通常为了防止液晶分子的特性固化,会采用交流驱动的方式进行驱动,常用的反转驱动方式有点反转驱动方式、列反转驱动方式、行反转驱动方式和1+2line反转驱动方式,其中,1+2line反转驱动方式的显示品质较好且功耗略低于点反转,因此是目前最常用的一种反转驱动方式。但是,1+2line反转驱动方式情况下,驱动芯片工作时的温度可达到120℃,甚至超过120℃,因此不得不采取贴附散热片的工序来降低驱动芯片的工作温度,增加了整个面板的生产成本。因此,目前开始越来越多的利用N line反转驱动方式,N取值越大,驱动芯片工作时的温度降低的越显著。

[0004] 但是,在一帧图像内的N Line反转驱动方式的输出是一种时序循环的变换极性,由于RC(Resistance Capacitance,电阻/电容)延迟效应会产生像素充电不足的问题,由此导致在液晶面板上出现水平等距横纹的现象,且当N值越大时,水平等距横纹的现象越明显。

### 发明内容

[0005] 为了解决现有技术中存在的上述问题,本发明提供了一种像素矩阵驱动装置、液晶显示器及像素矩阵驱动方法。本发明要解决的技术问题通过以下技术方案实现:

[0006] 本发明实施例提供了一种像素矩阵驱动装置,包括:

[0007] 时序控制器,用于接收第一极性数字信号,并将所述第一极性数字信号对应的极性位置进行位置重排,获得第二极性数字信号;

[0008] 源极驱动电路,用于对所述第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号。

[0009] 在一个具体实施例中,所述时序控制器包括若干储存单元,每个储存单元包括N个储存器,且所述第一极性数字信号包括若干个子极性数字信号,每个所述储存器用于根据预设规则接收1个子极性数字信号。

[0010] 在一个具体实施例中,所述源极驱动电路包括:

[0011] 极性转换单元,用于对所述第二极性数字信号进行极性转换,获得第二极性转换信号;

[0012] 开关恢复单元,用于根据所述第一极性数字信号的位置,对所述第二极性转换信号进行位置恢复,获得第一极性转换信号。

[0013] 在一个具体实施例中,所述极性转换单元包括N个极性转换模块,所述极性转换模块包括正极性转换模块和负极性转换模块;其中,当第X级所述极性转换模块为正极性转换模块时,则第X+1级所述极性转换模块为负极性转换模块,其中,N、X均为正整数,且 $1 \leq X \leq N$ 。

[0014] 在一个具体实施例中,开关恢复单元包括N个开关恢复模块,所述第二极性转换信号包括若干个子极性转换信号,所述开关恢复模块用于根据所述第一极性数字信号的位置,对所述子极性转换信号进行位置恢复。

[0015] 在一个具体实施例中,第X级所述开关恢复模块包括若干开关,所述开关的输入端连接第X级所述极性转换模块,所述开关的输出端用于控制不同的第一极性数字信号的极性。

[0016] 在一个具体实施例中,所述源极驱动电路还包括数据锁存单元和电平转换单元,所述数据锁存单元包括N个数据锁存器,所述电平转换单元包括N个电平转换器,第X级所述数据锁存器和第X级所述电平转换器依次连接于第X级所述储存器和第X级所述极性转换模块之间。

[0017] 在一个具体实施例中,所述源极驱动电路还包括输出缓存单元,所述输出缓存单元包括N个输出缓存器,第X级所述输出缓存器连接于第X级所述极性转换模块和第X级所述开关恢复模块之间。

[0018] 本发明同时还提供一种像素矩阵驱动方法,包括:

[0019] 接收第一极性数字信号,并将所述第一极性数字信号对应的极性位置进行位置重排,获得第二极性数字信号;

[0020] 对所述第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号。

[0021] 本发明同时还提供一种液晶显示器,包括上述任一项所述的像素矩阵驱动装置。

[0022] 与现有技术相比,本发明的有益效果:

[0023] 本发明通过时序控制器实现对第一极性数字信号的位置重排,以得到第二极性数字信号,并通过源极驱动电路对进行位置重排后的第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号,使得输出的第一极性转换信号输出至显示面板的对应位置,从而使得该像素矩阵驱动装置不仅适用于传统的极性反转方式,还能适用于交错式极性反转方式,进而减少了显示面板的水平等距横纹的现象,还能够降低驱动芯片工作时的温度。

## 附图说明

[0024] 图1为本发明实施例提供的一种像素矩阵驱动装置的结构示意图;

[0025] 图2为本发明实施例提供的一种像素单元的结构示意图;

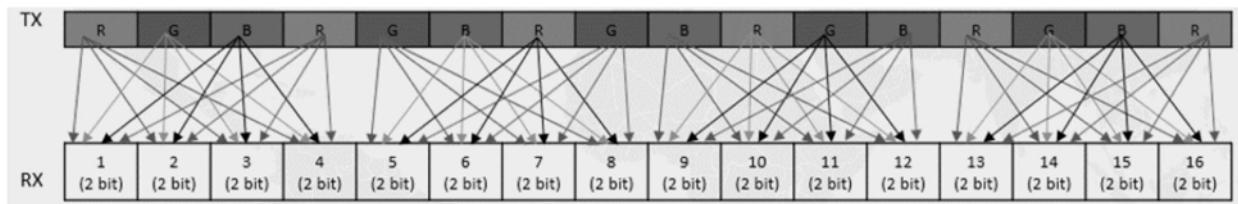

[0026] 图3为本发明实施例提供的一种驱动信号输出结果示意图;

[0027] 图4为本发明实施例提供的一种时序控制器的结构示意图;

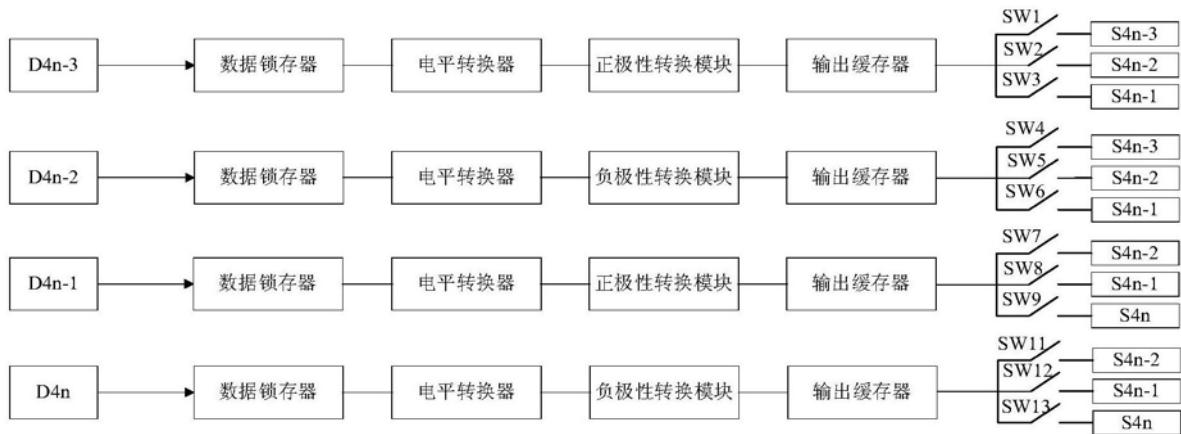

[0028] 图5为本发明实施例提供的一种源极驱动电路示意图。

## 具体实施方式

[0029] 下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

[0030] 需要说明的是,当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。本文所使用的术语“垂直”、“水平”、“左”、“右”以及类似的表述只是为了说明的目的,并不表示是唯一的实施方式。

[0031] 实施例一

[0032] 请参见图1,图1为本发明实施例提供的一种像素矩阵驱动装置的结构示意图。本实施例的像素矩阵驱动装置包括:

[0033] 时序控制器,用于接收第一极性数字信号,并将所述第一极性数字信号对应的极性位置进行位置重排,获得第二极性数字信号;

[0034] 源极驱动电路,用于对所述第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号。

[0035] 本发明实施例通过时序控制器实现对第一极性数字信号的位置重排,以得到第二极性数字信号,并通过源极驱动电路对进行位置重排后的第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号,使得输出的第一极性转换信号输出至显示面板的对应位置,从而使得该像素矩阵驱动装置不仅适用于传统的极性反转方式,还能适用于交错式极性反转方式,进而减少了显示面板的水平等距横纹的现象,还能够降低驱动芯片工作时的温度。

[0036] 本发明实施例的像素矩阵驱动装置不仅适用于点反转驱动方式、列反转驱动方式、行反转驱动方式、1+2line反转驱动方式和N Line反转驱动方式,还适用于交错式极性反转方式,交错式极性反转方式是指像素矩阵的第*i*列子像素与第*i*+1列子像素之间具有不同的极性反转位置,具体地,液晶显示面板,包括相互平行的多列数据线和相互平行的多行扫描线,多列所述数据线和多行所述扫描线相互垂直交叉排列,多列所述数据线和多行所述扫描线交叉形成以矩阵方式排列的x行y列像素矩阵,x和y为正整数,其中,第*i*列子像素与第*i*+1列子像素之间具有不同的极性反转位置,其中,0<*i*<x。

[0037] 具体地,极性反转位置是指在任意一列子像素中,极性发生变化的位置,如第*i*列子像素的第1个子像素至第*a*个子像素均为正极性,第*a*+1个子像素为负极性,则第*a*+1个子像素即为极性发生变化的位置。每一列子像素对应的与一条数据线连接,每一行子像素对应的与一条扫描线连接。其中,数据线用于为对应的一列子像素提供数据信号,扫描线用于为对应的一行子像素提供扫描信号。

[0038] 例如,请参见图2,该像素矩阵包括16行16列子像素,其中,第1列子像素D1的极性反转位置发生在第9行子像素G9的像素位置,第2列子像素D2的极性反转位置发生在第5行子像素G5的像素位置和第13行子像素G15的像素位置,第3列子像素D3的极性反转位置发生在第9行子像素G9,依次类推,该方式即为交错式极性反转方式。

[0039] 交错式极性反转方式通过将极性变换位置分配到不同的像素位置上,可减轻水平等距横纹现象,提高液晶显示面板的显示质量,同时,能够降低由驱动所产生的功耗和温度,改善液晶显示面板的显示质量,提高液晶显示面板的使用寿命。

[0040] 请参见图3,对于每隔8行进行一次极性反转的交错式极性反转方式的实现要求能够输出如图3所示的驱动信号,即能输出图3中的组合A(子像素的极性排列方式为++--)、组合B(子像素的极性排列方式为--++)、组合C(子像素的极性排列方式为+-+-)、组合D(子像素的极性排列方式为-+-+)、组合E(子像素的极性排列方式为+-+-)、组合F(子像素的极性

排列方式为-+++)、目前用于源极驱动的驱动电路仅能实现组合C至组合F四种极性输出组合,但不能实现组合A和组合B两种极性输出组合方式,因此目前的驱动装置不适用于交错式极性反转方式。

[0041] 在一个具体实施例中,时序控制器,用于接收第一极性数字信号,并将所述第一极性数字信号对应的极性位置进行位置重排,获得第二极性数字信号;

[0042] 在一个具体实施例中,第一开关单元用于接收第一极性数字信号,根据所述第一极性数字信号中每个极性位置的极性,将所述第一极性数字信号中每个极性位置进行位置重排,获得第二极性数字信号。

[0043] 具体地,所述时序控制器包括若干储存单元,每个储存单元包括N个储存器,且所述第一极性数字信号包括若干个子极性数字信号,每个所述储存器用于根据预设规则接收1个子极性数字信号。其中,第一极性数字信号对应的每个子像素的极性代表1个子极性数字信号,即子极性数字信号反应了其对应的子像素的极性。

[0044] 进一步地,当时序控制器接收到第一极性数字信号时,会将每个子极性数字信号按照预设规则对应传输至1个存储器中,即当时序控制器接收到第一极性数字信号时,根据每个储存单元中储存器的个数,按照像素矩阵中第一极性数字信号的顺序,对应将相同个数的子极性数字信号传输至每个储存单元,且每个存储器按照预设规则接收1个子极性数字信号,其中,当每个储存单元中包含m个储存器时,则该储存单元按照像素矩阵中第一极性数字信号的顺序对应接收m个储存器,预设规则是指当某m个子极性数字信号传输至某个储存单元时,根据每个子极性数字信号的极性将其传输至该储存单元中与其极性对应的某个储存器中,即若该子极性数字信号的极性为正极性,则其传输的某个储存器所对应的某个极性转换模块也为正极性转换模块,若该子极性数字信号的极性为负极性,则其传输的某个储存器所对应的某个极性转换模块也为负极性转换模块,且当某个子极性数字信号传输至某个储存单元的某个储存器时,传输至该储存单元的其余子极性数字信号则不能再传输至该储存器中,将按照该预设规则进行位置重排后的子极性数字信号即为第二极性数字信号。

[0045] 进一步地,每个储存单元的每个储存器将其接收的子极性数字信号对应传输至极性转换模块,且每个储存单元中的储存器的数目与源极驱动电路中的极性转换模块相等,即若极性转换模块共有N个,则每个储存单元中的储存器的个数也为N个,且每个储存单元中的储存器按照顺序将子极性数字信号传输至极性转换模块中,即储存单元中的第M级储存器将其接收的子极性数字信号传输至第M级极性转换模块(第M级即为第M个)。

[0046] 在一个具体实施例中,该源极驱动电路包括极性转换单元和开关恢复单元,且源极驱动电路包括N级源极驱动器,即源极驱动电路包括N个源极驱动器,每个源极驱动器均包括1个极性转换模块和1个开关恢复模块,其中,每个源极驱动器接收由TCON(时序控制器)传输的若干行第二极性数字信号。

[0047] 其中,极性转换单元,用于对所述第二极性数字信号进行极性转换,获得第二极性转换信号;

[0048] 具体地,极性转换单元用于将经过时序控制器进行位置重排的子极性数字信号进行极性转换,将储存单元接收到的子极性数字信号传输至开关恢复模块中,若开关恢复模块对应的极性转换模块为负极性转换模块,则该子极性数字信号经过极性转换模块输出的

模拟信号的极性即为负极性,若开关恢复模块对应的极性转换模块为正极性转换模块,则该子极性数字信号经过极性转换模块输出的模拟信号的极性即为正极性,经过极性转换后的所有子极性数字信号即为第二极性转换信号,第二极性转换信号为模拟信号。

[0049] 进一步地,所述极性转换单元包括N个极性转换模块,所述极性转换模块包括正极性转换模块和负极性转换模块;其中,当第X级所述极性转换模块为正极性转换模块时,则第X+1级所述极性转换模块为负极性转换模块,其中,N、X均为正整数,且 $1 \leq X \leq N$ 。

[0050] 例如,请参见图5,第1级极性转换模块为正极性转换模块,第2级极性转换模块为负极性转换模块,第3级极性转换模块为正极性转换模块,第4级极性转换模块负正极性转换模块。

[0051] 其中,开关恢复单元,用于根据所述第一极性数字信号的位置,对所述第二极性转换信号进行位置恢复,获得第一极性转换信号。

[0052] 具体地,开关恢复单元包括N个开关恢复模块,所述第二极性转换信号包括若干个子极性转换信号,所述开关恢复模块用于根据所述第一极性数字信号的位置,对所述子极性转换信号进行位置恢复。

[0053] 进一步地,第X级所述开关恢复模块包括若干开关,所述开关的输入端连接第X级所述极性转换模块,所述开关的输出端用于控制不同的第一极性数字信号的极性,即通过开关将所获得的子极性转换信号恢复至其对应的子极性数字信号所在的像素矩阵中的位置。

[0054] 第一极性转换信号是通过开关恢复单元将经时序控制器进行位置重排后的第二极性转换信号进行位置恢复,例如将第1级存储单元的第1级存储器接收到的子极性数字信号传输至第2级极性转换模块中,则需通过第2级开关恢复单元将该子极性数字信号对应的子极性转换信号恢复至其原来的像素位置,即通过第2级开关恢复单元中的与控制该子极性数字信号位置极性的开关进行连通,以使第2级开关恢复单元块正确控制其对应像素位置的极性。

[0055] 进一步地,第X级开关恢复模块包括p个开关,其中1个开关的输出端连接本级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,其余开关的输出端可以分别连接除本级源极驱动器之外其余不同的源极驱动器。

[0056] 优选地,每个开关恢复模块包括3个开关,在第1级开关恢复模块中,其中1个开关的输出端连接本级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,另外1个开关的输出端连接下一级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第3个开关连接下两级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性;在第Y级开关恢复模块中,其中1个开关的输出端连接本级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,另外1个开关的输出端连接上一级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第3个开关的输出端连接下一级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,在第N级开关恢复模块中,其中1个开关的输出端连接本级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,另外1个开关的输出端连接上一级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第3个开关连接上两级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,这样设计可以节省芯片面积,提高运行速率,其中, $1 < Y < N$ 。

[0057] 本发明实施例的每个开关恢复模块的开关个数还可以为其它,例如可以根据每个像素矩阵的极性设置特点进行变换,以实现子极性数字信号的位置重排和位置恢复,熟悉本领域技术的人员显然可以容易地对这些实施例做出各种修改,并把在此说明的一般原理应用到其他实施例中而不必经过创造性的劳动。因此,本发明不限于上述实施例,本领域技术人员根据本发明的揭示,不脱离本发明范畴所做出的改进和修改都应该在本发明的保护范围之内。

[0058] 例如,请参见图5,图5给出了一种具体的源极驱动电路,其中,每个开关恢复模块包括3个开关,第1级极性转换模块(正极性转换模块)对应连接每级储存单元中的第1级储存器,第1级极性转换模块的输出端连接第1级开关恢复模块中的3个开关,第1个开关SW1的输出端连接第1级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第2个开关SW2的输出端连接第2级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第3个开关SW3的输出端连接第3级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性;第2级极性转换模块(负极性转换模块)对应连接每级储存单元中的第2级储存器,第2级极性转换模块的输出端连接第2级开关恢复模块中的3个开关,第1个开关SW4的输出端连接第1级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第2个开关SW5的输出端连接第2级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第3个开关SW6的输出端连接第3级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性;第3级极性转换模块(正极性转换模块)对应连接每级储存单元中的第3级储存器,第3级极性转换模块的输出端连接第3级开关恢复模块中的3个开关,第1个开关SW7的输出端连接第2级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第2个开关SW8的输出端连接第3级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第3个开关SW9的输出端连接第4级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性;第4级极性转换模块(负极性转换模块)对应连接每级储存单元中的第4级储存器,第4级极性转换模块的输出端连接第4级开关恢复模块中的3个开关,第1个开关SW10的输出端连接第2级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第2个开关SW11的输出端连接第3级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性,第3个开关SW12的输出端连接第4级源极驱动器所控制的子极性数字信号所在的像素矩阵位置的极性。

[0059] 在一个具体实施例中,源极驱动电路还包括数据锁存单元、电平转换单元,数据锁存单元用于存储第二极性数字信号,电平转换单元用于对第二极性数字信号进行电平转换,其中数据锁存单元包括N个数据锁存器,电平转换单元包括N个电平转换器,第X级所述数据锁存器和第X级所述电平转换器依次连接于第X级所述储存器和第X级所述极性转换模块之间。

[0060] 在一个具体实施例中,源极驱动电路还包括输出缓存单元,输出缓存单元用于缓存所述第一极性转换信号,所述输出缓存单元包括N个输出缓存器,第X级所述输出缓存器连接于第X级所述极性转换模块和第X级所述开关恢复模块之间。

[0061] 为了更好的理解本发明的像素矩阵驱动装置,本实施例将以1个具体的实施方式进行说明。请同时参见图2、图4和图5,如图3所示,该像素矩阵的第一行子像素对应的第一极性数字信号的极性分别为+----+----+----+,并将每个储存单元中的储存器的个数设置

为4个，则源极驱动电路包括4个源极驱动器；如图4所示，TX行对应的为传输至时序控制器的第一极性数字信号，RX行对应的为经过位置重排的第二极性数字信号。其中，每个储存单元包括4个储存器，每个第一极性数字信号包括16个子极性数字信号，即储存器1、储存器2、储存器3和储存器4构成第1级储存单元，储存器5、储存器6、储存器7和储存器8构成第2级储存单元，储存器9、储存器10、储存器11和储存器12构成第3级储存单元，储存器13、储存器14、储存器15和储存器16构成第4级储存单元，其中，储存器1、储存器5、储存器9、储存器13对应将其接收的子极性数字信号传输至第1级极性转换模块，储存器2、储存器6、储存器10、储存器14对应将其接收的子极性数字信号传输至第2级极性转换模块，储存器3、储存器7、储存器11、储存器15对应将其接收的子极性数字信号传输至第3级极性转换模块，储存器4、储存器8、储存器12、储存器16对应将其接收的子极性数字信号传输至第4级极性转换模块；则每个储存单元对应接收4个子极性数字信号，则第1个子极性数字信号至第4个子极性数字信号对应传输至第1级储存单元（第1个子极性数字信号至第4个子极性数字信号的极性分别为+---），则第5个子极性数字信号至第8个子极性数字信号对应传输至第2级储存单元（第5个子极性数字信号至第8个子极性数字信号的极性分别为+---），则第9个子极性数字信号至第12个子极性数字信号对应传输至第3级储存单元（第9个子极性数字信号至第12个子极性数字信号的极性分别为+---），则第13个子极性数字信号至第16个子极性数字信号对应传输至第4级储存单元（第13个子极性数字信号至第16个子极性数字信号的极性分别为+---），第1个子极性数字信号的极性为+，则可以将第1个子极性数字信号传输至储存器1，第2个子极性数字信号的极性为-，则可以将第2个子极性数字信号传输至储存器4，第3个子极性数字信号的极性为-，则可以将第3个子极性数字信号传输至储存器2，第4个子极性数字信号的极性为+，则可以将第4个子极性数字信号传输至储存器3，第5个子极性数字信号的极性为+，则可以将第5个子极性数字信号传输至储存器5，第6个子极性数字信号的极性为-，则可以将第6个子极性数字信号传输至储存器6，第7个子极性数字信号的极性为-，则可以将第7个子极性数字信号传输至储存器8，第8个子极性数字信号的极性为+，则可以将第8个子极性数字信号传输至储存器7，第9个子极性数字信号的极性为+，则可以将第9个子极性数字信号传输至储存器9，第10个子极性数字信号的极性为-，则可以将第10个子极性数字信号传输至储存器12，第11个子极性数字信号的极性为-，则可以将第11个子极性数字信号传输至储存器10，第12个子极性数字信号的极性为+，则可以将第12个子极性数字信号传输至储存器11，第13个子极性数字信号的极性为+，则可以将第13个子极性数字信号传输至储存器13，第14个子极性数字信号的极性为-，则可以将第14个子极性数字信号传输至储存器14，第15个子极性数字信号的极性为-，则可以将第15个子极性数字信号传输至储存器16，第16个子极性数字信号的极性为+，则可以将第16个子极性数字信号传输至储存器15，则当第1个子极性数字信号至第4个子极性数字信号传输至源极驱动电路时，将开关SW1接通、开关SW6接通、开关SW9接通、开关SW11接通，开关SW2断开、开关SW3断开、开关SW4断开、开关SW5断开、开关SW7断开、开关SW8断开、开关SW10断开、开关SW12断开、开关SW13断开，当第5个子极性数字信号至第8个子极性数字信号传输至源极驱动电路时，将开关SW1接通、开关SW5接通、开关SW9接通、开关SW12接通，开关SW2断开、开关SW3断开、开关SW4断开、开关SW6断开、开关SW7断开、开关SW8断开、开关SW10断开、开关SW11断开、开关SW13断开，则当第9个子极性数字信号至第12个子极性数字信号传输至源极驱动电路时，将开关SW1接

通、开关SW6接通、开关SW9接通、开关SW11接通，开关SW2断开、开关SW3断开、开关SW4断开、开关SW5断开、开关SW7断开、开关SW8断开、开关SW10断开、开关SW12断开、开关SW13断开，当第13个子极性数字信号至第16个子极性数字信号传输至源极驱动电路时，将开关SW1接通、开关SW5接通、开关SW9接通、开关SW12接通，开关SW2断开、开关SW3断开、开关SW4断开、开关SW6断开、开关SW7断开、开关SW8断开、开关SW10断开、开关SW11断开、开关SW13断开。同理地，请参见该像素矩阵的第五行子像素对应的第一极性数字信号的极性分别为+-+-+-+---++--，则第1个子极性数字信号的极性为+，则可以将第1个子极性数字信号传输至储存器1，第2个子极性数字信号的极性为+，则可以将第2个子极性数字信号传输至储存器3，第3个子极性数字信号的极性为-，则可以将第3个子极性数字信号传输至储存器2，第4个子极性数字信号的极性为-，则可以将第4个子极性数字信号传输至储存器4，第5个子极性数字信号的极性为+，则可以将第5个子极性数字信号传输至储存器5，第6个子极性数字信号的极性为+，则可以将第6个子极性数字信号传输至储存器7，第7个子极性数字信号的极性为-，则可以将第7个子极性数字信号传输至储存器6，第8个子极性数字信号的极性为-，则可以将第8个子极性数字信号传输至储存器8，第9个子极性数字信号的极性为+，则可以将第9个子极性数字信号传输至储存器9，第10个子极性数字信号的极性为+，则可以将第10个子极性数字信号传输至储存器11，第11个子极性数字信号的极性为-，则可以将第11个子极性数字信号传输至储存器10，第12个子极性数字信号的极性为-，则可以将第12个子极性数字信号传输至储存器12，第13个子极性数字信号的极性为+，则可以将第13个子极性数字信号传输至储存器13，第14个子极性数字信号的极性为+，则可以将第14个子极性数字信号传输至储存器15，第15个子极性数字信号的极性为-，则可以将第15个子极性数字信号传输至储存器14，第16个子极性数字信号的极性为-，则可以将第16个子极性数字信号传输至储存器16，则当第1个子极性数字信号至第4个子极性数字信号传输至源极驱动电路时，将开关SW1接通、开关SW6接通、开关SW8接通、开关SW13接通，开关SW2断开、开关SW3断开、开关SW4断开、开关SW5断开、开关SW7断开、开关SW9断开、开关SW10断开、开关SW11断开、开关SW12断开，当第5个子极性数字信号至第8个子极性数字信号传输至源极驱动电路时，将开关SW1接通、开关SW6接通、开关SW7接通、开关SW13接通，开关SW2断开、开关SW3断开、开关SW4断开、开关SW5断开、开关SW8断开、开关SW9断开、开关SW10断开、开关SW11断开、开关SW12断开，当第9个子极性数字信号至第12个子极性数字信号传输至源极驱动电路时，将开关SW1接通、开关SW6接通、开关SW8接通、开关SW13接通，开关SW2断开、开关SW3断开、开关SW4断开、开关SW5断开、开关SW7断开、开关SW9断开、开关SW10断开、开关SW11断开、开关SW12断开，当第13个子极性数字信号至第16个子极性数字信号传输至源极驱动电路时，将开关SW1接通、开关SW6接通、开关SW7接通、开关SW13接通，开关SW2断开、开关SW3断开、开关SW4断开、开关SW5断开、开关SW8断开、开关SW9断开、开关SW10断开、开关SW11断开、开关SW12断开。依次类推，通过该实施例的像素矩阵驱动装置便可以实现+-+-、-++-、++-、-+-+、+-+以及-++，从而使得本实施例的像素矩阵驱动装置不仅适用于传统的极性反转方式，还能适用于交错式极性反转方式，进而减少了显示面板的水平等距横纹的现象，还能够降低驱动芯片工作时的温度。

[0062] 本发明实施例通过增加每个储存单元中储存器的个数和源极驱动器的个数还可以实现+++-----、----++…，例如储存器和源极驱动器的个数为6个，则像素单元的极

性可以实现++++-、---++的排列方式,从而使得本实施例的像素矩阵驱动装置不仅适用于传统的极性反转方式,还能适用于交错式极性反转方式,进而减少了显示面板的水平等距横纹的现象,还能够降低驱动芯片工作时的温度。

[0063] 本发明通过时序控制器实现对第一极性数字信号的位置重排,以得到第二极性数字信号,并通过源极驱动电路对进行位置重排后的第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号,使得输出的第一极性转换信号输出至显示面板的对应位置,从而使得该像素矩阵驱动装置不仅适用于传统的极性反转方式,还能适用于交错式极性反转方式,进而减少了显示面板的水平等距横纹的现象,还能够降低驱动芯片工作时的温度。

[0064] 本发明实施例还提供一种像素矩阵驱动方法,该方法包括:

[0065] 接收第一极性数字信号,并将所述第一极性数字信号对应的极性位置进行位置重排,获得第二极性数字信号;

[0066] 对所述第二极性数字信号进行极性转换和位置恢复,获得第一极性转换信号。

[0067] 本发明实施例的方法不仅适用于传统的极性反转方式,还能适用于交错式极性反转方式,进而减少了显示面板的水平等距横纹的现象,还能够降低驱动芯片工作时的温度。

[0068] 本发明实施例还提供一种液晶显示器,该液晶显示器包括上述任一项所述的像素矩阵驱动装置,从而使得该液晶显示器的水平等距横纹的现象,还能够降低驱动芯片工作时的温度。

[0069] 以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

图1

|     | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | D16 |

|-----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

| G1  | +  | -  | -  | +  | +  | -  | -  | +  | +  | -   | -   | +   | +   | -   | -   | +   |

| G2  | +  | -  | -  | +  | -  | -  | +  | +  | +  | -   | -   | +   | +   | -   | -   | +   |

| G3  | +  | -  | -  | +  | -  | -  | +  | +  | -  | -   | +   | +   | +   | -   | -   | +   |

| G4  | +  | -  | -  | +  | -  | -  | +  | +  | -  | -   | +   | +   | -   | -   | +   | +   |

| G5  | +  | +  | -  | -  | -  | -  | +  | +  | -  | -   | +   | +   | -   | -   | +   | +   |

| G6  | +  | +  | -  | -  | -  | +  | +  | -  | -  | +   | +   | -   | -   | +   | +   | +   |

| G7  | +  | +  | -  | -  | -  | +  | +  | -  | -  | +   | +   | -   | -   | +   | +   | +   |

| G8  | +  | +  | -  | -  | -  | +  | +  | -  | -  | +   | +   | -   | -   | +   | +   | -   |

| G9  | -  | +  | +  | -  | -  | +  | +  | -  | -  | +   | +   | -   | -   | +   | +   | -   |

| G10 | -  | +  | +  | -  | +  | +  | -  | -  | -  | +   | +   | -   | -   | +   | +   | -   |

| G11 | -  | +  | +  | -  | +  | +  | -  | -  | +  | +   | -   | -   | -   | +   | +   | -   |

| G12 | -  | +  | +  | -  | +  | +  | -  | -  | +  | +   | -   | -   | +   | +   | -   | -   |

| G13 | -  | -  | +  | +  | +  | +  | -  | -  | +  | +   | -   | -   | +   | +   | -   | -   |

| G14 | -  | -  | +  | +  | +  | -  | -  | +  | +  | +   | -   | -   | +   | +   | -   | -   |

| G15 | -  | -  | +  | +  | +  | -  | -  | +  | +  | -   | -   | +   | +   | -   | -   | -   |

| G16 | -  | -  | +  | +  | +  | -  | -  | +  | +  | -   | -   | +   | +   | -   | -   | +   |

图2

|   | S1 | S2 | S3 | S4 |

|---|----|----|----|----|

| A | +  | +  | -  | -  |

| B | -  | -  | +  | +  |

| C | +  | -  | -  | +  |

| D | -  | +  | +  | -  |

| E | +  | -  | +  | -  |

| F | -  | +  | -  | +  |

图3

图4

图5

|         |                                                |         |            |

|---------|------------------------------------------------|---------|------------|

| 专利名称(译) | 一种像素矩阵驱动装置、液晶显示器及像素矩阵驱动方法                      |         |            |

| 公开(公告)号 | <a href="#">CN111312181A</a>                   | 公开(公告)日 | 2020-06-19 |

| 申请号     | CN201811521101.8                               | 申请日     | 2018-12-12 |

| [标]发明人  | 刘子涵<br>王柏钧                                     |         |            |

| 发明人     | 刘子涵<br>王柏钧                                     |         |            |

| IPC分类号  | G09G3/36                                       |         |            |

| 代理人(译)  | 张捷                                             |         |            |

| 外部链接    | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

**摘要(译)**

本发明公开了一种像素矩阵驱动装置，包括：时序控制器，用于接收第一极性数字信号，并将第一极性数字信号对应的极性位置进行位置重排，获得第二极性数字信号；源极驱动电路，用于对第二极性数字信号进行极性转换和位置恢复，获得第一极性转换信号。本发明实施例通过时序控制器实现对第一极性数字信号的位置重排，以得到第二极性数字信号，并通过源极驱动电路对进行位置重排后的第二极性数字信号进行极性转换和位置恢复，使得输出的第一极性转换信号输出至显示面板的对应位置，使得该像素矩阵驱动装置不仅适用于传统的极性反转方式，还适用于交错式极性反转方式，进而减少了显示面板的水平等距横纹的现象，还能够降低驱动芯片工作时的温度。