(12) 实用新型专利

(10) 授权公告号 CN 205104208 U

(45) 授权公告日 2016. 03. 23

(21) 申请号 201520814592. 0

(22) 申请日 2015. 10. 20

(73) 专利权人 重庆惠科金扬科技有限公司

地址 401320 重庆市巴南区界石镇石桂大道

16 号 3 幢 1-1

(72) 发明人 王智勇 王磐

(74) 专利代理机构 深圳中一专利商标事务所

44237

代理人 张全文

(51) Int. Cl.

G09G 3/36(2006. 01)

权利要求书7页 说明书15页 附图5页

(54) 实用新型名称

一种液晶显示屏控制电路

(57) 摘要

本实用新型涉及显示屏控制技术领域，尤其涉及一种液晶显示屏控制电路。在本实用新型的实施例中，所述液晶显示屏控制电路包括 VGA 接口模块、HDMI 接口模块、主控模块、音频输出模块、接屏模块和电源模块，所述 VGA 接口模块接收电脑或上位机输出的模拟视频图像信息，所述 HDMI 接口模块接收电脑或上位机输出的数字视频图像信息，所述主控模块将所述模拟视频图像信息或数字视频图像信息进行处理后输出至音频输出模块和接屏模块，进行音频的输出和视频图像信息的显示。本实用新型在传统液晶显示屏控制电路的基础上，减少了一个背光驱动芯片，节简了外围电路，大大节约了 PCB 板的空间，降低了成本，且提高了电路的稳定性。

1. 一种液晶显示屏控制电路，其特征在于，所述液晶显示屏控制电路包括：

接收电脑或上位机输出的模拟视频图像信息的 VGA 接口模块；

接收电脑或上位机输出的数字视频图像信息的 HDMI 接口模块；

输出端与扬声器连接，输出音频的音频输出模块；

输出端与显示屏连接，输出视频图像的接屏模块；

输入端与所述 VGA 接口模块和所述 HDMI 接口模块的输出端连接，输出端与所述音频输出模块和所述接屏模块的输入端连接，将所述模拟视频图像信息或所述数字视频图像信息进行处理并输出至所述音频输出模块和所述接屏模块进行音频输出和视频图像显示的主控模块；

分别与所述 VGA 接口模块、所述 HDMI 接口模块、所述音频输出模块、所述接屏模块和所述主控模块连接，为整个电路供电的电源模块。

2. 如权利要求 1 所述的液晶显示屏控制电路，其特征在于，所述主控模块包括主控芯片、晶振单元、复位单元、闪存单元、背光驱动单元以及电流电压检测单元；

所述晶振单元包括第一电阻、晶体振荡器、第一电容和第二电容；

所述主控芯片的振荡器输出脚、所述第一电阻的第一端、所述晶体振荡器的第一端和所述第一电容的第一端共接，所述主控芯片的振荡器输入脚、所述第一电阻的第二端、所述晶体振荡器的第二端和所述第二电容的第一端共接，所述第一电容的第二端、所述第二电容的第二端和所述晶体振荡器的第三端共接于地，所述主控芯片的振荡器电源脚接 +3.3V 电源，所述主控芯片的振荡器 地脚接地；

所述复位单元包第二电阻和第三电容；

所述主控芯片的复位脚、所述第二电阻的第二端和所述第三电容的第一端共接，所述第二电阻的第一端接 +3.3V 电源，所述第三电容的第二端接地；

所述闪存单元包括闪存芯片、第三电阻、第四电阻、第五电阻、第六电阻、第七电阻、第八电阻、第九电阻、第四电容和第五电容；

所述主控芯片的 SPI 总线时钟脚、所述第三电阻的第一端和所述第四电容的第一端共接，所述第四电容的第二端接地，所述第三电阻的第二端接所述闪存芯片的串行数据时钟脚，所述主控芯片的 SPI 总线数据输入脚通过所述第四电阻接所述闪存芯片的串行数据输入脚，所述主控芯片的 SPI 总线数据输出脚通过所述第五电阻接所述闪存芯片的串行数据输出脚，所述主控芯片的 SPI 总线使能脚通过所述第七电阻接所述闪存芯片的使能脚，所述主控芯片的第零 E 输入输出脚接所述第七电阻的第一端，所述第七电阻的第二端、所述第八电阻的第一端和所述闪存芯片的写保护脚共接，所述第八电阻的第二端接地，所述闪存芯片的电源脚、所述第九电阻的第二端和所述第五电容的第一端共接于 +3.3V 电源，所述闪存芯片的保持脚接所述第九电阻的第一端，所述闪存芯片的地脚和所述第五电阻的第二端共接于地；

所述背光驱动单元包括第一二极管、第六电容、第七电容、第八电容、第九电容、第十电容、第一电感、第十电阻、第一稳压二极管、第十一电容、第十二电容、第十三电容、第十四电容、第十五电容、第十一电阻、第十二电阻、第二稳压二极管、第十三电阻、第一 MOS 管、第十四电阻、第十五电阻、第十六电阻、第十七电阻、第十八电阻、第十九电阻；

所述主控芯片的电源启动脚、所述第一二极管的正极和所述第六电容的第一端共接，

所述第一二极管的负极接 +1.2V 电源，所述第六电容的第二端接地，所述主控芯片的过电压保护输入脚通过串联的所述第十二电阻和所述电阻接所述第二稳压二极管的负极，所述第二稳压二极管的负极通过所述第十三电阻接 +5V 电源，所述第二稳压二极管的正极接地，所述主控芯片的电流检测输入脚、所述第十七电阻的第二端、所述第十八电阻的第二端和所述第十九电阻的第二端共接于地，所述主控芯片的电流回路脚接所述第十六电阻的第一端，所述第十六电阻的第二端、所述第十七电阻的第一端、所述第十八电阻的第一端和所述第十九电阻的第一端共接于所述第一 MOS 管的源极，所述第一 MOS 管的栅极接所述第十四电阻的第二端，所述第十四电阻的第一端、所述第十五电阻的第一端和所述主控芯片的驱动输出脚共接，所述第十五电阻的第二端接地，所述第一 MOS 管的漏极、所述第一稳压二极管的正极、所述第十电阻的第一端和所述第一电感的第二端共接，所述第一稳压二极管的负极、所述第十一电容的第一端、所述第十三电容的第一端和所述第十五电容的正极共接于所述第二稳压二极管的负极，所述第十一电容的第二端接所述第十二电容的第一端，所述第十三电容接所述第十四电容的第一端，所述第十二电容的第二端、所述第十四电容的第二端和所述第十五电容的负极共接于地，所述第一电感的第一端、所述第八电容的第一端和所述第七电容的正极共接于 +12V 电源，所述第七电容的负极和所述第八电容的第二端共接于地，所述第十电阻的第二端通过串联的所述第十电容和所述第九电容接地；

所述电流电压检测单元包括第二十电阻、第二十一电阻、第二十二电阻、第二十三电阻、第二十四电阻、第十六电容、第二十五电阻、第二 MOS 管、第二十六电阻、第三 MOS 管、第二十七电阻、第四 MOS 管、第二十八电阻、第五 MOS 管、第二十九电阻；

所述主控芯片的环路补偿脚接所述第二十四电阻的第二端，所述第二十四电阻的第一端接所述第十六电容的第二端，所述主控芯片的第一 DRV 电流检测脚接所述第二十三电阻的第二端，所述主控芯片的第二 DRV 电流检测脚接所述第二十二电阻的第二端，所述主控芯片的第三 DRV 电流检测脚接所述第二十一电阻的第二端，所述主控芯片的第四 DRV 电流检测脚接所述第二十电阻的第二端，所述第二十电阻的第一端、所述第二十一电阻的第一端、所述第二十二电阻的第一端、所述第二十三电阻的第一端和所述第十六电容的第一端共接于地，所述主控芯片的第四电流控制脚接所述第二 MOS 管的源极，所述主控芯片的第四电压检测脚接所述第二十六电阻的第二端，所述主控芯片的第三电流控制脚接所述第三 MOS 管的源极，所述主控芯片的第三电压检测脚接所述第二十七电阻的第二端，所述主控芯片的第二电流控制脚接所述第四 MOS 管的源极，所述主控芯片的第二电压检测脚接所述第二十八电阻的第二端，所述主控芯片的第一电流控制脚接所述第五 MOS 管的源极，所述主控芯片的第一电压检测脚接所述第二十九电阻的第二端，所述第二 MOS 管的栅极、所述第三 MOS 管的栅极、所述第四 MOS 管的栅极、所述第五 MOS 管的栅极和所述第二十五电阻的第二端共接，所述第二十五电阻的第一端接 +5V 电源，所述第二十六电阻的第一端、所述第二十七电阻的第一端、所述第二十八电阻的第一端和所述第二十九电阻的第一端分别接所述第二 MOS 管的漏极、所述第三 MOS 管的漏极、所述第四 MOS 管的漏极和所述第五 MOS 管的漏极。

3. 如权利要求 2 所述的液晶显示屏控制电路，其特征在于，所述 VGA 接口模块包括 VGA 接口单元、第一 ESD 保护单元和第一存储单元；

所述 VGA 接口单元包括 VGA 接口、第三十电阻、第三十一电阻和第十七电容；

所述 VGA 接口的红色分量信号地脚、绿色分量信号地脚和蓝色分量信号地脚共接于地，所述 VGA 接口的地脚、所述第十七电容的第一端和所述第三十一电阻的第一端共接，所述第十七电容的第二端接地，所述第三十一电阻的第二端、所述第三十电阻的第二端和所述主控芯片的第五 C 输入输出脚共接；

所述第一 ESD 保护单元包括第一 ESD 保护芯片、第二 ESD 保护芯片、第三十二电阻、第三十三电阻、第三十四电阻、第三十五电阻、第三十六电阻、第三十七电阻、第三十八电阻、第三十九电阻、第四十电阻、第四十一电阻、第四十二电阻、第四十三电阻、第四十四电阻、第十八电容、第十九电容、第二十电容、第二十一电容、第二十二电容、第二十三电容、第二十四电容、第二十五电容、第二十六电容、第二十七电容、第二十八电容、第二十九电容、第二电感、第三电感和第四电感；

所述第一 ESD 保护芯片的电源脚与所述第二十八电容的第二端共接于所述第三十电阻的第一端，所述第二十八电容的第一端和所述第一 ESD 保护芯片的地脚共接于地，所述第一 ESD 保护芯片的第一输入输出脚、所述第三十二电阻的第一端和所述第二电感的第一端共接于所述 VGA 接口的蓝色分量信号脚，所述第二电感的第二端通过串联的所述第三十三电阻和所述第十八电容接所述主控芯片的蓝色分量信号正输入脚，所述第三十二电阻的第二端和所述第三十四电阻的第一端共接于地，所述第三十四电阻的第二端通过所述第十九电容接所述主控芯片的蓝色分量信号负输入脚，所述第一 ESD 保护芯片的第三输入输出脚、所述第三十五电阻的第一端和所述第三电感的第一端共接于所述 VGA 接口的绿色分量信号脚，所述第三电感的第二端通过串联的所述第三十六电阻和所述第二十电容接所述主控芯片的绿色分量信号正输入脚，所述第三十五电阻的第二端和所述第三十七电阻的第一端共接于地，所述第三十七电阻的第二端通过所述第二十一电容接所述主控芯片的绿色分量信号负输入脚，所述第一 ESD 保护芯片的第四输入输出脚、所述第三十八电阻的第一端和所述第四电感的第一端共接于所述 VGA 接口的红色分量信号脚，所述第四电感的第二端通过串联的所述第三十九电阻和所述第二十二电容接所述主控芯片的红色分量信号正输入脚，所述第三十八电阻的第二端和所述第四十电阻的第一端共接于地，所述第四十电阻的第二端通过所述第二十三电容接所述主控芯片的红色分量信号负输入脚，所述第二 ESD 保护芯片的第四输入输出脚、所述第四十一电阻的第一端、所述第二十四电容的第一端和所述第四十二电阻的第一端共接于所述 VGA 接口的行同步信号脚，所述第四十一电阻的第二端、所述第二十四电容的第二端和所述第二十五电容的第二端共接于地，所述第四十二电阻的第二端和所述第二十五电容的第一端共接于所述主控芯片的行同步信号输入脚，所述第二 ESD 保护芯片的第三输入输出脚、所述第四十三电阻的第一端、所述第二十六电容的第一端和所述第四十四电阻的第一端共接于所述 VGA 接口的场同步信号脚，所述第四十三电阻的第二端、所述第二十六电容的第二端和所述第二十七电容的第二端共接于地，所述第四十四电阻的第二端和所述第二十七电容的第一端共接于所述主控芯片的场同步信号输入脚，所述第二 ESD 保护芯片的地脚接地，所述第二 ESD 保护芯片的电源脚通过所述第二十九电容接地，所述第二 ESD 保护芯片的第一输入输出脚和第二输入输出脚接所述第一存储单元；

所述第一存储单元包括第一存储芯片、第四十五电阻、第四十六电阻、第四十七电阻、第四十八电阻、第四十九电阻、第五十电阻、第三十电容、第二二极管、第三二极管和第三稳

压二极管；

所述第一存储芯片的电源脚、所述第三十电容的第一端、所述第二二极管的负极、所述第三二极管的负极、所述第四十九电阻的第一端、所述第四十八电阻的第一端和所述第四十七电阻的第一端共接于所述第二 ESD 保护芯片的电源脚，所述第二二极管的正极接所述 VGA 接口的电源脚，所述第三二极管的正极与所述第三稳压二极管的负极共接于 +5V 电源，所述第三稳压二极管的负极接地，所述第一存储芯片的写保护脚接所述第五十电阻的第二端，所述第五十电阻的第一端和所述第四十九电阻的第二端共接于所述主控芯片的第三 A 输入输出脚，所述第一存储芯片的 I2C 总线时钟脚、所述第四十八电阻的第二端、所述第四十五电阻的第二端和所述第二 ESD 保护芯片的第二输入输出脚共接于所述主控芯片的第四 B 输入输出脚，所述第一存储芯片的 I2C 总线数据脚、所述第四十七电阻的第二端、所述第四十六电阻的第二端、所述第二 ESD 保护芯片的第一输入输出脚共接于所述主控芯片的第五 B 输入输出脚，所述第四十五电阻的第一端和所述第四十六电阻的第一端分别接所述 VGA 接口的 I2C 总线数据脚和 I2C 总线时钟脚，所述第一存储芯片的地脚和所述第三十电容的第二端接地。

4. 如权利要求 3 所述的液晶显示屏控制电路，其特征在于，所述 HDMI 接口模块包括 HDMI 接口、第二 ESD 保护单元和第二存储单元；

所述第二 ESD 保护单元包括第三 ESD 保护芯片、第四 ESD 保护芯片、第五 ESD 保护芯片、第三十一电容、第一双向稳压二极管、第五十一电阻、第五十二电阻、第二双向稳压二极管、第三十二电容、第三双向稳压二极管、第三十三电容、第四稳压二极管、第五十三电阻和第六十电阻；

所述 HDMI 接口的第三数据通道正脚、第三数据通道负脚、第二数据通道正脚和第二数据通道负脚分别接所述第三 ESD 保护芯片的第一输入脚、第二输入脚、第三输入脚和第四输入脚，所述 HDMI 接口的第一数据通道正脚、第一数据通道负脚、时钟通道正脚和时钟通道负脚分别接所述第四 ESD 保护芯片的第一输入脚、第二输入脚、第三输入脚和第四输入脚，所述 HDMI 接口的第二地脚、第一地脚、第零地脚和第四地脚接地，所述第三 ESD 保护芯片的第一输出脚、第二输出脚、第三输出脚和第四输出脚分别接所述主控芯片的第三 TDMS 数据通道正脚、第三 TDMS 数据通道负脚、第二 TDMS 数据通道正脚和第二 TDMS 数据通道负脚，所述第四 ESD 保护芯片的第一输出脚、第二输出脚、第三输出脚和第四输出脚分别接所述主控芯片的第一 TDMS 数据通道正脚、第一 TDMS 数据通道负脚、TDMS 时钟通道正脚和 TDMS 时钟通道负脚，所述 HDMI 接口的第三地脚、所述第五 ESD 保护芯片的第二输入输出脚、所述第三十一电容的第一端、所述第一双向稳压二极管的第一端和所述第五十一电阻的第一端共接，所述第三十一电容的第二端和所述第一双向稳压二极管的第二端共接于地，所述第五十一电阻的第二端和所述第五十二电阻的第一端共接于所述主控芯片的第四 C 输入输出脚，所述第五十二电阻的第二端、所述第三十二电容的第二端和所述第五 ESD 保护芯片的地脚共接于地，所述第五 ESD 保护芯片的电源脚接所述第三十二电容的第一端，所述 HDMI 接口的电源脚、所述第三双向稳压二极管的第一端、所述第三十三电容的第一端、所述第四稳压二极管的第一端和所述第五十三电阻的第一端共接于所述第二存储模块，所述 HDMI 接口的热插拔检测脚、所述第二双向稳压二极管的第一端、所述第三十二电容的第一端和所述第五十三电阻的第二端共接于所述第六十电阻的第一端，所述第六十电阻的

第二端接所述主控芯片的第五 A 输入输出脚，所述第二双向稳压二极管的第二端、所述第三十二电容的第二端、所述第三双向稳压二极管的第二端、所述第三十三电容的第二端和所述第四稳压二极管的第二端共接于地；

所述第二存储单元包括第二存储芯片、第四二极管、第五二极管、第五稳压二极管、第三十四电容、第五十四电阻、第五十五电阻、第五十六电阻、第五十七电阻、第五十八电阻、第五十九电阻、第四双向稳压二极管和第五双向稳压二极管；

所述第二存储芯片的电源脚、所述第三十四电容的第一端、所述第四二极负极、所述第五二极管的负极、所述第五十六电阻的第一端、所述第五十五电阻的第一端和所述第五十四电阻的第一端共接于所述第五十二电阻的第二端，所述第四二极管的正极接所述第五十三电阻的第一端，所述第五二极管的正极和所述第五稳压二极管的负极共接于 +5V 电源，所述第五稳压二极管的正极接地，所述第三十四电容的第二端和所述第二存储芯片的地脚共接于地，所述第二存储芯片的写保护脚接所述第五十七电阻的第二端，所述第五十七电阻的第一端和所述第五十六电阻的第二端共接于所述主控芯片的第三 A 输入输出脚，所述第二存储芯片的 I2C 总线时钟脚、所述第五十五电阻的第二端和所述第五十八电阻的第二端共接于所述主控芯片的第六 B 输入输出脚，所述第二存储芯片的 I2C 总线数据脚和所述第五十九电阻的第二端共接于所述主控芯片的第七 B 输入输出脚，所述第五十八电阻的第一端、所述第五双向稳压二极管的第一端和所述第五 ESD 保护芯片的第二输入输出脚共接于所述 HDMI 接口的 I2C 总线时钟端，所述第五十九电阻的第一端、所述第四双向稳压二极管的第一端和所述第五 ESD 保护芯片的第三输入输出脚共接于所述 HDMI 接口的 I2C 总线数据脚。

5. 如权利要求 4 所述的液晶显示屏控制电路，其特征在于，所述音频输出模块包括音频放大芯片、第六十一电阻、第六十二电阻、第六十三电阻、第六十四电阻、第六十五电阻、第六十六电阻、第六十七电阻、第六十八电阻、第六十九电阻、第七十电阻、第七十一电阻、第七十二电阻、第七十三电阻、第三十五电容、第三十六电容、第三十七电容、第三十八电容、第三十九电容、第四十电容、第四十一电容、第四十二电容、第四十三电容、第四十四电容、第四十五电容、第四十六电容、第四十七电容、第四十八电容、第四十九电容、第五十电容、第五十一电容、第五十二电容、第五十三电容、第五十四电容、第五十五电容、第五十六电容、第五电感、第六电感、第七电感和第八电感；

所述音频放大芯片的左声道电源脚、所述第四十二电容的第一端和所述第四十一电容的第一端共接于 +5V 电源，所述音频放大芯片的左声道地脚、所述第四十一电容的第二端和所述第四十二电容的第二端共接于地，所述音频放大芯片的左声道输入脚和所述第四十三电容的第二端共接于所述第三十五电容的第二端，所述第三十五电容的第一端、所述第六十二电阻的第一端、所述第三十六电容的第一端和所述第六十一电阻的第二端共接，所述第六十一电阻的第一端接所述主控芯片的第一空置脚，所述第三十六电容的第二端和所述第六十二电阻的第二端共接于地，所述音频放大芯片的右声道输入脚和所述第四十四电容的第二端共接于所述第三十七电容的第二端，所述第三十七电容的第一端、所述第六十四电阻的第一端、所述第三十八电容的第一端和所述第六十三电阻的第二端共接，所述第六十三电阻的第一端接所述主控芯片的第二空置脚，所述第三十八电容的第二端和所述第六十四电阻的第二端共接于地，所述第四十三电容的第一端、所述第四十六

电容的第一端、所述第六十八电阻的第一端、所述第六十五电阻的第二端和所述第三十九电容的第二端共接，所述第三十九电容的第一端接所述主控芯片的第三空置脚，所述第四十四电容的第一端、所述第四十五电容的第一端、所述第六十七电阻的第一端、所述第六十六电阻的第二端和所述第四十电容的第二端共接，所述第四十电容的第一端接所述主控芯片的第四空置脚，所述第六十七电阻的第二端、所述第六十八电阻的第二端、所述第四十五电容的第二端和所述第四十六电容的第二端共接于地，所述音频放大芯片的关断控制输入脚、所述第六十九电阻的第二端和所述第四十七电容的第一端共接，所述第六十九电阻的第一端和所述第七十电阻的第一端共接于所述主控芯片的第七 C 输入输出脚，所述音频放大芯片的模拟信号参考脚接所述第四十八电容的第一端，所述音频放大芯片的地脚、所述第四十八电容的第二端、所述第四十七电容第二端和所述第七十电阻的第二端共接于地，所述音频放大芯片的右声道电源脚、所述第四十九电容的第一端和所述第五十电容的第一端共接于 +5V 电源，所述音频放大芯片的右声道地脚、所述第四十九电容的第二端和所述第五十电容的第二端共接于地，所述音频放大芯片的左声道负输出脚、左声道正输出脚、右声道负输出脚和右声道正输出脚分别接第五电感的第一端、第六电感的第一端、第七电感的第一端和第八电感的第一端，所述第五电感的第二端、第六电感的第二端、第七电感的第二端和第八电感的第二端分别接所述第五十一电容的第一端、第五十二电容的第一端、第五十三电容的第一端和第五十四电容的第一端，所述第五十一电容的第二端、第五十二电容的第二端、第五十三电容的第二端和第五十四电容的第二端共接于地，所述音频放大芯片的 DC 音量控制脚、所述第五十六电容的第一端和所述第七十一电阻的第一端共接，所述第七十一电阻的第二端和所述第七十三电阻的第一端共接于所述主控芯片的第零 C 输入输出脚，所述音频放大芯片的电源脚、所述第五十五电容的第一端和所述第七十二电阻的第一端共接，所述第七十二电阻的第二端和所述第七十三电阻的第二端共接于 +5V 电源，所述第五十五电容的第二端和所述第五十六电容的第二端共接于地。

6. 如权利要求 5 所述的液晶显示屏控制电路，其特征在于，所述接屏模块包括插排、屏幕开关控制芯片、第九电感、第十电感、第十一电感、第七十四电阻、第七十五电阻、第七十六电阻、第七十七电阻、第七十八电阻、第五十七电容、第五十八电容、第五十九电容、第六十电容、第一三极管和第六 MOS 管；

所述插排的第一输入脚至第二十输入脚均接所述主控芯片，所述插排的电源脚接 LCD 正电源，所述插排的地脚接地，所述第一三极管的基极、所述第七十六电阻的第二端和所述第五十八电容的第一端共接，所述第七十六电阻的第一端和所述第七十七电阻的第一端共接于所述主控芯片的第六 C 输入输出端，所述第七十七电阻的第二端和所述第五十八电容的第二端共接于地，所述第一三极管的发射极接地，所述第一三极管的集电极、所述第七十四电阻的第二端和所述第七十五电阻共接，所述第七十四电阻的第一端、所述第五十七电容的第一端、所述屏幕开关控制芯片的第一至第三输入脚共接于所述第六 MOS 管的源极，所述第十一电感的第二端、所述第十电感的第二端和所述第九电感的第二端共接，所述第十一电感的第一端、所述第十电感的第一端和所述第九电感的第一端分别接 +5V 电源、+3.3V 电源和 +12V 电源，所述第七十五电阻的第二端、所述屏幕开关控制芯片的地脚和所述第六 MOS 管的栅极共接，所述第六 MOS 管的漏极、所述第五十九电容的正极、所述第六十电容的第一端和所述第七十八电阻的第一端共接，所述第五十九电容的负极、所述第

六十电容的第二端和所述第七十八电阻的第二端共接于地。

7. 如权利要求 6 所述的液晶显示屏控制电路, 其特征在于, 所述电源模块提供的电源包括 +12V 电源、+5V 电源、+3. 3V 电源和 +1. 2V 电源。

## 一种液晶显示屏控制电路

### 技术领域

[0001] 本实用新型涉及显示屏控制技术领域，尤其涉及一种液晶显示屏控制电路。

### 背景技术

[0002] 液晶显示屏控制电路是显示屏的核心部分，负责接收来自电脑或上位机输出的视频图像信息，并将所述视频图像信息进行处理后输出至显示屏和扬声器。

[0003] 传统的液晶显示屏控制电路大多采用主芯片和背光驱动芯片的方案，该方案电路结构复杂，占用 PCB 版空间，稳定性差且成本高。

### 实用新型内容

[0004] 本实用新型的目的在于提供一种液晶显示屏控制电路，旨在解决传统的液晶显示屏控制电路结构复杂，占用 PCB 版空间，稳定性差且成本高的问题。

[0005] 本实用新型是这样实现的，本实用新型提供了一种液晶显示屏控制电路，所述液晶显示屏控制电路包括：

[0006] 接收电脑或上位机输出的模拟视频图像信息的 VGA 接口模块；

[0007] 接收电脑或上位机输出的数字视频图像信息的 HDMI 接口模块；

[0008] 输出端与扬声器连接，输出音频的音频输出模块；

[0009] 输出端与显示屏连接，输出视频图像的接屏模块；

[0010] 输入端与所述 VGA 接口模块和所述 HDMI 接口模块的输出端连接，输出端与所述音频输出模块和所述接屏模块的输入端连接，将所述模拟视频图像信息或所述数字视频图像信息进行处理并输出至所述音频输出模块和所述接屏模块进行音频输出和视频图像显示的主控模块；

[0011] 分别与所述 VGA 接口模块、所述 HDMI 接口模块、所述音频输出模块、所述接屏模块和所述主控模块连接，为整个电路供电的电源模块。

[0012] 进一步的，所述主控模块包括主控芯片、晶振单元、复位单元、闪存单元、背光驱动单元以及电流电压检测单元；

[0013] 所述晶振单元包括第一电阻、晶体振荡器、第一电容和第二电容；

[0014] 所述主控芯片的振荡器输出脚、所述第一电阻的第一端、所述晶体振荡器的第一端和所述第一电容的第一端共接，所述主控芯片的振荡器输入脚、所述第一电阻的第二端、所述晶体振荡器的第二端和所述第二电容的第一端共接，所述第一电容的第二端、所述第二电容的第二端和所述晶体振荡器的第三端共接于地，所述主控芯片的振荡器电源脚接 +3.3V 电源，所述主控芯片的振荡器地脚接地；

[0015] 所述复位单元包第二电阻和第三电容；

[0016] 所述主控芯片的复位脚、所述第二电阻的第二端和所述第三电容的第一端共接，所述第二电阻的第一端接 +3.3V 电源，所述第三电容的第二端接地；

[0017] 所述闪存单元包括闪存芯片、第三电阻、第四电阻、第五电阻、第六电阻、第七电

阻、第八电阻、第九电阻、第四电容和第五电容；

[0018] 所述主控芯片的 SPI 总线时钟脚、所述第三电阻的第一端和所述第四电容的第一端共接，所述第四电容的第二端接地，所述第三电阻的第二端接所述闪存芯片的串行数据时钟脚，所述主控芯片的 SPI 总线数据输入脚通过所述第四电阻接所述闪存芯片的串行数据输入脚，所述主控芯片的 SPI 总线数据输出脚通过所述第五电阻接所述闪存芯片的串行数据输出脚，所述主控芯片的 SPI 总线使能脚通过所述第七电阻接所述闪存芯片的使能脚，所述主控芯片的第零 E 输入输出脚接所述第七电阻的第一端，所述第七电阻的第二端、所述第八电阻的第一端和所述闪存芯片的写保护脚共接，所述第八电阻的第二端接地，所述闪存芯片的电源脚、所述第九电阻的第二端和所述第五电容的第一端共接于 +3.3V 电源，所述闪存芯片的保持脚接所述第九电阻的第一端，所述闪存芯片的地脚和所述第五电阻的第二端共接于地；

[0019] 所述背光驱动单元包括第一二极管、第六电容、第七电容、第八电容、第九电容、第十电容、第一电感、第十电阻、第一稳压二极管、第十一电容、第十二电容、第十三电容、第十四电容、第十五电容、第十一电阻、第十二电阻、第二稳压二极管、第十三电阻、第一 MOS 管、第十四电阻、第十五电阻、第十六电阻、第十七电阻、第十八电阻、第十九电阻；

[0020] 所述主控芯片的电源启动脚、所述第一二极管的正极和所述第六电容的第一端共接，所述第一二极管的负极接 +1.2V 电源，所述第六电容的第二端接地，所述主控芯片的过电压保护输入脚通过串联的所述第十二电阻和所述电阻接所述第二稳压二极管的负极，所述第二稳压二极管的负极通过所述第十三电阻接 +5V 电源，所述第二稳压二极管的正极接地，所述主控芯片的电流检测输入脚、所述第十七电阻的第二端、所述第十八电阻的第二端和所述第十九电阻的第二端共接于地，所述主控芯片的电流回路脚接所述第十六电阻的第一端，所述第十六电阻的第二端、所述第十七电阻的第一端、所述第十八电阻的第一端和所述第十九电阻的第一端共接于所述第一 MOS 管的源极，所述第一 MOS 管的栅极接所述第十四电阻的第二端，所述第十四电阻的第一端、所述第十五电阻的第一端和所述主控芯片的驱动输出脚共接，所述第十五电阻的第二端接地，所述第一 MOS 管的漏极、所述第一稳压二极管的正极、所述第十电阻的第一端和所述第一电感的第二端共接，所述第一稳压二极管的负极、所述第十一电容的第一端、所述第十三电容的第一端和所述第十五电容的正极共接于所述第二稳压二极管的负极，所述第十一电容的第二端接所述第十二电容的第一端，所述第十三电容接所述第十四电容的第一端，所述第十二电容的第二端、所述第十四电容的第二端和所述第十五电容的负极共接于地，所述第一电感的第一端、所述第八电容的第一端和所述第七电容的正极共接于 +12V 电源，所述第七电容的负极和所述第八电容的第二端共接于地，所述第十电阻的第二端通过串联的所述第十电容和所述第九电容接地；

[0021] 所述电流电压检测单元包括第二十电阻、第二十一电阻、第二十二电阻、第二十三电阻、第二十四电阻、第十六电容、第二十五电阻、第二 MOS 管、第二十六电阻、第三 MOS 管、第二十七电阻、第四 MOS 管、第二十八电阻、第五 MOS 管、第二十九电阻；

[0022] 所述主控芯片的环路补偿脚接所述第二十四电阻的第二端，所述第二十四电阻的第一端接所述第十六电容的第二端，所述主控芯片的第一 DRV 电流检测脚接所述第二十三电阻的第二端，所述主控芯片的第二 DRV 电流检测脚接所述第二十二电阻的第二端，所述主控芯片的第三 DRV 电流检测脚接所述第二十一电阻的第二端，所述主控芯片的第四 DRV

电流检测脚接所述第二十电阻的第二端，所述第二十电阻的第一端、所述第二十一电阻的第一端、所述第二十二电阻的第一端、所述第二十三电阻的第一端和所述第十六电容的第一端共接于地，所述主控芯片的第四电流控制脚接所述第二 MOS 管的源极，所述主控芯片的第四电压检测脚接所述第二十六电阻的第二端，所述主控芯片的第三电流控制脚接所述第三 MOS 管的源极，所述主控芯片的第三电压检测脚接所述第二十七电阻的第二端，所述主控芯片的第二电流控制脚接所述第四 MOS 管的源极，所述主控芯片的第二电压检测脚接所述第二十八电阻的第二端，所述主控芯片的第一电流控制脚接所述第五 MOS 管的源极，所述主控芯片的第一电压检测脚接所述第二十九电阻的第二端，所述第二 MOS 管、所述第三 MOS 管、所述第四 MOS 管、所述第五 MOS 管和所述第二十五电阻的第二端共接，所述第二十五电阻的第一端接 +5V 电源，所述第二十六电阻的第一端、所述第二十七电阻的第一端、所述第二十八电阻的第一端和所述第二十九电阻的第一端分别接所述第二 MOS 管的漏极、所述第三 MOS 管的漏极、所述第四 MOS 管的漏极和所述第五 MOS 管的漏极。

[0023] 进一步的，所述 VGA 接口模块包括 VGA 接口单元、第一 ESD 保护单元和存储单元；

[0024] 所述 VGA 接口单元包括 VGA 接口、第三十电阻、第三十一电阻和第十七电容；

[0025] 所述 VGA 接口的红色分量信号脚、绿色分量信号脚和蓝色分量信号脚共接于地，所述 VGA 接口的地脚、所述第十七电容的第一端和所述第三十一电阻的第一端共接，所述第十七电容的第二端接地，所述第三十一电阻的第二端、所述第三十电阻的第二端和所述主控芯片的第五 C 输入输出脚共接；

[0026] 所述第一 ESD 保护单元包括第一 ESD 保护芯片、第二 ESD 保护芯片、第三十二电阻、第三十三电阻、第三十四电阻、第三十五电阻、第三十六电阻、第三十七电阻、第三十八电阻、第三十九电阻、第四十电阻、第四十一电阻、第四十二电阻、第四十三电阻、第四十四电阻、第十八电容、第十九电容、第二十电容、第二十一电容、第二十二电容、第二十三电容、第二十四电容、第二十五电容、第二十六电容、第二十七电容、第二十八电容、第二十九电容、第二电感、第三电感和第四电感；

[0027] 所述第一 ESD 保护芯片的电源脚与所述第二十八电容的第二端共接于所述第三十电阻的第一端，所述第二十八电容的第一端和所述 ESD 保护芯片的地端共接于地，所述 ESD 保护芯片的第一输入输出脚、所述第三十二电阻的第一端和所述第二电感的第一端共接于所述 VGA 接口的蓝色分量信号脚，所述第二电感的第二端通过串联的所述第三十三电阻和所述第十八电容接所述主控芯片的蓝色分量信号正输入脚，所述第三十二电阻的第二端和所述第三十四电阻的第一端共接于地，所述第三十四电阻的第二端通过所述第十九电容接所述主控芯片的蓝色分量信号负输入脚，所述 ESD 保护芯片的第三输入输出脚、所述第三十五电阻的第一端和所述第三电感的第一端共接于所述 VGA 接口的绿色分量信号脚，所述第三电感的第二端通过串联的所述第三十六电阻和所述第二十电容接所述主控芯片的绿色分量信号正输入脚，所述第三十五电阻的第二端和所述第三十七电阻的第一端共接于地，所述第三十七电阻的第二端通过所述第二十一电容接所述主控芯片的绿色分量信号负输入脚，所述 ESD 保护芯片的第四输入输出脚、所述第三十八电阻的第一端和所述第四电感的第一端共接于所述 VGA 接口的红色分量信号脚，所述第四电感的第二端通过串联的所述第三十九电阻和所述第二十二电容接所述主控芯片的红色分量信号正输入脚，所述第三十八电阻的第二端和所述第四十电阻的第一端共接于地，所述第四十电阻的

第二端通过所述第二十三电容接所述主控芯片的红色分量信号负输入脚，所述第二 ESD 保护芯片的第四输入输出脚、所述第四十一电阻的第一端、所述第二十四电容的第一端和所述第四十二电阻的第一端共接于所述 VGA 接口的行同步信号脚，所述第四十一电阻的第二端、所述第二十四电容的第二端和所述第二十五电容的第二端共接于地，所述第四十二电阻的第二端和所述第二十五电容的第一端共接于所述主控芯片的行同步信号输入脚，所述第二 ESD 保护芯片的第三输入输出脚、所述第四十三电阻的第一端、所述第二十六电容的第一端和所述第四十四电阻的第一端共接于所述 VGA 接口的场同步信号脚，所述第四十三电阻的第二端、所述第二十六电容的第二端和所述第二十七电容的第二端共接于地，所述第四十四电阻的第二端和所述第二十七电容的第一端共接于所述主控芯片的场同步信号输入脚，所述第二 ESD 保护芯片的地脚接地，所述第二 ESD 保护芯片的电源脚通过所述第二十九电容接地，所述第二 ESD 保护芯片的第一输入输出脚和第二输入输出脚接所述存储单元；

[0028] 所述存储单元包括第一存储芯片、第四十五电阻、第四十六电阻、第四十七电阻、第四十八电阻、第四十九电阻、第五十电阻、第三十电容、第二二极管、第三二极管和第三双向稳压二极管；

[0029] 所述第一存储芯片的电源脚、所述第三十电容的第一端、所述第二二极管的负极、所述第三二极管的负极、所述第四十九电阻的第一端、所述第四十八电阻的第一端和所述第四十七电阻的第一端共接于所述第二 ESD 保护芯片的电源脚，所述第二二极管的正极接所述 VGA 接口的电源脚，所述第三二极管的正极与所述第三双向稳压二极管的负极共接于 +5V 电源，所述第三双向稳压二极管的负极接地，所述第一存储芯片的写保护脚接所述第五十电阻的第二端，所述第五十电阻的第一端和所述第四十九电阻的第二端共接于所述主控芯片的第三 A 输入输出脚，所述第一存储芯片的 I2C 总线时钟脚、所述第四十八电阻的第二端、所述第四十五电阻的第二端和所述第二 ESD 保护芯片的第二输入输出脚共接于所述主控芯片的第四 B 输入输出脚，所述第一存储芯片的 I2C 总线数据脚、所述第四十七电阻的第二端、所述第四十六电阻的第二端、所述第二 ESD 保护芯片的第一输入输出脚共接于所述主控芯片的第五 B 输入输出脚，所述第四十五电阻的第一端和所述第四十六电阻的第一端分别接所述 VGA 接口的 I2C 总线数据脚和 I2C 总线时钟脚，所述第一存储芯片的地脚和所述第三十电容的第二端接地。

[0030] 进一步的，所述 HDMI 接口模块包括 HDMI 接口、第二 ESD 保护单元和第二存储单元；

[0031] 所述第二 ESD 保护单元包括第三 ESD 保护芯片、第四 ESD 保护芯片、第五 ESD 保护芯片、第三十一电容、第一双向稳压二极管、第五十一电阻、第五十二电容、第二双向稳压二极管、第三十二电容、第三双向稳压二极管、第三十三电容、第四稳压二极管、第五十三电阻和第六十电阻；

[0032] 所述 HDMI 接口的第三数据通道正脚、第三数据通道负脚、第二数据通道正脚和第二数据通道负脚分别接所述第三 ESD 保护芯片的第一输入脚、第二输入脚、第三输入脚和第四输入脚，所述 HDMI 接口的第一数据通道正脚、第一数据通道负脚、时钟通道正脚和时钟通道负脚分别接所述第四 ESD 保护芯片的第一输入脚、第二输入脚、第三输入脚和第四输入脚，所述 HDMI 接口的第二地脚、第一地脚、第零地脚和第四地脚接地，所述第三 ESD 保

护芯片的第一输出脚、第二输出脚、第三输出脚和第四输出脚分别接所述主控芯片的第三 TDMS 数据通道正脚、第三 TDMS 数据通道负脚、第二 TDMS 数据通道正脚和第二 TDMS 数据通道负脚，所述第四 ESD 保护芯片的第一输出脚、第二输出脚、第三输出脚和第四输出脚分别接所述主控芯片的第一 TDMS 数据通道正脚、第一 TDMS 数据通道负脚、TDMS 时钟通道正脚和 TDMS 时钟通道负脚，所述 HDMI 接口的第三地脚、所述第五 ESD 保护芯片的第二输入输出脚、所述第三十一电容的第一端、所述第一双向稳压二极管的第一端和所述第五十一电阻的第一端共接，所述第三十一电容的第二端和所述第一双向稳压二极管的第二端共接于地，所述第五十一电阻的第二端和所述第五十二电阻的第一端共接于所述主控芯片的第四 C 输入输出脚，所述第五十二电阻的第二端、所述第三十二电容的第二端和所述第五 ESD 保护芯片的地脚共接于地，所述第五 ESD 保护芯片的电源端接所述第三十二电容的第一端，所述 HDMI 接口的电源脚、所述第三双向稳压二极管的第一端、所述第三十三电容的第一端、所述第四稳压二极管的第一端和所述第五十三电阻的第一端共接于所述第二存储模块，所述 HDMI 接口的热插拔检测脚、所述第二双向稳压二极管的第一端、所述第三十二电容的第一端和所述第五十三电阻的第二端共接于所述第六十电阻的第一端，所述第六十电阻的第二端接所述主控芯片的第五 A 输入输出脚，所述第二双向稳压二极管的第二端、所述第三十二电容的第二端、所述第三双向稳压二极管的第二端、所述第三十三电容的第二端和所述第四稳压二极管的第二端共接于地；

[0033] 所述第二存储单元包括第二存储芯片、第四二极管、第五二极管、第五稳压二极管、第三十四电容、第五十四电阻、第五十五电阻、第五十六电阻、第五十七电阻、第五十八电阻、第五十九电阻、第四双向稳压二极管和第五双向稳压二极管；

[0034] 所述第二存储芯片的电源脚、所述第三十四电容的第一端、所述第四二极负极、所述第五二极管的负极、所述第五十六电阻的第一端、所述第五十五电阻的第一端和所述第五十四电阻的第一端共接于所述第五十二电阻的第二端，所述第四二极管的正极接所述第五十三电阻的第一端，所述第五二极管的正极和所述第五稳压二极管的负极共接于 +5V 电源，所述第五稳压二极管的正极接地，所述第三十四电容的第二端和所述第二存储芯片的地脚共接于地，所述第二存储芯片的写保护脚接所述第五十七电阻的第二端，所述第五十七电阻的第一端和所述第五十六电阻的第二端共接于所述主控芯片的第三 A 输入输出脚，所述第二存储芯片的 I2C 时钟脚、所述第五十五电阻的第二端和所述第五十八电阻的第二端共接于所述主控芯片的第六 B 输入输出脚，所述第二存储芯片的 I2C 总线数据脚和所述第五十九电阻的第二端共接于所述主控芯片的第七 B 输入输出脚，所述第五十八电阻的第一端、所述第五双向稳压二极管的第一端和所述第五 ESD 保护芯片的第二输入输出脚共接于所述 HDMI 接口的 I2C 总线时钟端，所述第五十九电阻的第一端、所述第四双向稳压二极管的第一端和所述第五 ESD 保护芯片的第三输入输出脚共接于所述 HDMI 接口的 I2C 总线数据脚。

[0035] 进一步的，所述音频输出模块包括音频放大芯片、第六十一电阻、第六十二电阻、第六十三电阻、第六十四电阻、第六十五电阻、第六十六电阻、第六十七电阻、第六十八电阻、第六十九电阻、第七十电阻、第七十一电阻、第七十二电阻、第七十三电阻、第三十五电容、第三十六电容、第三十七电容、第三十八电容、第三十九电容、第四十电容、第四十一电容、第四十二电容、第四十三电容、第四十四电容、第四十五电容、第四十六电容、第四十七

电容、第四十八电容、第四十九电容、第五十电容、第五十一电容、第五十二电容、第五十三电容、第五十四电容、第五十五电容、第五十六电容、第五电感、第六电感、第七电感和第八电感；

[0036] 所述音频放大芯片的左声道电源脚、所述第四十二电容的第一端和所述第四十一电容的第一端共接于 +5V 电源，所述音频放大芯片的左声道地脚、所述第四十一电容的第二端和所述第四十二电容的第二端共接于地，所述音频放大芯片的左声道输入脚和所述第四十三电容的第二端共接于所述第三十五电容的第二端，所述第三十五电容的第一端、所述第六十二电阻的第一端、所述第三十六电容的第一端和所述第六十一电阻的第二端共接，所述第六十一电阻的第一端接所述主控芯片的第一空置脚，所述第三十六电容的第二端和所述第六十二电阻的第二端共接于地，所述音频放大芯片的右声道输入脚和所述第四十四电容的第二端共接于所述第三十七电容的第二端，所述第三十七电容的第一端、所述第六十四电阻的第一端、所述第三十八电容的第一端和所述第六十三电阻的第二端共接，所述第六十三电阻的第一端接所述主控芯片的第二空置脚，所述第三十八电容的第二端和所述第六十四电阻的第二端共接于地，所述第四十三电容的第一端、所述第四十六电容的第一端、所述第六十八电阻的第一端、所述第六十五电阻的第二端和所述第三十九电容的第二端共接，所述第三十九电容的第一端接所述主控芯片的第三空置脚，所述第四十四电容的第一端、所述第四十五电容的第一端、所述第六十七电阻的第一端、所述第六十六电阻的第二端和所述第四十电容的第二端共接，所述第四十电容的第一端接所述主控芯片的第四空置脚，所述第六十七电阻的第二端、所述第六十八电阻的第二端、所述第四十五电容的第二端和所述第四十六电容的第二端共接于地，所述音频放大芯片的关断控制输入脚、所述第六十九电阻的第二端和所述第四十七电容的第一端共接，所述第六十九电阻的第一端和所述第七十电阻的第一端共接于所述主控芯片的第七 C 输入输出脚，所述音频放大芯片的模拟信号参考脚接所述第四十八电容的第一端，所述音频放大芯片的地脚、所述第四十八电容的第二端、所述第四十七电容第二端和所述第七十电阻的第二端共接于地，所述音频放大芯片的右声道电源脚、所述第四十九电容的第一端和所述第五十电容的第一端共接于 +5V 电源，所述音频放大芯片的右声道地脚、所述第四十九电容的第二端和所述第五十电容的第二端共接于地，所述音频放大芯片的左声道负输出脚、左声道正输出脚、右声道负输出脚和右声道正输出脚分别接第五电感的第一端、第六电感的第一端、第七电感的第一端和第八电感的第一端，所述第五电感的第二端、第六电感的第二端、第七电感的第二端和第八电感的第二端分别接所述第五十一电容的第一端、第五十二电容的第一端、第五十三电容的第一端和第五十四电容的第一端，所述第五十一电容的第二端、第五十二电容的第二端、第五十三电容的第二端和第五十四电容的第二端共接于地，所述音频放大芯片的 DC 音量控制脚、所述第五十六电容的第一端和所述第七十一电阻的第一端共接，所述第七十一电阻的第二端和所述第七十三电阻的第一端共接于所述主控芯片的第零 C 输入输出脚，所述音频放大芯片的电源脚、所述第五十五电容的第一端和所述第七十二电阻的第一端共接，所述第七十二电阻的第二端和所述第七十三电阻的第二端共接于 +5V 电源，所述第五十五电容的第二端和所述第五十六电容的第二端共接于地。

[0037] 进一步的，所述接屏模块包括插排、屏幕开关控制芯片、第九电感、第十电感、第十一电感、第七十四电阻、第七十五电阻、第七十六电阻、第七十七电阻、第七十八电阻、第

五十七电容、第五十八电容、第五十九电容、第六十电容、第一三极管和第六 MOS 管；

[0038] 所述插排的第一输入脚至第二十输入脚均接所述主控芯片，所述插排的电源脚接 LCD 正电源，所述插排的地脚接地，所述第一三极管的基极、所述第七十六电阻的第二端和所述第五十八电容的第一端共接，所述第七十六电阻的第一端和所述第七十七电阻的第一端共接于所述主控芯片的第六 C 输入输出端，所述第七十七电阻的第二端和所述第五十八电容的第二端共接于地，所述第一三极管的发射极接地，所述第一三极管的集电极、所述第七十四电阻的第二端和所述第七十五电阻共接，所述第七十四电阻的第一端、所述第五十七电容的第一端、所述屏幕开关控制芯片的第一至第三输入脚共接共接于所述第六 MOS 管的源极，所述第十一电感的第二端、所述第十电感的第二端和所述第九电感的第二端共接，所述第十一电感的第一端、所述第十电感的第一端和所述第九电感的第一端分别接 +5V 电源、+3.3V 电源和 +12V 电源，所述第七十五电阻的第二端、所述屏幕开关控制芯片的地脚和所述第六 MOS 管的栅极共接，所述第六 MOS 管的漏极、所述第五十九电容的正极、所述第六十电容的第一端和所述第七十八电阻的第一端共接，所述第五十九电容的负极、所述第六十电容的第二端和所述第七十八电阻的第二端共接于地。

[0039] 进一步的，所述电源模块提供的电源包括 +12V 电源、+5V 电源、+3.3V 电源和 +1.2V 电源。

[0040] 在本实用新型的实施例中，所述液晶显示屏控制电路包括 VGA 接口模块、HDMI 接口模块、主控模块、音频输出模块、接屏模块和电源模块，所述 VGA 接口模块接收电脑或上位机输出的模拟视频图像信息，所述 HDMI 接口模块接收电脑或上位机输出的数字视频图像信息，所述主控模块将所述模拟视频图像信息或数字视频图像信息进行处理后输出至音频输出模块和接屏模块，进行音频的输出和视频图像信息的显示。本实用新型在传统液晶显示屏控制电路的基础上，减少了一个背光驱动芯片，节简了外围电路，大大节约了 PCB 板的空间，降低了成本，且提高了电路的稳定性。

## 附图说明

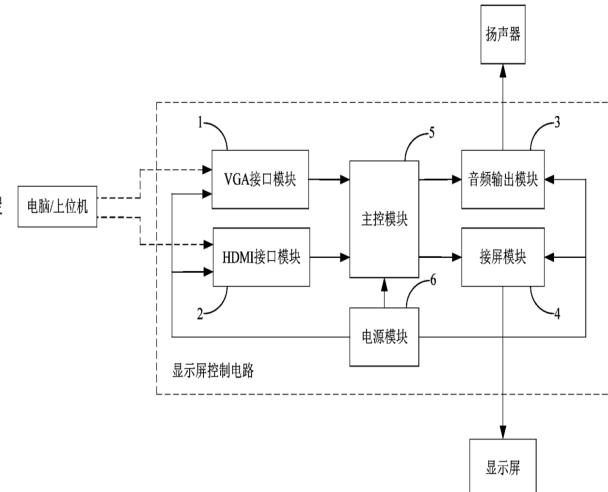

[0041] 图 1 是本实用新型实施例提供的液晶显示屏控制电路的模块图；

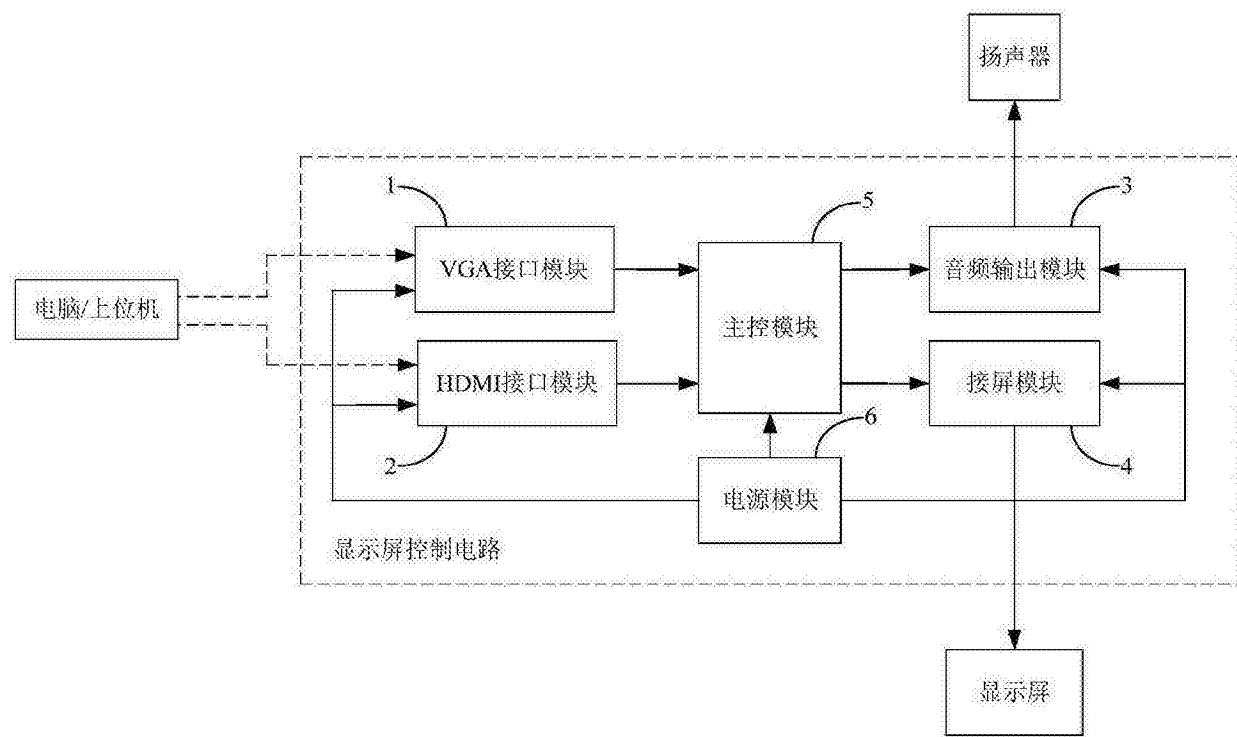

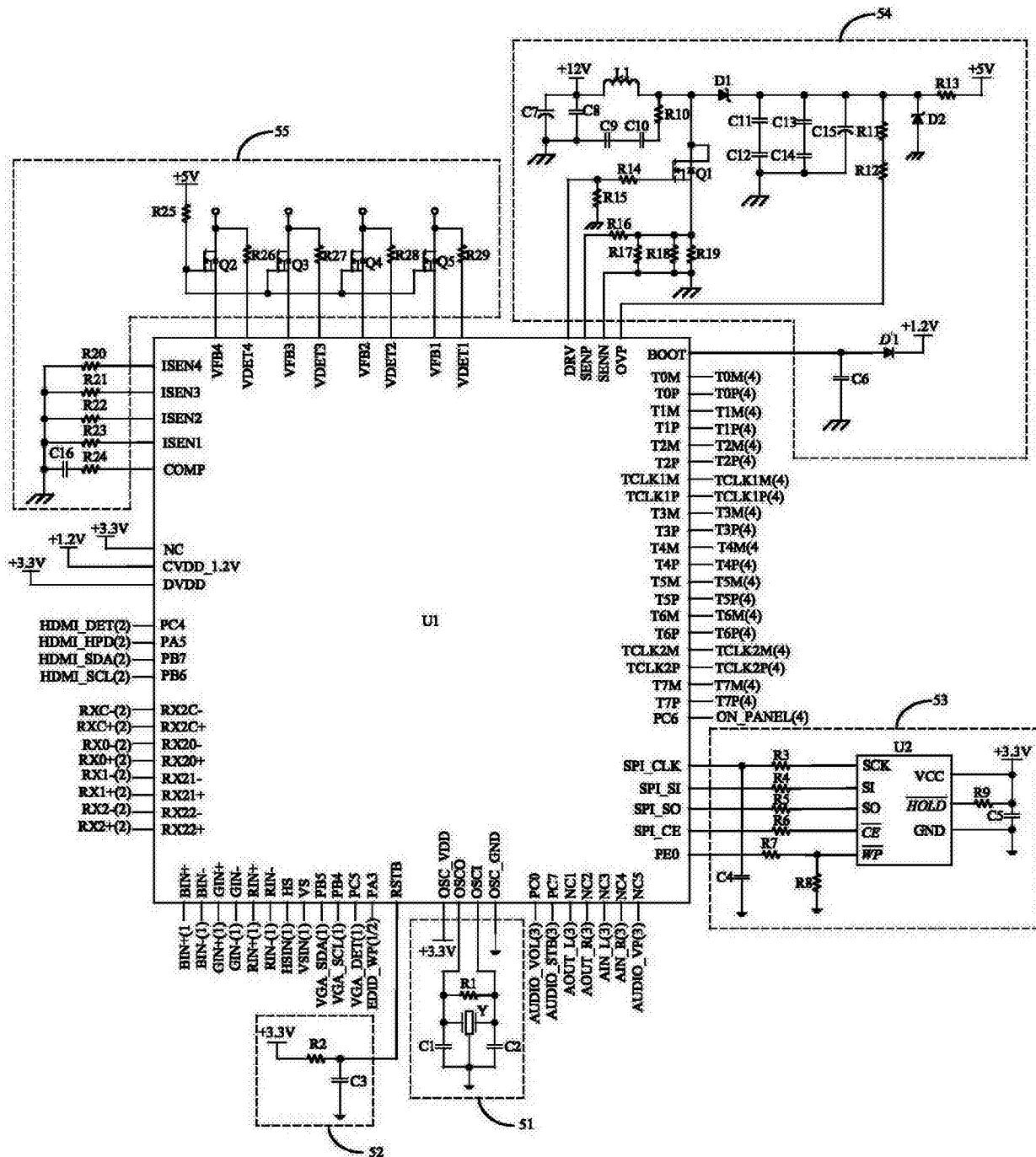

[0042] 图 2 是本实用新型实施例提供的液晶显示屏控制电路主控模块的电路图；

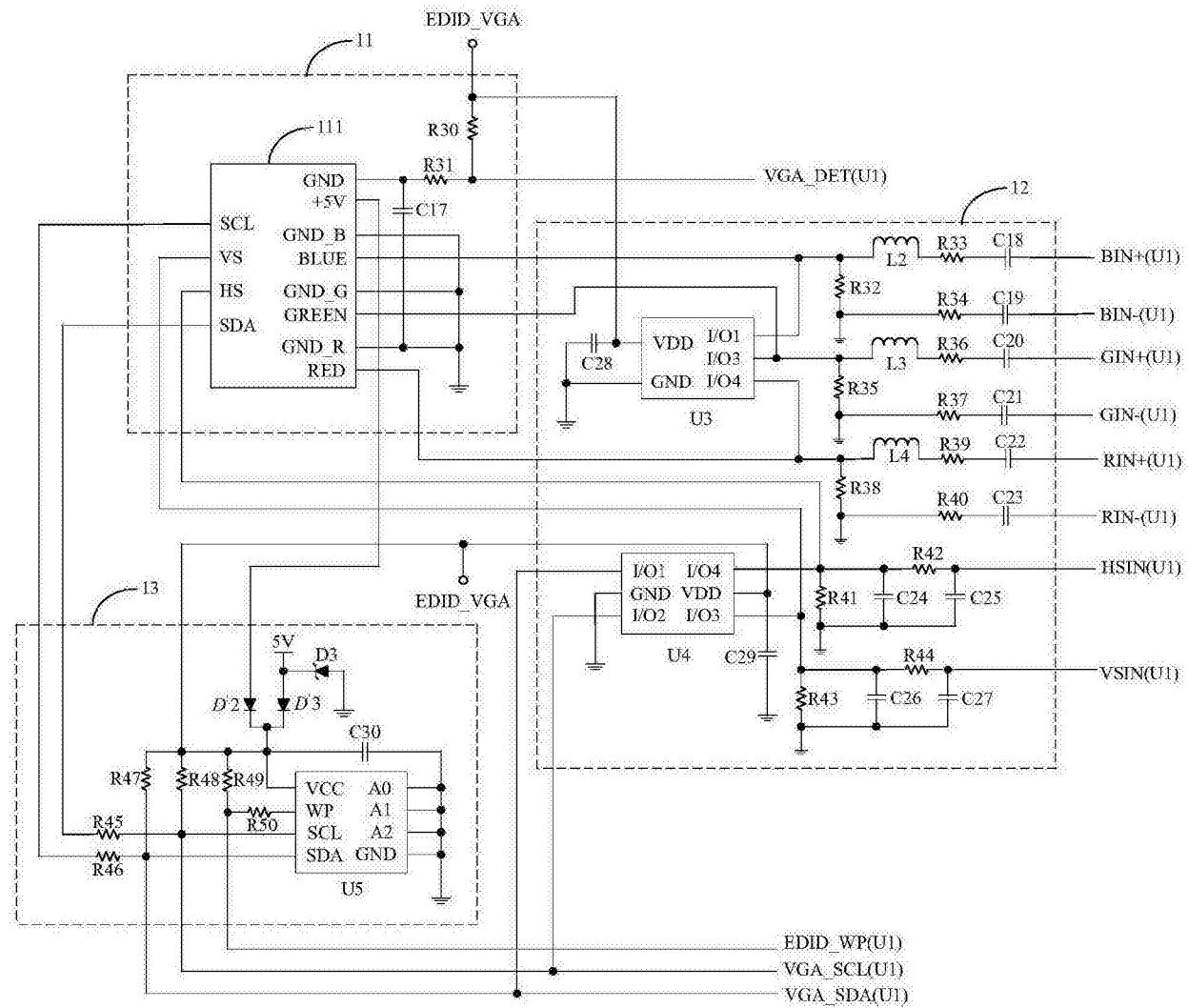

[0043] 图 3 是本实用新型实施例提供的液晶显示屏控制电路 VGA 接口模块的电路图；

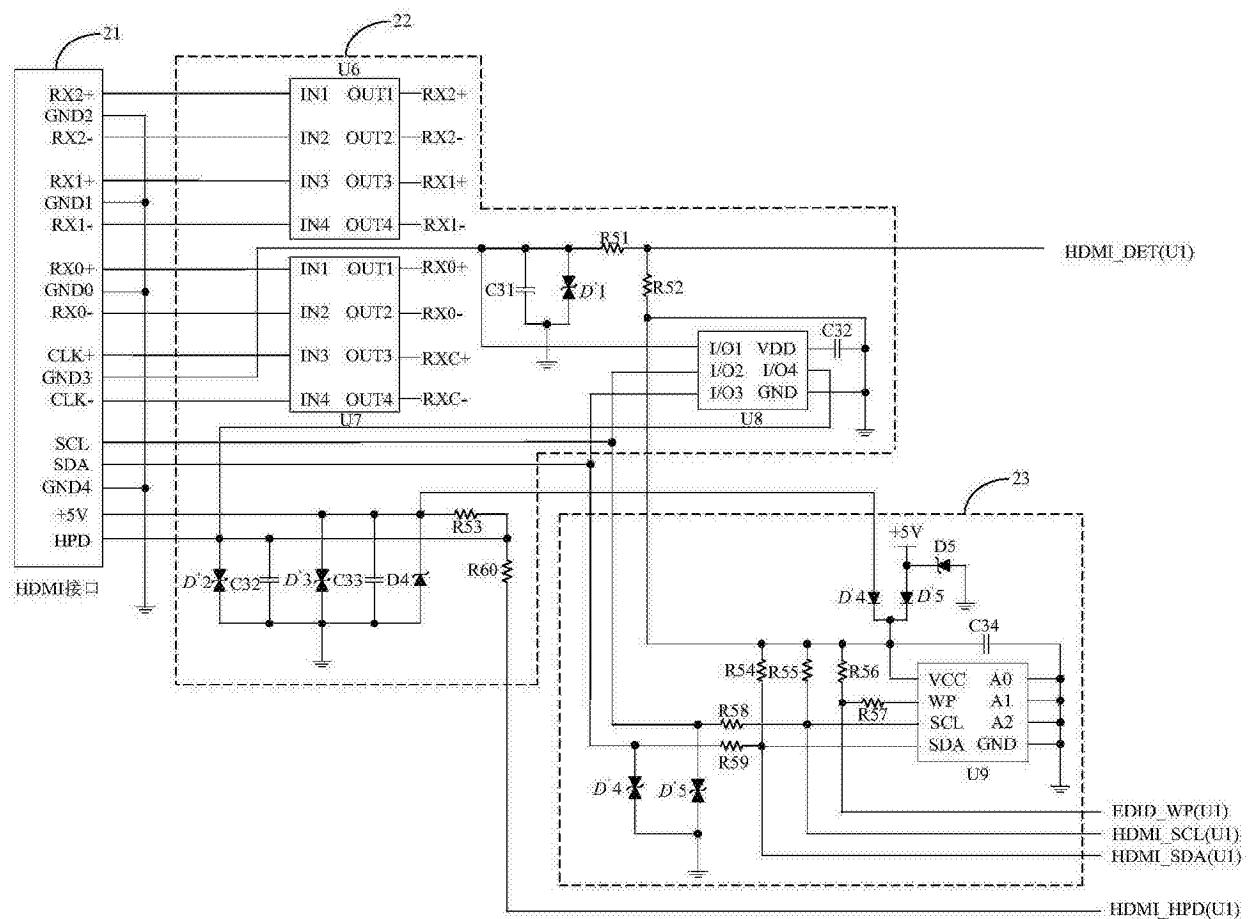

[0044] 图 4 是本实用新型实施例提供的液晶显示屏控制电路 HDMI 接口模块的电路图；

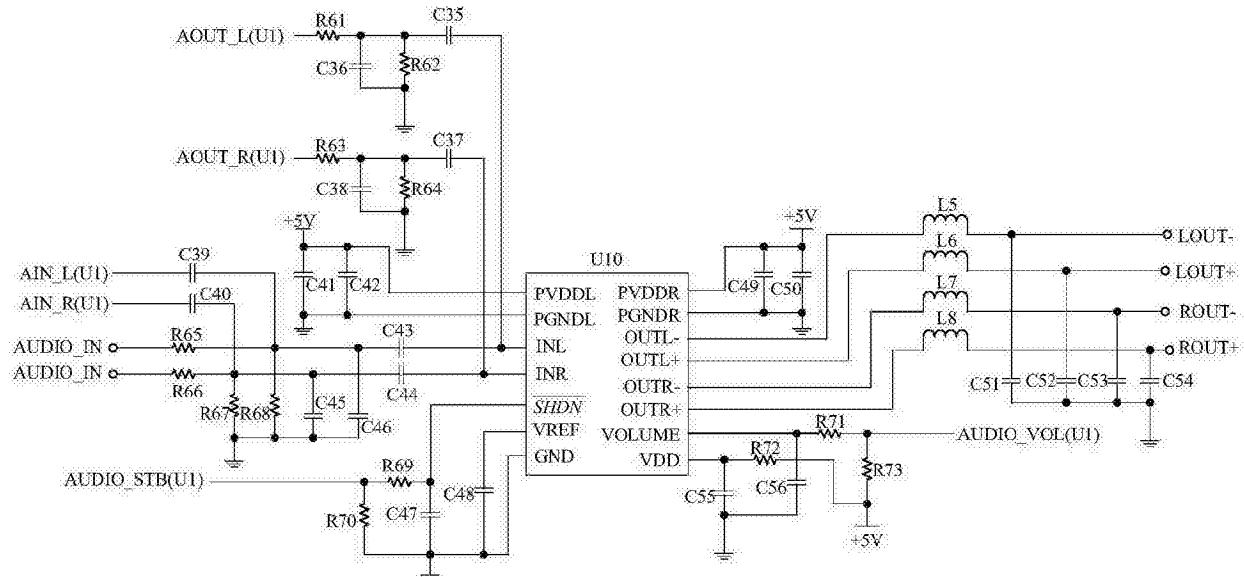

[0045] 图 5 是本实用新型实施例提供的液晶显示屏控制电路音频输出模块的电路图；

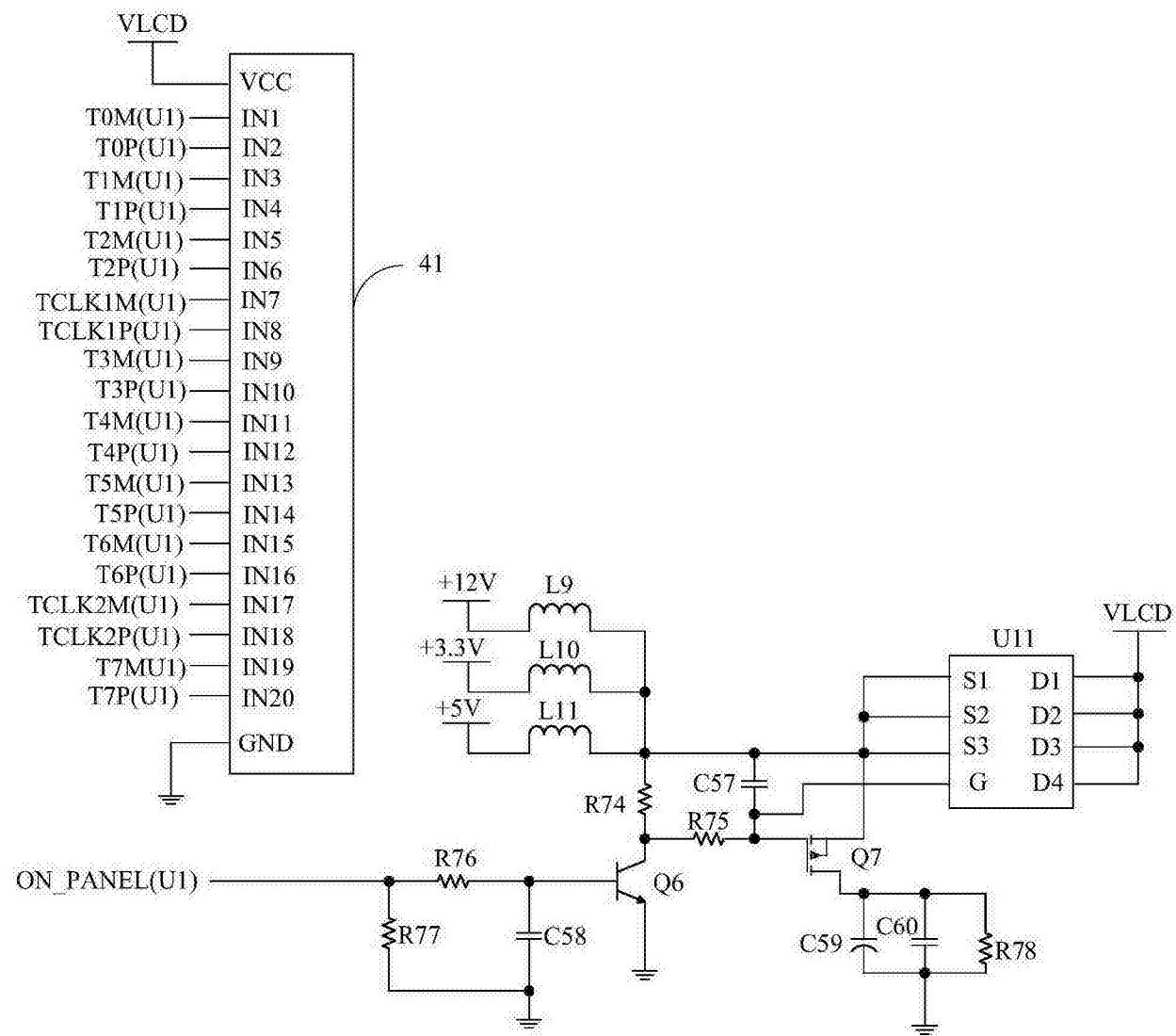

[0046] 图 6 是本实用新型实施例提供的液晶显示屏控制电路接屏模块的电路图。

## 具体实施方式

[0047] 为了使本实用新型的目的、技术方案及优点更加清楚明白，以下结合附图及实施例，对本实用新型进行进一步详细说明。应当理解，此处所描述的具体实施例仅仅用以解释本实用新型，并不用于限定本实用新型。

[0048] 图 1 示出了本实用新型实施例提供的液晶显示屏控制电路的结构图。为了便于说明，仅示出了与本实用新型实施例相关的部分。

[0049] 一种液晶显示屏控制电路，所述液晶显示屏控制电路包括：

[0050] 接收电脑或上位机输出的模拟视频图像信息的 VGA(Video Graphics Array, 视频图形阵列) 接口模块 1；

[0051] 接收电脑或上位机输出的数字视频图像信息的 HDMI(High Definition Multimedia Interface, 高清晰度多媒体) 接口模块 2；

[0052] 输出端与扬声器连接,输出音频的音频输出模块 3；

[0053] 输出端与显示屏连接,输出视频图像的接屏模块 4；

[0054] 输入端与 VGA 接口模块 1 和 HDMI 接口模块 2 的输出端连接,输出端与音频输出模块 3 和接屏模块 4 的输入端连接,将所述模拟视频图像信息或所述数字视频图像信息进行处理并输出至音频输出模块 3 和接屏模块 4 进行音频输出和视频图像显示的主控模块 5；

[0055] 分别与 VGA 接口模块 1、HDMI 接口模块 2、音频输出模块 3、接屏模块 4 和主控模块 5 连接,为整个电路供电的电源模块 6。

[0056] 图 2 示出了本实用新型实施例提供的液晶显示屏控制电路主控模块的电路图。为了便于说明,仅示出了与本实用新型实施例相关的部分。

[0057] 作为本实用新型的一实施例,主控模块 5 包括主控芯片 U1、晶振单元 51、复位单元 52、闪存单元 53、背光驱动单元 54 以及电流电压检测单元 55；

[0058] 晶振单元 51 包括第一电阻 R1、晶体振荡器 Y、第一电容 C1 和第二电容 C2；

[0059] 主控芯片 U1 的振荡器输出脚 OSCO、第一电阻 R1 的第一端、晶体振荡器 Y 的第一端和第一电容 C1 的第一端共接,主控芯片 U1 的振荡器输入脚 OSCI、第一电阻 R1 的第二端、晶体振荡器 Y 的第二端和第二电容 C2 的第一端共接,第一电容 C1 的第二端、第二电容 C2 的第二端和晶体振荡器 Y 的第三端共接于地,主控芯片 U1 的振荡器电源脚 OSC\_VDD 接 +3.3V 电源,主控芯片 U1 的振荡器地脚 OSC\_GND 接地；

[0060] 复位单元 52 包第二电阻 R2 和第三电容 C3；

[0061] 主控芯片 U1 的复位脚 RSTB、第二电阻 R2 的第二端和第三电容 C3 的第一端共接,第二电阻 R2 的第一端接 +3.3V 电源,第三电容 C3 的第二端接地；

[0062] 闪存单元 53 包括闪存芯片 U2、第三电阻 R3、第四电阻 R4、第五电阻 R5、第六电阻 R6、第七电阻 R7、第八电阻 R8、第九电阻 R9、第四电容 C4 和第五电容 C5；

[0063] 主控芯片 U1 的 SPI(Serial Peripheral Interface, 串行外设接口) 总线时钟脚 SPI\_CLK、第三电阻 R3 的第一端和第四电容 C4 的第一端共接,第四电容 C4 的第二端接地,第三电阻 R3 的第二端接闪存芯片 U2 的串行数据时钟脚 SCK,主控芯片 U1 的 SPI 总线数据输入脚 SPI\_SI 通过第四电阻 R4 接闪存芯片 U2 的串行数据输入脚 SI,主控芯片 U1 的 SPI 总线数据输出脚 SPI\_SO 通过第五电阻 R5 接闪存芯片 U2 的串行数据输出脚 SO,主控芯片 U1 的 SPI 总线使能脚 SPI\_CE 通过第七电阻 R7 接闪存芯片 U2 的使能脚  $\overline{CE}$ ,主控芯片 U1 的第零 E 输入输出脚 PE0 接第七电阻 R7 的第一端,第七电阻 R7 的第二端、第八电阻 R8 的第一端和闪存芯片 U2 的写保护脚  $\overline{WP}$  共接,第八电阻 R8 的第二端接地,闪存芯片 U2 的电源脚 VCC、第九电阻 R9 的第二端和第五电容 C5 的第一端共接于 +3.3V 电源,闪存芯片 U2 的保持脚  $\overline{HOLD}$  接第九电阻 R9 的第一端,闪存芯片 U2 的地脚 GND 和第五电阻 R5 的第二端共接于地；

[0064] 背光驱动单元 54 包括第一二极管 D'1、第六电容 C6、第七电容 C7、第八电容 C8、第

九电容 C9、第十电容 C10、第一电感 L1、第十电阻 R10、第一稳压二极管 D1、第十一电容 C11、第十二电容 C12、第十三电容 C13、第十四电容 C14、第十五电容 C15、第十一电阻 R11、第十二电阻 R12、第二稳压二极管 D2、第十三电阻 R13、第一 MOS 管 Q1、第十四电阻 R14、第十五电阻 R15、第十六电阻 R16、第十七电阻 R17、第十八电阻 R18、第十九电阻 R19；

[0065] 主控芯片 U1 的电源启动脚 BOOT、第一二极管 D'1 的正极和第六电容 C6 的第一端共接，第一二极管 D'1 的负极接 +1.2V 电源，第六电容 C6 的第二端接地，主控芯片 U1 的过电压保护输入脚 OVP 通过串联的第十二电阻 R12 和电阻接第二稳压二极管的负极，第二稳压二极管 D2 的负极通过第十三电阻 R13 接 +5V 电源，第二稳压二极管 D2 的正极接地，主控芯片 U1 的电流检测输入脚 SENN、第十七电阻 R17 的第二端、第十八电阻 R18 的第二端和第十九电阻 R19 的第二端共接于地，主控芯片 U1 的电流回路脚 SENP 接第十六电阻 R16 的第一端，第十六电阻 R16 的第二端、第十七电阻 R17 的第一端、第十八电阻 R18 的第一端和第十九电阻 R19 的第一端共接于第一 MOS 管 Q1 的源极，第一 MOS 管 Q1 的栅极接第十四电阻 R14 的第二端，第十四电阻 R14 的第一端、第十五电阻 R15 的第一端和主控芯片 U1 的驱动输出脚 DRV 共接，第十五电阻 R15 的第二端接地，第一 MOS 管 Q1 的漏极、第一稳压二极管 D1 的正极、第十电阻 R10 的第一端和第一电感 L1 的第二端共接，第一稳压二极管 D1 的负极、第十一电容 C11 的第一端、第十三电容 C13 的第一端和第十五电容 C15 的正极共接于第二稳压二极管 D2 的负极，第十一电容 C11 的第二端接第十二电容 C12 的第一端，第十三电容 C13 接第十四电容 C14 的第一端，第十二电容 C12 的第二端、第十四电容 C14 的第二端和第十五电容 C15 的负极共接于地，第一电感 L1 的第一端、第八电容 C8 的第一端和第七电容 C7 的正极共接于 +12V 电源，第七电容 C7 的负极和第八电容 C8 的第二端共接于地，第十电阻 R10 的第二端通过串联的第十电容 C10 和第九电容 C9 接地；

[0066] 电流电压检测单元包括第二十电阻 R20、第二十一电阻 R21、第二十二电阻 R22、第二十三电阻 R23、第二十四电阻 R24、第十六电容 C16、第二十五电阻 R25、第二 MOS 管 Q2、第二十六电阻 R26、第三 MOS 管 Q3、第二十七电阻 R27、第四 MOS 管 Q4、第二十八电阻 R28、第五 MOS 管 Q5、第二十九电阻 R27；

[0067] 主控芯片 U1 的环路补偿脚 COMP 接第二十四电阻 R24 的第二端，第二十四电阻 R24 的第一端接第十六电容 C16 的第二端，主控芯片 U1 的第一 DRV 电流检测脚 ISEN1 接第二十三电阻 R23 的第二端，主控芯片 U1 的第二 DRV 电流检测脚 ISEN2 接第二十二电阻 R22 的第二端，主控芯片 U1 的第三 DRV 电流检测脚 ISEN3 接第二十一电阻 R21 的第二端，主控芯片 U1 的第四 DRV 电流检测脚 ISEN4 接第二十电阻 R20 的第二端，第二十电阻 R20 的第一端、第二十一电阻 R21 的第一端、第二十二电阻 R22 的第一端、第二十三电阻 R23 的第一端和第十六电容 C16 的第一端共接于地，主控芯片 U1 的第四电流控制脚 VFB4 接第二 MOS 管 Q2 的源极，主控芯片 U1 的第四电压检测脚 VDET4 接第二十六电阻 R26 的第二端，主控芯片 U1 的第三电流控制脚 VFB3 接第三 MOS 管 Q3 的源极，主控芯片 U1 的第三电压检测脚 VDET3 接第二十七电阻 R27 的第二端，主控芯片 U1 的第二电流控制脚 VFB2 接第四 MOS 管 Q4 的源极，主控芯片 U1 的第二电压检测脚 VDET2 接第二十八电阻 R28 的第二端，主控芯片 U1 的第一电流控制脚 VFB1 接第五 MOS 管 Q5 的源极，主控芯片 U1 的第一电压检测脚 VDET1 接第二十九电阻 R27 的第二端，第二 MOS 管 Q2 的栅极、第三 MOS 管 Q3 的栅极、第四 MOS 管 Q4 的栅极、第五 MOS 管 Q5 的栅极和第二十五电阻 R25 的第二端共接，第二十五电阻 R25 的第一

端接 +5V 电源,第二十六电阻 R26 的第一端、第二十七电阻 R27 的第一端、第二十八电阻 R28 的第一端和第二十九电阻 R27 的第一端分别接第二 MOS 管 Q2 的漏极、第三 MOS 管 Q3 的漏极、第四 MOS 管 Q4 的漏极和第五 MOS 管 Q5 的漏极。

[0068] 图 3 示出了本实用新型实施例提供的液晶显示屏控制电路 VGA 接口模块的电路图。为了便于说明,仅示出了与本实用新型实施例相关的部分。

[0069] 作为本实用新型的一实施例,VGA 接口模块 1 包括 VGA 接口单元 11、第一 ESD(Electro-Static discharge, 静电释放) 保护单元 12 和第一存储单元 13;

[0070] VGA 接口单元 11 包括 VGA 接口 111、第三十电阻 R30、第三十一电阻 R31 和第十七电容 C17;

[0071] VGA 接口 111 的红色分量信号地脚 GND\_R、绿色分量信号地脚 GND\_G 和蓝色分量信号地脚 GND\_B 共接于地,VGA 接口的地脚 GND、第十七电容 C17 的第一端和第三十一电阻 R31 的第一端共接,第十七电容 C17 的第二端接地,第三十一电阻 R31 的第二端、第三十电阻 R30 的第二端和主控芯片 U1 的第五 C 输入输出脚 PC5 共接;

[0072] 第一 ESD 保护单元 12 包括第一 ESD 保护芯片 U3、第二 ESD 保护芯片 U4、第三十二电阻 R32、第三十三电阻 R33、第三十四电阻 R34、第三十五电阻 R35、第三十六电阻 R36、第三十七电阻 R37、第三十八电阻 R38、第三十九电阻 R39、第四十电阻 R40、第四十一电阻 R41、第四十二电阻 R42、第四十三电阻 R43、第四十四电阻 R44、第十八电容 C18、第十九电容 C19、第二十电容 C20、第二十一电容 C21、第二十二电容 C22、第二十三电容 C23、第二十四电容 C24、第二十五电容 C25、第二十六电容 C26、第二十七电容 C27、第二十八电容 C28、第二十九电容 C29、第二电感 L2、第三电感 L3 和第四电感 L4;

[0073] 第一 ESD 保护芯片 U3 的电源脚 VDD 与第二十八电容 C28 的第二端共接于第三十电阻 R30 的第一端,第二十八电容 C28 的第一端和第一 ESD 保护芯片 U3 的地脚 GND 共接于地,第一 ESD 保护芯片的第一输入输出脚 I/01、第三十二电阻 R32 的第一端和第二电感 L2 的第一端共接于 VGA 接口 111 的蓝色分量信号脚 BLUE,第二电感 L2 的第二端通过串联的第三十三电阻 R33 和第十八电容 C18 接主控芯片 U1 的蓝色分量信号正输入脚 BIN+,第三十二电阻 R32 的第二端和第三十四电阻 R34 的第一端共接于地,第三十四电阻 R34 的第二端通过第十九电容 C19 接主控芯片 U1 的蓝色分量信号负输入脚 BIN-,第一 ESD 保护芯片 U3 的第三输入输出脚 I/03、第三十五电阻 R35 的第一端和第三电感 L3 的第一端共接于 VGA 接口 111 的绿色分量信号脚 GREEN,第三电感 L3 的第二端通过串联的第三十六电阻 R36 和第二十电容 C20 接主控芯片 U1 的绿色分量信号正输入脚 GIN+,第三十五电阻 R35 的第二端和第三十七电阻 R37 的第一端共接于地,第三十七电阻 R37 的第二端通过第二十一电容 C21 接主控芯片 U1 的绿色分量信号负输入脚 GIN-,第一 ESD 保护芯片的第四输入输出脚 I/04、第三十八电阻 R38 的第一端和第四电感 L4 的第一端共接于 VGA 接口 111 的红色分量信号脚 RED,第四电感 L4 的第二端通过串联的第三十九电阻 R39 和第二十二电容 C22 接主控芯片 U1 的红色分量信号正输入脚 RIN+,第三十八电阻 R38 的第二端和第四十电阻 R40 的第一端共接于地,第四十电阻 R40 的第二端通过第二十三电容 C23 接主控芯片 U1 的红色分量信号负输入脚 RIN-,第二 ESD 保护芯片 U4 的第四输入输出脚 I/04、第四十一电阻 R41 的第一端、第二十四电容 C24 的第一端和第四十二电阻 R42 的第一端共接于 VGA 接口 111 的行同步信号脚 HS,第四十一电阻 R41 的第二端、第二十四电容 C24 的第二端和第二十五电容

C25 的第二端共接于地,第四十二电阻 R42 的第二端和第二十五电容 C25 的第一端共接于主控芯片 U1 的行同步信号输入脚 HSIN,第二 ESD 保护芯片 U4 的第三输入输出脚 I/03、第四十三电阻 R43 的第一端、第二十六电容 C26 的第一端和第四十四电阻 R44 的第一端共接于 VGA 接口 111 的场同步信号脚 VS,第四十三电阻 R43 的第二端、第二十六电容 C26 的第二端和第二十七电容 C27 的第二端共接于地,第四十四电阻 R44 的第二端和第二十七电容 C27 的第一端共接于主控芯片 U1 的场同步信号输入脚 VSIN,第二 ESD 保护芯片 U4 的地脚接地,第二 ESD 保护芯片 U4 的电源脚 VDD 通过第二十九电容 C29 接地,第二 ESD 保护芯片 U4 的第一输入输出脚 I/01 和第二输入输出脚 I/02 接第一存储单元 13;

[0074] 第一存储单元 13 包括第一存储芯片 U5、第四十五电阻 R45、第四十六电阻 R46、第四十七电阻 R47、第四十八电阻 R48、第四十九电阻 R49、第五十电阻 R50、第三十电容 C30、第二二极管 D' 2、第三二极管 D' 3 和第三稳压二极管 D3;

[0075] 第一存储芯片 U5 的电源脚 VCC、第三十电容 C30 的第一端、第二二极管 D' 2 的负极、第三二极管 D' 3 的负极、第四十九电阻 R49 的第一端、第四十八电阻 R48 的第一端和第四十七电阻 R47 的第一端共接于第二 ESD 保护芯片 U4 的电源脚 VDD,第二二极管 D' 2 的正极接 VGA 接口 111 的电源脚 +5V,第三二极管 D' 3 的正极与第三稳压二极管 D3 的负极共接于 +5V 电源,第三稳压二极管 D3 的负极接地,第一存储芯片 U5 的写保护脚 WP 接第五十电阻 R50 的第二端,第五十电阻 R50 的第一端和第四十九电阻 R49 的第二端共接于主控芯片 U1 的第三 A 输入输出脚 PA3,第一存储芯片 U5 的 I2C 总线时钟脚 SCL、第四十八电阻 R48 的第二端、第四十五电阻 R45 的第二端和第二 ESD 保护芯片 U4 的第二输入输出脚 I/02 共接于主控芯片 U1 的第四 B 输入输出脚 PB4,第一存储芯片 U5 的 I2C 总线数据脚 SDA、第四十七电阻 R47 的第二端、第四十六电阻 R46 的第二端、第二 ESD 保护芯片 U4 的第一输入输出脚 I/01 共接于主控芯片 U1 的第五 B 输入输出脚 PB5,第四十五电阻 R45 的第一端和第四十六电阻 R46 的第一端分别接 VGA 接口 111 的 I2C 总线数据脚 SCL 和 I2C 总线时钟脚 SDA,第一存储芯片 U5 的地脚 GND 和第三十电容 C30 的第二端接地。

[0076] 图 4 示出了本实用新型实施例提供的液晶显示屏控制电路 HDMI 接口模块的电路图。为了便于说明,仅示出了与本实用新型实施例相关的部分。

[0077] 作为本实用新型的一实施例,HDMI 接口模块 2 包括 HDMI 接口 21、第二 ESD 保护单元 22 和第二存储单元 23;

[0078] 第二 ESD 保护单元 22 包括第三 ESD 保护芯片 U6、第四 ESD 保护芯片 U7、第五 ESD 保护芯片 U8、第三十一电容 C31、第一双向稳压二极管 D" 1、第五十一电阻 R51、第五十二电阻 R52、第二双向稳压二极管 D" 2、第三十二电容 C32、第二双向稳压二极管 D" 3、第三十三电容 C33、第四稳压二极管 D4、第五十三电阻 R53 和第六十电阻 R60;

[0079] HDMI 接口 21 的第三数据通道正脚 RX2+、第三数据通道负脚 RX2-、第二数据通道正脚 RX1+ 和第二数据通道负脚 RX1- 分别接第三 ESD 保护芯片 U6 的第一输入脚 IN1、第二输入脚 IN2、第三输入脚 IN3 和第四输入脚 IN4,HDMI 接口 21 的第一数据通道正脚 RX0+、第一数据通道负脚 RX0-、时钟通道正脚 CLK+ 和时钟通道负脚 CLK- 分别接第四 ESD 保护芯片 U7 的第一输入脚 IN1、第二输入脚 IN2、第三输入脚 IN3 和第四输入脚 IN4, HDMI 接口 21 的第二地脚 GND2、第一地脚 GND1、第零地脚 GND0 和第四地脚 GND4 接地,第三 ESD 保护芯片 U6 的第一输出脚 OUT1、第二输出脚 OUT2、第三输出脚 OUT3 和第四输出脚 OUT4 分别接主控芯片

U1 的第三 TDMS 数据通道正脚 RX22+、第三 TDMS 数据通道负脚 RX22-、第二 TDMS 数据通道正脚 RX21+ 和第二 TDMS 数据通道负脚 RX21-，第四 ESD 保护芯片 U7 的第一输出脚 OUT1、第二输出脚 OUT2、第三输出脚 OUT3 和第四输出脚 OUT4 分别接主控芯片 U1 的第一 TDMS 数据通道正脚 RX20+、第一 TDMS 数据通道负脚 RX20-、TDMS 时钟通道正脚 RX2C+ 和 TDMS 时钟通道负脚 RX2C-，HDMI 接口 21 的第三地脚 GND3、第五 ESD 保护芯片 U8 的第二输入输出脚 I/02、第三十一电容 C31 的第一端、第一双向稳压二极管 D”1 的第一端和第五十一电阻 R51 的第一端共接，第三十一电容 C31 的第二端和第一双向稳压二极管 D”1 的第二端共接于地，第五十一电阻 R51 的第二端和第五十二电阻 R52 的第一端共接于主控芯片 U1 的第四 C 输入输出脚 PC4，第五十二电阻 R52 的第二端、第三十二电容 C32 的第二端和第五 ESD 保护芯片 U8 的地脚共接于地，第五 ESD 保护芯片 U8 的电源脚 VDD 接第三十二电容 C32 的第一端，HDMI 接口 21 的电源脚 +5V、第二双向稳压二极管 D”3 的第一端、第三十三电容 C33 的第一端、第四稳压二极管 D4 的第一端和第五十三电阻 R53 的第一端共接于第二存储模块 23，HDMI 接口 21 的热插拔检测脚 HPD、第二双向稳压二极管 D”2 的第一端、第三十二电容 C32 的第一端和第五十三电阻 R53 的第二端共接于第六十电阻 R60 的第一端，第六十电阻 R60 的第二端接主控芯片的第五 A 输入输出脚 PA5，第二双向稳压二极管 D”2 的第二端、第三十二电容 C32 的第二端、第二双向稳压二极管 D”3 的第二端、第三十三电容 C33 的第二端和第四稳压二极管 D4 的第二端共接于地；

[0080] 第二存储单元 23 包括第二存储芯片 U9、第四二极管 D’4、第五二极管 D’5、第五稳压二极管 D5、第三十四电容 C34、第五十四电阻 R54、第五十五电阻 R55、第五十六电阻 R56、第五十七电阻 R57、第五十八电阻 R58、第五十九电阻 R59、第四双向稳压二极管 D”4 和第五双向稳压二极管 D”5；

[0081] 第二存储芯片 U9 的电源脚 VCC、第三十四电容 C34 的第一端、第四二极负极、第五二极管 D’5 的负极、第五十六电阻 R56 的第一端、第五十五电阻 R55 的第一端和第五十四电阻 R54 的第一端共接于第五十二电阻 R52 的第二端，第四二极管 D’4 的正极接第五十三电阻 R53 的第一端，第五二极管 D’5 的正极和第五稳压二极管 D5 的负极共接于 +5V 电源，第五稳压二极管 D5 的正极接地，第三十四电容 C34 的第二端和第二存储芯片 U9 的地脚共接于地，第二存储芯片 U9 的写保护脚 WP 接第五十七电阻 R57 的第二端，第五十七电阻 R57 的第一端和第五十六电阻 R56 的第二端共接于主控芯片 U1 的第三 A 输入输出脚 PA3，第二存储芯片 U9 的 I2C 总线时钟脚 SCL、第五十五电阻 R55 的第二端和第五十八电阻 R58 的第二端共接于主控芯片 U1 的第六 B 输入输出脚 PB6，第二存储芯片 U9 的 I2C 总线数据脚 SDA 和第五十九电阻 R59 的第二端共接于主控芯片 U1 的第七 B 输入输出脚 PB7，第五十八电阻 R58 的第一端、第五双向稳压二极管 D”5 的第一端和第五 ESD 保护芯片 U8 的第二输入输出脚 I/02 共接于 HDMI 接口 21 的 I2C 总线时钟端 SDA，第五十九电阻 R59 的第一端、第四双向稳压二极管 D”4 的第一端和第五 ESD 保护芯片 U8 的第三输入输出脚 I/03 共接于 HDMI 接口 21 的 I2C 总线数据脚 SDA。

[0082] 图 5 示出了本实用新型实施例提供的液晶显示屏控制电路音频输出模块的电路图。为了便于说明，仅示出了与本实用新型实施例相关的部分。

[0083] 作为本实用新型的一实施例，音频输出模块 3 包括音频放大芯片 U10、第六十一电阻 R61、第六十二电阻 R62、第六十三电阻 R63、第六十四电阻 R64、第六十五电阻 R65、第

六十六电阻 R66、第六十七电阻 R67、第六十八电阻 R68、第六十九电阻 R69、第七十电阻 R70、第七十一电阻 R71、第七十二电阻 R72、第七十三电阻 R72、第三十五电容 C35、第三十六电容 C36、第三十七电容 C37、第三十八电容 C38、第三十九电容 C39、第四十电容 C40、第四十一电容 C41、第四十二电容 C42、第四十三电容 C43、第四十四电容 C44、第四十五电容 C45、第四十六电容 C46、第四十七电容 C47、第四十八电容 C48、第四十九电容 C49、第五十电容 C50、第五十一电容 C51、第五十二电容 C52、第五十三电容 C53、第五十四电容 C54、第五十五电容 C55、第五十六电容 C56、第五电感 L5、第六电感 L6、第七电感 L7 和第八电感 L8；

[0084] 音频放大芯片 U10 的左声道电源脚 PVDDL、第四十二电容 C42 的第一端和第四十一电容 C41 的第一端共接于 +5V 电源，音频放大芯片 U10 的左声道地脚 PGNDL、第四十一电容 C41 的第二端和第四十二电容 C42 的第二端共接于地，音频放大芯片 U10 的左声道输入脚 INL 和第四十三电容 C43 的第二端共接于第三十五电容 C35 的第二端，第三十五电容 C35 的第一端、第六十二电阻 R62 的第一端、第三十六电容 C36 的第一端和第六十一电阻 R61 的第二端共接，第六十一电阻 R61 的第一端接主控芯片 U1 的第一空置脚 NC1，第三十六电容 C36 的第二端和第六十二电阻 R62 的第二端共接于地，音频放大芯片 U10 的右声道输入脚 INR 和第四十四电容 C44 的第二端共接于第三十七电容 C37 的第二端，第三十七电容 C37 的第一端、第六十四电阻 R64 的第一端、第三十八电容 C38 的第一端和第六十三电阻 R63 的第二端共接，第六十三电阻 R63 的第一端接主控芯片 U1 的第二空置脚 NC2，第三十八电容 C38 的第二端和第六十四电阻 R64 的第二端共接于地，第四十三电容 C43 的第一端、第四十六电容 C46 的第一端、第六十八电阻 R68 的第一端、第六十五电阻 R65 的第二端和第三十九电容 C39 的第二端共接，第三十九电容 C39 的第一端接主控芯片 U1 的第三空置脚 NC3，第四十四电容 C44 的第一端、第四十五电容 C45 的第一端、第六十七电阻 R67 的第一端、第六十六电阻 R66 的第二端和第四十电容 C40 的第二端共接，第四十电容 C40 的第一端接主控芯片 U1 的第四空置脚 NC4，第六十七电阻 R67 的第二端、第六十八电阻 R68 的第二端、第四十五电容 C45 的第二端和第四十六电容 C46 的第二端共接于地，音频放大芯片 U10 的关断控制输入脚 SHDN、第六十九电阻 R69 的第二端和第四十七电容 C47 的第一端共接，第六十九电阻 R69 的第一端和第七十电阻 R70 的第一端共接于主控芯片 U1 的第七 C 输入输出脚 PC7，音频放大芯片 U10 的模拟信号参考脚 VREF 接第四十八电容 C48 的第一端，音频放大芯片 U10 的地脚 GND、第四十八电容 C48 的第二端、第四十七电容 C47 第二端和第七十电阻 R70 的第二端共接于地，音频放大芯片 U10 的右声道电源脚 PVDDR、第四十九电容 C49 的第一端和第五十电容 C50 的第一端共接于 +5V 电源，音频放大芯片 U10 的右声道地脚 PGNDR、第四十九电容 C49 的第二端和第五十电容 C50 的第二端共接于地，音频放大芯片 U10 的左声道负输出脚 OUTL-、左声道正输出脚 OUTL+、右声道负输出脚 OUTR- 和右声道正输出脚 OUTR+ 分别接第五电感 L5 的第一端、第六电感 L6 的第一端、第七电感 L7 的第一端和第八电感 L8 的第一端，第五电感 L5 的第二端、第六电感 L6 的第二端、第七电感 L7 的第二端和第八电感 L8 的第二端分别接第五十一电容 C51 的第一端、第五十二电容 C52 的第一端、第五十三电容 C53 的第一端和第五十四电容 C54 的第一端，第五十一电容 C51 的第二端、第五十二电容 C52 的第二端、第五十三电容 C53 的第二端和第五十四电容 C54 的第二端共接于地，音频放大芯片 U10 的 DC 音量控制脚 VOLUME、第五十六电容 C56 的第一端和第七十一电阻 R71 的第一端共接，第七十一电阻 R71 的第二端和第七十三电阻 R72 的第一端共接于主控芯片 U1 的第零 C

输入输出脚 PC0, 音频放大芯片 U10 的电源脚 VDD、第五十五电容 C55 的第一端和第七十二电阻 R72 的第一端共接, 第七十二电阻 R72 的第二端和第七十三电阻 R72 的第二端共接于 +5V 电源, 第五十五电容 C55 的第二端和第五十六电容 C56 的第二端共接于地。

[0085] 图 6 示出了本实用新型实施例提供的液晶显示屏控制电路接屏模块的电路图。为了便于说明, 仅示出了与本实用新型实施例相关的部分。

[0086] 作为本实用新型的一实施例, 接屏模块 4 包括插排 41、屏幕开关控制芯片 U11、第九电感 L9、第十电感 L10、第十一电感 L11、第七十四电阻 R74、第七十五电阻 R75、第七十六电阻 R76、第七十七电阻 R77、第七十八电阻 R78、第五十七电容 C57、第五十八电容 C58、第五十九电容 C59、第六十电容 C60、第一三极管 Q6 和第六 MOS 管 Q7;

[0087] 插排 41 的第一输入脚 IN1 至第二十输入脚 IN20 均接主控芯片 U1, 插排 41 的电源脚 VCC 接 LCD 正电源 VLCD, 插排 41 的地脚 GND 接地, 第一三极管 Q6 的基极、第七十六电阻 R76 的第二端和第五十八电容 C58 的第一端共接, 第七十六电阻 R76 的第一端和第七十七电阻 R77 的第一端共接于主控芯片 U1 的第六 C 输入输出端 PC6, 第七十七电阻 R77 的第二端和第五十八电容 C58 的第二端共接于地, 第一三极管 Q6 的发射极接地, 第一三极管 Q6 的集电极、第七十四电阻 R74 的第二端和第七十五电阻 R75 共接, 第七十四电阻 R74 的第一端、第五十七电容 C57 的第一端、屏幕开关控制芯片 U11 的第一至第三输入脚 S1 ~ S3 共接于第六 MOS 管 Q7 的源极, 第十一电感 L11 的第二端、第十电感 L10 的第二端和第九电感 L9 的第二端共接, 第十一电感 L11 的第一端、第十电感 L10 的第一端和第九电感 L9 的第一端分别接 +5V 电源、+3.3V 电源和 +12V 电源, 第七十五电阻 R75 的第二端、屏幕开关控制芯片 U11 的地脚 G 和第六 MOS 管 Q7 的栅极共接, 第六 MOS 管 Q7 的漏极、第五十九电容 C59 的正极、第六十电容 C60 的第一端和第七十八电阻 R78 的第一端共接, 第五十九电容 C59 的负极、第六十电容 C60 的第二端和第七十八电阻 R78 的第二端共接于地。

[0088] 作为本实用新型的一实施例, 所述电源模块 6 提供的电源包括 +12V 电源、+5V 电源、+3.3V 电源和 +1.2V 电源。

[0089] 作为本实用新型的一实施例, 主控芯片 U1 的型号为 Novatek 联咏平板显示器控制芯片 NT68760/770/771。

[0090] 作为本实用新型的一实施例, 闪存芯片 U2 的型号为 PM25LV010。

[0091] 作为本实用新型的一实施例, 第一 ESD 保护芯片 U3、第二 ESD 保护芯片 U4、第五 ESD 保护芯片 U8 的型号为 AZC099-04S, 第三 ESD 保护芯片 U6 和第四 ESD 保护芯片 U7 的型号为 AZ1045-04F. R7G。

[0092] 作为本实用新型的一实施例, 第一存储芯片 U5 和第二存储芯片 U9 的型号为 M24C02。

[0093] 作为本实用新型的一实施例, 音频放大芯片 U10 的型号为 AD52653 或 PAM8003。

[0094] 作为本实用新型的一实施例, 屏幕开关控制芯片 U11 的型号为 NC/AP9435GM。

[0095] 以下结合工作原理, 对本实用新型的实施例作进一步说明:

[0096] VGA 接口模块 1 接收电脑或上位机输出的模拟视频图像信息, HDMI 接口模块 2 接收电脑或上位机输出的数字视频图像信息, VGA 接口模块和 HDMI 接口模块将接收到的视频图像信息输出至主控模块 5, 主控模块 5 将所述视频图像信息进行处理后, 输出至音频输出模块 3 和接屏模块 4。其中 VGA 接口模块和 HDMI 接口模块均包括 ESD 保护芯片, 用于防止静

电直接从 VGA 接口或 HDMI 接口串入主控芯片导致损坏, 主控芯片 U1 可直接输出 LVDS (Low Voltage Differential Signaling, 低压差分信号), 直接驱动液晶显示屏。

[0097] 在本实用新型的实施例中, 所述液晶显示屏控制电路包括 VGA 接口模块、HDMI 接口模块、主控模块、音频输出模块、接屏模块和电源模块, 所述 VGA 接口模块接收电脑或上位机输出的模拟视频图像信息, 所述 HDMI 接口模块接收电脑或上位机输出的数字视频图像信息, 所述主控模块将所述模拟视频图像信息或数字视频图像信息进行处理后输出至音频输出模块和接屏模块, 进行音频的输出和视频图像信息的显示。本实用新型在传统液晶显示屏控制电路的基础上, 减少了一个背光驱动芯片, 节简了外围电路, 大大节约了 PCB 板的空间, 降低了成本, 且提高了电路的稳定性。

[0098] 以上所述仅为本实用新型的较佳实施例而已, 并不用以限制本实用新型, 凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等, 均应包含在本实用新型的保护范围之内。

图 1

图 2

图 3

图 4

图 5

图 6

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种液晶显示屏控制电路                                    |         |            |

| 公开(公告)号        | <a href="#">CN205104208U</a>                   | 公开(公告)日 | 2016-03-23 |

| 申请号            | CN201520814592.0                               | 申请日     | 2015-10-20 |

| [标]申请(专利权)人(译) | 重庆惠科金扬科技有限公司                                   |         |            |

| 申请(专利权)人(译)    | 重庆惠科金扬科技有限公司                                   |         |            |

| 当前申请(专利权)人(译)  | 重庆惠科金扬科技有限公司                                   |         |            |

| [标]发明人         | 王智勇<br>王磐                                      |         |            |

| 发明人            | 王智勇<br>王磐                                      |         |            |

| IPC分类号         | G09G3/36                                       |         |            |

| 代理人(译)         | 张全文                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本实用新型涉及显示屏控制技术领域，尤其涉及一种液晶显示屏控制电路。在本实用新型的实施例中，所述液晶显示屏控制电路包括VGA接口模块、HDMI接口模块、主控模块、音频输出模块、接屏模块和电源模块，所述VGA接口模块接收电脑或上位机输出的模拟视频图像信息，所述HDMI接口模块接收电脑或上位机输出的数字视频图像信息，所述主控模块将所述模拟视频图像信息或数字视频图像信息进行处理后输出至音频输出模块和接屏模块，进行音频的输出和视频图像信息的显示。本实用新型在传统液晶显示屏控制电路的基础上，减少了一个背光驱动芯片，节简了外围电路，大大节约了PCB板的空间，降低了成本，且提高了电路的稳定性。