(12)发明专利申请

(10)申请公布号 CN 110189719 A

(43)申请公布日 2019.08.30

(21)申请号 201910463435.2

(22)申请日 2019.05.30

(71)申请人 重庆蓝岸通讯技术有限公司

地址 401120 重庆市渝北区回兴街道翠屏

路16号

(72)发明人 陈新银 刘立明

(74)专利代理机构 重庆为信知识产权代理事务

所(普通合伙) 50216

代理人 余锦曦

(51)Int.Cl.

G09G 3/36(2006.01)

G09G 3/00(2006.01)

权利要求书1页 说明书4页 附图6页

(54)发明名称

内置式LTPS显示面板像素点监测系统

(57)摘要

本发明公开一种内置式LTPS显示面板像素点监测系统,包括显示面板,该显示面板由内至外依次包括面板基板、液晶层、偏光层,所述面板基板上刻蚀有 $m \times n$ 个像素点的像素点阵列,所述面板基板上还设置有检测采集模块,所述检测采集模块包括像素监测阵列、时序采样电路,所述像素监测阵列包括 $m \times n$ 个监测单元,所述监测单元与所述像素点一一对应。有益效果:在实际每个可能坏点的像素点上微观地检测其是否正常,监测的效果必然直接、精确,监测单元的监测信号由时序采样电路编译转换为时序信流,自检分析模块解析时序信流,得出像素坏点结果,就能快速获知坏点的位置。

1. 一种内置式LTPS显示面板像素点监测系统,包括显示面板(A),该显示面板(A)由内至外依次包括面板基板(A1)、液晶层(A2)、偏光层(A3),所述面板基板(A1)上刻蚀有m×n个像素点(B1)的像素点阵列(B),其中,n为行数,m为列数,特征在于:所述面板基板(A1)上还设置有检测采集模块(C),所述检测采集模块(C)包括像素监测阵列(C1)、时序采样电路(C2),所述像素监测阵列(C1)包括m×n个监测单元(C11),所述监测单元(C11)与所述像素点(B1)一一对应,所述时序采样电路(C2)的采样端组连接所述像素监测阵列(C1)的监测输出端组,所述时序采样电路(C2)的时序信流输出端组连接有自检分析模块(D)的信号接收端组;

所述自检分析模块(D)用于分析处理时序信流,得出像素坏点结果。

2. 根据权利要求1所述的内置式LTPS显示面板像素点监测系统,特征在于:所述像素点(B1)包括一个MOSFET(B11)和一个像素电极(B12),所述MOSFET(B11)的源极S连接像素点数据驱动线(A01),栅极G连接像素点扫描驱动线(A02),漏极D连接所述像素电极(B12);

所述监测单元(C11)设置有至少一个光生伏特效应PN结,所述光生伏特效应PN结依附于所述像素电极(B12),所述光生伏特效应PN结接入所述时序采样电路(C2)的采样端组。

3. 根据权利要求2所述的内置式LTPS显示面板像素点监测系统,特征在于:所述像素电极(B12)的一侧设有PN位,所述PN位内布置有所述光生伏特效应PN结。

4. 根据权利要求2所述的内置式LTPS显示面板像素点监测系统,特征在于:每个所述监测单元(C11)设置有2个所述光生伏特效应PN结,其中,一个为行测PN结,另一个为列测PN结;

所述像素监测阵列(C1)中每一行的所述行测PN结依次连接,且第i个行测PN结的阴极连接第i+1个行测PN结的阳极,1≤i≤m,第1个行测PN结的阳极接地,第m个行测PN结的阴极连接所述时序采样电路(C2)的行采样单元(C2b);

所述像素监测阵列(C1)中每一列的所述列测PN结依次连接,且第j个列测PN结的阴极连接第j+1个列测PN结的阳极,1≤j≤n,第1个列测PN结的阳极接地线,第n个列测PN结的阴极连接所述时序采样电路(C2)的列采样单元(C2a)。

5. 根据权利要求4所述的内置式LTPS显示面板像素点监测系统,特征在于:所述列采样单元(C2a)设置有时序电路a,该时序电路a包括m个寄存单元,m个所述寄存单元的输入端分别连接所述像素监测阵列(C1)中每一列第n个列测PN结的阴极;

所述行采样单元(C2b)设置有时序电路b,该时序电路b包括n个寄存单元,n个所述寄存单元的输入端分别连接所述像素监测阵列(C1)中每一行第m个行测PN结的阴极。

6. 根据权利要求2所述的内置式LTPS显示面板像素点监测系统,特征在于:所述光生伏特效应PN结蚀刻于所述面板基板(A1)表面。

7. 根据权利要求1所述的内置式LTPS显示面板像素点监测系统,特征在于:所述自检分析模块(D)安装于所述面板基板(A1)上,所述面板基板(A1)还设置有像素坏点显示处理单元,该像素坏点显示处理单元的信号接收端连接自检分析模块(D)的输出端,所述像素坏点显示处理单元的显示输出端连接LTPS显示面板的显示驱动端。

## 内置式LTPS显示面板像素点监测系统

### 技术领域

[0001] 本发明涉及LTPS显示面板坏点检测技术领域,具体的说,涉及一种内置式LTPS显示面板像素点监测系统。

### 背景技术

[0002] 薄膜晶体管液晶显示(TFT-LCD)为现今电子显示屏的一种显示技术,通过基板上的TFT像素点阵控制液晶层的透光情况,具体包括非晶硅(a-Si)和低温多晶硅(LTPS)两种TFT技术。其中,LTPS面板的结构包括底层光源,底层光源上由内至外依次有TFT基板、液晶层、偏光层、玻璃保护层,如图1所示,而TFT基板为玻璃基板,其表面覆有一层多晶硅薄膜,在该多晶硅薄膜上刻蚀FET(Field Effect Transistor,场效应晶体管)点阵,如图2,非FET点阵的晶硅制成像素电极,像素电极与液晶层上部的共通电极形成储存电容,每个储存电容中都夹有液晶单元,如图3,通过给FET点阵扫描供电,储存电容获得一定电压使液晶单元透光,从而形成图案。

[0003] 在显示屏的使用过程中,像素点能否正常透光成为显示屏正常显示的主因,但在少部分像素点无法正常透光,即坏点时,容易产生花屏现象,此时整体显示屏还能继续显示部分内容,但一些信息无法完整显示出,而废弃掉整个显示屏又造成极大浪费,若能准确知道哪些像素点故障,则可以针对性地修复这些坏点,从而再次正常工作使用。

[0004] 现有技术中,无法确定像素点阵列中坏点的具体位置或较具体的位置。

### 发明内容

[0005] 针对上述缺陷,本发明提出了一种内置式LTPS显示面板像素点监测系统,通过在像素点处设置监测单元,把像素点的透光情况实时采集并交由检测分析模块分析,就能快速获知坏点的位置,从而方便修复坏点的像素点,可以将坏点的显示屏重新利用,而不用整个废弃,节约资源及成本。

[0006] 为达到上述目的,本发明采用的具体技术方案如下:

[0007] 一种内置式LTPS显示面板像素点监测系统,包括显示面板,该显示面板由内至外依次包括面板基板、液晶层、偏光层,所述面板基板上刻蚀有 $m \times n$ 个像素点的像素点阵列,其中,n为行数,m为列数,所述面板基板上还设置有检测采集模块,所述检测采集模块包括像素监测阵列、时序采样电路,所述像素监测阵列包括 $m \times n$ 个监测单元,所述监测单元与所述像素点一一对应,所述时序采样电路的采样端组连接所述像素监测阵列的监测输出端组,所述时序采样电路的时序信流输出端组连接有自检分析模块的信号接收端组;

[0008] 所述自检分析模块用于分析处理时序信流,得出像素坏点结果。

[0009] 通过上述设计,在实际每个可能坏点的像素点上微观地检测其是否正常,监测的效果必然直接、精确,监测单元的监测信号由时序采样电路编译转换为时序信流,自检分析模块解析时序信流,得出像素坏点结果,就能快速获知坏点的位置。

[0010] 自检分析模块既可内置于显示面板内,其得出的分析结果可经外接串口输出到结

果显示器上,还可于显示面板上设置一个像素坏点显示处理单元,为一个单片机或处理器,将像素坏点结果显示在显示面板上;

[0011] 自检分析模块也可以是外置的分析设备,时序采样电路的时序信流输出端组为外接串口,分析设备只需插上外接串口即可接收到时序信流进行分析。

[0012] 所述像素点包括一个MOSFET和一个像素电极,所述MOSFET的源极S连接像素点数据驱动线,栅极G连接像素点扫描驱动线,漏极D连接所述像素电极;

[0013] MOSFET即金属氧化物半导体场效应晶体管,属于一种常用的FET,当像素点扫描驱动线对MOSFET的栅极G发出扫描电平信号时,源极S与漏极D导通,像素点数据驱动线为像素电极供电充能,像素电极与共通电极之间夹有液晶单元,液晶单元得电后导光,最终形成点阵控制的导光面。

[0014] 进一步的,所述监测单元设置有至少一个光生伏特效应PN结,所述光生伏特效应PN结依附于所述像素电极,所述光生伏特效应PN结接入所述时序采样电路的采样端组。

[0015] 光生伏特效应PN结可在受到光照时形成电荷流动从而产生电势差,其阴极产生高电势,阳极对应为低电势,因此当像素点正常透光时,有光线照射在光生伏特效应PN结上,对应的PN结两端具有电势差,反之背光源的光线无法照射到PN结上时,其两端的电势差会骤降,以此电势的升降来识别像素点是否正常透光。

[0016] 光生伏特效应PN结为在硅中掺入V族元素,形成N型半导体,硅中掺入III族元素则形成P型半导体,可直接在多晶硅薄膜上加工,从而形成光生伏特效应PN结。

[0017] 更进一步设计,所述像素电极的一侧设有PN位,所述PN位内布置有所述光生伏特效应PN结。

[0018] 将PN结置于PN位中与透光的像素电极紧邻,能够更准确监测,PN位最好是像素电极上部镂空位置,像素电极不透光时,上部镂空位置也无法获得光照,仅当像素电极透光时,背光源的光线穿过像素电极,部分进入PN位令PN结产生电势差。

[0019] PN结可仅设置一个,再将每个PN结的电势差变化一一获取,就能快速得到分析结果,但在实际布设时,每个PN结都要分别接线,会让导线路占用大量空间,反而影响像素点本身的正常工作,因此本设计选用以下方案:

[0020] 每个所述监测单元设置有2个所述光生伏特效应PN结,其中,一个为行测PN结,另一个为列测PN结;

[0021] 所述像素监测阵列中每一行的所述行测PN结依次连接,且第i个行测PN结的阴极连接第i+1个行测PN结的阳极,1≤i≤m,第1个行测PN结的阳极接地,第m个行测PN结的阴极连接所述时序采样电路的行采样单元;

[0022] 所述像素监测阵列中每一列的所述列测PN结依次连接,且第j个列测PN结的阴极连接第j+1个列测PN结的阳极,1≤j≤n,第1个列测PN结的阳极接地线,第n个列测PN结的阴极连接所述时序采样电路的列采样单元。

[0023] 将像素点分别进行行和列的联立测试,分析时,只需知道哪一行的像素点有坏点,同时,其中一列的像素点也存在坏点,则行与列相交的点即为最大可能的坏点。其中,任一行或列的若干个PN结形成同向的串联,每个PN结对应的像素点都正常透光时,串联的总电势差最大,一旦其中有坏点,则出现2种情况:其一是,PN结在无光照时无法传递电能时,串联的总电势差会骤减为0,此时若多个坏点,则只能分析出行列的多个交点中可能存在坏

点;其二,PN结在无光照时无电势差,但可传递电能,则串联的总电势差随坏点个数为递减变化,此时的分析结果能够精确每个坏点的具体位置。

[0024] 更进一步设计,所述列采样单元设置有时序电路a,该时序电路a包括m个寄存单元,m个所述寄存单元的输入端分别连接所述像素监测阵列中每一列第n个列测PN结的阴极;

[0025] 所述行采样单元设置有时序电路b,该时序电路b包括n个寄存单元,n个所述寄存单元的输入端分别连接所述像素监测阵列中每一行第m个行测PN结的阴极。

[0026] 每一行或列的电势差为一个幅值模拟信号,共m列的m个幅值模拟信号与共n行的n个幅值模拟信号分别设为时序信号,其传输与分析都更方便快捷。

[0027] 所述光生伏特效应PN结蚀刻于所述面板基板表面。

[0028] 所述自检分析模块安装于所述面板基板上,所述面板基板还设置有像素坏点显示处理单元,该像素坏点显示处理单元的信号接收端连接自检分析模块的输出端,所述像素坏点显示处理单元的显示输出端连接LTPS显示面板的显示驱动端。

[0029] 上述设计将整个监测系统均内置于显示面板,虽然一定程度增加了其体积,但用户可以直观看到像素点的好坏,由此决定是否需要修理或报废。

[0030] 本发明的有益效果:在实际每个可能坏点的像素点上微观地检测其是否正常,监测的效果必然直接、精确,监测单元的监测信号由时序采样电路编译转换为时序信流,自检分析模块解析时序信流,得出像素坏点结果,就能快速获知坏点的位置。

## 附图说明

- [0031] 图1为显示面板的横截分层示意图;

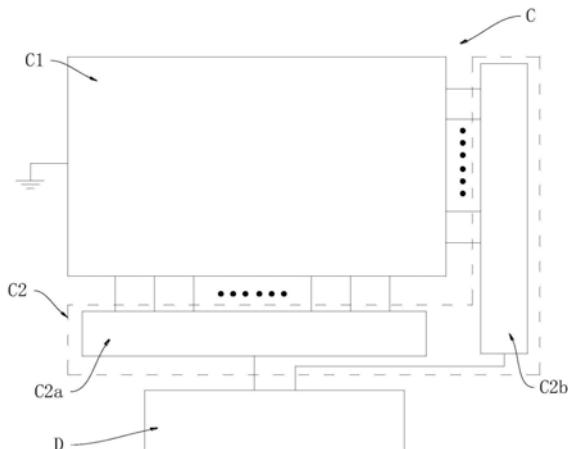

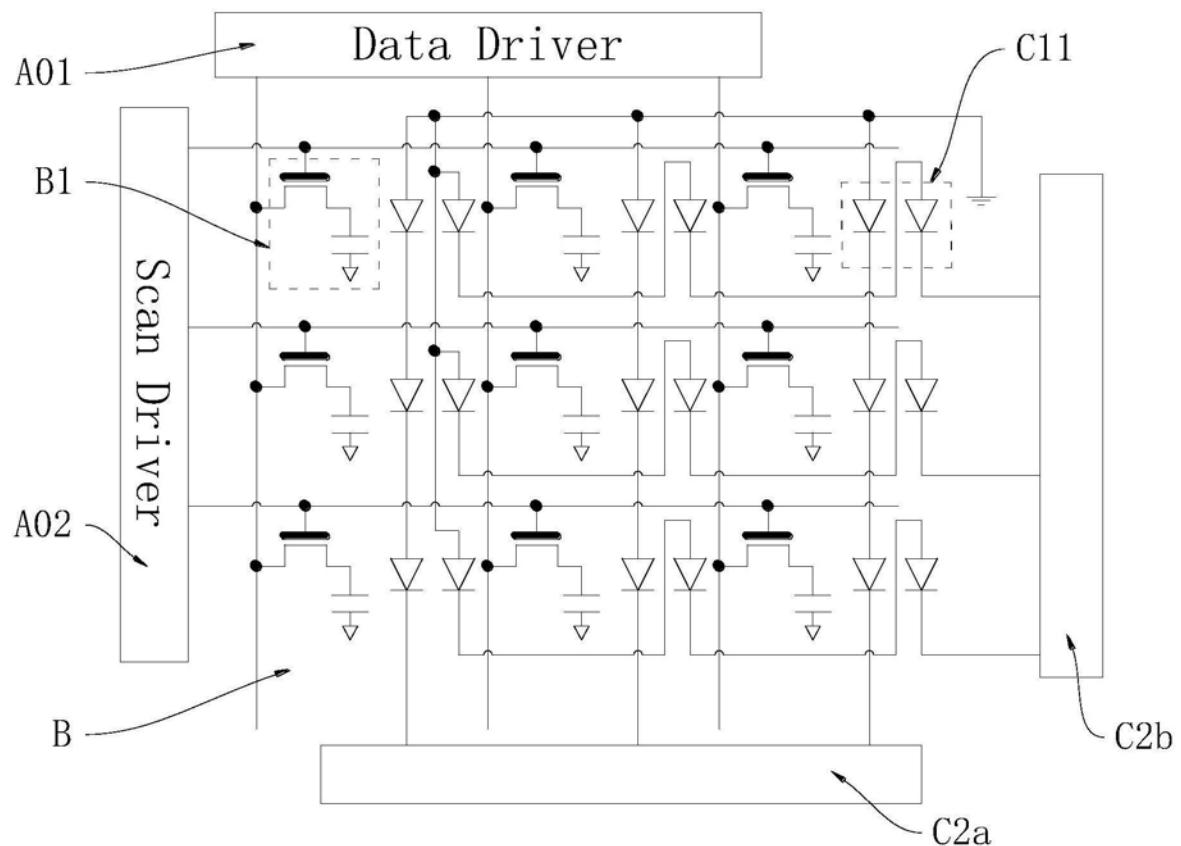

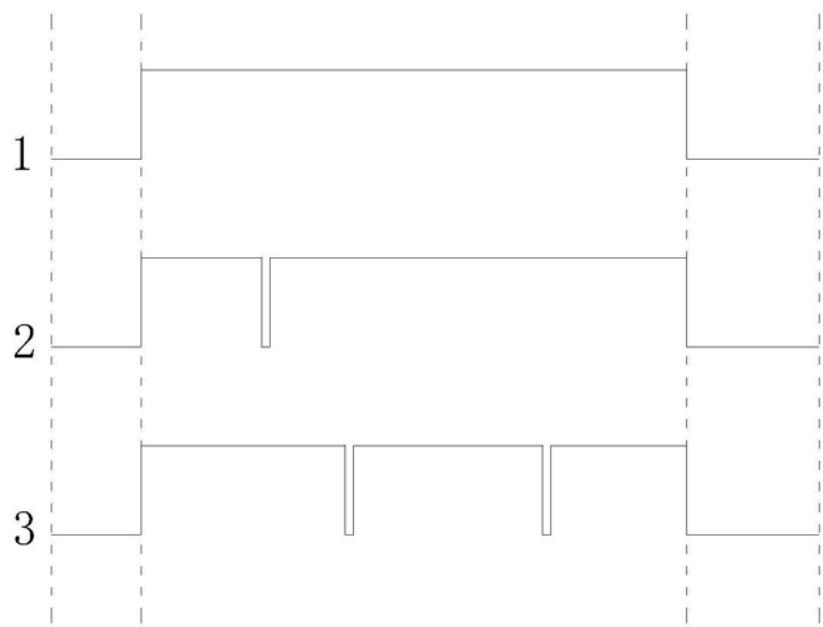

- [0032] 图2为现有技术像素点阵列的示意图;

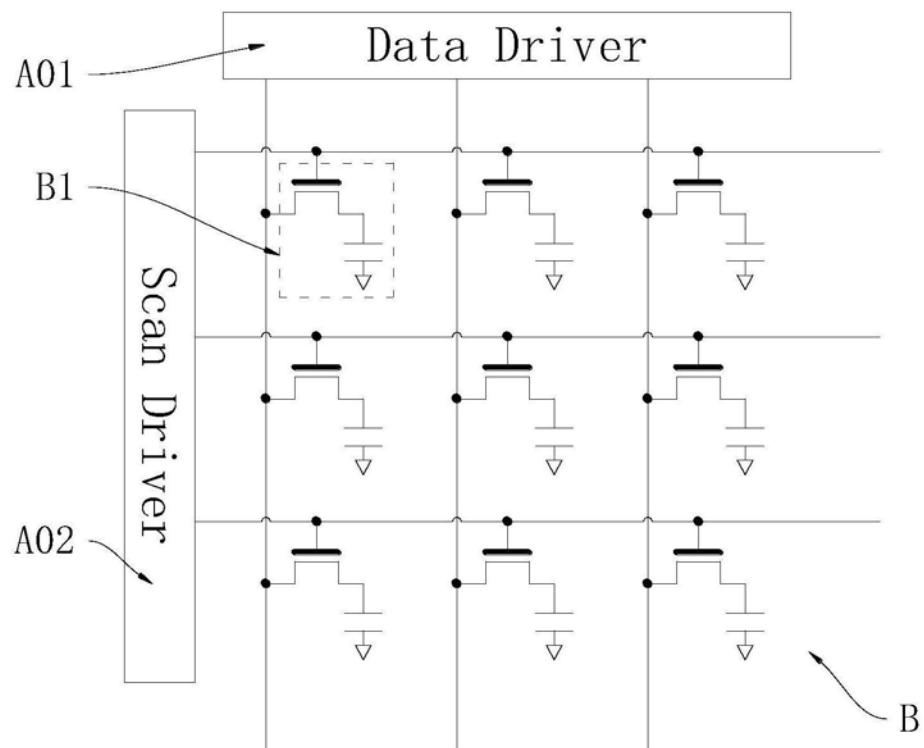

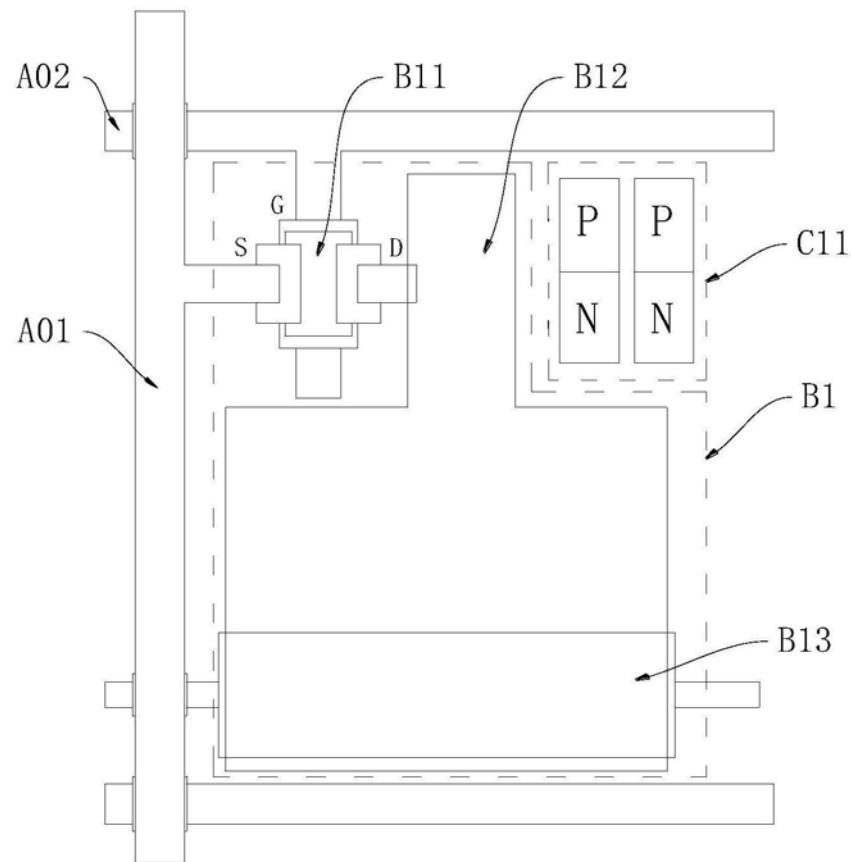

- [0033] 图3为现有技术每个像素点的示意图;

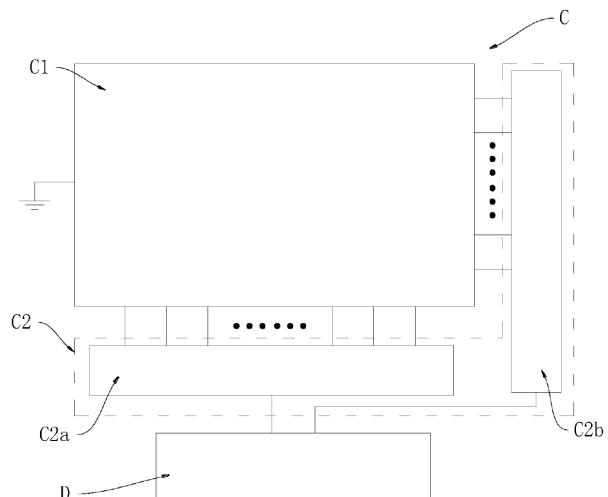

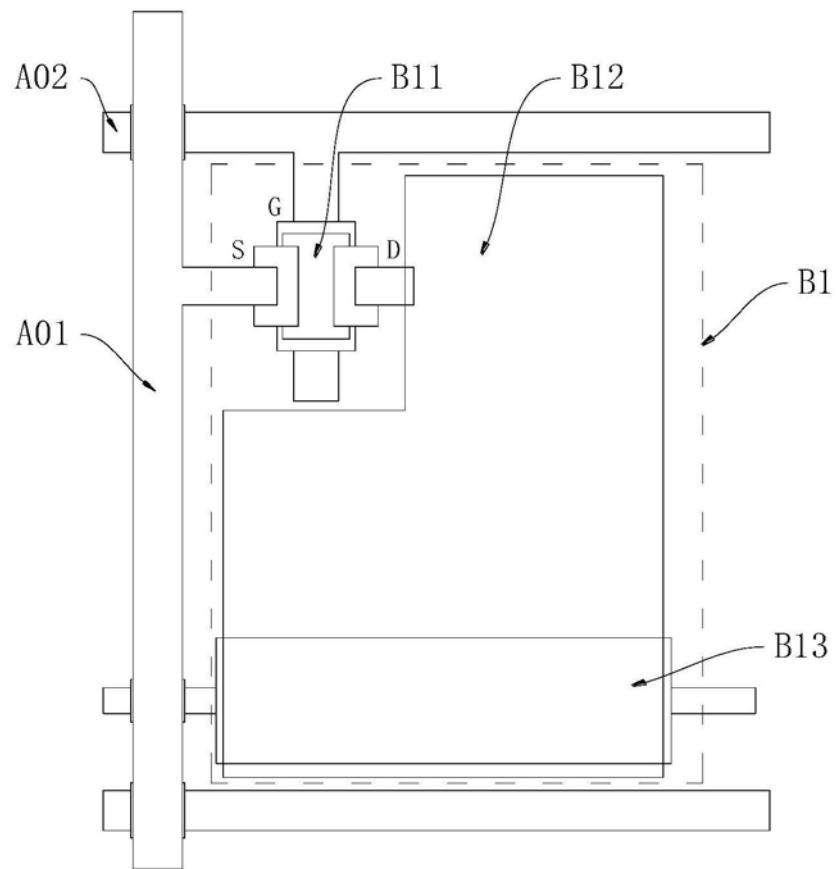

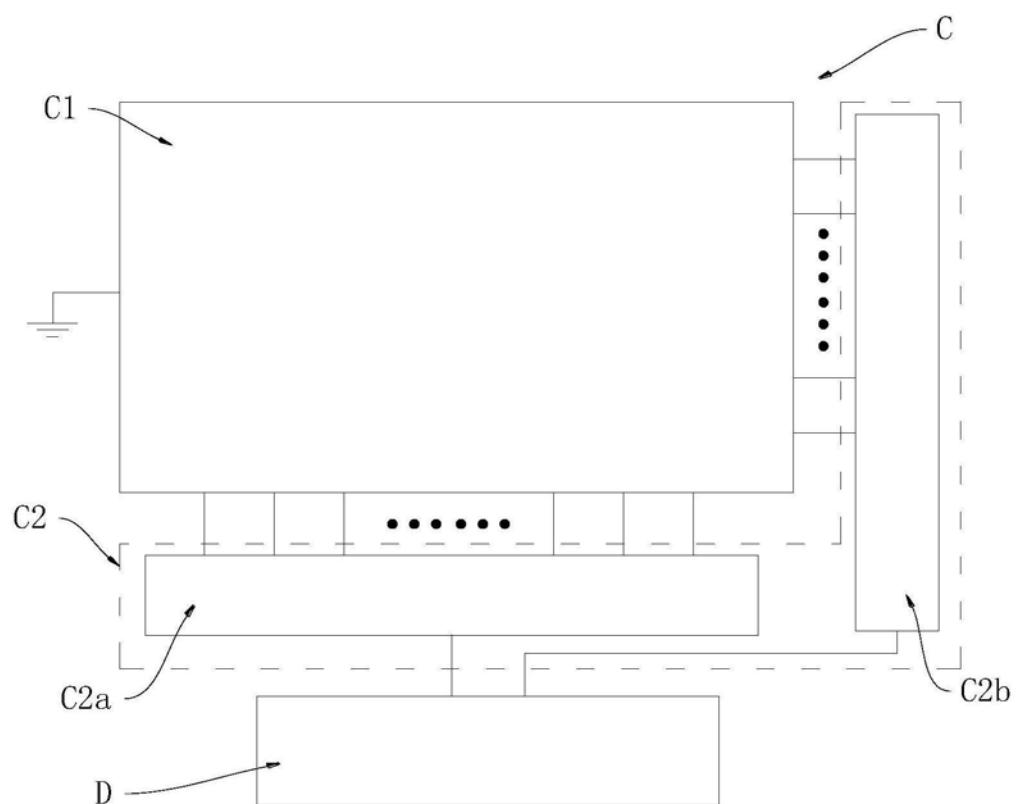

- [0034] 图4为实施例检测采集模块的结构示意图;

- [0035] 图5为实施例像素点阵列的示意图;

- [0036] 图6为实施例每个像素点的示意图;

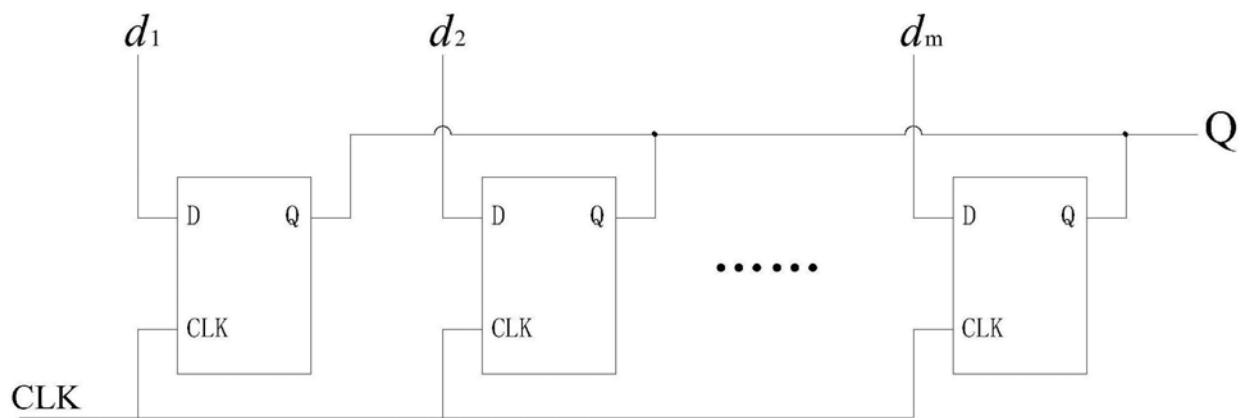

- [0037] 图7为实施例时序电路a的示意图;

- [0038] 图8为实施例时序信流的示意图。

## 具体实施方式

[0039] 下面结合附图及具体实施例对本发明作进一步详细说明。

[0040] 一种内置式LTPS显示面板像素点监测系统,包括显示面板A,该显示面板A如图1所示,由内至外依次包括面板基板A1、液晶层A2、偏光层A3,所述面板基板A1上刻蚀有m×n个像素点B1的像素点阵列B,其中,n为行数,m为列数,如图2、3,所述像素点B1包括一个MOSFETB11和一个像素电极B12,所述MOSFETB11的源极S连接像素点数据驱动线A01,栅极G连接像素点扫描驱动线A02,漏极D连接所述像素电极B12,其中,每个像素电极B12旁还设有存储电容B13,其作用与像素电极B12类似,目的是增加像素点的电压值;

[0041] 如图4所示,所述面板基板A1上还设置有检测采集模块C,所述检测采集模块C包括像素监测阵列C1、时序采样电路C2,所述像素监测阵列C1包括m×n个监测单元C11,所述监

测单元C11与所述像素点B1一一对应,如图5,所述时序采样电路C2的采样端组连接所述像素监测阵列C1的监测输出端组,所述时序采样电路C2的时序信流输出端组连接有自检分析模块D的信号接收端组;

[0042] 所述监测单元C11设置有至少一个光生伏特效应PN结,如图6,所述像素电极B12的一侧设有PN位,所述PN位内布置有所述光生伏特效应PN结,所述光生伏特效应PN结接入所述时序采样电路C2的采样端组。

[0043] 本实施例每个所述监测单元C11优选设置有2个所述光生伏特效应PN结,其中,一个为行测PN结,另一个为列测PN结;

[0044] 以图5-7所示的列分布布设示例:

[0045] 所述像素监测阵列C1中每一列的所述列测PN结依次连接,且第j个列测PN结的阴极连接第j+1个列测PN结的阳极,1≤j≤n,第1个列测PN结的阳极接地线,第n个列测PN结的阴极连接所述时序采样电路C2的列采样单元C2a;

[0046] 所述列采样单元C2a设置有时序电路a,该时序电路a包括m个寄存单元,m个所述寄存单元的输入端分别连接所述像素监测阵列C1中每一列第n个列测PN结的阴极。

[0047] 行分布布设与上述列分布布设相似:

[0048] 所述像素监测阵列C1中每一行的所述行测PN结依次连接,且第i个行测PN结的阴极连接第i+1个行测PN结的阳极,1≤i≤m,第1个行测PN结的阳极接地,第m个行测PN结的阴极连接所述时序采样电路C2的行采样单元C2b;

[0049] 所述行采样单元C2b设置有时序电路b,该时序电路b包括n个寄存单元,n个所述寄存单元的输入端分别连接所述像素监测阵列C1中每一行第m个行测PN结的阴极。

[0050] 如图8所示,任一时序电路a或b的时序信号输出,其中,信号1表示全部像素点都能正常透光的情况,信号2、3则分别表示几行/列中有坏点的情况,比如信号2表示第6行有坏点,信号3表示第10列与第19列均有坏点,则坏点分析结果为第6行第10列的像素点与第6行第19列的像素点,该结果为最大可能的坏点位置。

[0051] 所述光生伏特效应PN结蚀刻于面板基板A1表面。

[0052] 所述自检分析模块D安装于所述面板基板A1上,所述面板基板A1还设置有像素坏点显示处理单元,该像素坏点显示处理单元的信号接收端连接自检分析模块D的输出端,所述像素坏点显示处理单元的显示输出端连接LTPS显示面板的显示驱动端。

[0053] 最后需要说明的是,上述描述仅为本发明的优选实施例,本领域的普通技术人员在本发明的启示下,在不违背本发明宗旨及权利要求的前提下,可以做出多种类似的表示,这样的变换均落入本发明的保护范围之内。

图1

图2

图3

图4

图5

图6

图7

图8

|                |                                            |                      |            |

|----------------|--------------------------------------------|----------------------|------------|

| 专利名称(译)        | 内置式LTPS显示面板像素点监测系统                         |                      |            |

| 公开(公告)号        | <a href="#">CN110189719A</a>               | 公开(公告)日              | 2019-08-30 |

| 申请号            | CN201910463435.2                           | 申请日                  | 2019-05-30 |

| [标]申请(专利权)人(译) | 重庆蓝岸通讯技术有限公司                               |                      |            |

| 申请(专利权)人(译)    | 重庆蓝岸通讯技术有限公司                               |                      |            |

| 当前申请(专利权)人(译)  | 重庆蓝岸通讯技术有限公司                               |                      |            |

| [标]发明人         | 陈新银<br>刘立明                                 |                      |            |

| 发明人            | 陈新银<br>刘立明                                 |                      |            |

| IPC分类号         | G09G3/36 G09G3/00                          |                      |            |

| CPC分类号         | G09G3/006 G09G3/36 G09G2330/10 G09G2330/12 |                      |            |

| 外部链接           | <a href="#">Espacenet</a>                  | <a href="#">Sipo</a> |            |

#### 摘要(译)

本发明公开一种内置式LTPS显示面板像素点监测系统，包括显示面板，该显示面板由内至外依次包括面板基板、液晶层、偏光层，所述面板基板上刻蚀有 $m \times n$ 个像素点的像素点阵列，所述面板基板上还设置有检测采集模块，所述检测采集模块包括像素监测阵列、时序采样电路，所述像素监测阵列包括 $m \times n$ 个监测单元，所述监测单元与所述像素点一一对应。有益效果：在实际每个可能坏点的像素点上微观地检测其是否正常，监测的效果必然直接、精确，监测单元的监测信号由时序采样电路编译转换为时序信流，自检分析模块解析时序信流，得出像素坏点结果，就能快速获知坏点的位置。