(12)发明专利申请

(10)申请公布号 CN 105739157 A

(43)申请公布日 2016.07.06

(21)申请号 201610290291.1

(22)申请日 2016.05.04

(71)申请人 上海中航光电子有限公司

地址 201108 上海市闵行区华宁路3388号

申请人 天马微电子股份有限公司

(72)发明人 席克瑞 朱娟 杜雷 周一安

(74)专利代理机构 北京英赛嘉华知识产权代理

有限责任公司 11204

代理人 王达佐 马晓亚

(51)Int.Cl.

G02F 1/1333(2006.01)

G02F 1/1362(2006.01)

权利要求书2页 说明书8页 附图5页

(54)发明名称

阵列基板及其制作方法、液晶显示装置

(57)摘要

本申请公开了一种阵列基板及其制作方法、液晶显示装置，所述阵列基板包括：设置于基板上的多个凸起结构，覆盖于所述凸起结构上的反射层，以及覆盖于所述反射层上的透明电极层，其中，所述凸起结构包括栅极层、非晶硅层、源漏极层、绝缘层和钝化层。上述用于全反射的阵列基板可以只包括栅极层、非晶硅层、源漏极层、绝缘层钝化层、反射层和透明电极层，而不需要有机层和有机凸起层，可以简化阵列基板的制作工艺，降低成本。

1. 一种阵列基板，其特征在于，包括：设置于基板上的多个凸起结构，覆盖于所述凸起结构上的反射层，以及覆盖于所述反射层上的透明电极层，其中，所述凸起结构包括栅极层、非晶硅层、源漏极层、绝缘层和钝化层。

2. 根据权利要求1所述的阵列基板，其特征在于，所述凸起结构中的栅极层、绝缘层、非晶硅层、源漏极层和钝化层沿第一方向依次设置，其中，所述第一方向与所述基板的上表面垂直，所述栅极层包括多个栅极层图案，所述栅极层图案的形状为第一凸台，所述第一凸台包括顶面、底面和侧面，其中，所述底面和所述顶面相互平行；

所述绝缘层至少完全覆盖各所述第一凸台的顶面和侧面，所述非晶硅层完全覆盖于所述栅极层上的绝缘层的顶面和外侧面，所述源漏极层完全覆盖于所述非晶硅层的顶面和外侧面，所述钝化层至少完全覆盖于所述源漏极层的顶面和外侧面。

3. 根据权利要求1所述的阵列基板，其特征在于，所述凸起结构中的栅极层、绝缘层、非晶硅层、源漏极层和钝化层沿所述第一方向依次设置，其中，所述第一方向与所述基板的上表面垂直，所述栅极层包括多个栅极层图案，所述栅极层图案的形状为第一凸台，所述第一凸台包括顶面、底面和侧面，其中，所述底面和所述顶面相互平行；

所述绝缘层至少完全覆盖各所述第一凸台的顶面和侧面，所述非晶硅层至少部分覆盖所述栅极层上的绝缘层的顶面，其中，所述非晶硅层包括多个形状为第二凸台的非晶硅，所述第二凸台包括顶面、底面和侧面，其中，所述底面和所述顶面相互平行；

所述源漏极层至少部分覆盖各所述非晶硅的顶面，其中，所述源漏极层包括多个形状为第三凸台的源漏极，所述第三凸台包括顶面、底面和侧面，其中，所述底面和所述顶面相互平行；

所述钝化层至少完全覆盖所述源漏极层的顶面和侧面、所述非晶硅的侧面、所述绝缘层的侧面。

4. 根据权利要求2或3所述的阵列基板，其特征在于，任意一所述凸起结构中的源漏极层与该凸起结构中的非晶硅层在第二方向上的长度差为a，所述非晶硅层与该凸起结构中的栅极层在所述第二方向上的长度差为b，所述栅极层与该凸起结构中的绝缘层在所述第二方向上的长度差为c，其中， $a \geq 0, b \geq 0, c \geq 1 \times 10^{-6}$ 米，所述第二方向与所述第一方向垂直。

5. 根据权利要求4所述的阵列基板，其特征在于，所述阵列基板上，所述透明电极层上的任意二点在第一方向上的高度差的最大值S满足： $1 \times 10^{-6}$ 米  $\leq S \leq 1.3 \times 10^{-6}$ 米。

6. 根据权利要求5所述的阵列基板，其特征在于，至少两个所述凸起结构中的第一凸台相连接。

7. 一种液晶显示装置，其特征在于，包括如权利要求1-6之一所述的阵列基板。

8. 一种阵列基板的制作方法，其特征在于，所述方法包括：

在基板上形成栅极层，其中，所述栅极层包括多个栅极层图案，所述栅极层图案的形状为第一凸台；

在所述栅极层上形成覆盖所述栅极层的绝缘层；

在位于所述栅极层上的绝缘层上形成非晶硅层；

在所述非晶硅层上形成源漏极层；

在所述源漏极层上或者所述源漏极层、非晶硅层和绝缘层上覆盖一钝化层，以形成凸

起结构；

形成覆盖所述基板和位于所述基板上的各所述凸起结构上的反射层，以及形成覆盖于所述反射层上的透明电极层。

9.根据权利要求8所述的方法，其特征在于，所述第一凸台包括顶面、底面和侧面，其中，所述底面和所述顶面相互平行；

所述绝缘层至少覆盖各所述第一凸台的顶面和侧面。

10.根据权利要求9所述的方法，其特征在于，所述绝缘层至少部分地覆盖所述基板。

11.根据权利要求10所述的方法其特征在于，所述非晶硅层完全覆盖所述栅极层上的绝缘层的顶面和外侧面；或者

所述非晶硅层至少部分覆盖所述栅极层上的绝缘层的顶面，其中，所述非晶硅层包括多个形状为第二凸台的非晶硅，所述第二凸台包括顶面、底面和侧面，其中，所述底面和所述顶面相互平行。

12.根据权利要求11所述的方法，其特征在于，若所述非晶硅层完全覆盖所述栅极层上的绝缘层的顶面和外侧面，则所述源漏极层完全覆盖所述非晶硅层的顶面和外侧面；

若所述非晶硅层至少部分覆盖所述栅极层上的绝缘层的顶面，则所述源漏极层至少部分覆盖各所述非晶硅的顶面，其中，所述源漏极层包括多个形状为第三凸台的源漏极，所述第三凸台包括顶面、底面和侧面，其中，所述底面和所述顶面相互平行。

13.根据权利要求12所述的方法，其特征在于，所述在所述源漏极层上或者所述源漏极层、非晶硅层和绝缘层上覆盖一钝化层，以形成凸起结构，包括：

若所述绝缘层仅覆盖各所述第一凸台的顶面和侧面，在所述源漏极层或者所述源漏极层、非晶硅层、绝缘层和基板上覆盖所述钝化层后，刻蚀位于所述基板上的所述钝化层以形成所述凸起结构；或者

若所述绝缘层覆盖所述基板和位于所述基板上的各所述第一凸台的顶面和侧面，在所述源漏极层上或者所述源漏极层、非晶硅层和绝缘层上覆盖所述钝化层后，刻蚀位于所述基板上的所述绝缘层上的所述钝化层以形成所述凸起结构。

14.根据权利要求8-13之一所述的方法，其特征在于，所述透明电极层上的任意二点在第一方向上的高度差的最大值S满足： $1 \times 10^{-6}$ 米  $\leq S \leq 1.3 \times 10^{-6}$ 米，其中，所述第一方向与所述基板垂直。

15.根据权利要求14所述的方法，其特征在于，所述方法还包括：

将至少两个所述凸起结构中的第一凸台相连接。

## 阵列基板及其制作方法、液晶显示装置

### 技术领域

[0001] 本申请一般涉及显示技术领域,尤其涉及阵列基板及其制作方法以及包括该阵列基板的液晶显示装置。

### 背景技术

[0002] 液晶显示装置具有低辐射和低功耗等优点,现已广泛的应用于各种显示领域。根据采用的光源不同,液晶显示装置可以分为使用内置背光源的透射式液晶显示装置、反射环境光的反射式液晶显示装置以及将透射与反射结合起来的半反半透式液晶显示装置。

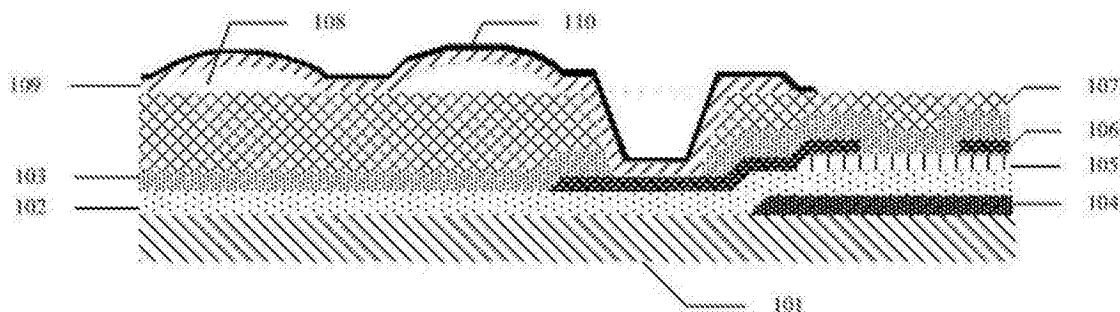

[0003] 对于透射式液晶显示装置,其内置背光源需处于常开状态,功耗大,并且当液晶显示装置处于户外且阳光过强时,显示器上图像不能清晰显示。半反射半投射式液晶显示装置,其利用内置的反射层,使得环境中的光源入射到反射层之后反射,然后从像素区域投射出去,以达到显示目的,但是该种液晶显示装置采用偏振光的原理,所以发光效率低,亮度和对比度低。而全反射式液晶显示装置可反射外界光源,然后通过对反射光进行调制而显示图像,可极大地降低功耗。图1示出了现有技术中全反射式液晶显示装置的阵列基板的结构示意图,现有的全反射式液晶显示装置通常需要在阵列基板101上形成绝缘层102、钝化层103、栅极层104、非晶硅层105、源漏极层106、有机层107、有机凸起层108、反射层109、透明电极层110,如图1所示,制作工艺复杂、成本高。

### 发明内容

[0004] 鉴于现有技术中的上述缺陷,本申请实施例提供一种阵列基板及其制作方法以及包括该阵列基板的液晶显示装置,来解决以上背景技术部分提到的技术问题。

[0005] 为了实现上述目的,第一方面,本申请实施例提供了一种阵列基板,包括:设置于基板上的多个凸起结构,覆盖于所述凸起结构上的反射层,以及覆盖于所述反射层上的透明电极层,其中,所述凸起结构包括栅极层、非晶硅层、源漏极层、绝缘层和钝化层。

[0006] 第二方面,本申请实施例还提供了一种液晶显示装置,包括上述的阵列基板。

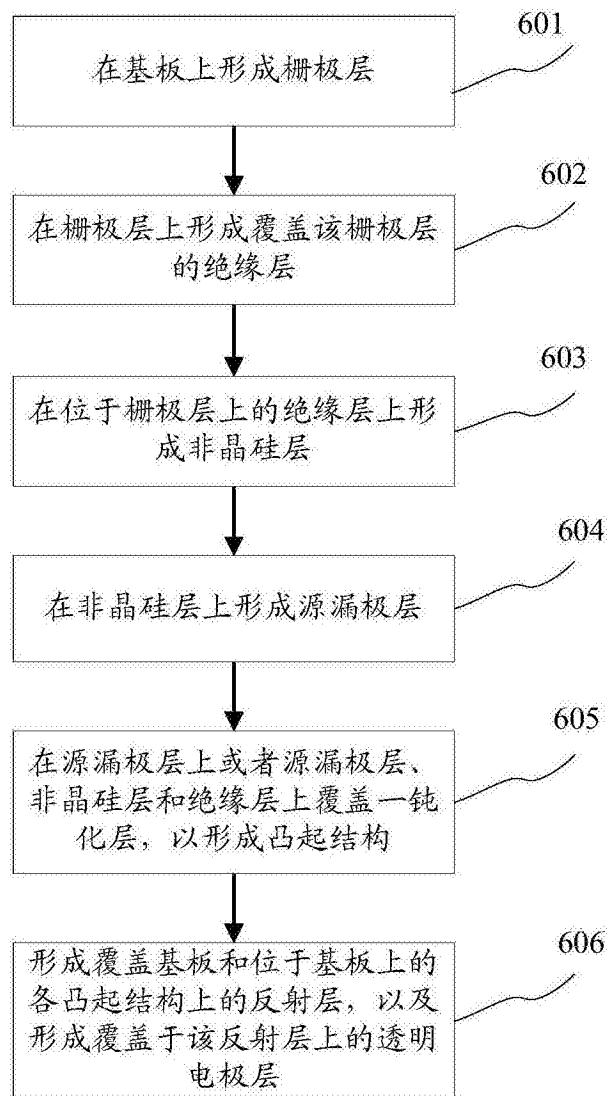

[0007] 第三方面,本申请实施例还提供了一种阵列基板的制作方法,所述方法包括:在基板上形成栅极层,其中,所述栅极层包括多个栅极层图案,所述栅极层图案的形状为第一凸台;在所述栅极层上形成覆盖所述栅极层的绝缘层;在位于所述栅极层上的绝缘层上形成非晶硅层;在所述非晶硅层上形成源漏极层;在所述源漏极层上或者所述源漏极层、非晶硅层和绝缘层上覆盖一钝化层,以形成凸起结构;形成覆盖所述基板和位于所述基板上的各所述凸起结构上的反射层,以及形成覆盖于所述反射层上的透明电极层。

[0008] 本申请实施例提供的阵列基板及其制作方法、液晶显示装置,该阵列基板包括在基板上的由栅极层、非晶硅层、源漏极层、绝缘层和钝化层构成的多个凸起结构,以及覆盖在凸起结构上反射层和覆盖在反射层上的透明电极层,而不包括有机层和有机凸起层,该阵列基板制作工艺简单、成本低。

## 附图说明

[0009] 通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本申请的其它特征、目的和优点将会变得更明显:

- [0010] 图1示出了现有技术中全反射式液晶显示装置的阵列基板的结构示意图;

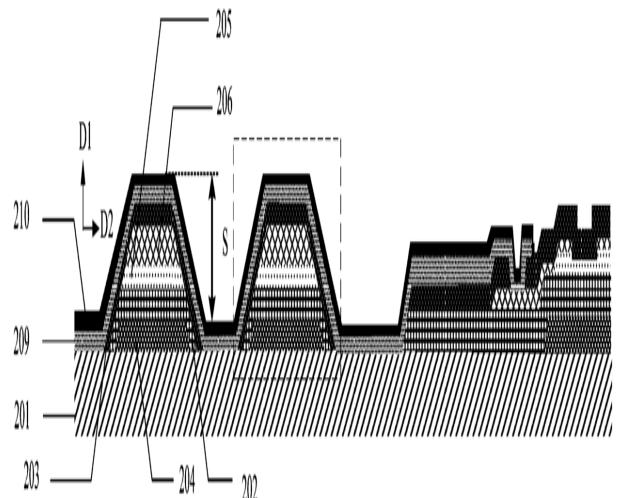

- [0011] 图2A示出了本申请的阵列基板的第一实施例的结构示意图;

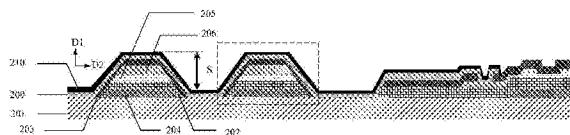

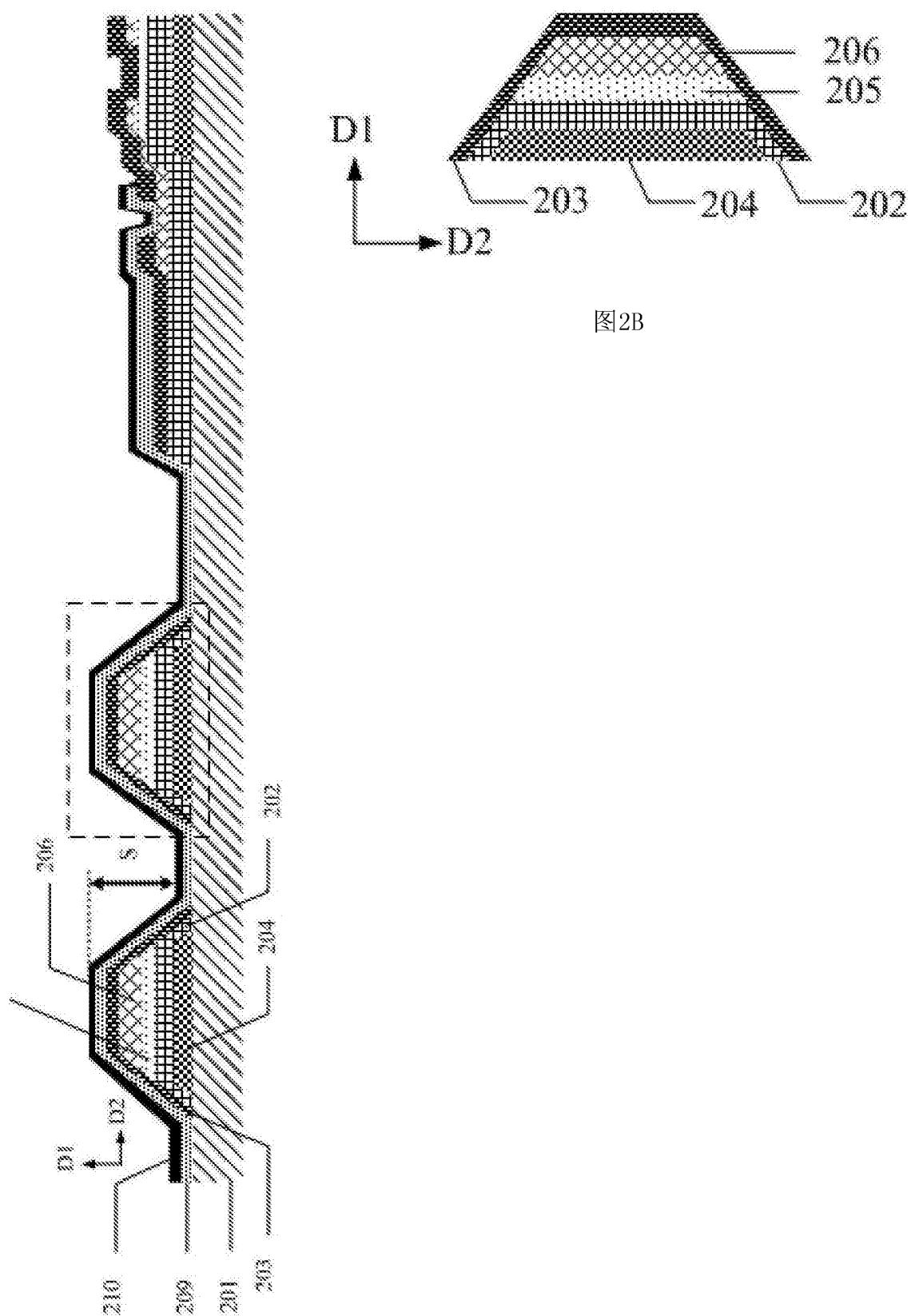

- [0012] 图2B示出了本申请的阵列基板的一种凸起结构的示意图;

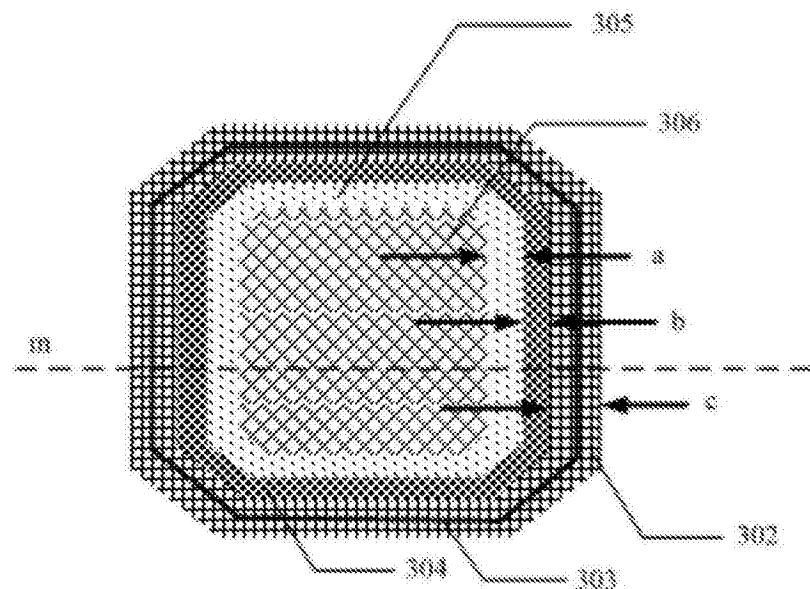

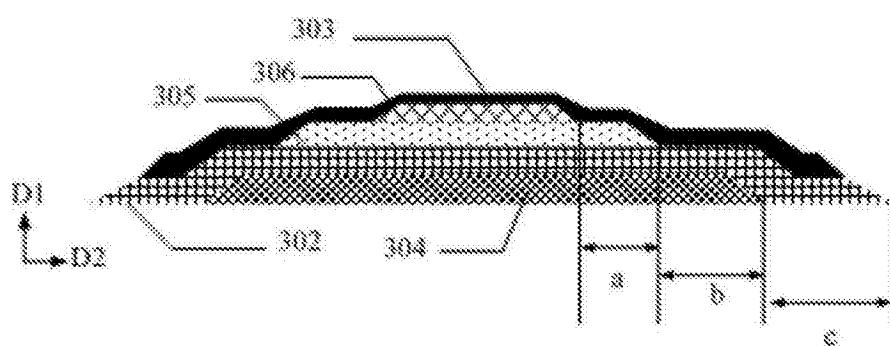

- [0013] 图3A示出了本申请的阵列基板的另一种凸起结构的俯视图;

- [0014] 图3B示出了图3A中凸起结构的剖视图;

- [0015] 图4示出了本申请的阵列基板的第二实施例的结构示意图;

- [0016] 图5示出了本申请的阵列基板的第三实施例的结构示意图;

- [0017] 图6示出了本申请的阵列基板的制作方法的一种实施例的示意性流程图。

## 具体实施方式

[0018] 下面结合附图和实施例对本申请的原理和特征作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与发明相关的一部分。

[0019] 需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本申请。

[0020] 请参考图2A,其为本申请的阵列基板的第一实施例的结构示意图。该图为本实施例的阵列基板的剖面图,如图所示,本申请的阵列基板包括:设置于基板201上的多个如图中虚线框中所示的凸起结构,该凸起结构的具体结构可以如图2B所示,覆盖于各凸起结构上的反射层209,以及覆盖于上述反射层209上的透明电极层210。

[0021] 在本实施例中,如图2A所示,阵列基板中的各凸起结构包括栅极层204、非晶硅层205、源漏极层206、绝缘层202和钝化层203。由此可见,本实施例提供的阵列基板可以包括栅极层204、非晶硅层205、源漏极层206、绝缘层202、钝化层203、反射层209和透明电极层210。与图1中的阵列基板相比,本申请提供的阵列基板不包括图1中所示的有机层107和有机凸起层108,而图1所示的阵列基板和本申请提供的阵列基板的主要区别在于图1所示的阵列基板可以通过有机层107和有机凸起层108使得反射层109凸起一定高度以使入射到该阵列基板所在的液晶显示装置的光实现漫反射,而本申请中如图2A所示的阵列基板,可以通过刻蚀上述多个膜层,以使得各个膜层组合形成的凸起与现有技术中有机凸起层形成的凸起具有相当的高度。上述多个膜层使得反射层209凸起一定高度以使入射到该阵列基板所在的液晶显示装置的光实现漫反射,使得来自自然界的光,通过反射层209可以向各个方向均匀反射,提高了各个方向的可视性。因此,上述阵列基板可以省略有机层和有机凸起层,使得本申请中的阵列基板制作工艺简化、成本降低。

[0022] 本实施例提供的阵列基板,还包括有扫描线、数据线、TFT元件等元件,这些元件可以和现有技术中的元件采用相同的结构,因此不再赘述。需要说明的是,扫描线和TFT元件中的栅极可以和凸起中的栅极层同层设置,TFT元件中的有源层可以和凸起中的非晶硅层同层设置,TFT元件中的源、漏极以及数据线可以和凸起中的源漏极层同层设置。本实施例

提供的阵列基板,相比现有技术,所有结构可以通过现有技术中的一些工序制得,不增加额外的成本。

[0023] 在本实施例的一些可选的实现方式中,在上述阵列基板中,上述透明电极层210上的任意二点在第一方向上的高度差的最大值S满足: $1 \times 10^{-6}$ 米≤S≤ $1.3 \times 10^{-6}$ 米,即,凸起的最大高度S满足 $1 \times 10^{-6}$ 米≤S≤ $1.3 \times 10^{-6}$ 米,如图2A所示。当阵列基板中的S满足上述条件时,该阵列的基板中的反射层209可以具备较高的漫反射率,使得该阵列基板所在的全反射式液晶显示装置具有较佳的显示效果。

[0024] 在本实施例的一些可选的实现方式中,上述阵列基板中的任意一个凸起结构的剖面图可以如图2B所示。在该凸起结构中,栅极层204、绝缘层202、非晶硅层205、源漏极层206和钝化层203沿第一方向D1依次设置,并且上述第一方向D1与上述基板201的上表面垂直。在上述阵列基板中的栅极层204可以包括多个栅极层图案,每一个栅极层图案的形状为第一凸台,并且该第一凸台包括顶面、底面和侧面,并且底面和顶面相互平行,如图2B所示。这里的第一凸台可以为圆台、棱台等,具体形状可以根据上述凸起结构的形状确定。在上述凸起结构中绝缘层202可以至少完全覆盖上述各第一凸台的顶面和侧面,即该绝缘层202可以仅完全覆盖在上述各第一凸台的顶面和侧面,而不覆盖上述基板201的除了第一凸台的其他区域,或者还可以完全覆盖在上述各第一凸台的顶面和侧面、以及上述基板201,上述非晶硅层205可以完全覆盖于上述栅极层204上的绝缘层202的顶面,上述源漏极层206可以完全覆盖于上述非晶硅层205的顶面,上述钝化层203至少完全覆盖于上述源漏极层206的顶面和侧面、非晶硅层205的侧面和绝缘层202的外侧面,形成如图2B所示的凸台结构。

[0025] 在本实施例的一些可选的实现方式中,上述凸起结构中的栅极层204、绝缘层202、非晶硅层205、源漏极层206和钝化层203沿第一方向D1依次设置,并且上述第一方向D1与上述基板201的上表面垂直。在上述阵列基板中的栅极层204包括多个栅极层图案,每一个栅极层图案的形状可以为第一凸台,该第一凸台包括顶面、底面和侧面,底面和顶面相互平行。并且在上述凸起结构中绝缘层202至少完全覆盖上述各第一凸台的顶面和侧面,上述非晶硅层205完全覆盖于上述栅极层204上的绝缘层202的顶面和外侧面,上述源漏极层206可以完全覆盖于上述非晶硅层205的顶面和外侧面,上述钝化层203至少完全覆盖于上述源漏极层206的顶面和外侧面。

[0026] 需要说明的是,上述凸起结构的形状、高度等可以影响上述阵列基板所在全反射式液晶显示装置的漫反射率,因此,通常在保证上述液晶显示装置的漫反射率足够大的情况下,该凸起结构可以具有不同的形状和高度。

[0027] 在本实施例的一些可选的实现方式中,上述阵列基板中的凸起结构还可以如图3A和图3B所示,其中图3A为本申请的阵列基板的另一种凸起结构的俯视图,图3B为图3A中凸起结构为沿虚线m形成的剖面图。如图3B所示,在上述阵列基板的凸起结构中绝缘层302可以部分覆盖栅极层304中的第一凸台顶面和侧面,非晶硅层305可以部分覆盖上述各第一凸台上的绝缘层302的顶面,其中,上述非晶硅层305包括多个形状为第二凸台的非晶硅,该第二凸台包括顶面、底面和侧面,且该第二凸台的底面和顶面相互平行;在上述阵列基板中的源漏极层306至少部分覆盖上述非晶硅层305的顶面,其中,上述源漏极层306包括多个形状为第三凸台的源漏极,该第三凸台包括顶面、底面和侧面,该第三凸台的底面和顶面相互平行;上述钝化层303完全覆盖上述源漏极层306中各第三凸台的顶面和侧面、非晶硅层305中

各第二凸台的部分顶面和侧面、以及绝缘层302的部分顶面和侧面。

[0028] 在本实施例的一些可选的实现方式中,任意一上述凸起结构中的源漏极层306与该凸起结构中的非晶硅层305在第二方向上的长度差可以为a,即在上述凸起结构中的第三凸台与第二凸台在第二方向D2上的长度差可以为a,上述非晶硅层305与该凸起结构中的栅极层304在第二方向上的长度差可以为b,即在上述凸起结构中的第二凸台与第一凸台在第二方向上的长度差可以为b,上述栅极层与该凸起结构中的绝缘层302在第二方向上的长度差可以为c,即在上述凸起结构中的第一凸台与覆盖在该第一凸台上的绝缘层302在第二方向上的长度差可以为c,其中,a≥0,b≥0,c≥1×10<sup>-6</sup>米,并且这里的第二方向与上述第一方向垂直。或者,在图3A中,对于上述长度差a、b、c还可以进行如下描述:上述源漏极层306正投影的轮廓与非晶硅层305正投影的轮廓在第二方向上D2的长度差可以为a,非晶硅层305正投影的轮廓与栅极层304正投影的轮廓在第二方向D2上的长度差可以为b,栅极层304正投影的轮廓与绝缘层302正投影的轮廓在第二方向上D2的长度差可以为c,其中,a≥0,b≥0,c≥1×10<sup>-6</sup>米,钝化层303覆盖在上述源漏极层306、非晶硅层305以及绝缘层302,为了在图3A中清楚的显示出上述源漏极层306、非晶硅层305以及绝缘层302,这里用黑色线框表示上述钝化层303。需要注意的是,这里说的长度长为单侧的长度差,如图3B中所示,例如,第一凸台和第二凸台,在图示的左侧和右侧,都具有一长度差,此时,左侧的长度差和右侧的长度差都应当大于等于1×10<sup>-6</sup>米。即,第一凸台和第二凸台在基板上的正投影轮廓的任意两点之间的最小距离应当大于等于1×10<sup>-6</sup>米。例如,当上述凸起结构如图3A和3B所示时,该凸起结构中的源漏极层306、非晶硅层305、栅极层304、绝缘层302等的俯视图为图3A所示的八边形,这里可以选取上述八边形的几何中心为起点,之后沿如图所述的第二方向D2测量获取上述源漏极层306、非晶硅层305、栅极层304、绝缘层302的长度,上述凸起结构中的源漏极层306的长度可以小于等于非晶硅层305的长度,非晶硅层305的长度可以小于等于栅极层304的长度,上述栅极层304的长度与绝缘层302的长度差可以大于等于1×10<sup>-6</sup>米,使得上述源漏极层306、非晶硅层305和栅极层302在俯视图中相互重叠或嵌套,如图3B所示。

[0029] 本申请的上述实施例提供的阵列基板,包括由栅极层、非晶硅层、源漏极层、绝缘层、钝化层、反射层和透明电极层,可以通过刻蚀绝缘层和钝化层形成凸起结构来满足该阵列基板所在的液晶显示装置的全反射要求,该结构的阵列基板可以取代现有的通过有机层和有机凸起层形成凸起高度满足全反射的阵列基板,并且本实施例提供的阵列基板制作工艺简单、成本低。

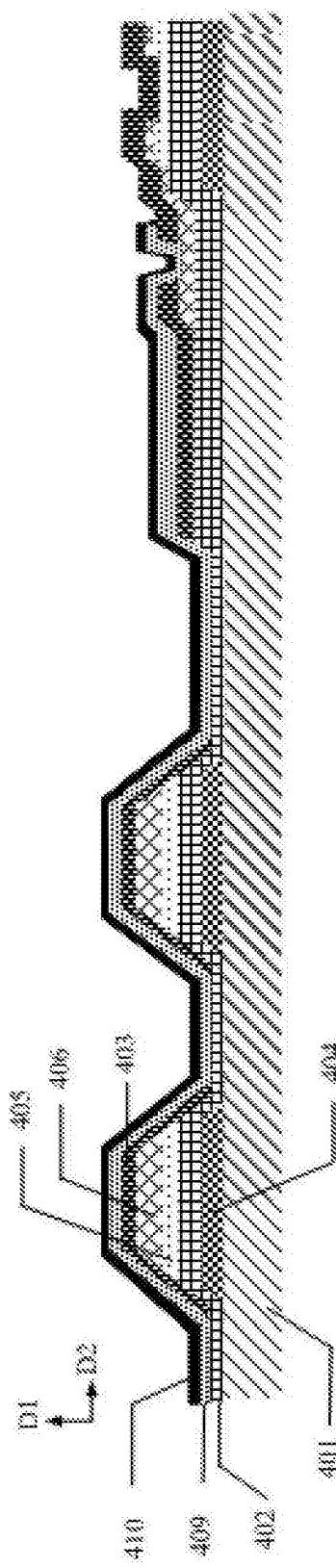

[0030] 继续参考图4,其为本申请的阵列基板的第二实施例的结构示意图。该图为本实施例的阵列基板的剖面图,如图所示,上述阵列基板中凸起结构的栅极层404、绝缘层402、非晶硅层405、源漏极层406和钝化层403沿第一方向D1依次设置,并且上述第一方向D1与上述基板401的上表面垂直。在上述阵列基板中的栅极层404包括多个栅极层图案,每一个栅极层图案的形状为第一凸台,该第一凸台包括顶面、底面和侧面,并且该第一凸台的底面和顶面相互平行。这里的凸起结构的具体形状可以如图2B或者图3B所示,这里没有唯一的限定。上述第一凸台可以为圆台、棱台等,具体形状可以根据上述凸起结构确定。

[0031] 在本实施例中,上述阵列基板中的绝缘层402除了可以完全覆盖在各第一凸台形状的栅极层图案的顶面和侧面之外,该绝缘层402还可以覆盖在上述第一凸台的基板401上,如图4所示,并且上述非晶硅层405至少完全覆盖于上述栅极层404上的绝缘层402的顶

面,上述源漏极层406至少完全覆盖于上述非晶硅层405的顶面,上述钝化层403可以仅完全覆盖于上述源漏极层106的顶面和侧面、非晶硅层405的侧面和绝缘层402的外侧面,而不覆盖直接与上述基板401相接触的绝缘层402,如图4所示。

[0032] 在本实施例的一些可选的实现方式中,上述阵列基板的各凸起结构的第一凸台可以相互独立,或者上述阵列基板的至少两个凸起结构中的第一凸台还可以相连接。当存在至少两个上述第一凸台相连接时,可以使得该阵列基板所在的液晶显示装置的公共电极的表面积增大,进而使得公共电极形成的电容增大。

[0033] 本申请的上述实施例提供的阵列基板,包括由栅极层、非晶硅层、源漏极层、绝缘层、钝化层、反射层和透明电极层,可以通过刻蚀钝化层形成凸起结构来实现该阵列基板所在的液晶显示装置的漫反射,并且本实施例提供的阵列基板制作工艺简单、成本低。

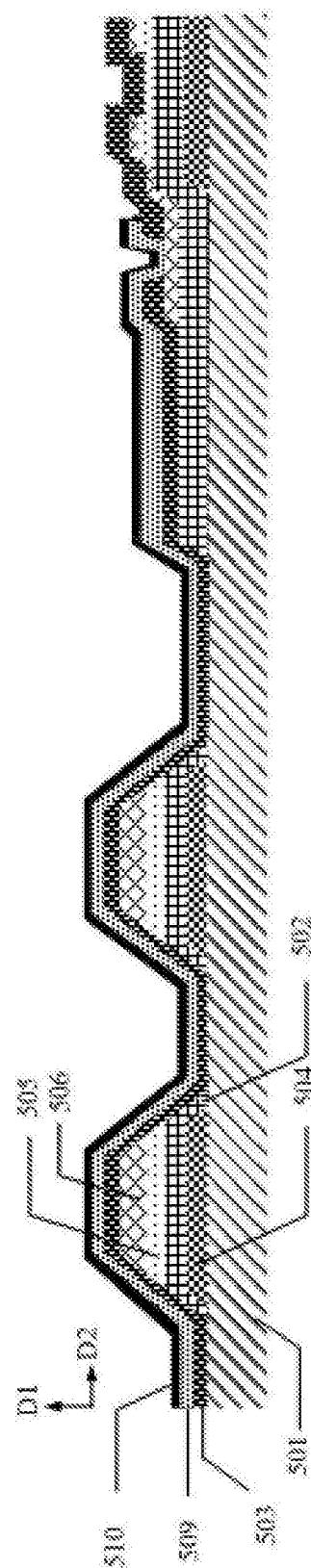

[0034] 请参考图5,其为本申请的阵列基板的第三实施例的结构示意图。该图为本实施例的阵列基板的剖面图,如图所示,上述阵列基板中的凸起结构的栅极层504、绝缘层502、非晶硅层505、源漏极层506和钝化层503沿第一方向D1依次设置,并且上述第一方向D1与上述基板501的上表面垂直。在上述阵列基板中的栅极层504包括多个栅极层图案,每一个栅极层图案的形状为第一凸台,该第一凸台包括顶面、底面和侧面,并且该第一凸台的底面和顶面相互平行。这里的凸起结构的具体形状可以如图2B或者图3B所示,这里没有唯一的限定。上述第一凸台可以为圆台、棱台等,具体形状可以根据上述凸起结构确定。

[0035] 在本实施例中,上述阵列基板中的绝缘层502可以仅完全覆盖在栅极层中各第一凸台的顶面和侧面,上述非晶硅层505至少完全覆盖于上述栅极层504上的绝缘层502的顶面,上述源漏极层506至少完全覆盖于上述非晶硅层505的顶面,上述钝化层503除了可以完全覆盖于上述源漏极层506的顶面和侧面、非晶硅层505的侧面和绝缘层502的外侧面之外,该钝化层503还可以覆盖在不包括上述第一凸台的基板501上,形成如图5所示的阵列基板。

[0036] 本申请的上述实施例提供的阵列基板,包括由栅极层、非晶硅层、源漏极层、绝缘层、钝化层、反射层和透明电极层,可以通过刻蚀绝缘层形成凸起结构来实现该阵列基板所在的液晶显示装置的漫反射,并且本实施例提供的阵列基板制作工艺简单、成本低。

[0037] 接下来请参考图6,其示出了本申请的阵列基板的制作方法的一种实施例的示意性流程图。所述的阵列基板的制作方法,包括如下步骤:

[0038] 步骤601,在基板上形成栅极层。

[0039] 在本实施例中,可以首先确定上述阵列基板中用于形成栅极层等的基板,这里的基板可以为玻璃、石英或其它不同材料,而后可以采用蒸镀、化学沉积等方式在上述基板上形成覆盖在整个基板的栅极层材料,最后刻蚀上述栅极层材料,使其形成包括多个栅极层图案的栅极层,并且这里的栅极层图案的形状为第一凸台。其中,栅极层材料可以采用钼金属、钼合金、铝金属、铝合金、铜金属、铜合金、铬金属或铬合金等。并且,在形成栅极层图案的这一工序中,形成了扫描线以及TFT元件的栅极。并且栅极和形成凸起的栅极层图案绝缘。

[0040] 需要说明的是,上述第一凸台可以为圆台或棱台等,具体形状可以根据上述凸起结构确定,上述第一凸台包括顶面、底面和侧面,并且该底面和顶面相互平行。

[0041] 步骤602,在栅极层上形成覆盖该栅极层的绝缘层。

[0042] 在本实施例中,可以在上述形成的栅极层上通过沉积等方式形成覆盖在阵列基板

上表面的绝缘层材料,使得形成的绝缘层至少覆盖在上述栅极层中的各第一凸台的顶面和侧面。该绝缘层材料可以为硅的氧化物(SiO<sub>x</sub>)、硅的氮化物(SiN<sub>x</sub>)等。

[0043] 在本实施例的一些可选的实现方式中,可以对位于上述基板上的绝缘层材料刻蚀,使其形成完全覆盖在上述各第一凸台的顶面和侧面的绝缘层,此时仅与上述第一凸台侧面的相邻部分的基板覆盖有绝缘层。或者,上述形成的绝缘层除了可以覆盖在各第一凸台的顶面和侧面之外,还可以覆盖在不包括上述第一凸台的基板上,此时绝缘层完全覆盖上述基板和栅极形成的表面。

[0044] 步骤603,在位于栅极层上的绝缘层上形成非晶硅层。

[0045] 在本实施例中,可以形成覆盖在阵列基板上表面的一层非晶硅材料,而后对其进行刻蚀,形成上述非晶硅层,该非晶硅层可以完全覆盖位于上述栅极层中各第一凸台的顶面。这里的非晶硅层可以包括多个形状为第二凸台的非晶硅,该第二凸台包括顶面、底面和侧面,并且底面和顶面相互平行。此外,TFT元件的有源层也在该工序中形成。

[0046] 在本实施例的一些可选的实现方式中,还可以对上述形成的覆盖在阵列基板上表面的非晶硅材料进行刻蚀,形成可以部分覆盖位于上述栅极层中各第一凸台的顶面的非晶硅层。

[0047] 在本实施例的一些可选的实现方式中,还可以对上述形成的覆盖在阵列基板上表面的非晶硅材料进行刻蚀,形成可以完全覆盖上述栅极层上的绝缘层的顶面和外侧面的非晶硅层。

[0048] 步骤604,在非晶硅层上形成源漏极层。

[0049] 在本实施例中,可以形成覆盖在阵列基板上表面的一层源漏极层材料,而后对其进行刻蚀,形成上述源漏极层,该源漏极层可以完全覆盖在上述非晶硅层中的各第二凸台的顶面。这里的源漏极层可以包括多个形状为第三凸台的源漏极,该第三凸台包括顶面、底面和侧面,并且底面和顶面相互平行。同样的,在形成源漏极层的这一工序中,同时形成了数据线以及TFT元件的源漏极,并且源漏极和形成凸起的源漏极层图案绝缘。

[0050] 在本实施例的一些可选的实现方式中,还可以对上述形成的覆盖在阵列基板上表面的源漏极层材料进行刻蚀,形成可以部分覆盖上述非晶硅层中的各第二凸台的顶面的源漏极层。

[0051] 在本实施例的一些可选的实现方式中,还可以对上述形成的覆盖在阵列基板上表面的源漏极层材料进行刻蚀,形成可以完全覆盖上述非晶硅层的顶面和外侧面的源漏极层。

[0052] 步骤605,在源漏极层上或者源漏极层、非晶硅层和绝缘层上覆盖一钝化层,以形成凸起结构。

[0053] 在本实施例中,可以形成覆盖在阵列基板上表面的一层钝化层材料,而后对其进行刻蚀,形成上述钝化层。具有而言,若上述非晶硅层完全覆盖于上述栅极层上的绝缘层的顶面和外侧面,且上述源漏极层完全覆盖于上述非晶硅层的顶面和外侧面,则可以在该源漏极层的顶面和外侧面覆盖上述钝化层;若上述非晶硅层至少部分覆盖上述绝缘层的顶面,且上述源漏极层至少部分覆盖上述非晶硅层的各第二凸台的顶面,则可以在上述源漏极层、非晶硅层和绝缘层上覆盖钝化层。

[0054] 在实施例的一些可选的实现方式中,若已经对上述绝缘层材料进行刻蚀形成了仅

覆盖各第一凸台的顶面和侧面的绝缘层，则在上述源漏极层或者源漏极层、非晶硅层、绝缘层和基板上覆盖钝化层材料后，可以刻蚀位于基板上的钝化层以形成上述凸起结构，该凸起结构可以形成如图2所示的阵列基板。

[0055] 在实施例的一些可选的实现方式中，若上述绝缘层覆盖在上述基板和位于该基板上的各第一凸台的顶面和侧面，则在上述源漏极层上或者上述源漏极层、非晶硅层和绝缘层上覆盖钝化层材料后，刻蚀位于上述基板上的绝缘层上的钝化层以形成上述凸起结构，该凸起结构可以形成如图4所示的阵列基板。或者，若上述绝缘层覆盖在上述基板和位于该基板上的各第一凸台的顶面和侧面，则在上述源漏极层上或者上述源漏极层、非晶硅层和绝缘层上覆盖钝化层材料后，可以刻蚀位于上述基板上的绝缘层和钝化层以形成上述凸起结构，该凸起结构可以形成如图2所示的阵列基板。

[0056] 在实施例的一些可选的实现方式中，若已经对上述绝缘层材料进行刻蚀形成了仅覆盖各第一凸台的顶面和侧面的绝缘层，则在上述源漏极层或者源漏极层、非晶硅层、绝缘层和基板上覆盖钝化层材料后，可以不刻蚀上述钝化层直接形成上述凸起结构，该凸起结构可以形成如图5所示的阵列基板。

[0057] 在实施例的一些可选的实现方式中，上述凸起结构中的源漏极层与该凸起结构中的非晶硅层在第二方向上的长度差为，上述非晶硅层与该凸起结构中的栅极层在第二方向上的长度差为b，上述栅极层与该凸起结构中的绝缘层在第二方向上的长度差为c，其中， $a \geq 0, b \geq 0, c \geq 1 \times 10^{-6}$ 米，并且这里的第二方向与上述第一方向垂直。

[0058] 步骤606，形成覆盖基板和位于基板上的各凸起结构上的反射层，以及形成覆盖于该反射层上的透明电极层。

[0059] 在本实施例中，可以首先形成覆盖在上述凸起结构和基板上的反射层，而后形成覆盖于上述反射层上的透明电极层。

[0060] 在实施例的一些可选的实现方式中，在上述阵列基板上，透明电极层上的任意二点在第一方向上的高度差的最大值S满足： $1 \times 10^{-6}$ 米  $\leq S \leq 1.3 \times 10^{-6}$ 米，这里的第一方向与上述基板垂直。

[0061] 在本实施例的一些可选的实现方式中，上述阵列基板的至少两个凸起结构中的第一凸台相连接，此种结构可以使得该阵列基板所在的液晶显示装置的公共电极的表面积增大，进而使得公共电极形成的电容增大。

[0062] 本申请的上述实施例提供的阵列基板的制作方法，可以制备上述结构的阵列基板，其可以在基板上依次形成栅极层、绝缘层、非晶硅层、源漏极层以及钝化层，并且对上述绝缘层和/或钝化层进行刻蚀形成具有一定高度和形状的多个凸起结构，之后在各凸起结构和基板上依次覆盖反射层和透明电极层，而不需要形成有机层和有机凸起层，此种方法制作阵列基板简化了制备工艺、降低了制备成本。

[0063] 需要说明的，本领域的技术人员可以对本发明进行各种改动和变形而不脱离本发明的范围。这样，倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内，则本发明也意图包含这些改动和变型在内。

[0064] 此外，本申请还提供了一种液晶显示装置，包括上述实施例中的阵列基板。该阵列基板的具体结构和制作方法与上述实施例相同，这里不再赘述。

[0065] 以上描述仅为本申请的较佳实施例以及对所运用技术原理的说明。本领域技术人

员应当理解,本申请中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离所述发明构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本申请中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

图1

图2A

图2B

图3A

图3B

图4

图5

图6

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 阵列基板及其制作方法、液晶显示装置                              |         |            |

| 公开(公告)号        | <a href="#">CN105739157A</a>                   | 公开(公告)日 | 2016-07-06 |

| 申请号            | CN201610290291.1                               | 申请日     | 2016-05-04 |

| [标]申请(专利权)人(译) | 上海中航光电子有限公司<br>天马微电子股份有限公司                     |         |            |

| 申请(专利权)人(译)    | 上海中航光电子有限公司<br>天马微电子股份有限公司                     |         |            |

| 当前申请(专利权)人(译)  | 上海中航光电子有限公司<br>天马微电子股份有限公司                     |         |            |

| [标]发明人         | 席克瑞<br>朱娟<br>杜雷<br>周一安                         |         |            |

| 发明人            | 席克瑞<br>朱娟<br>杜雷<br>周一安                         |         |            |

| IPC分类号         | G02F1/1333 G02F1/1362                          |         |            |

| CPC分类号         | G02F1/1333 G02F1/1362 G02F2001/133302          |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

## 摘要(译)

本申请公开了一种阵列基板及其制作方法、液晶显示装置，所述阵列基板包括：设置于基板上的多个凸起结构，覆盖于所述凸起结构上的反射层，以及覆盖于所述反射层上的透明电极层，其中，所述凸起结构包括栅极层、非晶硅层、源漏极层、绝缘层和钝化层。上述用于全反射的阵列基板可以只包括栅极层、非晶硅层、源漏极层、绝缘层钝化层、反射层和透明电极层，而不需要有机层和有机凸起层，可以简化阵列基板的制作工艺，降低成本。