(12)发明专利申请

(10)申请公布号 CN 108335681 A

(43)申请公布日 2018.07.27

(21)申请号 201810148674.4

(22)申请日 2018.02.13

(71)申请人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路10号

申请人 合肥鑫晟光电科技有限公司

(72)发明人 杨海鹏 王登峰 戴珂 周茂秀

(74)专利代理机构 北京风雅颂专利代理有限公司 11403

代理人 朱亲林

(51)Int.Cl.

G09G 3/36(2006.01)

H01L 27/02(2006.01)

权利要求书1页 说明书5页 附图2页

(54)发明名称

一种用于薄膜晶体管的防静电单元、驱动电路及显示装置

(57)摘要

本发明公开了一种用于薄膜晶体管的防静电单元、驱动电路及显示装置，属于液晶显示相关技术领域。其中，所述用于薄膜晶体管的防静电单元中，所述薄膜晶体管的第一极与输入端之间或者所述薄膜晶体管的栅极与第一极或第二极之间设置有防静电单元，用于保护所述薄膜晶体管不受到静电破坏；其中，所述薄膜晶体管的第一极为源极或漏极，所述薄膜晶体管的第二极为对应的漏极或源极；所述输入端为静电发生端。本申请所述防静电单元能够消除静电对相应薄膜晶体管带来的损坏，进而保证显示质量、提高产品良率。

1. 一种用于薄膜晶体管的防静电单元,其特征在于,所述薄膜晶体管的第一极与输入端之间或者所述薄膜晶体管的栅极与第一极或第二极之间设置有防静电单元,用于保护所述薄膜晶体管不受到静电破坏;其中,所述薄膜晶体管的第一极为源极或漏极,所述薄膜晶体管的第二极为对应的漏极或源极;所述输入端为静电发生端。

2. 根据权利要求1所述的防静电单元,其特征在于,所述防静电单元包括第一薄膜晶体管;所述第一薄膜晶体管的栅极与所述第一薄膜晶体管的第一极连接;所述第一薄膜晶体管的第一极连接到输入端,所述第一薄膜晶体管的第二极连接到所述薄膜晶体管的第一极;其中,所述第一薄膜晶体管的第一极为源极或漏极,所述第一薄膜晶体管的第二极为对应的漏极或源极。

3. 根据权利要求2所述的防静电单元,其特征在于,所述防静电单元还包括第二薄膜晶体管;所述第二薄膜晶体管的栅极与所述第二薄膜晶体管的第一极连接;所述第二薄膜晶体管的第一极与所述薄膜晶体管的第二极连接;所述第二薄膜晶体管的第二极连接到输出端;所述第二薄膜晶体管的第一极为源极或漏极,所述第二薄膜晶体管的第二极为对应的漏极或源极。

4. 根据权利要求3所述的防静电单元,其特征在于,所述防静电单元设置有多个串联设置的第二薄膜晶体管。

5. 根据权利要求2-4任一项所述的防静电单元,其特征在于,所述防静电单元设置有多个串联设置的第一薄膜晶体管。

6. 根据权利要求1所述的防静电单元,其特征在于,所述防静电单元包括第三薄膜晶体管;所述第三薄膜晶体管的栅极与所述薄膜晶体管的栅极连接;所述第三薄膜晶体管的第一极与所述薄膜晶体管的第一极或第二极连接;所述第三薄膜晶体管的第二极为浮接状态;所述第三薄膜晶体管的第一极为源极或漏极,所述第三薄膜晶体管的第二极为对应的漏极或源极。

7. 根据权利要求6所述的防静电单元,其特征在于,所述防静电单元还包括第四薄膜晶体管;所述第四薄膜晶体管的栅极与所述薄膜晶体管的栅极连接;所述第四薄膜晶体管的第一极与所述薄膜晶体管对应的第二极或第一极连接;所述第四薄膜晶体管的第二极为浮接状态;所述第四薄膜晶体管的第一极为源极或漏极,所述第四薄膜晶体管的第二极为对应的漏极或源极。

8. 根据权利要求7所述的防静电单元,其特征在于,所述防静电单元设置有多个并联设置的第三薄膜晶体管;

和/或,所述防静电单元设置有多个并联设置的第四薄膜晶体管。

9. 一种驱动电路,其特征在于,所述驱动电路包括至少一个如权利要求1-8任一项所述的用于薄膜晶体管的防静电单元。

10. 一种显示装置,其特征在于,所述显示装置包括权利要求9所述的驱动电路。

## 一种用于薄膜晶体管的防静电单元、驱动电路及显示装置

### 技术领域

[0001] 本发明涉及液晶显示相关技术领域,特别是指一种用于薄膜晶体管的防静电单元、驱动电路及显示装置。

### 背景技术

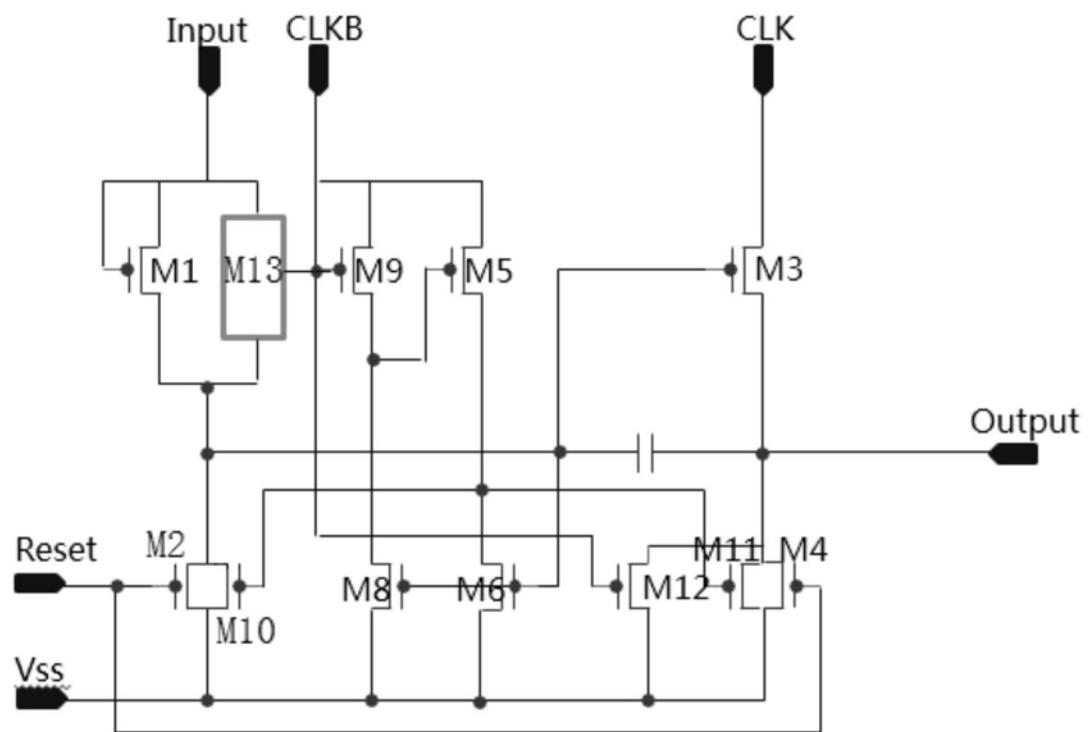

[0002] 当前随着手机、平板等显示设备的飞速发展与普及,液晶显示技术也不断飞速发展,其控制的精细度也越来越精细,控制要求同时相应提高。其中,在液晶显示相关设备中较为常用的就是TFT (Thin Film Transistor, 薄膜晶体管),但是基于相关电路中所需要的位置、体积以及功能需求的不同,在同一设备中的薄膜晶体管的尺寸也各不相同,而基于相关设备在生产制备、组装或者使用的过程中某些位置容易出现静电,而对于尺寸较小的薄膜晶体管来说,难以抵抗大静电带来的冲击,容易使得薄膜晶体管烧穿进而造成相关设备的损毁。例如:目前使用的12T1C GOA架构,如图1所示,STV0 (帧信号起始端或输入端) 的长度是Panel (面板) 宽带的大小,在这么长的线上工艺中很容易积累静电,而与STV0信号(即input信号)直接连接的薄膜晶体管只有M1或M13,而M13管设计值一般都很小,所以抗静电能力差,容易发生ESD (静电释放),这样将会使得产品良率下降,使得产品出现显示异常。

[0003] 因此,在实现本申请的过程中,发明人发现现有技术至少存在以下缺陷:当前设备中存在抗静电能力弱的薄膜晶体管,在设备出现静电尤其是大静电时,容易出现烧穿损毁现象,影响设备的显示或者产品良率。

### 发明内容

[0004] 有鉴于此,本发明的目的在于提出一种用于薄膜晶体管的防静电单元、驱动电路及显示装置,能够消除静电对相应薄膜晶体管带来的损坏,进而保证显示质量、提高产品良率。

[0005] 基于上述目的本发明提供的一种用于薄膜晶体管的防静电单元,所述薄膜晶体管的第一极与输入端之间或者所述薄膜晶体管的栅极与第一极或第二极之间设置有防静电单元,用于保护所述薄膜晶体管不受到静电破坏;其中,所述薄膜晶体管的第一极为源极或漏极,所述薄膜晶体管的第二极为对应的漏极或源极;所述输入端为静电发生端。

[0006] 可选的,所述防静电单元包括第一薄膜晶体管;所述第一薄膜晶体管的栅极与所述第一薄膜晶体管的第一极连接;所述第一薄膜晶体管的第一极连接到输入端,所述第一薄膜晶体管的第二极连接到所述薄膜晶体管的第一极;其中,所述第一薄膜晶体管的第一极为源极或漏极,所述第一薄膜晶体管的第二极为对应的漏极或源极。

[0007] 可选的,所述防静电单元还包括第二薄膜晶体管;所述第二薄膜晶体管的栅极与所述第二薄膜晶体管的第一极连接;所述第二薄膜晶体管的第一极与所述薄膜晶体管的第二极连接;所述第二薄膜晶体管的第二极连接到输出端;所述第二薄膜晶体管的第一极为源极或漏极,所述第二薄膜晶体管的第二极为对应的漏极或源极。

[0008] 可选的,所述防静电单元设置有多个串联设置的第二薄膜晶体管。

[0009] 可选的,所述防静电单元设置有多个串联设置的第一薄膜晶体管。

[0010] 可选的,所述防静电单元包括第三薄膜晶体管;所述第三薄膜晶体管的栅极与所述薄膜晶体管的栅极连接;所述第三薄膜晶体管的第一极与所述薄膜晶体管的第一极或第二极连接;所述第三薄膜晶体管的第二极为浮接状态;所述第三薄膜晶体管的第一极为源极或漏极,所述第三薄膜晶体管的第二极为对应的漏极或源极。

[0011] 可选的,所述防静电单元还包括第四薄膜晶体管;所述第四薄膜晶体管的栅极与所述薄膜晶体管的栅极连接;所述第四薄膜晶体管的第一极与所述薄膜晶体管对应的第二极或第一极连接;所述第四薄膜晶体管的第二极为浮接状态;所述第四薄膜晶体管的第一极为源极或漏极,所述第四薄膜晶体管的第二极为对应的漏极或源极。

[0012] 可选的,所述防静电单元设置有多个并联设置的第三薄膜晶体管;

[0013] 和/或,所述防静电单元设置有多个并联设置的第四薄膜晶体管。

[0014] 本申请还提供了一种驱动电路,所述驱动电路包括至少一个如上述任一项所述的用于薄膜晶体管的防静电单元。

[0015] 本申请还提供了一种显示装置,所述显示装置包括所述的驱动电路。

[0016] 从上面所述可以看出,本发明提供的用于薄膜晶体管的防静电单元、驱动电路及显示装置,通过在薄膜晶体管于静电发生端之间设置防静电单元,使得静电首先通过防静电单元而不会直接对薄膜晶体管造成损害,同时又不影响薄膜晶体管的正常工作时的信号传输,或者在所述薄膜晶体管的栅极与源漏极中的一个连接防静电单元,使得通过栅极连接所述防静电单元能够给薄膜晶体管起到分散电厂强度的作用,进而提高抗静电能力,也即能够避免静电损害。因此,本申请所述防静电单元能够消除静电对相应薄膜晶体管带来的损坏,进而保证显示质量、提高产品良率。

## 附图说明

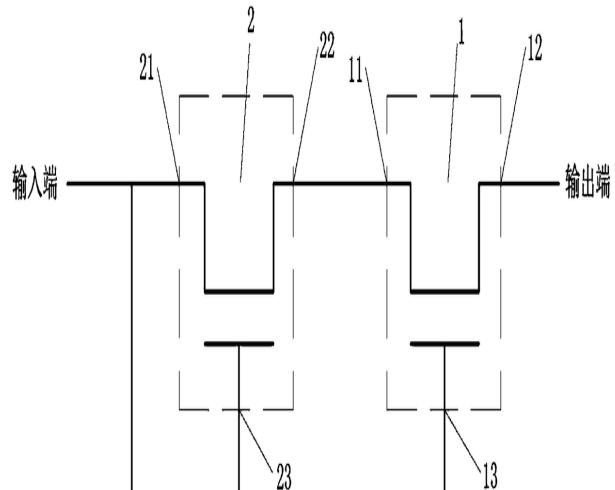

[0017] 图1为现有技术中一种GOA架构示意图;

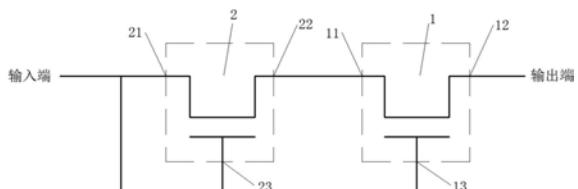

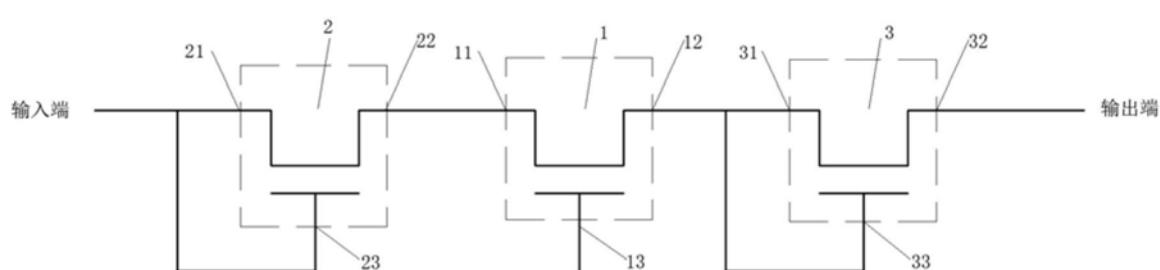

[0018] 图2为本发明提供的防静电单元第二个实施例的结构示意图一;

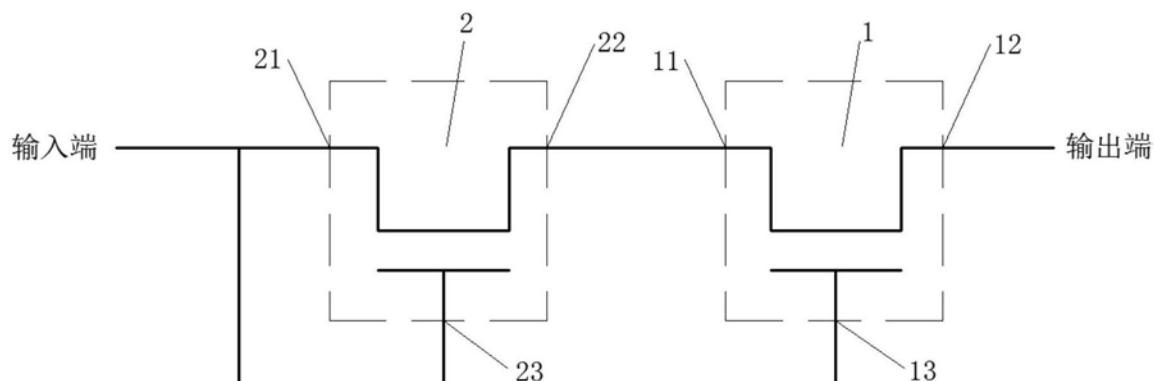

[0019] 图3为本发明提供的防静电单元第二个实施例的结构示意图二;

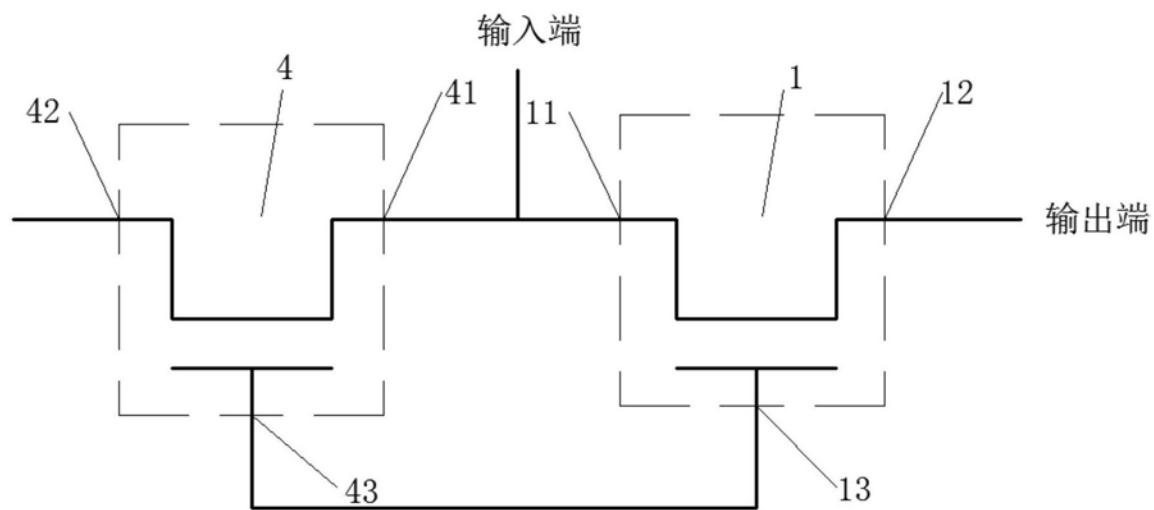

[0020] 图4为本发明提供的防静电单元第三个实施例的结构示意图一;

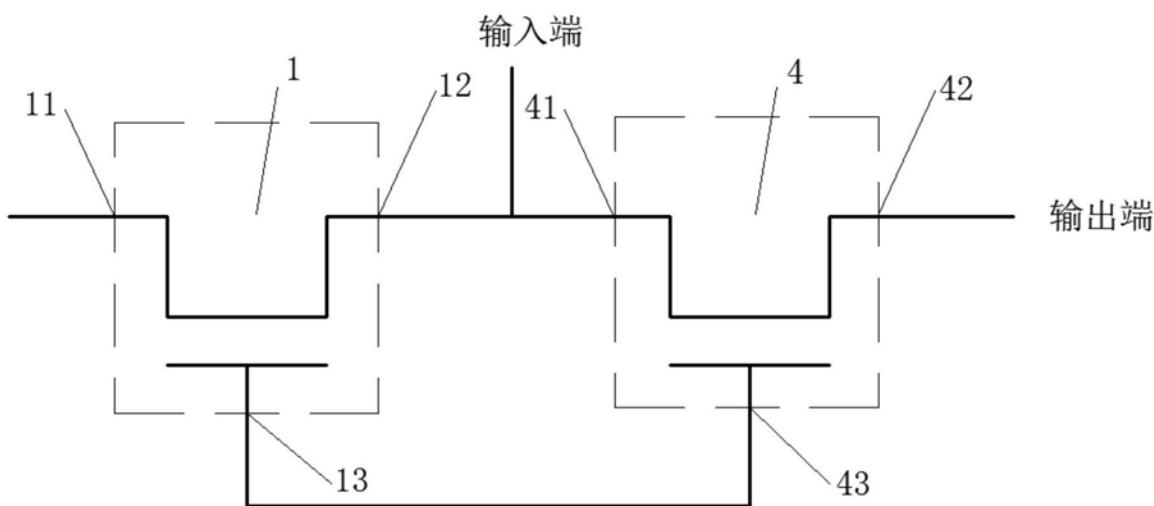

[0021] 图5为本发明提供的防静电单元第三个实施例的结构示意图二;

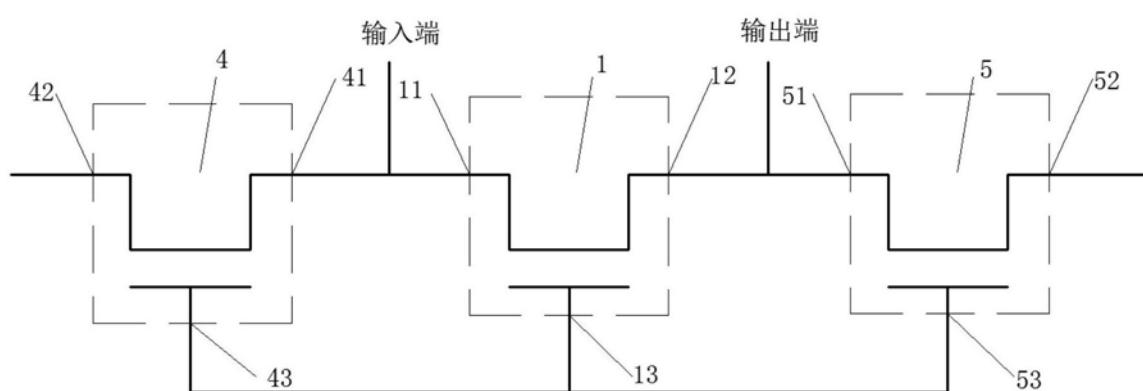

[0022] 图6为本发明提供的防静电单元第三个实施例的结构示意图三。

## 具体实施方式

[0023] 为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

[0024] 需要说明的是,本发明实施例中所有使用“第一”和“第二”的表述均是为了区分两个相同名称非相同的实体或者非相同的参量,可见“第一”“第二”仅为了表述的方便,不应理解为对本发明实施例的限定,后续实施例对此不再一一说明。

[0025] 实施例一,

[0026] 针对于当前技术中薄膜晶体管容易由于静电作用而产生损坏的问题,尤其是对于如图1所示的应用于GOA驱动电路中的薄膜晶体管来说,基于结构位置等考虑,薄膜晶体管

的尺寸通常设计的比较小,一般是<100nm,图1中的薄膜晶体管M13的一侧与Input信号连接,另一侧连接到PU(上拉节点),栅极连在CLKB(时钟信号)上,由此,如果input输入端出现大静电导致该薄膜晶体管M13出现损坏,将会使得整个驱动电路无法工作,因此需要解决这一类抗静电能力弱的薄膜晶体管的抗静电问题。

[0027] 需要说明的是,虽然本申请以图1中的薄膜晶体管M13引出相应的问题,但是实际上本申请所提出的防静电单元适用于任何具有防静电需求的薄膜晶体管,也即本申请并不限制薄膜晶体管的应用环境和位置关系。

[0028] 基于以上分析,在本申请一个可选的实施例中,为了对目标薄膜晶体管进行防静电设计,需要针对静电的特点进行相应的设计,申请人经过研究认为,一方面可以基于静电的直接破坏性,在静电发送端与薄膜晶体管之间设置一个防静电单元,使得出现静电时将首先作用于防静电单元而不会对目标薄膜晶体管造成损坏,而防静电单元在正常工作时能够起到良好的导通作用,不影响目标薄膜晶体管正常工作。另一方面,还可以通过在目标薄膜晶体管的栅极位置与源漏极中的至少一个之间设置一个防静电单元使得通过栅极的传递,所述防静电单元能够为目标薄膜晶体管分散静电带来的电场强度,进而增强目标薄膜晶体管的抗静电能力,同时,所述防静电单元不影响目标薄膜晶体管正常工作。由此得到本申请的一个设计方案为,提出一种用于薄膜晶体管的防静电单元,所述薄膜晶体管的第一极与输入端之间或者所述薄膜晶体管的栅极与第一极或第二极之间设置有防静电单元,用于保护所述薄膜晶体管不受到静电破坏;其中,所述薄膜晶体管的第一极为源极或漏极,所述薄膜晶体管的第二极为对应的漏极或源极;所述输入端为静电发生端。

[0029] 由上述实施例可知,本申请提出的用于薄膜晶体管的防静电单元通过在薄膜晶体管于静电发生端之间设置防静电单元,使静电首先通过防静电单元而不会直接对薄膜晶体管造成损害,同时又不影响薄膜晶体管的正常工作时的信号传输,或者在所述薄膜晶体管的栅极与源漏极中的一个连接防静电单元,使得通过栅极连接所述防静电单元能够给薄膜晶体管起到分散电厂强度的作用,进而提高抗静电能力,也即能够避免静电损害。因此,本申请所述防静电单元能够消除静电对相应薄膜晶体管带来的损坏,进而保证显示质量、提高产品良率。

[0030] 需要说明的是,上述两种设计既可以单独使用,也可以同时使用,同时使用能够进一步提高防静电的效果。

[0031] 实施例二,

[0032] 参照图2所示,为本发明提供的防静电单元第二个实施例的结构示意图一。由图可知,目标薄膜晶体管,即所述薄膜晶体管1在正常情况下,所述薄膜晶体管1的第一极11对应连接到输入端,所述薄膜晶体管1的第二极12对应连接到输出端,所述薄膜晶体管1的栅极13对应连接到相应的控制端,例如,参考图1可知,所述薄膜晶体管的第一极11连接到input输入信号,所述薄膜晶体管的第二极12连接到上拉节点,所述薄膜晶体管的栅极13连接到CLKB时钟信号。基于input输入信号容易出现静电,所以需要对所述薄膜晶体管1进行改善。本申请通过在所述薄膜晶体管1的第一极与输入端之间增加防静电单元来实现防静电作用。具体的,所述防静电单元包括第一薄膜晶体管2;所述第一薄膜晶体管2的栅极23与所述第一薄膜晶体管2的第一极11连接;所述第一薄膜晶体管2的第一极21连接到输入端,所述第一薄膜晶体管的第二极22连接到所述薄膜晶体管的第一极11;其中,所述第一薄膜晶体

管的第一极21为源极或漏极,所述第一薄膜晶体管的第二极22为对应的漏极或源极。这样,正常工作时,所述第一薄膜晶体管2作为一个二极管能够将输入端对应的信号输入到目标薄膜晶体管中,而当输入端出现大静电时,将会首先烧穿所述第一薄膜晶体管2,进而保护目标薄膜晶体管1不受损害,同时烧穿的所述第一薄膜晶体管2将会作为导线,进行正常的信号传递。

[0033] 参照图3所示,为本发明提供的防静电单元第二个实施例的结构示意图二。由图可知,所述防静电单元还包括第二薄膜晶体管3;所述第二薄膜晶体管3的栅极33与所述第二薄膜晶体管3的第一极31连接;所述第二薄膜晶体管的第一极31与所述薄膜晶体管的第二极12连接;所述第二薄膜晶体管的第二极32连接到输出端;所述第二薄膜晶体管的第一极31为源极或漏极,所述第二薄膜晶体管的第二极32为对应的漏极或源极。这样,通过在目标薄膜晶体管的两端均增加具有防静电作用的薄膜晶体管,使得目标薄膜晶体管的输出端出现静电时,也能够起到防静电作用,更加全面的保护目标薄膜晶体管。

[0034] 在本申请一些可选的实施例中,所述防静电单元设置有多个串联设置的第二薄膜晶体管,和/或,所述防静电单元设置有多个串联设置的第一薄膜晶体管。基于上述实施例中的第一薄膜晶体管或第二薄膜晶体管形成的防静电单元只能起到一次防静电作用,所以本申请提出还可以设置串联的多个第一薄膜晶体管或第二薄膜晶体管,实现多次防静电效果。

[0035] 实施例三,

[0036] 参照图4所示,为本发明提供的防静电单元第三个实施例的结构示意图一;图5为本发明提供的防静电单元第三个实施例的结构示意图二。由图可知,所述防静电单元包括第三薄膜晶体管4;所述第三薄膜晶体管的栅极43与所述薄膜晶体管的栅极13连接;所述第三薄膜晶体管的第一极41与所述薄膜晶体管的第一极11或第二极12连接;所述第三薄膜晶体管的第二极42为浮接状态;所述第三薄膜晶体管的第一极41为源极或漏极,所述第三薄膜晶体管的第二极42为对应的漏极或源极。这样,无论是目标薄膜晶体管的输入端还是输出端出现静电,通过所述薄膜晶体管的栅极13连接防静电单元均能够起到分散电场强度,提高抗静电能力的作用。

[0037] 参照图6所示,为本发明提供的防静电单元第三个实施例的结构示意图三。所述防静电单元还包括第四薄膜晶体管5;所述第四薄膜晶体管的栅极53与所述薄膜晶体管的栅极13连接;所述第四薄膜晶体管的第一极51与所述薄膜晶体管对应的第二极12或第一极11连接;所述第四薄膜晶体管的第二极52为浮接状态;所述第四薄膜晶体管的第一极51为源极或漏极,所述第四薄膜晶体管的第二极52为对应的漏极或源极。这样,通过在目标薄膜晶体管的两端均设置具有防静电作用的薄膜晶体管,能够进一步提高防静电的效果。

[0038] 在本申请一些可选的实施例中,所述防静电单元设置有多个并联设置的第三薄膜晶体管;和/或,所述防静电单元设置有多个并联设置的第四薄膜晶体管。这样,通过设置多个并联的第三薄膜晶体管或第四薄膜晶体管,能够使得给静电带来的电场更加分散,也即进一步提高防静电效果。

[0039] 实施例四,

[0040] 在本申请一些可选的实施例中,还提供了一种驱动电路,所述驱动电路包括至少一个上述任一项实施例所述的用于薄膜晶体管的防静电单元。

[0041] 在本申请一些可选的实施例中,还提供了一种显示装置,所述显示装置包括所述驱动电路。

[0042] 基于上述驱动电路或显示装置中同样包含有防静电单元,因此具有同样的防静电效果,本实施例不再重复赘述。

[0043] 所属领域的普通技术人员应当理解:以上任何实施例的讨论仅为示例性的,并非旨在暗示本公开的范围(包括权利要求)被限于这些例子;在本发明的思路下,以上实施例或者不同实施例中的技术特征之间也可以进行组合,步骤可以以任意顺序实现,并存在如上所述的本发明的不同方面的许多其它变化,为了简明它们没有在细节中提供。

[0044] 另外,为简化说明和讨论,并且为了不会使本发明难以理解,在所提供的附图中可以示出或可以不示出与集成电路(IC)芯片和其它部件的公知的电源/接地连接。此外,可以以框图的形式示出装置,以便避免使本发明难以理解,并且这也考虑了以下事实,即关于这些框图装置的实施方式的细节是高度取决于将要实施本发明的平台的(即,这些细节应当完全处于本领域技术人员的理解范围内)。在阐述了具体细节(例如,电路)以描述本发明的示例性实施例的情况下,对本领域技术人员来说显而易见的是,可以在没有这些具体细节的情况下或者这些具体细节有变化的情况下实施本发明。因此,这些描述应被认为是说明性的而不是限制性的。

[0045] 尽管已经结合了本发明的具体实施例对本发明进行了描述,但是根据前面的描述,这些实施例的很多替换、修改和变型对本领域普通技术人员来说将是显而易见的。例如,其它存储器架构(例如,动态RAM(DRAM))可以使用所讨论的实施例。

[0046] 本发明的实施例旨在涵盖落入所附权利要求的宽泛范围之内的所有这样的替换、修改和变型。因此,凡在本发明的精神和原则之内,所做的任何省略、修改、等同替换、改进等,均应包含在本发明的保护范围之内。

图1

图2

图3

图4

图5

图6

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种用于薄膜晶体管的防静电单元、驱动电路及显示装置                      |         |            |

| 公开(公告)号        | <a href="#">CN108335681A</a>                   | 公开(公告)日 | 2018-07-27 |

| 申请号            | CN201810148674.4                               | 申请日     | 2018-02-13 |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司<br>合肥鑫晟光电科技有限公司                  |         |            |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司<br>合肥鑫晟光电科技有限公司                  |         |            |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司<br>合肥鑫晟光电科技有限公司                  |         |            |

| [标]发明人         | 杨海鹏<br>王登峰<br>戴珂<br>周茂秀                        |         |            |

| 发明人            | 杨海鹏<br>王登峰<br>戴珂<br>周茂秀                        |         |            |

| IPC分类号         | G09G3/36 H01L27/02                             |         |            |

| CPC分类号         | G09G3/36 H01L27/0266                           |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明公开了一种用于薄膜晶体管的防静电单元、驱动电路及显示装置，属于液晶显示相关技术领域。其中，所述用于薄膜晶体管的防静电单元中，所述薄膜晶体管的第一极与输入端之间或者所述薄膜晶体管的栅极与第一极或第二极之间设置有防静电单元，用于保护所述薄膜晶体管不受到静电破坏；其中，所述薄膜晶体管的第一极为源极或漏极，所述薄膜晶体管的第二极为对应的漏极或源极；所述输入端为静电发生端。本申请所述防静电单元能够消除静电对相应薄膜晶体管带来的损坏，进而保证显示质量、提高产品良率。