(12)发明专利申请

(10)申请公布号 CN 111243549 A

(43)申请公布日 2020.06.05

(21)申请号 202010219774.9

(22)申请日 2020.03.25

(71)申请人 新相微电子(上海)有限公司

地址 200233 上海市徐汇区漕河泾新兴技术开发区桂平路680号创业中心大厦5楼517室

(72)发明人 肖宏 覃正才 周剑 林昆宗

(51)Int.Cl.

G09G 3/36(2006.01)

权利要求书2页 说明书12页 附图5页

(54)发明名称

一种用于薄膜晶体管液晶显示的控制方法、装置及系统

(57)摘要

本发明提供用于薄膜晶体管液晶显示信号的控制方法，包括步骤：在一个行周期的第一阶段P1内，设置公共电极为高电压，并相应地设置负电压列对应的源极电压低于所述高电压以使得所述负电压列的输出信号相对为负；在所述行周期的第二阶段P2内，设置所述公共电极为正常电压，并相应地设置正电压列对应的源极电压高于所述正常电压以使得所述正电压列的输出信号相对为正。而负列电压的输出为浮接，藉由公共电极高转低的作用产生出负电压。第三阶段P3内，些微充电以达到预期目标电压。本发明还提供对应驱动装置及控制芯片。通过本发明，使得电荷泵、片上电容在至少减少一半的情况下实现现有技术效果一致的点反转模式，减少了显示控制芯片的耗电量。

1. 一种用于薄膜晶体管液晶显示信号的控制方法, 其用于在点反转模式下提供低功率电路, 其特征在于, 包括如下步骤:

a. 在一个行周期的第一阶段P1内, 设置公共电极为高电压, 并相应地设置负电压列对应的源极输出电压低于公共电极的电压, 正电压列对应的源极输出为高于或等于公共电极的电压;

b. 在所述行周期的第二阶段P2内, 设置所述公共电极为正常电压, 并相应地设置正电压列对应的源极电压高于所述公共电极的电压;

c. 在所述行周期的第三阶段P3内, 设置负电压列对应的源极电压低于所述公共电极正常电压, 以使得所述负电压列的输出信号相对为负, 设置正电压列对应的源极电压高于所述公共电极正常电压, 以使得所述正电压列的输出信号相对为正。

2. 根据权利要求1所述的控制方法, 其特征在于, 在所述步骤c中, 当所述正电压列和负电压列的输出信号达到预计值之时或之后, 将所述栅极电极关闭, 采样所述源极电极上的电压并将其作为所述薄膜晶体管液晶显示设备的液晶单元的输入信号。

3. 根据权利要求1或2所述的控制方法, 其特征在于, 在所述步骤a中在所述公共电极由正常电压被设置到所述高电压之间, 所有负电压列的输出保持接地, 正电压列输出保持浮动或者与所述公共电极的高电压相同。

4. 根据权利要求1至3中任一项所述的控制方法, 其特征在于, 在所述步骤b中在所述公共电极由高电压被设置到正常电压之间, 所有负电压列的输出源极电极保持浮动, 正电压列输出高于所述公共电极的正常电压。

5. 根据权利要求1至4中任一项所述的控制方法, 其特征在于, 所述P1、P2、P3的时间长短关系为如下方式的任一种:

-P1=P2=P3, 每个阶段为一个行周期的三分之一;

-P1=P2<P3; 或者

-P1<P2<P3; 或者

-P2<P1<P3。

6. 根据权利要求1至5中任一项所述的控制方法, 其特征在于, 所述P1、P2、P3的先后顺序为如下方式的任一种:

-P1=>P2=>P3;

-P2=>P1=>P3; 或者

-P1=>P3。

7. 根据权利要求1至6中任一项所述的控制方法, 其特征在于, 所述P1的时间周期被设置为使得所述负电压列的电压相对所述公共电极达到第一预期值; 相应地, 所述P2的时间周期被设置为使得所述正电压列的电压相对所述公共电极达到第二预期值。

8. 根据权利要求1至7中任一项所述的控制方法, 其特征在于, 在所述步骤c中, 对所述源极输出充电以使得所述源极输出的电压相对所述公共电极达到最终预定值。

9. 一种低功率点反转薄膜晶体管液晶显示设备的驱动装置, 其用于在点反转模式下提供低功率电路, 包括N列源极输出, 所述每一列源极输出连接至M个液晶单元的源极, 其特征在于, 还包括N/2个正向驱动缓冲器, 所述每个正向驱动缓冲器通过第一选择电路用于向两列所述源极输出电压, 其中, 所述驱动装置根据权利要求1至8中任一项所述的控制方法设

置电压。

10. 根据权利要求9所述的驱动装置,其特征在于,所述正向驱动缓冲器连接一数字模拟转换器,且所述数字模拟转换器的输入端通过所述第二选择电路分别连接两列数字信号输出端。

11. 根据权利要求10所述的驱动装置,其特征在于,所述正向驱动缓冲器与所述数字模拟转换器的连接方式为:针对每一个数字模拟转换器,均设置一个正向驱动缓冲器的输入端与所述数字模拟转换器的输出端相连接。

12. 根据权利要求9至11中任一项所述的驱动装置,其特征在于,还包括N/2个负向驱动缓冲器,所述负向驱动缓冲器通过第三选择电路用于向两列所述源极输出电压。

13. 根据权利要求12所述的驱动装置,其特征在于,所述负向驱动缓冲器连接一数字模拟转换器,且所述数字模拟转换器的输入端通过所述第四选择电路至少连接两列数字信号输出端。

14. 根据权利要求13所述的驱动装置,其特征在于,所述负向驱动缓冲器与所述数字模拟转换器的连接方式为:针对每一个数字模拟转换器,均设置一个负向驱动缓冲器的输入端与所述数字模拟转换器的输出端相连接。

15. 一种低功率点反转薄膜晶体管液晶显示设备的显示控制芯片,包括:栅极驱动装置、公共电极驱动装置、高电压产生装置、时序控制装置,所述栅极驱动装置、所述公共电极驱动装置分别向所述薄膜晶体管液晶显示设备的液晶单元提供栅极电压、公共电压,所述时序控制装置提供时序控制信号,所述高电压产生装置提供所需电源电压,其特征在于,还包括根据权利要求9至14中任一项所述的驱动装置,所述驱动装置用于向所述薄膜晶体管液晶显示设备的液晶单元提供源极电压。

## 一种用于薄膜晶体管液晶显示的控制方法、装置及系统

### 技术领域

[0001] 本发明涉及薄膜晶体管液晶显示设备,特别是采用点反转模式的薄膜晶体管液晶显示设备,尤其是具有低功率的点反转薄膜晶体管液晶显示设备,以及用于该等低功率点反转薄膜晶体管液晶显示设备中的显示控制芯片,以及对应的驱动装置,以及用于控制该等低功率点反转薄膜晶体管液晶显示设备稳定显示的显示控制方法。

### 背景技术

[0002] 薄膜晶体管液晶显示设备经过不断地技术提升,以其工作电压低、功耗小、外型轻薄和分辨率高等优点,广泛应用于电视机、个人计算机,手机用显示等显示设备。

[0003] 从原理上来看,液晶显示设备通常是在一对玻璃基板之间配置有液晶层从而构成液晶显示面板,这样的基板一般来说其中一块是透明玻璃。基板上根据特定工艺形成显示像素,也可以成为显示单元,在工作过程中,通过有选择性地对这些显示像素对应的不同电极施加电压,从而可以控制像素的亮度,就形成了液晶显示设备的显示信号。同时,为了防止导致像素对应的液晶元素产生极化,寿命缩短等不利现象,所以,不能一直对像素液晶上施加同极性的电压,通常会对上述像素进行电压交流化处理,即对像素的公共电极提供的公共电压(VCOM)为基准,使施加于像素的源极电极的电压,周期性地向正电压侧/负电压侧变化,从而实现恒定时间使施加于液晶层的电压交流化,既保证显示信号的稳定,又保证液晶层不会发生极化。上述对于电压交流化的描述,可以参考日本特开2009-15334号公报来实现。

[0004] 对于显示信号的控制驱动方法,可以有多种,比如行反转模式和点反转模式(Dot-inversion)。其中,行反转模式是控制一行的像素的电压为正,而该一行的上一行、下一行的像素的电压为负,该一行像素的隔一行的像素的电压又为正,以此循环。在这样的过程中,例如,通过公共电极提供一个公共电压(VCOM),使施加于像素源极电极的电压(即灰度电压)反转成比公共电压(VCOM)高电位的电压,或反转成比公共电压(VCOM)低电位的电压,从而实现针对上述像素(液晶单元)的电压极性为正或者为负。这样的显示驱动方法相对容易实现,但是显示效果略差,例如比较容易产生闪烁和横向显示瑕疵。而点反转模式则是控制一个像素的电压为正,而该像素的上下左右相邻的四个像素在该时间周期内电压为负,与所述上下左右相邻的四个像素相邻的像素在该时间周期内电压又为正,且所有像素的电压在下一个时间周期反转,从而实现每个像素的电压在恒定时间进行反转。点反转模式的显示效果是目前的公知方法中相对最好的,其显示效果均匀,闪烁最低,所以也是最为常用的做法。

[0005] 例如,专利申请号为201210392386.6、发明名称为液晶显示设备的专利申请中描述了点反转模式的显示原理。其中描述,在点反转模式中,若着眼于相邻的像素,例如G0线的DR0(+)和DG0(-),则像素的极性以正(+)和负(-),在其以后的像素中也成为相邻的像素的极性相反的方式进行驱动。在这里,所谓正(+),是指在对像素写入灰度电压时,对像素电极施加比公共电极高电位的灰度电压,所谓负(-),是指在对像素写入灰度电压时,对像素

电极施加比公共电极低电位的灰度电压。在下一帧中,像素的极性与前一帧的极性相反。即,在前一帧中极性为(+)的像素在下一帧中极性为(-),在前一帧中极性为(-)的像素在下一帧中极性为(+)。

[0006] 上述内容描述了点反转模式的显示原理,而从电路层面来说,为了实现上述像素电压的反转,或者说为了实现针对上述公共电极的公共电压(VCOM)的相对较高或者相对较低的电压,需要特定的电路结构来实现。在这样的电路结构中,一个液晶单元(也称为像素单元)即要具备可以被提供与公共电压(VCOM)的相对较高的电压,从而使得其极性为正,也需要具备被提供与公共电压(VCOM)的相对较低的电压,从而使得其极性为负。通常来说,为了控制上述液晶显示设备上的每个像素单元可以显示一个信号,我们会通过一个显示芯片来控制每个像素单元,通过该显示芯片,数字信号被输入,同时模拟信号被输出给每个像素单元,从而使得液晶显示设备显示我们希望其显示的信号。而为了上述模拟信号可以被稳定地显示在像素单元上,需要驱动缓冲器为像素单元提供稳定的电压。又由于在传统的点反转模式中每个像素单元既需要正电压、需要负电压,所以这样的驱动缓冲器需要正向驱动缓冲器(P Buffer),需要负向驱动缓冲器(N Buffer)。在显示驱动芯片中,驱动缓冲器要负责推动液晶面板,一般是最耗电的电路。

[0007] 图3以及图4描述了在现有技术中上述正向驱动缓冲器以及负向驱动缓冲器的工作原理。其中,在一个行周期内,一个列输出,例如图中所示A1(Source),其针对像素单元输出正电压信号(VSP),并且在这个行周期结束后(也可以理解为这个行周期结束的那个时刻),该列输出针对像素单元输出负电压信号(VSN)。在这样的过程中,当输出上述正电压信号(VSP)时,所述公共电极输出的公共电压被输出为VCOM电压的直流信号,通常是一个接近为零电压(GND)的电压,而与一个像素单元对应的控制单元的栅极电压则在正高电压(VGH)时打开并且在负高电压(VGL)时关闭,从而使得控制单元向像素单元输出上述正电压信号(VSP)。相应地,在输出上述负电压信号(VSN)时,所述公共电极输出的公共电压仍被输出为VCOM电压的直流信号,与一个像素单元对应的控制单元的栅极电压则在正高电压(VGH)时打开并且在负高电压(VGL)时关闭,从而使得控制单元向像素单元输出上述负电压信号(VSN)。

[0008] 对应于上述过程,一个控制单元需要同时具有输出正电压信号以及输出负电压信号的结构,并且基于控制信号,其在一个行周期内输出正电压信号,并且在下一个行周期内输出负电压信号。为了实现这一点,在现有技术中采用上述的正向驱动缓冲器(P-Buffer)以及上述的负向驱动缓冲器(N-Buffer)来实现,例如图3示出了现有技术中典型的若干个控制单元的电路结构示意图,其中一个控制单元控制两列输出。而且在现有技术中,针对一个控制单元就需要一个正向驱动缓冲器(P-Buffer)以及一个负向驱动缓冲器(N-Buffer),两者构成一正、一负两个相反的电压组件。

[0009] 本领域技术人员理解,无论是正向驱动缓冲器(P-Buffer)还是负向驱动缓冲器(N-Buffer)都需要通过电荷泵(Charge Pump)来提供高电源电压来实现。通过该电荷泵(Charge Pump),可以将输入电源电压转换为正高电压以及负高电压,例如在公共电极输入正常公共电压(VCOM)的情况下,在向一个控制单元提供,例如,3V电源电压时,通过该电荷泵(Charge Pump)可以将该3V电压转换为正5~6V,也就是我们说的AVDD,从而实现所述控制单元对外输出正高电压;相反,则将该3V电压转换-5~-6V,也就是我们说的AVEE,从而实

现所述控制单元对外输出负高电压。但本领域技术人员也知悉,这样的电荷泵结构需要大量的片内电容(on-chip capacitors),就会导致芯片面积非常大,从而成本高、耗电量也大。

[0010] 为了尽量地减少芯片面积、降低耗电量,申请人曾经通过中国专利申请“低功率薄膜晶体管液晶显示控制芯片、驱动装置及控制方法”、中国专利申请号:201710997686.X提出了在一个行周期内分为两个阶段对电压进行控制的方法,从而获得更小电流、更小芯片面积的薄膜晶体管液晶显示器。

[0011] 在上述现有技术的基础上,申请人希望提出能够获得更小芯片面积的技术方案。

## 发明内容

[0012] 针对现有技术的现状,本发明的目的是在缩减上述电荷泵结构需要大量的片内电容(on-chip capacitors)的基础上,提供实现点反转模式的驱动控制方法。基于该目的,基于本发明的一个方面,本发明提供一种用于薄膜晶体管液晶显示信号的控制方法,其用于在点反转模式下提供低功率电路,其特征在于,包括如下步骤:

[0013] a. 在一个行周期的第一阶段P1内,设置公共电极为高电压,并相应地设置负电压列对应的源极输出电压低于公共电极的电压,正电压列对应的源极输出为高于或等于公共电极的电压;

[0014] b. 在所述行周期的第二阶段P2内,设置所述公共电极为正常电压,并相应地设置正电压列对应的源极电压高于所述公共电极的电压;

[0015] c. 在所述行周期的第三阶段P3内,设置负电压列对应的源极电压低于所述公共电极正常电压,以使得所述负电压列的输出信号相对为负,设置正电压列对应的源极电压高于所述公共电极正常电压,以使得所述正电压列的输出信号相对为正。

[0016] 优选地,在所述步骤c中,当所述正电压列和负电压列的输出信号达到预计值之时或之后,将所述栅极电极关闭,采样所述源极电极上的电压并将其作为所述薄膜晶体管液晶显示设备的液晶单元的输入信号。

[0017] 优选地,在所述步骤a中在所述公共电极由正常电压被设置到所述高电压之间,所有负电压列的输出保持接地,正电压列输出保持浮动或者与所述公共电极的高电压相同。

[0018] 优选地,在所述步骤b中在所述公共电极由高电压被设置到正常电压之间,所有负电压列的输出源极电极保持浮动,正电压列输出高于所述公共电极的正常电压。

[0019] 优选地,所述P1、P2、P3的时间长短关系为如下方式的任一种:

[0020] -P1=P2=P3,每个阶段为一个行周期的三分之一;

[0021] -P1=P2<P3;或者

[0022] -P1<P2<P3;或者

[0023] -P2<P1<P3。

[0024] 优选地所述P1、P2、P3的先后顺序为如下方式的任一种:

[0025] -P1=>P2=>P3;

[0026] -P2=>P1=>P3;或者

[0027] -P1=>P3。

[0028] 优选地,所述P1的时间周期被设置为使得所述负电压列的电压相对所述公共电极

达到第一预期值；相应地，所述P2的时间周期被设置为使得所述正电压列的电压相对所述公共电极达到第二预期值。

[0029] 优选地，在所述步骤c中，对所述源极输出充电以使得所述源极输出的电压相对所述公共电极达到最终预定值。

[0030] 根据本方面的另一个方面，还提供一种低功率点反转薄膜晶体管液晶显示设备的驱动装置，其用于在点反转模式下提供低功率电路，包括N列源极输出，所述每一列源极输出连接至M个液晶单元的源极，其特征在于，还包括N/2个正向驱动缓冲器，所述每个正向驱动缓冲器通过第一选择电路用于向两列所述源极输出电压，其中，所述驱动装置根据上述的控制方法设置电压。

[0031] 优选地，所述正向驱动缓冲器连接一数字模拟转换器，且所述数字模拟转换器的输入端通过所述第二选择电路分别连接两列数字信号输出端。

[0032] 优选地，所述正向驱动缓冲器与所述数字模拟转换器的连接方式为：针对每一个数字模拟转换器，均设置一个正向驱动缓冲器的输入端与所述数字模拟转换器的输出端相连接。

[0033] 优选地，所述驱动装置还包括N/2个负向驱动缓冲器，所述负向驱动缓冲器通过第三选择电路用于向两列所述源极输出电压。

[0034] 优选地，所述负向驱动缓冲器连接一数字模拟转换器，且所述数字模拟转换器的输入端通过所述第四选择电路至少连接两列数字信号输出端。

[0035] 优选地，所述负向驱动缓冲器与所述数字模拟转换器的连接方式为：针对每一个数字模拟转换器，均设置一个负向驱动缓冲器的输入端与所述数字模拟转换器的输出端相连接。

[0036] 根据本方面的又一个方面，还提供一种低功率点反转薄膜晶体管液晶显示设备的显示控制芯片，包括：栅极驱动装置、公共电极驱动装置、高电压产生装置、时序控制装置，所述栅极驱动装置、所述公共电极驱动装置分别向所述薄膜晶体管液晶显示设备的液晶单元提供栅极电压、公共电压，所述时序控制装置提供时序控制信号，所述高电压产生装置提供所需电源电压，其特征在于，还包括根据权利要求9至14中任一项所述的驱动装置，所述驱动装置用于向所述薄膜晶体管液晶显示设备的液晶单元提供源极电压。

[0037] 通过本发明提供的驱动控制方法，使得在电荷泵结构的片内电容(on-chip capacitors)在现有技术基础上使用更为少的情况下实现现有技术效果一致的点反转模式，从而大大节省了针对薄膜晶体管液晶显示装置的显示控制芯片的面积，也减少了这样的显示控制芯片的耗电量，从而大大减少了显示控制芯片的成本。具体地，在一个行周期内通过三个阶段的电压等控制，从而使得整个芯片需要的充电电流的值更小，从而减小了电荷泵稳压所需的电容。相应地，本发明提供的显示驱动单元，结构简单，易于实现，可以实现包含上述显示驱动单元的显示控制芯片的成本控制，对于芯片产业的进一步深入、细化具有重要意义。

## 附图说明

[0038] 通过阅读参照以下附图对非限制性实施例所作的详细描述，本发明的其他特征、目的和优点将会变得更明显：

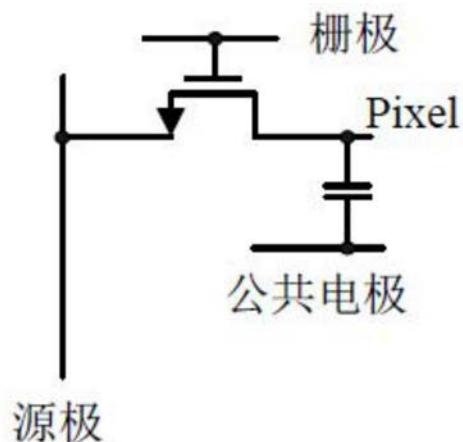

[0039] 图1示出了根据现有技术的一个用于薄膜晶体管的液晶显示设备的液晶单元的电路结构图；

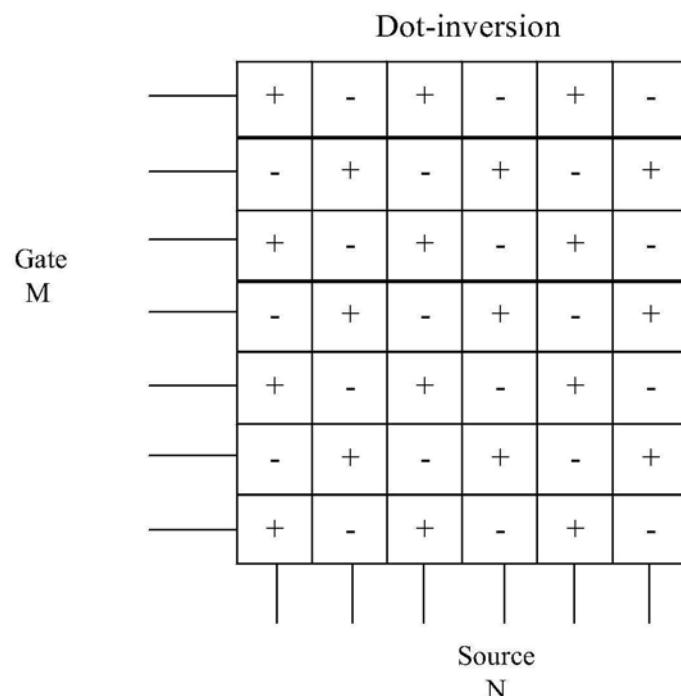

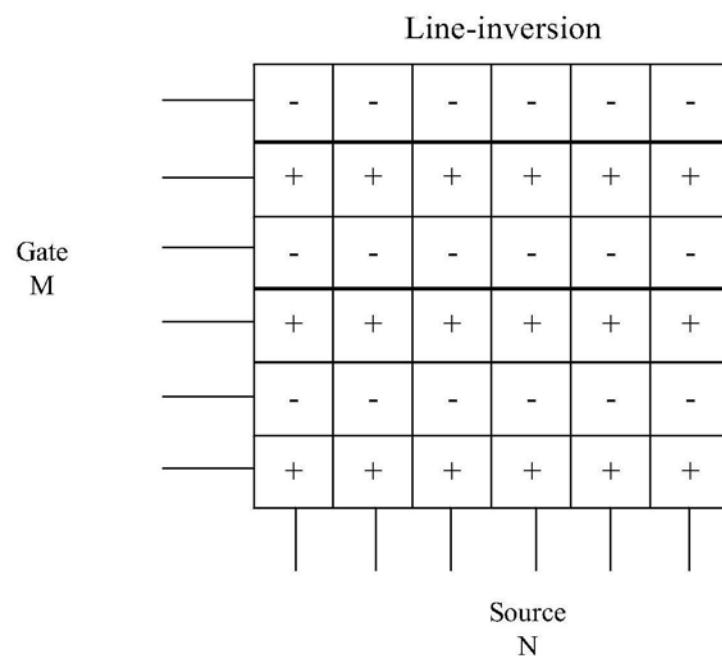

[0040] 图2-1示出了根据现有技术的一个用于薄膜晶体管的液晶显示设备的点反转模式的示意图；

[0041] 图2-2示出了根据现有技术的一个用于薄膜晶体管的液晶显示设备的行反转模式的示意图；

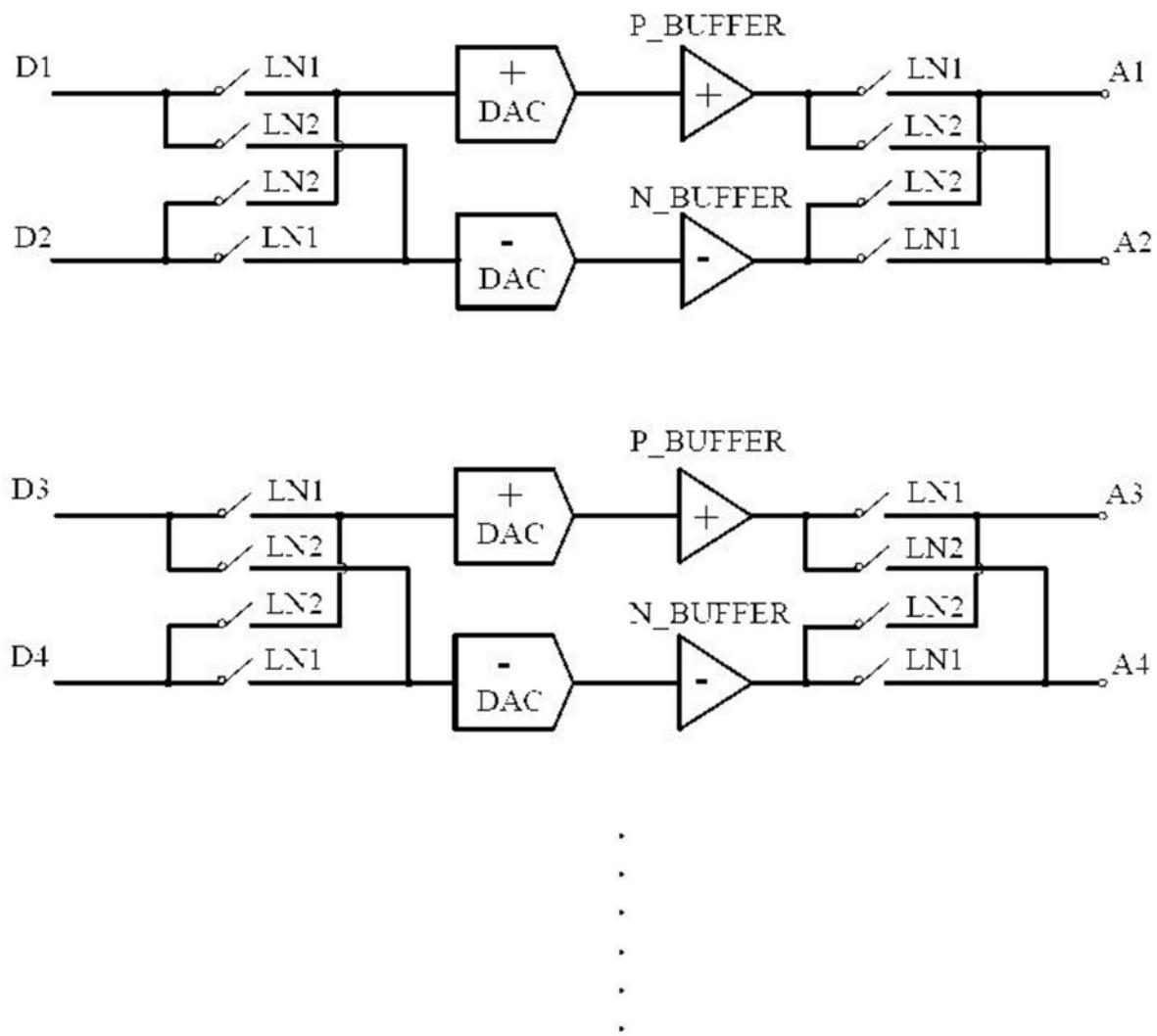

[0042] 图3示出了根据现有技术的一个用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置的电路结构图；

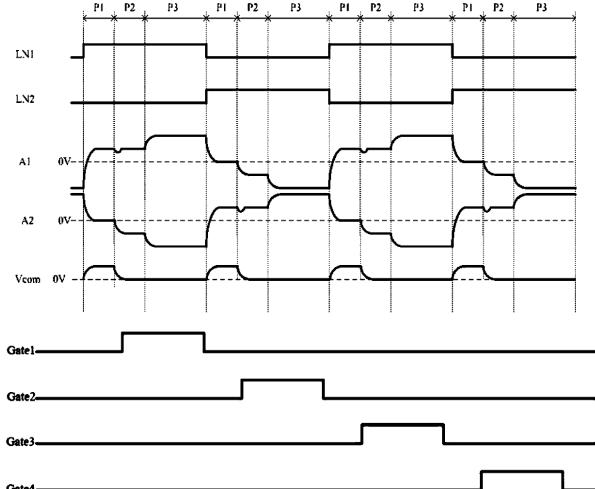

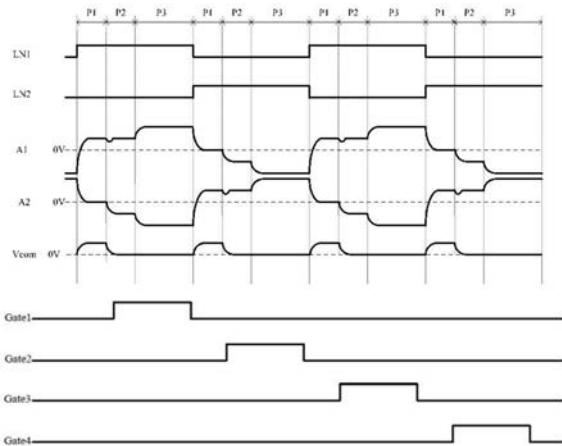

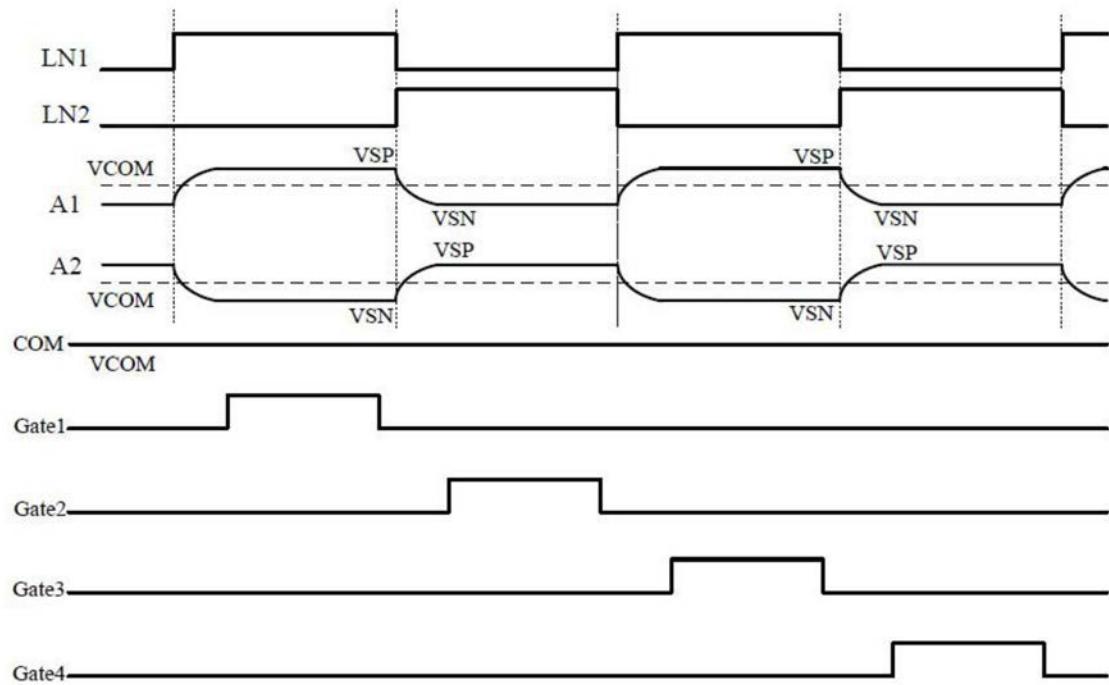

[0043] 图4示出了根据现有技术的一个用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置输出电压的时序图；

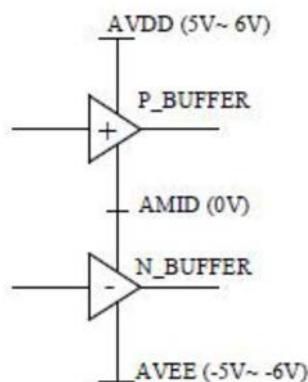

[0044] 图5示出了根据现有技术的一个用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置中的P-Buffer与N-Buffer的电路结构示意图；

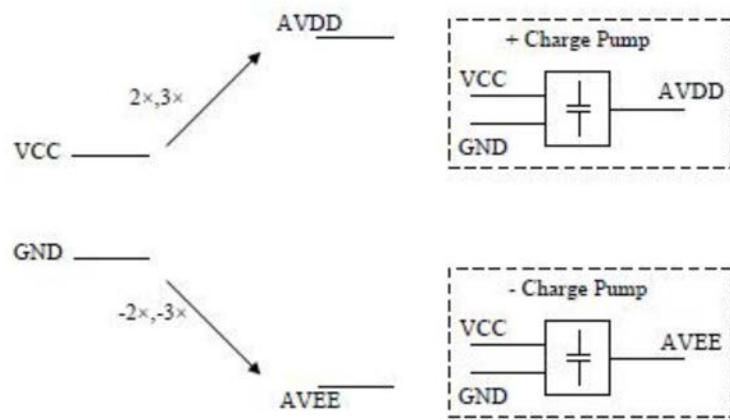

[0045] 图6示出了根据现有技术的一个用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置中的电荷泵(Charge Pump)结构，和需要的片内电容(on-chip capacitors)结构原理示意图；以及

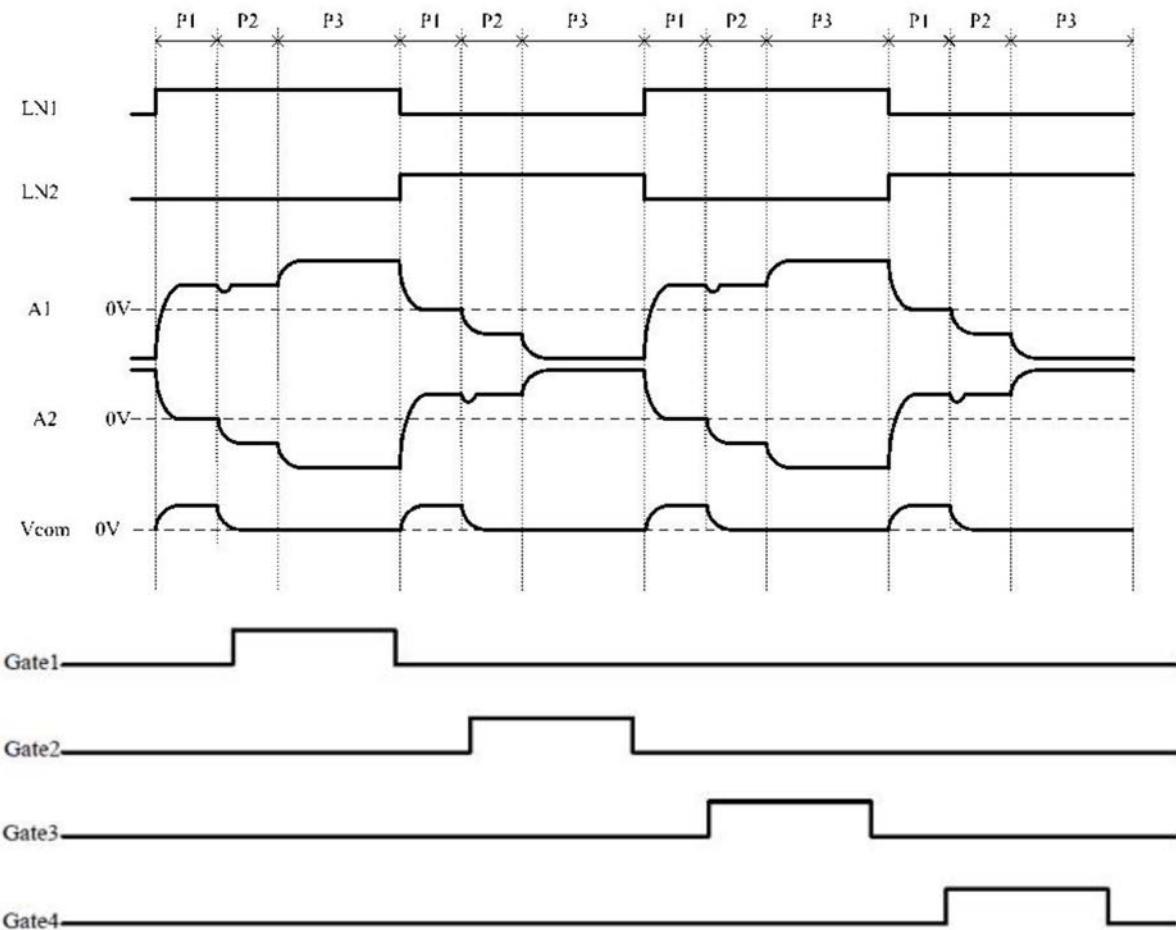

[0046] 图7示出了根据本发明实施例的用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置输出电压的时序图。

## 具体实施方式

[0047] 为了更好的使本发明的技术方案清晰的表示出来，下面结合附图对本发明作进一步说明，其中，图1示出了根据现有技术的一个用于薄膜晶体管的液晶显示设备的液晶单元的电路结构图。基于对现有技术的理解，我们更加容易理解本发明的发明点。

[0048] 具体地，在图1所示现有技术的电路结构图中，其通过示意图的方式示出了液晶显示设备的显示面板上的一个液晶单元Pixel1，其主体包括位于图1右下侧的电容C，该电容C一端连接公共电极，该公共电极向该电容C提供公共电压，所述电容C的另一端连接一个TFT单元，所述TFT单元的两个端子分别连接源极电极以及栅极电极。进一步地，本领域技术人员理解，在现有技术中，用于与上所述显示面板配合的显示控制芯片的配合，所述显示控制芯片向每个液晶单元Pixel1分别提供来自源极电极的源极电压以及栅极电极的栅极电压、来自公共电极的公共电压。进一步地，本领域技术人员理解，如背景技术所描述的，通过向公共电极提供公共电压VCOM，以及向所述源极电压提供不高于5~6V的输出正电压，或者向所述源极电压提供不低于-5~-6V的输出负电压，从而实现液晶单元Pixel1的极性转换。这个过程分别由P-Buffer以及N-Buffer完成，针对下图的描述对此原理还有所涉及。

[0049] 图2-1示出了根据现有技术的一个用于薄膜晶体管的液晶显示设备的点反转模式的示意图。在图2-1中，假设一个液晶显示设备有M\*N个液晶单元，则每一个液晶单元分别连接源极电极以及栅极电极，且在工作过程中，在一个行周期内，所述源极电极针对每一列的液晶单元分别输出正电压以及负电压，并且输出给所述每一列液晶单元的正电压与负电压是间隔的，从而使得一行液晶单元的极性为间隔的，并且在一个行周期内所述栅极电极会关闭，从而保持这一行液晶单元获得了稳定的电信号并保持该电信号直至一个帧周期结束后重新接收信号。相应地，在下一个行周期内，对下一行的所有列液晶单元做同样的操作。

通过这样的控制方式,保证了液晶面板上的每一个点的极性与其相邻的点的极性都是相反的,从而实现了背景技术中所描述的点反转模式。

[0050] 图2-2示出了根据现有技术的一个用于薄膜晶体管的液晶显示设备的行反转模式的示意图。与图2-1示意图相比较,其区别点在于,在一个行周期内,针对每一列液晶单元的源极电极都输出相同的电压,例如是正电压;相应地,在下一个行周期内,针对每一列液晶单元的源极电极也都输出相同的电压,例如是负电压,但在这个行周期内输出的电压与上一个周期输出的电压极性相反,从而使得相邻行的液晶单元的极性是相反的。进一步地,在下一个帧周期内,再对每一列液晶单元的源极电压的输出进行反转,就可以实现针对液晶显示设备的行反转模式。

[0051] 图3示出了根据现有技术的一个用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置的电路结构图。在图3中,示意性地示出了对应于四列液晶单元的驱动装置的电路结构图,其中,每一列的输出就是上述描述的源极电压。其中,以两列为一组,即A1、A2对应于两列液晶单元,优选地对应于相邻的两列液晶单元,但通过合适的扁平电缆、联机布置,也可以使得A1、A2对应于不相邻的两列液晶单元。本领域技术人员理解,只要保证A1、A2对应的两列液晶单元在工作过程中分别显示不同的极性即可,这并不会影响现有技术的实现,也不会影响本发明所阐述的发明内容的实现。以下阐述中优选地将A1、A2对应描述成针对相邻的两列液晶单元的控制,这并不影响本发明的技术内容,在此不予赘述。

[0052] 以D1、D2作为输入端的两列为例,所述D1输入端通过一个选择电路,即图3中从上向下的两个选择开关控制,并通过控制信号LN1、LN2的控制使得所述D1输入端向图3所示数字模拟转换器(DAC+,为了表述方便称为第一数字模拟转换器)以及另一个数字模拟转换器(DAC-,为了表述方便称为第二数字模拟转换器)输出,相应地,仍然是通过控制信息LN1、LN2使得所述D2输入端向该第一数字模拟转换器以及第二数字模拟转换器输出。相应地,在图3所示的电路结构中,所述D3、D4作为输入端的两列也是通过选择电路、控制信号与其对应的DAC+、DAC-输出,以此类推。进一步地,本领域技术人员理解,图3所示所述控制信号LN1、LN2优选地为相同的控制信号,即LN1控制信号控制多个开关,而这些开关分别归属于与不同输入端对应的选择电路,相应地,所述LN2控制信号也控制多个不同的开关。更进一步地,本领域技术人员理解,图3所示开关并没有标注图例开关1、开关2、开关3、开关4,而是用控制信号LN1、LN2表示其控制关系,这并不影响本领域技术人员对实现这些开关、选择电路的理解,在此不予赘述。

[0053] 进一步地,所述第一数字模拟转换器的输出端连接一个正向驱动缓冲器(为表述方便,我们优先地称其为P-Buffer)的输入端,而所述P-Buffer的输出端则通过一个选择电路分别连接A1、A2的输出端。进一步地,结合上述描述,本领域技术人员理解,所述A1、A2进一步地分别连接至一列液晶单元(例如M个液晶单元)的源极,从而使得A1、A2的输出作为所述液晶单元源极的输入,从而使得通过所述驱动装置控制所述液晶单元的极性。与之相配合,所述第二数字模拟转换器的输出端连接一个负向驱动缓冲器(为表述方便,我们优先地称其为N-Buffer)的输入端,而所述N-Buffer的输出端也通过一个选择电路分别连接A1、A2的输出端。在这样的现有技术中,在一个行周期内,经所述P-Buffer的作用,所述A1向所述液晶单元的源极输出正电压,相应地,在该行周期内,经所述N-Buffer的作用,所述A2向液晶单元的源极输出负电压,从而使得两列液晶单元获得一正一负不同的极性。类似地,

A3、A4也分别向液晶单元的源输出正电压、负电压,从而使得在一个行周期内N列液晶单元的源极分别获得正电压、负电压。而在下一个行周期内,经过所述N-Buffer的作用,所述A1向液晶单元的源极输出负电压,相应地,在该行周期内,经所述P-Buffer的作用,所述A2向液晶单元的源极输出正电压。类似地,A3、A4也分别向液晶单元的源极输出负电压、正电压,从而使得在该下一个行周期内N列液晶单元的源极分别获得负电压、正电压,且使得每一列液晶单元的极性正好相反,从而实现每个液晶单元的极性转换,即完成上述描述的点反转模式。

[0054] 本领域技术人员理解,图3所示电路结构图中,所述A1的正电压、负电压的切换,系通过与A1对应的选择电路完成,即通过控制信号LN1、LN2的控制来控制对应的选择电路中的开关的闭合切换来实现P-Buffer向A1输出正电压或者向A2输出正电压。相应地,所述A2的正电压、负电压的切换也是通过与A2对应的选择电路来完成的。与上述对于D1、D2与数字模拟转换器的连接关系描述相类似,在与A1、A2对应的选择电路也是不同的开关来组成,该等所述开关则通过控制信号LN1、LN2来实现。这些控制信号LN1、LN2与上述描述也是一致的,在此不予赘述。相应地,针对A3、A4的电路结构以及控制信号LN1、LN2的工作模式与上述描述也是一致的。在图3以及图4所示的现有技术中,一个行周期是开关控制信号的一个切换周期。

[0055] 在图3的基础上,图4进一步示出了根据现有技术的一个用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置输出电压的示意图。图4示出的驱动装置输出电压的示意与图3所示电路结构基本对应。具体地,在第一个行周期内,在时序控制信号的控制下,受控制信号LN1控制的对应开关闭合,相应地受控制信号LN2控制的对应开关断开,即控制信号LN1使得P-Buffer与A1导通、N-Buffer与A2导通。此时,公共电极输出的公共电压为VCOM,而P-Buffer输出正电压,例如在一个优选实施例中采用5~6V电压,从而使得P-Buffer的输出电压与VCOM相比为正电压,即所述A1输出正电压,相应地,所述N-Buffer输出负电压,例如在一个优选实施例中采用-5~-6V电压,从而使得N-Buffer的输出电压与VCOM相比为负电压,即所述A2输出负电压。从而使得A1输出正电压的同时A2输出负电压。类似地,本领域技术人员理解,基于同样的控制方式,在该行周期内,A3输出正电压的同时A4输出负电压,以此类推。

[0056] 在该第一个行周期内,当P-Buffer、N-Buffer的对外输出稳定后,即作为输出端的A1、A2等已经向液晶单元的源极输出了稳定的电压后,则栅极控制信号控制所述栅极电极关闭,即使得上述A1、A2所输出的电压被稳定地输出给所述液晶单元的源极,从而保证这一行的(M个)液晶单元稳定地显示信号。上述栅极电压关闭的过程,在图4中显示即为与第一行液晶单元匹配的栅极电压的栅极控制信号Gate1的电压从高变为低,以此类推。

[0057] 相应地,在第二个行周期内,受控制信号LN1控制的对应开关断开,相应地受控制信号LN2控制的对应开关闭合,即LN2使得N-Buffer与A1导通、P-Buffer与A2导通。此时,公共电极输出的公共电压仍然为VCOM,而P-Buffer仍然输出正电压,例如在一个优选实施例中采用5~6V电压,从而使得P-Buffer的输出电压与VCOM相比为正电压,即所述A2输出正电压,相应地,所述N-Buffer仍然输出负电压,例如在一个优选实施例中采用-5~-6V电压,从而使得N-Buffer的输出电压与VCOM相比为负电压,即所述A1输出负电压。从而使得A1输出负电压的同时A2输出正电压。类似地,本领域技术人员理解,基于同样的控制方式,在该行

周期内,A3输出负电压的同时A4输出正电压,从而使得与每一列液晶单元的源极对应的输出电压均进行了极性的反转,在此不予赘述。

[0058] 在该第二个行周期内,同样地,当P-Buffer、N-Buffer的对外输出稳定后,即作为输出端的A1、A2等已经向液晶单元的源极电极输出了稳定的电压后,则栅极控制信号控制所述栅极电极关闭,即使得上述A1、A2所输出的电压被稳定地输出给所述液晶单元的源极,从而保证第二行(如果假设第一个行周期控制的是第一行)的(N个)液晶单元稳定地显示信号。

[0059] 在第三个行周期内,重复第一个行周期的控制过程,从而使得第三行液晶单元获得了稳定的信号。在此过程中,只是与第三行液晶单元对应的栅极电极被关闭,即Gate3的电压从高变为低,而其他行液晶单元的栅极电极保持不变,以此类推。

[0060] 当N个行周期过后,则一个帧周期结束,开始下一个帧周期,继续重复上述第一个行周期的控制过程。

[0061] 通过上述控制过程可以理解,在上述过程中,控制信号LN1、LN2以一个行周期为周期进行切换,同时,公共电压始终保持为VCOM,本领域技术人员理解VCOM是相对恒变的电压,且P-Buffer、N-Buffer同时工作以使得A1、A2、A3、A4分别对外输出正电压、负电压、正电压、负电压等。

[0062] 相应地,在图3以及图4的基础上,图5示出了根据现有技术的一个用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置中的P-Buffer(图中示为P\_Buffer,与说明书中其他部分所表述为P Buffer均为同一部件)与N-Buffer(图中示为N\_Buffer,与说明书中其他部分所表述为N Buffer均为同一部件)的电路结构示意图。本领域技术人员,在现有技术的技术方案中,P-Buffer的电源AVDD应向P-Buffer提供5~6V的电压,从而使得P-Buffer的输出电压与VCOM(AMID提供接近0V的电压)相比为正电压;相应地,所述N-Buffer的电源AVEE应向N-Buffer提供-5~-6V的电压,从而使得N-Buffer的输出电压与VCOM(AMID提供接近0V的电压)相比为负电压。同时,本领域技术人员理解,在现有工艺中,提供P-Buffer的所需电压AVDD是相对较节省片内电容(on-chip capacitors),而提供N-Buffer所需电压AVEE是比较耗费大量的片内电容(on-chip capacitors),就会导致芯片面积非常大,从而成本高、耗电量也大。

[0063] 在图5基础上,图6示出了电荷泵(Charge Pump)的示意图,所述P-Buffer以及所述N-Buffer均通过电荷泵(Charge Pump)提供电压,即一个电荷泵分别连接电源以及接地电压,在图3、图4所示现有技术中,所述接地电压即为公共电压VCOM。在外部VCC为3V的情况下,通过上述电荷泵的工作,使得上述电荷泵的对外输出达到图3所示技术方案所需要的高电压5~6V,即得到图5所示的电源AVDD。类似地,也通过上述电荷泵的工作,获得图5所示的电源AVEE。但上述AVEE负电压的成本比较高。

[0064] 与上述图4相对比,图7示出了根据本发明的第一实施例的用于薄膜晶体管液晶显示设备的显示控制芯片中的驱动装置输出电压的示意图。与图4相比较,针对LN1、LN2的控制信号与现有技术具有明显不同。具体地,在第一个行周期内,在第一时间阶段P1内,受LN1控制信号控制的对应开关处于闭合状态,受LN2控制信号控制的对应开关处于断开状态,即所述P-Buffer的输出端与所述输出端A1相连接,N-Buffer的输出端与所述输出端A2相连接。在第一时间阶段P1内,设置与所述公共电极的公共电压为高电压VCOMH,同时设置所述

P-Buffer输出浮接或等于所述高电压VCOMH的电压。设置所述N-Buffer输出低于所述高电压VCOMH的电压,从而使得所述N-Buffer的输出电压与公共电压VCOMH相比为负电压。

[0065] 而在第二时间阶段P2内,受LN1控制信号控制的开关处于闭合状态,受LN2控制信号控制的开关处于断开状态。P buffer的输出浮接或是等于所述的高电压VCOMH,N-buffer的输出为浮接。相应的地设置与所述公共电极的公共电压为从VCOMH向下拉到正常电压VCOM,同时设置所述P-Buffer输出高于所述正常电压VCOM的高电压,从而使得所述P-Buffer的输出电压与公共电压VCOM相比为正电压,即所述A1输出正电压,“VCOMH”。

[0066] 相应地,在上述第二时间阶段P2内,公共电极的公共电压由高电压VCOMH转为正常电压VCOM,由于N-buffer的输出保持为浮动,所述输出端A2为浮动,由于面板上A2和公共电极的寄生电容关系,A2的电压仍会相对公共电极为低,即所述A2输出会保持负电压,“-VCOMH”。

[0067] 而在第三时间阶段P3内,受LN1控制信号控制的开关处于闭合状态,受LN2控制信号控制的开关处于断开状态。P-buffer输出面板所需的正电压,将电压由原先的“VCOMH”拉升到显示所需的正电压,即所述的A1输出面板所需的正电压。相应地,所述N-buffer的输出由原先的“-VCOMH”往下拉到面板所需的负电压,即所述的A2输出面板所需的负电压。

[0068] 相应地,在上述第三时间阶段P3内,与所述第一行周期对应的一行液晶单元的栅极电极闭合,从而使得在输出端A1的正电压稳定后,和输出端A2的负电压,被稳定在显示在对应液晶单元。在一个优选实施例中,所述第一行周期对应的一行液晶单元就是第一行液晶单元,而与其对应的栅极电极优选地为图7所示Gate1。本领域技术人员理解,在上述第三时间阶段P3对所述Gate1的电压切换仍然是通过电压控制信号完成的,。

[0069] 通过上述过程完成在第一个行周期内对第一行液晶单元的源极的源极电压(对应于A1的输出)以及栅极的栅极电压(对应于Gate1)的控制,上述过程具体参考图7的控制信号LN1、LN2的变化,对于公共电极的公共电压COM的控制,对于Gate1的控制,以及与两行液晶单元的源极电极对应的输出端A1、A2的电压变化。

[0070] 进一步地,在这样的优选实施例中,在下一个行周期内,优选地在第二个行周期内,与上一个行周期类似,在第一时间阶段P1内,受控制信号LN1控制的开关处于断开状态,相应地,受控制信号LN2控制的开关处于闭合状态,一个P-Buffer的输出端与所述输出端A2相连接,一个N-Buffer的输出端与所述输出端A1相连接具体如图7所示,相应地,在第一时间阶段P1内,设置与所述公共电极的公共电压为高电压VCOMH,同时设置所述P-Buffer输出浮接或是等于高电压VCOMH的电压,设置所述N-Buffer输出低于所述高电压VCOMH的电压,从而使得所述N-Buffer的输出电压与公共电压VCOMH相比为负电压。

[0071] 而在第二时间阶段P2内,受LN1控制信号控制的开关处于断开状态,受LN2控制信号控制的开关处于闭合状态。P-buffer的输出浮接或是等于所述的高电压VCOMH,N-buffer的输出为浮接。相应的地设置与所述公共电极的公共电压为从VCOMH向下拉到正常电压VCOM,同时设置所述P-Buffer输出高于所述正常电压VCOM的高电压,从而使得所述P-Buffer的输出电压与公共电压VCOM相比为正电压,即所述A2输出正电压,“VCOMH”。

[0072] 相应地,在上述第二时间阶段P2内,公共电极的公共电压由高电压VCOMH转为正常电压VCOM,由于N-buffer的输出保持为浮动,所述输出端A1为浮动,由于面板上A1和公共电极的寄生电容关系,A1的电压仍会相对公共电极为低,即所述A1输出会保持负电压,“-

VCOMH”。

[0073] 而在第三时间阶段P3内,受LN1控制信号控制的开关处于断开状态,受LN2控制信号控制的开关处于闭合状态。P-buffer输出面板所需的正电压,将电压由原先的“VCOMH”拉到显示所需的正电压,即所述的A2输出面板所需的正电压。N-buffer的输出由原先的“-VCOMH”往下拉到面板所需的负电压,即所述的A1输出面板所需的负电压。

[0074] 相应地,在上述第三时间阶段P3内,与所述输出端A2对应的第二行液晶单元的栅极电极进行闭合操作,即对图7所示Gate2电压进行切换,从而使得在输出端A2的正电压稳定后保持该第二行的信号被稳定在显示在所述液晶单元。本领域技术人员理解,在上述第三时间阶段P3对所述Gate2的电压切换仍然是通过电压控制信号完成的,与图4的电压控制信号相比较,所述电压切换优选是在第三时间阶段P3内完成的。

[0075] 通过上述过程完成在第二个行周期内对第二行液晶单元的源极电极的源极电压(对应于A2的输出)以及栅极电极的栅极电压(对应于Gate2),上述过程具体参考图7的所述控制信号LN1、LN2的变化,对于公共电极的公共电压COM的控制,对于Gate2的控制,以及与两行液晶单元的源极电极对应的输出端A1、A2的电压变化。

[0076] 再进一步地,在第三个行周期内,控制第三行、第四行液晶单元对应的源极的输出A3、A4(图7中未示出)的选择电路中的开关(也在与第一个行周期相类似的控制信号LN1、LN2的控制下执行闭合、断开动作。

[0077] 更进一步地,在第四个行周期内,控制第三行、第四行液晶单元对应的源极电极的源极电压A3、A4的所述开关也在与第二个行周期相类似的控制信号LN1、LN2的控制下执行闭合、断开的动作。

[0078] 更进一步地,在第五个行周期内以及后续的行周期内,针对下一行液晶单元也重复上述操作,从而使得每一行都在相应的行周期内输出正电压和负电压。当N个行周期过后,则一个帧周期结束,开始下一个帧周期,继续重复上述第一个行周期的控制过程。

[0079] 通过上述控制过程可以理解,在上述过程中,在一个行周期,公共电压存在从初始化设置为VCOMH、然后再设置为VCOM的过程,且P-Buffer对外分两阶段输出正电压,即等于高电压VCOMH的电压(此时P-Buffer的电压为正),然后再输出显示面板所需要的正电压;而N-Buffer对外分为三个阶段输出,输出低于所述高电压VCOMH的电压,接着浮动不输出,最后输出面板所需要的负电压。

[0080] 进一步地,本领域技术人员理解,在上述图7所示的控制过程中,在所述第三时间阶段P3的某一个时间点,优选地,在所述正电压列的电压相对所述公共电极达到最终预期值之后或者那个时刻,所述栅极电极(Gate)被关闭,相应地,采样所述源极电极上的电压进入薄膜晶体管液晶显示设备的液晶单元。进一步地,本领域技术人员理解,所述时刻点的选择可以根据芯片的具体要求而设定,例如时刻点的一点点偏移并不影响本发明的实质内容,都在本发明的保护范围内,在此不予赘述。

[0081] 更进一步地,本领域技术人员理解,在所述第三时间阶段P3至所述一个行周期结束之间的时间阶段内,所述栅极电压可以在任何一个时间点被关闭,而不限于必须在某一个特定时间点关闭,在此不予赘述。

[0082] 进一步地,在一个优选实施例中,所述第一时间阶段P1与所述第二时间阶段P2相等,而第三时间P3大于P1和P2。而在另一个优选实施例中,所述第一时间阶段P1的周期小于

所述第二时间阶段P2，即P1<P2，即在一个行周期内，向负电压列提供负电压的准备时间短于向正电压提供正电压的准备时间。本领域技术人员理解，随着所述第二时间阶段P2的到来，这样的过程是通过控制公共电压VCOM的控制，还有N-Buffer输出浮接来实现的，而从所述第二时间阶段P2开始，如前所述的正电压列对应的源极电压被设置为高于所述正常电压，从而对正电压列的液晶单元的源极提供正电压。在另外一个实施例中，所述第一时间阶段P1的周期大于所述第二时间阶段P2，即P1>P2，即在一个行周期内，向负电压列提供负电压的准备时间长于向正电压提供正电压的准备时间，在此不予赘述。基于类似的控制方式，本领域技术人员可以理解，如何对一个行周期内的不同阶段的时间进行控制。相应地，所述三个阶段的顺序关系也可以进行不同方式的调整，这些变化都在本发明的保护范围内，在此不予赘述。

[0083] 进一步地，本领域技术人员理解，在一个优选实施例中，在上述第一时间阶段P1周期内，所述正电压列对应的源极电极保持浮动。本领域技术人员理解，源极电极保持浮动意味着不需要对所述源极电极提供额外的电压，使得所述源极电极在上一个行周期结束时的状态上自己产生变化，即浮动。在浮动状态下，所述电路的耗电相对非常小，在此不予赘述。

[0084] 更进一步地，在另一个优选实施例中，在所述第一时间阶段P1内，在所述公共电极被设置到所述高电压之前，所有所述源极电极保持浮动。本领域技术人员结合上述描述，能够理解对电极保持浮动如何实现，在此不予赘述。

[0085] 更进一步地，在又一个优选实施例中，在所述第一时间阶段P1内，在所述公共电极被设置到所述高电压之前，所有所述栅极电极保持浮动。

[0086] 而在另一个优选实施例中，在所述第二时间阶段P2内，在所述公共电极被设置到所述正常电压之前，所有所述源极电极保持浮动。

[0087] 更进一步地，在又一个优选实施例中，在所述第二时间阶段P2内，在所述公共电极被设置到所述正常电压之前，所有所述栅极电极保持浮动。

[0088] 本领域技术人员理解，在本发明提供的各种实施例中，通过对公共电压、源极电压的控制，使得即使在部分电极保持浮动的情况下，仍然能够对所述源极提供稳定的正电压或者负电压，从而实现本发明的技术目的，在此不予赘述。

[0089] 更进一步地，本领域技术人员理解，通过本发明提供的优选实施例，在一个行周期的第一阶段P1内，设置公共电极为高电压，并相应地设置负电压列对应的源极电压低于所述高电压以使得所述负电压列的输出信号相对为负；在所述行周期的第二阶段P2内，设置所述公共电极为正常电压，并相应地设置正电压列对应的源极电压高于所述正常电压以使得所述正电压列的输出信号相对为正。而负列电压的输出为浮接，藉由公共电极高转低的作用，藉由面板上的寄生电容产生出真正的负电压。第三阶段P3内，正电压列和负电压列只需再些微充电就可以达到预期目标电压。本发明还提供对应的驱动装置以及显示控制芯片。通过本发明，使得电荷泵(Charge Pump)结构，和需要的片上电容(on-chip capacitors)在至少减少一半的情况下实现现有技术效果一致的点反转模式，从而大大节省了针对薄膜晶体管液晶显示设备的显示控制芯片的面积，也减少了这样的显示控制芯片的耗电量。

[0090] 更进一步地，本领域技术人员理解，本发明对应的硬件结构可以部分参考现有技术：中国专利申请“低功率薄膜晶体管液晶显示控制芯片、驱动装置及控制方法”、中国专利

申请号:201710997686.X中描述的原理予以实现,例如开关的设置和控制,P-Buffer、N-Buffer与其他部件的连接关系等,在此不予赘述。

[0091] 以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变形或修改,这并不影响本发明的实质内容。

图1

图2-1

图2-2

图3

图4

OP 架构

图5

图6

图7

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种用于薄膜晶体管液晶显示的控制方法、装置及系统                       |         |            |

| 公开(公告)号        | <a href="#">CN111243549A</a>                   | 公开(公告)日 | 2020-06-05 |

| 申请号            | CN202010219774.9                               | 申请日     | 2020-03-25 |

| [标]申请(专利权)人(译) | 新相微电子(上海)有限公司                                  |         |            |

| 申请(专利权)人(译)    | 新相微电子(上海)有限公司                                  |         |            |

| 当前申请(专利权)人(译)  | 新相微电子(上海)有限公司                                  |         |            |

| [标]发明人         | 肖宏<br>覃正才<br>周剑<br>林昆宗                         |         |            |

| 发明人            | 肖宏<br>覃正才<br>周剑<br>林昆宗                         |         |            |

| IPC分类号         | G09G3/36                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明提供用于薄膜晶体管液晶显示信号的控制方法，包括步骤：在一个行周期的第一阶段P1内，设置公共电极为高电压，并相应地设置负电压列对应的源极电压低于所述高电压以使得所述负电压列的输出信号相对为负；在所述行周期的第二阶段P2内，设置所述公共电极为正常电压，并相应地设置正电压列对应的源极电压高于所述正常电压以使得所述正电压列的输出信号相对为正。而负列电压的输出为浮接，藉由公共电极高转低的作用产生出负电压。第三阶段P3内，些微充电以达到预期目标电压。本发明还提供对应驱动装置及控制芯片。通过本发明，使得电荷泵、片上电容在至少减少一半的情况下实现现有技术效果一致的点反转模式，减少了显示控制芯片的耗电量。