(12)发明专利申请

(10)申请公布号 CN 110189671 A

(43)申请公布日 2019.08.30

(21)申请号 201910561526.X

(22)申请日 2019.06.26

(71)申请人 滁州惠科光电科技有限公司

地址 239000 安徽省滁州市琅琊区滁州经济技术开发区苏滁大道101号

申请人 北海惠科光电技术有限公司

(72)发明人 黄世帅

(74)专利代理机构 广州华进联合专利商标代理有限公司 44224

代理人 景怀宇

(51)Int.Cl.

G09G 3/00(2006.01)

G02F 1/13(2006.01)

权利要求书2页 说明书6页 附图2页

(54)发明名称

成盒测试电路、阵列基板和液晶显示装置

(57)摘要

本发明实施例了一种成盒测试电路、阵列基板和液晶显示装置。所述成盒测试电路用于对液晶显示面板测试，所述液晶显示面板包括显示区域和非显示区域，所述成盒测试电路包括设置在所述非显示区域中的多个测试焊盘组，其中至少一个所述测试焊盘组包括两个测试焊盘对和一个转接焊盘，且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘，其中一个所述测试焊盘对包括一个奇数数据测试焊盘和一个偶数数据测试焊盘。

1. 一种成盒测试电路, 用于对液晶显示面板测试, 所述液晶显示面板包括显示区域和非显示区域, 其特征在于, 所述成盒测试电路包括设置在所述非显示区域中的多个测试焊盘组, 其中至少一个所述测试焊盘组包括两个测试焊盘对和一个转接焊盘, 且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘, 其中一个所述测试焊盘对包括一个奇数数据测试焊盘和一个偶数数据测试焊盘。

2. 如权利要求1所述的成盒测试电路, 其特征在于, 在同一所述测试焊盘组中, 所述转接焊盘设置在两个所述测试焊盘对之间。

3. 如权利要求2所述的成盒测试电路, 其特征在于, 所述测试焊盘组包括依次排列设置的第一奇数数据测试焊盘、第一偶数数据测试焊盘、转接焊盘、第二奇数数据测试焊盘和第二偶数数据测试焊盘;

所述第一奇数数据测试焊盘和所述第二奇数数据测试焊盘, 均与所述液晶显示面板中的奇数测试信号线以及所述液晶显示面板中的集成电路电连接;

所述第一偶数数据测试焊盘和所述第二偶数数据测试焊盘, 均与所述偶数测试信号线以及所述集成电路电连接;

所述转板焊盘与所述液晶显示面板中的彩膜基板电连接。

4. 如权利要求3所述的成盒测试电路, 其特征在于, 还包括转接板, 所述转接焊盘与所述彩膜基板通过所述转接板实现电连接。

5. 如权利要求4所述的成盒测试电路, 其特征在于, 在成盒测试过程中, 所述第一奇数数据测试焊盘和所述第二奇数数据测试焊盘分别通过所述奇数测试信号线输出数据信号, 所述第一偶数数据测试焊盘和所述第二偶数数据测试焊盘分别通过所述偶数测试信号线输出数据信号, 所述转接焊盘通过所述转接板为所述彩膜基板提供公共电压信号。

6. 如权利要求3所述的成盒测试电路, 其特征在于, 每一所述奇数数据测试焊盘对应一条所述奇数数据测试信号线, 每一所述偶数数据测试焊盘对应一条所述偶数数据测试信号线。

7. 一种阵列基板, 其特征在于, 包括显示区域和非显示区域, 所述非显示区域中设置有成盒测试电路, 所述成盒测试电路包括多个测试焊盘组, 其中至少一个所述测试焊盘组包括两个测试焊盘对和一个转接焊盘, 且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘, 其中一个所述测试焊盘对包括一个奇数数据测试焊盘和一个偶数数据测试焊盘。

8. 如权利要求7所述的阵列基板, 其特征在于, 在同一所述测试焊盘组中, 所述转接焊盘设置在两个所述测试焊盘对之间。

9. 如权利要求7所述的阵列基板, 其特征在于, 所述测试焊盘组包括依次排列设置的第一奇数数据测试焊盘、第一偶数数据测试焊盘、转接焊盘、第二奇数数据测试焊盘和第二偶数数据测试焊盘;

所述第一奇数数据测试焊盘和所述第二奇数数据测试焊盘, 均与所述阵列基板中的奇数测试信号线以及所述阵列基板中的集成电路电连接;

所述第一偶数数据测试焊盘和所述第二偶数数据测试焊盘, 均与所述偶数测试信号线以及所述集成电路电连接;

所述转板焊盘与和所述阵列基板匹配的彩膜基板电连接。

10. 一种液晶显示装置, 其特征在于, 所述液晶显示装置包括如权利要求7~9任一权项

所述的阵列基板。

## 成盒测试电路、阵列基板和液晶显示装置

### 技术领域

[0001] 本发明涉及液晶显示技术领域,尤其涉及一种成盒测试电路、阵列基板和液晶显示装置。

### 背景技术

[0002] 目前在对显示面板进行绑定工艺前,需要通过shorting bar(短接棒)点灯的方式来进行点灯测试,将测试数据信号分成ODD奇数类和偶数类,奇数类信号会串在一起电连接到一个测试区域;偶数类讯号会串在一起,电连接到另一个测试区域。通过给测试区域施加测试信号传入到显示面板内以完成对盒测试。

[0003] 随着电视行业技术的发展,人们对于液晶显示的品质要求越来越高,液晶显示面板的解析度也越来越高。对于大尺寸高解析度产品来说,CFO(Chip On Flex,or,Chip On Film,覆晶薄膜)数目会增加,CFO之间的测试区域也会随着增多。在点灯测试的过程中,过多的测试区域必然要增多的扎针数目以及增大扎针时间,严重影响了检测效率。

### 发明内容

[0004] 基于此,本提供一种成盒测试电路、阵列基板和液晶显示装置,以减少点灯测试时的扎针的数据和扎针的组数,进而缩短测试时间,提供测试效率。

[0005] 本发明实施例提供了一种成盒测试电路,用于对液晶显示面板测试,所述液晶显示面板包括显示区域和非显示区域,所述成盒测试电路包括设置在所述非显示区域中的多个测试焊盘组,其中至少一个所述测试焊盘组包括两个测试焊盘对和一个转接焊盘,且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘,其中一个所述测试焊盘对包括一个奇数数据测试焊盘和一个偶数数据测试焊盘。

[0006] 在其中一个实施例中,在同一所述测试焊盘组中,所述转接焊盘设置在两个所述测试焊盘对之间。

[0007] 在其中一个实施例中,所述测试焊盘组包括依次排列设置的第一奇数数据测试焊盘、第一偶数数据测试焊盘、转接焊盘、第二奇数数据测试焊盘和第二偶数数据测试焊盘;

[0008] 所述第一奇数数据测试焊盘和所述第二奇数数据测试焊盘,均与所述液晶显示面板中的奇数测试信号线以及所述液晶显示面板中的集成电路电连接;

[0009] 所述第一偶数数据测试焊盘和所述第二偶数数据测试焊盘,均与所述偶数测试信号线以及所述集成电路电连接;

[0010] 所述转板焊盘与所述液晶显示面板中的彩膜基板电连接。

[0011] 在其中一个实施例中,所述成盒测试电路还包括转接板,所述转接焊盘与所述彩膜基板通过所述转接板实现电连接。

[0012] 在其中一个实施例中,在成盒测试过程中,所述第一奇数数据测试焊盘和所述第二奇数数据测试焊盘分别通过所述奇数测试信号线输出数据信号,所述第一偶数数据测试焊盘和所述第二偶数数据测试焊盘分别通过所述偶数测试信号线输出数据信号,所述转接

焊盘通过所述转接板为所述彩膜基板提供公共电压信号。

[0013] 在其中一个实施例中,每一所述奇数数据测试焊盘对应一条所述奇数数据测试信号线,每一所述偶数数据测试焊盘对应一条所述偶数数据测试信号线。

[0014] 基于同一发明构思,本发明实施例还提供了一种阵列基板,所述阵列基板包括显示区域和非显示区域,所述非显示区域中设置有成盒测试电路,所述成盒测试电路包括多个测试焊盘组,其中至少一个所述测试焊盘组包括两个测试焊盘对和一个转接焊盘,且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘,其中一个所述测试焊盘对包括一个奇数数据测试焊盘和一个偶数数据测试焊盘。

[0015] 在其中一个实施例中,在同一所述测试焊盘组中,所述转接焊盘设置在两个所述测试焊盘对之间。

[0016] 在其中一个实施例中,所述测试焊盘组包括依次排列设置的第一奇数数据测试焊盘、第一偶数数据测试焊盘、转接焊盘、第二奇数数据测试焊盘和第二偶数数据测试焊盘;

[0017] 所述第一奇数数据测试焊盘和所述第二奇数数据测试焊盘,均与所述阵列基板中的奇数测试信号线以及所述阵列基板中的集成电路电连接;

[0018] 所述第一偶数数据测试焊盘和所述第二偶数数据测试焊盘,均与所述偶数测试信号线以及所述集成电路电连接;

[0019] 所述转板焊盘与和所述阵列基板匹配的彩膜基板电连接。

[0020] 基于同一发明构思,本发明实施例还提供了一种液晶显示装置,所述液晶显示装置包括上述任一实施例所述的阵列基板。

[0021] 综上,本发明实施例了一种成盒测试电路、阵列基板和液晶显示装置。所述成盒测试电路用于对液晶显示面板测试,所述液晶显示面板包括显示区域和非显示区域,所述成盒测试电路包括设置在所述非显示区域中的多个测试焊盘组,其中至少一个所述测试焊盘组包括两个测试焊盘对和一个转接焊盘,且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘,其中一个所述测试焊盘对包括一个奇数数据测试焊盘和一个偶数数据测试焊盘。本发明中,将原本位于每对COF之间的测试焊盘组两两归在一起,通过一组扎针对两对相邻的COF实现测试,减少一半的扎针组数从而提高了检测效率,同时,同一测试焊盘组中的两对测试焊盘共用一个转接焊盘,在利用其中的一对测试焊盘完成测试换后,然后再利用另一对测试焊盘进行测试时,不需要再对转接焊盘进行插针,减少了对转接焊盘的插针次数,进一步提高了检测效率。

## 附图说明

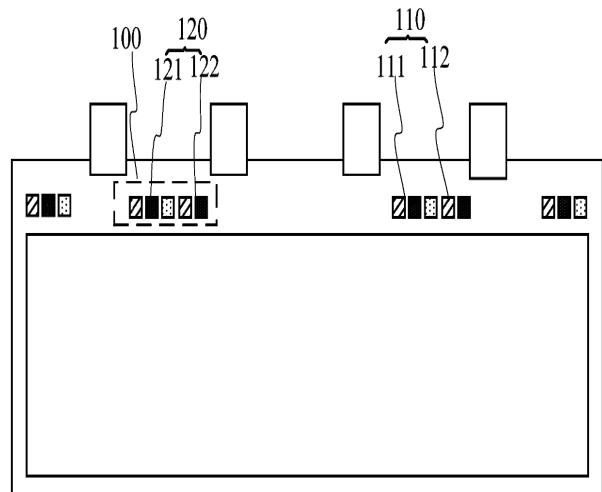

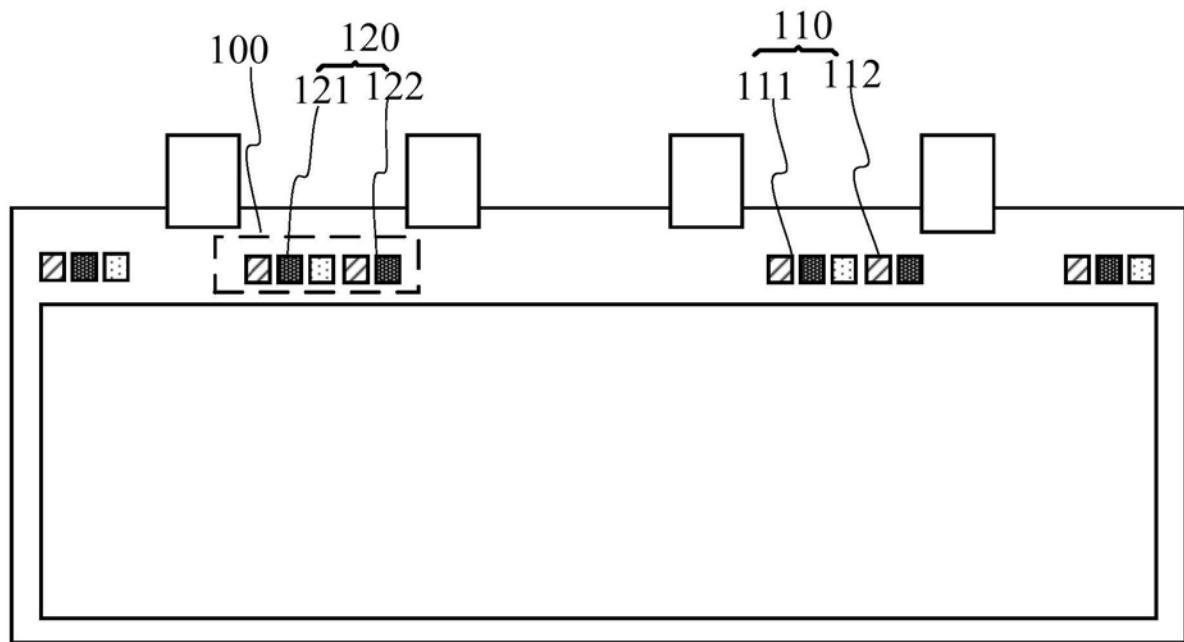

[0022] 图1为示例性的成盒测试电路的结构示意图;

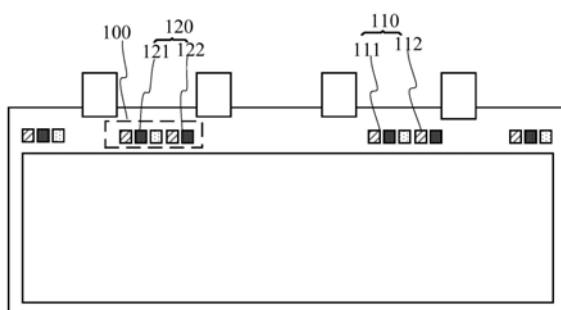

[0023] 图2为示例性成盒测试电路中的布线示意图;

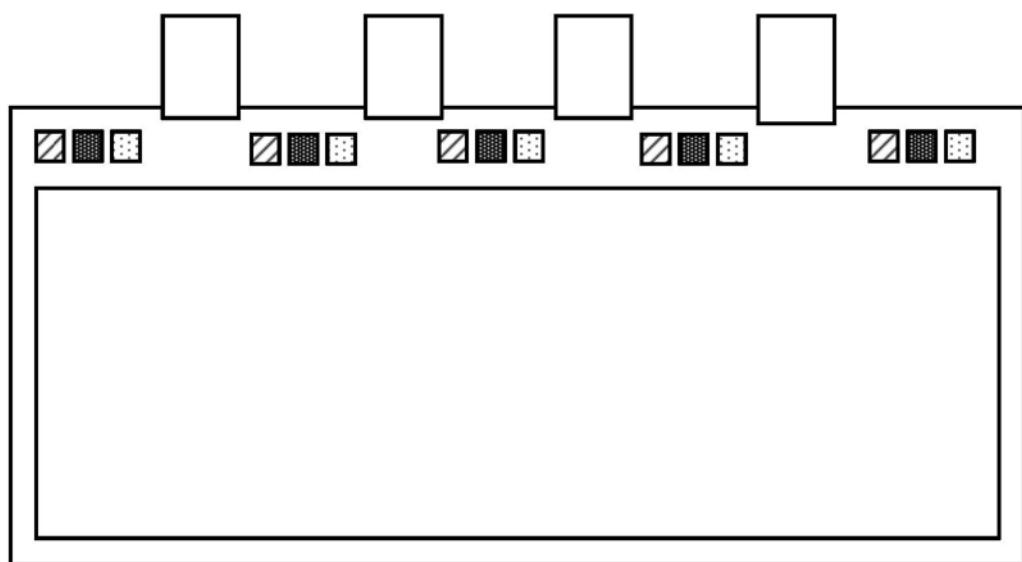

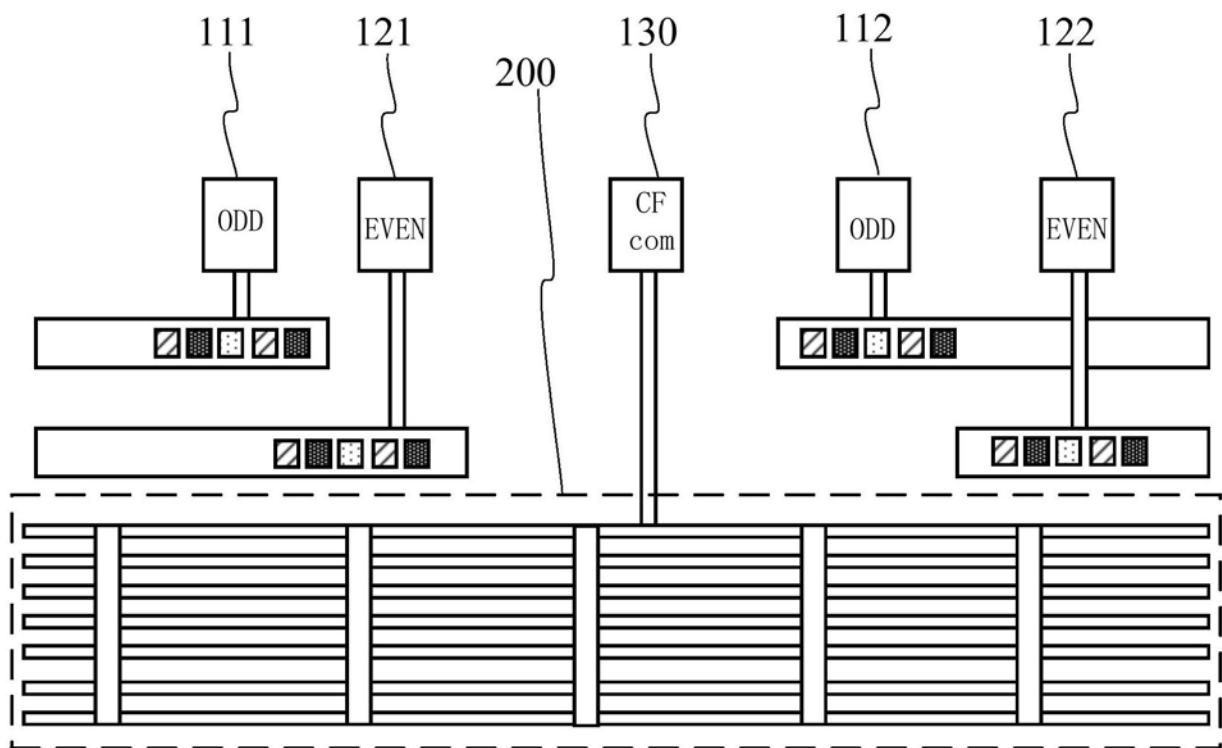

[0024] 图3为本发明实施例提供的结构示意图;

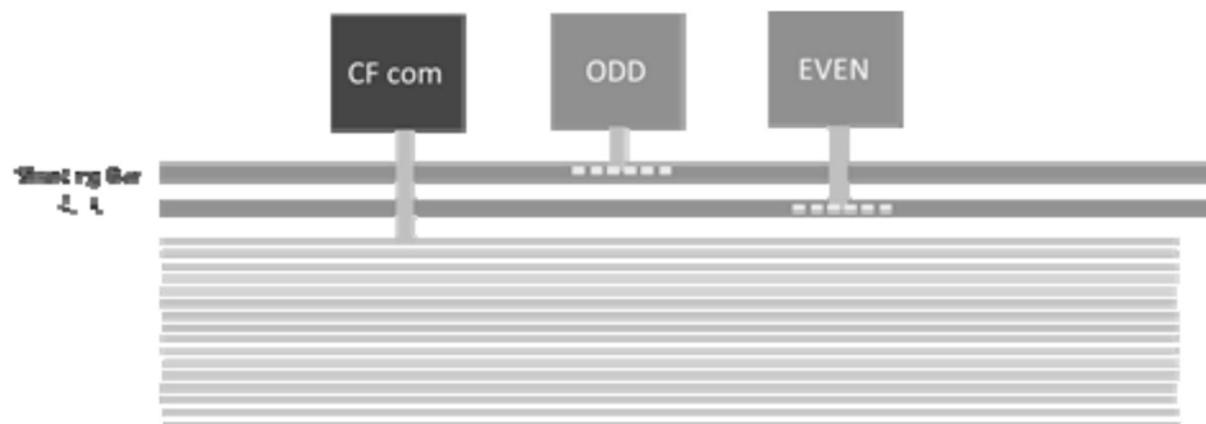

[0025] 图4为本发明实施例提供的成盒测试电路的布线示意图。

## 具体实施方式

[0026] 为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图对本发明的具体实施方式做详细的说明。在下面的描述中阐述了很多具体细节以便于充分理解本发

明。但是本发明能够以很多不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本发明内涵的情况下做类似改进,因此本发明不受下面公开的具体实施的限制。

[0027] 在TFT-LCD (Thin Film Transistor-Liquid Crystal Display, 薄膜晶体管液晶显示器) 的制造过程中, 在将TFT阵列基板与彩膜基板对合形成显示模组 (Cell盒) 之后, 集成电路 (IC) 焊接到Cell盒之前, 需要对TFT基板上各个薄膜晶体管的功能通过shorting bar (短接棒) 点灯的方式来进行点灯测试。请参见图1和图2, 每对COF之间都设置有cell test pad (测试区), 每一cell test pad都要通过扎针给提供信号。

[0028] 对于大尺寸高解析度产品, COF数目会增加, COF之间的cell test pad组数也会随着增加。过多的cell test pad必然要多的扎针数目和扎针时间, 从而影响检测效率。

[0029] 针对上述问题, 本发明实施例提供了一种成盒测试电路, 请参见图3和图4, 所述成盒测试电路用于对液晶显示面板测试, 所述液晶显示面板包括显示区域和非显示区域, 所述成盒测试电路包括设置在所述非显示区域中的多个测试焊盘组100, 其中至少一个所述测试焊盘组100包括两个测试焊盘对和一个转接焊盘130, 且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘130, 其中一个所述测试焊盘对包括一个奇数数据测试焊盘110和一个偶数数据测试焊盘120。

[0030] 可以理解, 将原本位于每对COF之间的测试焊盘组100两两归在一起, 通过一组扎针对两对相邻的COF实现测试, 可减少一半的扎针组数, 从而提高了检测效率。同时, 同一测试焊盘组100中的两对测试焊盘共用一个转接焊盘130, 在利用其中的一对测试焊盘完成测试换后, 然后再利用另一对测试焊盘进行测试时, 不需要再对转接焊盘130进行插针, 减少了对转接焊盘130的插针次数, 进一步提高了检测效率。此外, 两对测试焊盘共用一个转接焊盘130, 还节省了一个转接焊盘130的制作空间和制作成本。

[0031] 在其中一个实施例中, 在同一所述测试焊盘组100中, 所述转接焊盘130设置在所述两个测试焊盘对之间。可以理解, 所述测试焊盘组100设置在相邻的两个COF之间, 每一对测试焊盘均与其同侧的COF电连接, 所述转接焊盘130为同一组中的两对测试焊盘共用, 因此当所述转接焊盘130设置在所述两对测试焊盘之间, 可避免引线之间产生交叉, 有利于简化布线设计。

[0032] 在其中一个实施例中, 所述测试焊盘组包括依次排列设置的第一奇数数据测试焊盘110、第一偶数数据测试焊盘120、转接焊盘130、第二奇数数据测试焊盘110和第二偶数数据测试焊盘120。

[0033] 所述第一奇数数据测试焊盘110和所述第二奇数数据测试焊盘110, 均与所述液晶显示面板中的奇数测试信号线以及所述液晶显示面板中的集成电路电连接。

[0034] 所述第一偶数数据测试焊盘120和所述第二偶数数据测试焊盘120, 均与所述偶数测试信号线以及所述集成电路电连接。

[0035] 所述转板焊盘与所述液晶显示面板中的彩膜基板电连接。

[0036] 本实施例中, 所述测试焊盘组包括依次排列设置的第一奇数数据测试焊盘111、第一偶数数据测试焊盘121、转接焊盘130、第二奇数数据测试焊盘112和第二偶数数据测试焊盘122, 在测试过程中, 可通过第一奇数数据测试焊盘111和第一偶数数据测试焊盘121分别为与其对应的COF中的集成电路提供奇数数据和偶数数据, 以及通过第二奇数数据测试焊盘112和第二偶数数据测试焊盘122分别为与其对应的COF中的集成电路提供奇数数据和偶数

数据,以实现点灯测试。此外,在测试过程中,两对所述测试焊盘通过共用的所述转接焊盘130与液晶显示面板中的彩膜基板电连接。

[0037] 在其中一个实施例中,所述成盒测试电路还包括转接板200,所述转接焊盘130与所述彩膜基板通过所述转接板200实现电连接。

[0038] 在其中一个实施例中,在成盒测试过程中,所述第一奇数数据测试焊盘111和所述第二奇数数据测试焊盘112分别通过所述奇数测试信号线输出数据信号,所述第一偶数数据测试焊盘121和所述第二偶数数据测试焊盘122分别通过所述偶数测试信号线输出数据信号,所述转接焊盘130通过所述转接板200为所述彩膜基板提供公共电压信号。即,本实施例中所述第一奇数数据测试焊盘111和所述第二奇数数据测试焊盘112分别通过所述奇数测试信号线输出数据信号,所述第一偶数数据测试焊盘121和所述第二偶数数据测试焊盘122分别通过所述偶数测试信号线输出数据信号,阵列基板在接收所述数据信号后,与接收公共电压信号后的彩膜基板之间形成电场,驱动液晶分子进行旋转,从而实现显示测试。

[0039] 在其中一个实施例中,每一所述奇数数据测试焊盘110对应一条所述奇数数据测试信号线,每一所述偶数数据测试焊盘120对应一条所述偶数数据测试信号线。可以理解,由于同一测试焊盘组100内的两对测试焊盘共用一个转接焊盘130,因此若奇数数据测试焊盘110仍串联在一条测试信号线中,偶数数据测试焊盘120仍串联在另一个测试信号信中,则同一测试焊盘组100对应的两个COF会同时进行工作,无法对COF进行逐一测试。本实施例中,每一所述奇数数据测试焊盘110对应一条所述奇数数据测试信号线,每一所述偶数数据测试焊盘120对应一条所述偶数数据测试信号线,可单独提供信号给每一奇数数据测试焊盘110和偶数数据测试焊盘120,从而可实现对COF进行逐一测试。

[0040] 基于同一发明构思,本发明实施例还提供了一种阵列基板,所述阵列基板包括显示区域和非显示区域,所述非显示区域中设置有成盒测试电路,所述成盒测试电路包括多个测试焊盘组100,其中至少一个所述测试焊盘组100包括两个测试焊盘对和一个转接焊盘130,且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘130,其中一个所述测试焊盘对包括一个奇数数据测试焊盘110和一个偶数数据测试焊盘120。

[0041] 可以理解,将原本位于每对COF之间的测试焊盘组100两两归在一起,通过一组扎针对两对相邻的COF实现测试,可减少一半的扎针组数,从而提高了检测效率。同时,同一测试焊盘组100中的两对测试焊盘共用一个转接焊盘130,在利用其中的一对测试焊盘完成测试换后,然后再利用另一对测试焊盘进行测试时,不需要再对转接焊盘130进行插针,减少了对转接焊盘130的插针次数,进一步提高了检测效率。此外,两对测试焊盘共用一个转接焊盘130,还节省了一个转接焊盘130的制作空间和制作成本。

[0042] 在其中一个实施例中,在同一所述测试焊盘组100中,所述转接焊盘130设置在所述两个测试焊盘对之间。可以理解,所述测试焊盘组100设置在相邻的两个COF之间,每一对测试焊盘均与其同侧的COF电连接,所述转接焊盘130为同一组中的两对测试焊盘共用,因此当所述转接焊盘130设置在所述两对测试焊盘之间,可避免引线之间产生交叉,有利于简化布线设计。

[0043] 在其中一个实施例中,所述测试焊盘组包括依次排列设置的第一奇数数据测试焊盘110、第一偶数数据测试焊盘120、转接焊盘130、第二奇数数据测试焊盘110和第二偶数数据测试焊盘120。

[0044] 所述第一奇数数据测试焊盘110和所述第二奇数数据测试焊盘110,均与所述液晶显示面板中的奇数测试信号线以及所述液晶显示面板中的集成电路电连接。

[0045] 所述第一偶数数据测试焊盘120和所述第二偶数数据测试焊盘120,均与所述偶数测试信号线以及所述集成电路电连接。

[0046] 所述转板焊盘与所述液晶显示面板中的彩膜基板电连接。

[0047] 本实施例中,所述测试焊盘组包括依次排列设置的第一奇数数据测试焊盘110、第一偶数数据测试焊盘120、转接焊盘130、第二奇数数据测试焊盘110和第二偶数数据测试焊盘120,在测试过程中,可通过第一奇数数据测试焊盘110和第一偶数数据测试焊盘120分别为与其对应的COF中的集成电路提供奇数数据和偶数数据,以及过第二奇数数据测试焊盘110和第二偶数数据测试焊盘120分别为与其对应的COF中的集成电路提供奇数数据和偶数数据,以实现点灯测试。此外,在测试过程中,两对所述测试焊盘通过共用的所述转接焊盘130与液晶显示面板中的彩膜基板电连接。

[0048] 在其中一个实施例中,所述成盒测试电路还包括转接板200,所述转接焊盘130与所述彩膜基板通过所述转接板200实现电连接。

[0049] 在其中一个实施例中,在成盒测试过程中,所述第一奇数数据测试焊盘和所述第二奇数数据测试焊盘分别通过所述奇数测试信号线输出数据信号,所述第一偶数数据测试焊盘和所述第二偶数数据测试焊盘分别通过所述偶数测试信号线输出数据信号,所述转接焊盘130通过所述转接板200为所述彩膜基板提供公共电压信号。

[0050] 在其中一个实施例中,每一所述奇数数据测试焊盘110对应一条所述奇数数据测试信号线,每一所述偶数数据测试焊盘120对应一条所述偶数数据测试信号线。

[0051] 基于同一发明构思,本发明实施例还提供了一种液晶显示装置,所述液晶显示装置包括如上述任一实施例所述的阵列基板

[0052] 综上,本发明实施例了一种成盒测试电路、阵列基板和液晶显示装置。所述成盒测试电路用于对液晶显示面板测试,所述液晶显示面板包括显示区域和非显示区域,所述成盒测试电路包括设置在所述非显示区域中的多个测试焊盘组100,其中至少一个所述测试焊盘组100包括两个测试焊盘对和一个转接焊盘130,且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘130,其中一个所述测试焊盘对包括一个奇数数据测试焊盘110和一个偶数数据测试焊盘120。本发明中,将原本位于每对COF之间的测试焊盘组100两两归在一起,通过一组扎针对两对相邻的COF实现测试,减少一半的扎针组数,从而提高了检测效率。同时,同一测试焊盘组100中的两对测试焊盘共用一个转接焊盘130,在利用其中的一对测试焊盘完成测试换后,然后再利用另一对测试焊盘进行测试时,不需要再对转接焊盘130进行插针,减少了对转接焊盘130的插针次数,进一步提高了检测效率。此外,两对测试焊盘共用一个转接焊盘130,还节省了一个转接焊盘130的制作空间和制作成本。

[0053] 以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0054] 以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护

范围。因此,本发明专利的保护范围应以所附权利要求为准。

图1

图2

图3

图4

|         |                              |                      |            |

|---------|------------------------------|----------------------|------------|

| 专利名称(译) | 成盒测试电路、阵列基板和液晶显示装置           |                      |            |

| 公开(公告)号 | <a href="#">CN110189671A</a> | 公开(公告)日              | 2019-08-30 |

| 申请号     | CN201910561526.X             | 申请日                  | 2019-06-26 |

| [标]发明人  | 黄世帅                          |                      |            |

| 发明人     | 黄世帅                          |                      |            |

| IPC分类号  | G09G3/00 G02F1/13            |                      |            |

| CPC分类号  | G02F1/1309 G09G3/006         |                      |            |

| 外部链接    | <a href="#">Espacenet</a>    | <a href="#">SIPO</a> |            |

### 摘要(译)

本发明实施例了一种成盒测试电路、阵列基板和液晶显示装置。所述成盒测试电路用于对液晶显示面板测试，所述液晶显示面板包括显示区域和非显示区域，所述成盒测试电路包括设置在所述非显示区域中的多个测试焊盘组，其中至少一个所述测试焊盘组包括两个测试焊盘对和一个转接焊盘，且在成盒测试过程中所述两个测试焊盘对共用所述转接焊盘，其中一个所述测试焊盘对包括一个奇数数据测试焊盘和一个偶数数据测试焊盘。