## (12) 发明专利申请

(10) 申请公布号 CN 103777419 A

(43) 申请公布日 2014.05.07

(21) 申请号 201210410154.9

G09G 3/34 (2006. 01)

(22) 申请日 2012.10.24

(71) 申请人 群康科技(深圳)有限公司

地址 518109 广东省深圳市宝安区龙华镇富士康科技工业园区 E 区 4 栋 1 楼

申请人 奇美电子股份有限公司

(72) 发明人 谢耀联 欧阳祥睿 黄钰胜

吴青龙

(74) 专利代理机构 北京三友知识产权代理有限公司 11127

代理人 任默闻

(51) Int. Cl.

G02F 1/1362 (2006. 01)

G02E 1/1368 (2006-01)

G02F 1/133 (2006, 01)

权利要求书2页 说明书6页 附图4页

(54) 发明名称

## 液晶显示装置

## (57) 摘要

本发明提供一种液晶显示装置包含多个像素、一扫描驱动电路以及一数据驱动电路。至少其中一个像素具有一第一电容、一第二电容以及一补偿电容，第一电容经由一电阻元件与补偿电容连接。扫描驱动电路经由多条扫描线驱动该等像素。一扫描线与一第一晶体管及一第二晶体管的栅极电连接。数据驱动电路经由多条数据线驱动该等像素。第一电容经由该第一晶体管与该一数据线电连接，第二电容经由第二晶体管与一数据线电连接。通过本发明的液晶显示装置，能够在改善色偏的同时，亦能使开口率提升并减少制造成本。

1. 一种液晶显示装置，其特征在于，所述的液晶显示装置包含：

多个像素，至少其中一像素具有一第一电容、一第二电容以及一补偿电容，所述第一电容经由一电阻元件与所述补偿电容电连接；

一扫描驱动电路，经由多条扫描线驱动所述多个像素，其中一所述扫描线与一第一晶体管及一第二晶体管的栅极电连接；以及

一数据驱动电路，经由多条数据线驱动所述多个像素，其中所述第一电容经由所述第一晶体管与一所述数据线电连接，所述第二电容经由所述第二晶体管与一所述数据线电连接。

2. 根据权利要求 1 所述的液晶显示装置，其特征在于，所述第一电容或所述第二电容包含一液晶电容与一储存电容。

3. 根据权利要求 1 所述的液晶显示装置，其特征在于，在所述第一晶体管被所述扫描线开启之后，所述第一电容与所述第一晶体管连接的一节点电压具有一准位变迁时间，所述准位变迁时间从所述节点的一充电状态到一放电状态，所述准位变迁时间大于等于图框时间的二百分之一，并小于等于图框时间的二分之一。

4. 根据权利要求 1 所述的液晶显示装置，其特征在于，所述电阻元件的阻抗值为 R，一图框时间为 T，所述第一电容的电容值为 C1，所述补偿电容的电容值为 CT，阻抗值 R 符合下列方程式：

$$T/1400 < RC < T/14, C = (C1 * CT) / (C1 + CT)。$$

5. 根据权利要求 1 所述的液晶显示装置，其特征在于，所述电阻元件的材质包含非晶硅、n<sup>+</sup> 非晶硅或其组合。

6. 一种液晶显示装置，其特征在于，所述的液晶显示装置包含：

多个像素，至少其中一像素具有一第一电容、一第二电容以及一补偿电容，所述第一电容经由一阻抗单元与所述补偿电容电连接；

一扫描驱动电路，经由多条扫描线驱动所述多个像素，其中一所述扫描线与一第一晶体管及一第二晶体管的栅极电连接；以及

一数据驱动电路，经由多条数据线驱动所述多个像素，其中所述第一电容经由所述第一晶体管与一所述数据线电连接，所述第二电容经由所述第二晶体管与一所述数据线电连接，

其中，所述阻抗单元的阻抗值为 R，一图框时间为 T，所述第一电容的电容值为 C1，所述补偿电容的电容值为 CT，阻抗值 R 符合下列方程式：

$$T/1400 < RC < T/14, C = (C1 * CT) / (C1 + CT)。$$

7. 根据权利要求 6 所述的液晶显示装置，其特征在于，所述阻抗单元包含一晶体管元件，所述晶体管元件的栅极电连接于一共同电压。

8. 根据权利要求 6 所述的液晶显示装置，其特征在于，在所述第一晶体管被所述扫描线开启之后，所述第一电容与所述第一晶体管连接的一节点电压具有一准位变迁时间，所述准位变迁时间从所述节点的一充电状态到一放电状态，所述准位变迁时间大于等于所述图框时间的二百分之一，并小于等于所述图框时间的二分之一。

9. 一种液晶显示装置，其特征在于，所述的液晶显示装置包含：

多个像素，至少其中一像素具有一第一电容、一第二电容以及一补偿电容，所述第一电

容经由一阻抗单元与所述补偿电容电连接；

一扫描驱动电路，经由多条扫描线驱动所述多个像素，其中一所述扫描线与一第一晶体管及一第二晶体管的栅极电连接；以及

一数据驱动电路，经由多条数据线驱动多个像素，其中所述第一电容经由所述第一晶体管与一所述数据线电连接，所述第二电容经由所述第二晶体管与一所述数据线电连接，

其中，在所述第一晶体管被所述扫描线开启之后，所述第一电容与所述第一晶体管连接的一节点电压具有一准位变迁时间，所述准位变迁时间从所述节点的一充电状态到一放电状态，所述准位变迁时间大于等于一图框时间的二百分之一，并小于等于所述图框时间的二分之一。

10. 根据权利要求 9 所述的液晶显示装置，其特征在于，所述阻抗单元包含一晶体管元件，所述晶体管元件的栅极电连接于一共同电压。

## 液晶显示装置

### 技术领域

[0001] 本发明是关于一种显示装置,特别是关于一种液晶显示装置。

### 背景技术

[0002] 液晶显示(Liquid Crystal Display, LCD)装置以其耗电量低、发热量少、重量轻、以及非辐射性等等优点,已经被使用于各式各样的电子产品中,并且逐渐地取代传统的阴极射线管(Cathode Ray Tube, CRT)显示装置。

[0003] 一般而言,液晶显示装置主要包含一液晶显示面板(LCD Panel)以及一背光模块(Backlight Module)。其中,液晶显示面板主要具有一薄膜晶体管基板、一彩色滤光基板以及一夹设于两基板间的液晶层,且两基板与液晶层形成多个阵列设置的像素。背光模块可将一光源的光线均匀地分布到液晶显示面板,并经由各像素显示色彩而形成一图案。然而,由于各像素间的电压 - 穿透率曲线会随着使用者观看液晶显示面板的角度(例如正看及侧看)而有所不同,因此于不同视角观看显示面板时将会有色偏的现象产生。

[0004] 为改善色偏现象,已有多种现有技术研发出来,其中大多的技术是将单一像素分成一亮区及一暗区,通过此两区正看及侧看的电压 - 穿透率曲线不同,而具有相互补偿的效果,以达到低色偏(Low Color Shift, LCS)的目的。然而,为使暗区产生较暗的亮度,需要在各像素中设置一额外的晶体管元件作为开关,且需额外扫描线以控制此元件的作动,因而使像素的开口率降低,也增加制造成本。

[0005] 因此,如何提供一种液晶显示装置,能在改善色偏的同时,亦能使开口率提升并减少制造成本,实为当前重要课题之一。

### 发明内容

[0006] 有鉴于上述课题,本发明的目的为提供一种液晶显示装置,其能够改善色偏,同时使开口率提升并减少制造成本。

[0007] 为达上述目的,依据本发明的一种液晶显示装置包含多个像素、一扫描驱动电路以及一数据驱动电路。至少其中一像素具有一第一电容、一第二电容以及一补偿电容,第一电容经由一电阻元件与补偿电容电连接。扫描驱动电路经由多条扫描线驱动该等像素,其中一扫描线与一第一晶体管及一第二晶体管的栅极电连接。数据驱动电路经由多条数据线驱动该等像素,其中第一电容经由第一晶体管与一数据线电连接,第二电容经由第二晶体管与一数据线电连接。

[0008] 在一实施例中,第一电容或第二电容包含一液晶电容与一储存电容。

[0009] 在一实施例中,在第一晶体管被扫描线开启之后,第一电容与第一晶体管连接的一节点电压具有一准位变迁时间(level transition time),准位变迁时间从节点的一充电状态到一放电状态。准位变迁时间大于等于图框时间的二百分之一,并小于等于图框时间的二分之一。

[0010] 在一实施例中,电阻元件的阻抗值为 R,一图框时间为 T,第一电容的电容值为 C1,

补偿电容的电容值为 CT, 阻抗值 R 符合下列方程式 :

[0011]  $T/1400 < RC < T/14, C = (C1 * CT) / (C1 + CT)$ 。

[0012] 在一实施例中, 电阻元件的材质包含非晶硅、 $n^+$  非晶硅或其组合。

[0013] 为达上述目的, 依据本发明的一种液晶显示装置包含多个像素、一扫描驱动电路以及一数据驱动电路。至少其中一像素具有一第一电容、一第二电容以及一补偿电容, 第一电容经由一阻抗单元与补偿电容电连接。扫描驱动电路经由多条扫描线驱动该等像素, 其中一扫描线与一第一晶体管及一第二晶体管的栅极电连接。数据驱动电路经由多条数据线驱动该等像素, 其中第一电容经由第一晶体管与一数据线电连接, 第二电容经由第二晶体管与一数据线电连接。阻抗单元的阻抗值为 R, 一图框时间为 T, 第一电容的电容值为 C1, 补偿电容的电容值为 CT, 阻抗值 R 符合下列方程式 :

[0014]  $T/1400 < RC < T/14, C = (C1 * CT) / (C1 + CT)$ 。

[0015] 在一实施例中, 第一电容或第二电容包含一液晶电容与一储存电容。

[0016] 在一实施例中, 阻抗单元包含一电阻元件。

[0017] 在一实施例中, 阻抗单元包含一晶体管元件, 晶体管元件栅极电连接于一共同电压。

[0018] 在一实施例中, 在第一晶体管被扫描线开启之后, 第一电容与第一晶体管连接的一节点电压具有一准位变迁时间, 准位变迁时间从节点的一充电状态到一放电状态。准位变迁时间大于等于图框时间的二百分之一, 并小于等于图框时间的二分之一。

[0019] 在一实施例中, 阻抗单元的材质包含非晶硅、 $n^+$  非晶硅或其组合。

[0020] 为达上述目的, 依据本发明的一种液晶显示装置包含多个像素、一扫描驱动电路以及一数据驱动电路。至少其中一像素具有一第一电容、一第二电容以及一补偿电容, 第一电容经由一阻抗单元与补偿电容电连接。扫描驱动电路经由多条扫描线驱动该等像素, 其中一扫描线与一第一晶体管及一第二晶体管的栅极电连接。数据驱动电路经由多条数据线驱动该等像素, 其中第一电容经由第一晶体管与一数据线电连接, 第二电容经由第二晶体管与一数据线电连接。在第一晶体管被扫描线开启之后, 第一电容与第一晶体管连接的一节点电压具有一准位变迁时间 (level transition time), 准位变迁时间从节点的一充电状态到一放电状态。准位变迁时间大于等于一图框时间的二百分之一, 并小于等于图框时间的二分之一。

[0021] 在一实施例中, 第一电容或第二电容包含一液晶电容与一储存电容。

[0022] 在一实施例中, 阻抗单元包含一电阻元件。

[0023] 在一实施例中, 阻抗单元的阻抗值为 R, 图框时间为 T, 第一电容的电容值为 C1, 补偿电容的电容值为 CT, 阻抗值 R 符合下列方程式 :

[0024]  $T/1400 < RC < T/14, C = (C1 * CT) / (C1 + CT)$ 。

[0025] 在一实施例中, 阻抗单元包含一晶体管元件, 晶体管元件的栅极电连接于一共同电压。

[0026] 在一实施例中, 阻抗单元的材质包含非晶硅、 $n^+$  非晶硅或其组合。

[0027] 承上所述, 在本发明的液晶显示装置中, 用具有高阻抗值的阻抗单元代替现有技术的暗区的薄膜晶体管, 进而达到低色偏目的, 同时由于省略一晶体管元件, 而能提升开口率并减少制造成本。其中, 阻抗单元例如为一电阻元件, 其具有一高阻抗值, 在第一晶体管

被扫描线开启之后，电阻元件可避免补偿电容被充电，而当第一晶体管关闭时，第一电容放电于补偿电容而使亮度降低并形成暗区，藉以达到低色偏功效。换言之，第一电容与第一晶体管连接的一节点电压具有一准位变迁时间，准位变迁时间从节点的一充电状态到一放电状态，而当准位变迁时间大于等于一图框时间的二百分之一，并小于等于图框时间的二分之一时，会使低色偏的效果最佳。

### 附图说明

[0028] 为了更清楚地说明本发明实施例或现有技术中的技术方案，下面将对实施例描述中所需要使用的附图作简单地介绍，显而易见地，下面描述中的附图仅仅是本发明的一些实施例，对于本领域普通技术人员来讲，在不付出创造性劳动性的前提下，还可以根据这些附图获得其他的附图。

[0029] 图 1 为本发明较佳实施例的一种液晶显示装置的方块示意图；

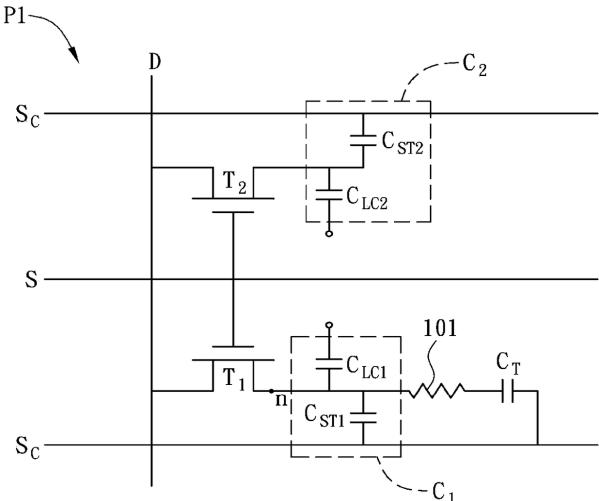

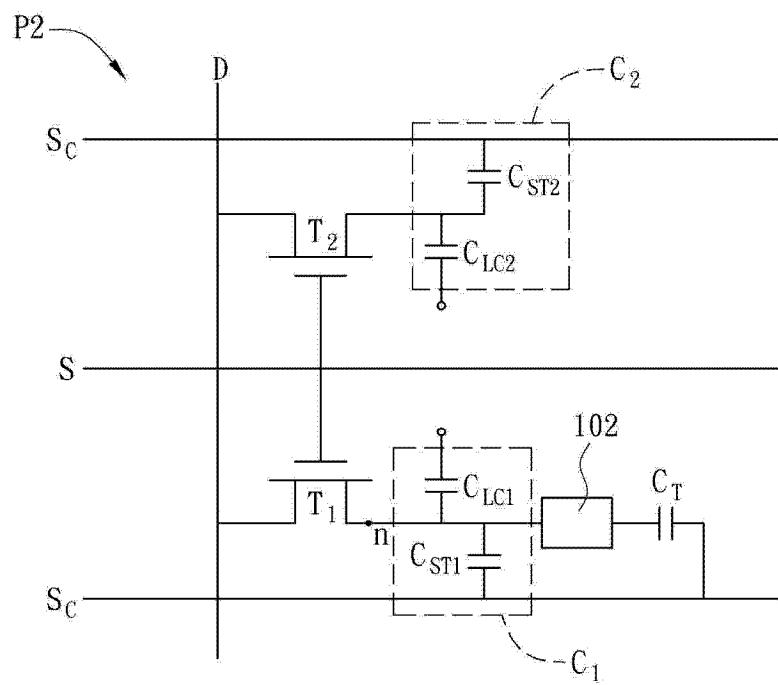

[0030] 图 2 为本发明第一实施例的一像素的电路示意图；

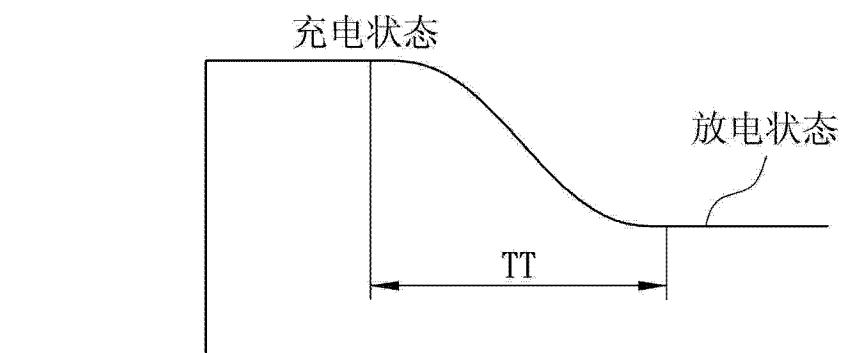

[0031] 图 3 为本发明较佳实施例的像素的一节点电压的示意图；

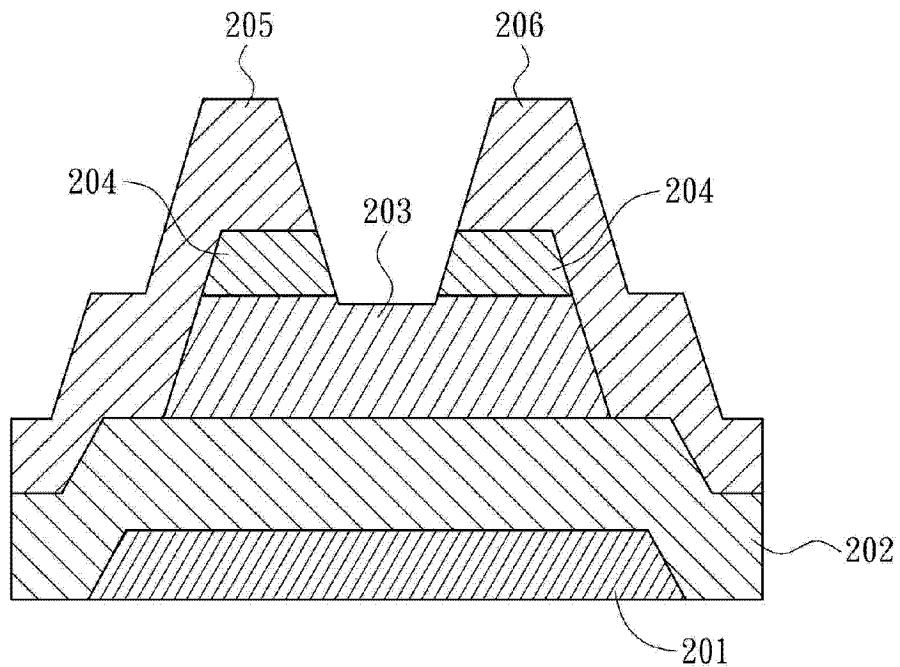

[0032] 图 4 为一般液晶显示面板的一薄膜晶体管的结构示意图；

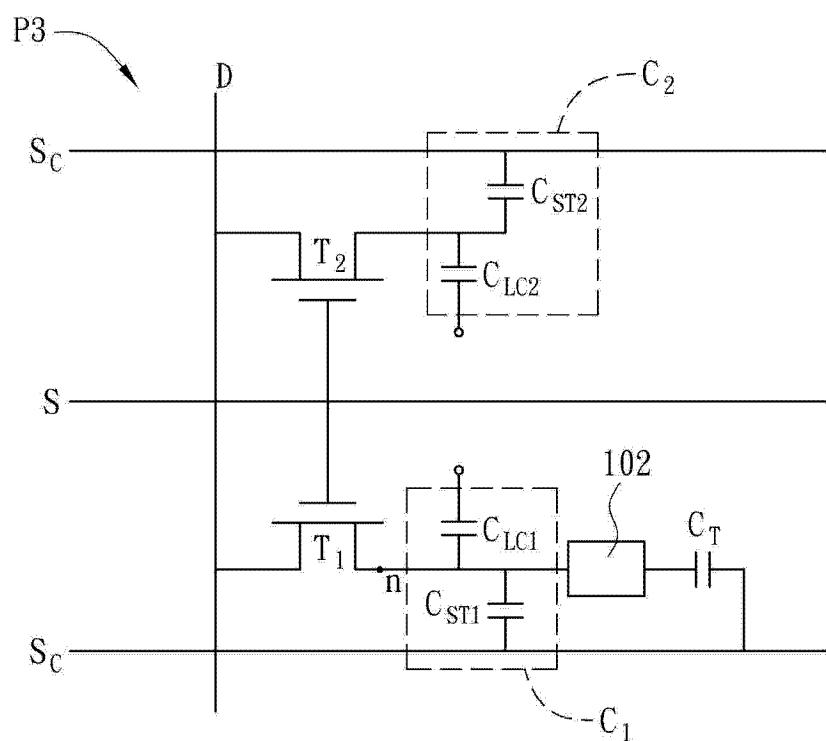

[0033] 图 5 为本发明第二实施例的一像素的电路示意图；以及

[0034] 图 6 为本发明第三实施例的一像素的电路示意图。

[0035] 附图标记

[0036] 1 : 液晶显示装置

[0037] 11 : 扫描驱动电路

[0038] 12 : 数据驱动电路

[0039] 101 : 电阻元件

[0040] 102 : 阻抗单元

[0041] 201 : 栅极层

[0042] 202 : 栅极绝缘层

[0043] 203 : 通道层

[0044] 204 : 掺杂层

[0045] 205 : 漏极层

[0046] 206 : 源极层

[0047] C<sub>1</sub> : 第一电容

[0048] C<sub>2</sub> : 第二电容

[0049] C<sub>T</sub> : 补偿电容

[0050] C<sub>LC1</sub>、C<sub>LC2</sub> : 液晶电容

[0051] C<sub>ST1</sub>、C<sub>ST2</sub> : 储存电容

[0052] D、D<sub>1~n</sub> : 数据线

[0053] n : 节点

[0054] P、P1、P2、P3 : 像素

[0055] S<sub>c</sub> : 信号线

[0056] S、S<sub>1~n</sub> : 扫描线

- [0057]  $T_1$  : 第一晶体管

- [0058]  $T_2$  : 第二晶体管

- [0059] TT : 准位变迁时间

## 具体实施方式

[0060] 以下将参照相关图式,说明依本发明较佳实施例的一种液晶显示装置,其中相同的元件将以相同的参照符号加以说明。

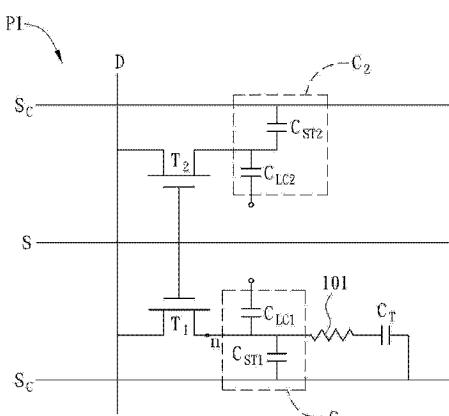

[0061] 图 1 为本发明较佳实施例的一种液晶显示装置 1 的方块示意图。液晶显示装置 1 包含多个像素 P、一扫描驱动电路 11 以及一数据驱动电路 12。像素 P 由液晶显示装置 1 的一液晶显示面板构成。一般而言,液晶显示面板具有一薄膜晶体管基板、一液晶层以及一彩色滤光基板,液晶层设置于薄膜晶体管基板与彩色滤光基板之间,并形成阵列设置的像素 P。在其他实施例中,液晶显示面板亦可有不同的变化态样,例如可将彩色滤光层设置于薄膜晶体管阵列的一侧(color filter on array, COA)、或将薄膜晶体管阵列设置于彩色滤光基板上(TFT on CF, 亦称为 TOC 或 array on CF)。另外,扫描驱动电路 11 通过多条扫描线  $S_{1 \sim n}$  驱动该等像素 P。数据驱动电路 12 通过多条数据线  $D_{1 \sim m}$  驱动该等像素 P。

[0062] 图 2 为本发明第一实施例的一像素 P1 的电路示意图,像素 P1 为该等像素 P 的其中之一。像素 P1 具有一第一电容  $C_1$ 、一第二电容  $C_2$  以及一补偿电容  $C_T$ ,第一电容  $C_1$  经由一电阻元件 101 与补偿电容  $C_T$  电连接。一扫描线 S 与一第一晶体管  $T_1$  及一第二晶体管  $T_2$  的栅极电连接。一数据线 D 分别经由第一晶体管  $T_1$  及第二晶体管  $T_2$  与第一电容  $C_1$  及第二电容  $C_2$  电连接。

[0063] 在本实施例中,像素 P1 具有一亮区及一暗区而达到低色偏功效。当扫描线 S 开启第一晶体管  $T_1$  与第二晶体管  $T_2$  时,数据线 D 经由第一晶体管  $T_1$  与第二晶体管  $T_2$  写入数据信号至第一电容  $C_1$  及第二电容  $C_2$  而进行充电,并使得第二电容  $C_2$  对应亮区。在本实施例中,第一电容  $C_1$  与第二电容  $C_2$  各包含一液晶电容  $C_{LC1}、C_{LC2}$  与一储存电容  $C_{ST1}、C_{ST2}$ ,液晶电容  $C_{LC1}、C_{LC2}$  的一端接收数据信号的电压,另一端接收一共同电压(来自共同电极侧)。储存电容  $C_{ST1}、C_{ST2}$  的一端接收数据信号的电压,另一端接收一共同电压(例如来自传送共同电压的一信号线  $S_C$ )。当扫描线 S 关闭第一晶体管  $T_1$  与第二晶体管  $T_2$  时,第一电容  $C_1$  开始向补偿电容  $C_T$  放电,而使得第一电容  $C_1$  与补偿电容  $C_T$  对应一暗区。

[0064] 当电阻元件 101 的阻抗值太小时,第一电容  $C_1$  放电于补偿电容  $C_T$  的速度较快,且在充电时,补偿电容  $C_T$  亦会被充电;当电阻元件 101 的阻抗值太大时,第一电容  $C_1$  放电于补偿电容  $C_T$  的速度会过低。上述两种情形皆不利达到低色偏功效。因此,电阻元件 101 的阻抗值实具有一较佳范围,在本实施例中,电阻元件 101 的阻抗值为 R,一图框时间为 T,第一电容的电容值为 C1,补偿电容的电容值为 CT,阻抗值 R 符合下列方程式:

$$T/1400 < RC < T/14, C = (C1 * CT) / (C1 + CT)。$$

[0066] 此外,当数据线 D 写入数据信号至第一电容  $C_1$  及第二电容  $C_2$  而进行充电时,第一电容  $C_1$  与第一晶体管  $T_1$  连接的一节点 n 电压达到一充电状态,而当第一电容  $C_1$  放电于补偿电容  $C_T$  至平衡时,节点 n 电压达到一放电状态。图 3 为节点 n 电压的示意图,从充电状态至放电状态具有一准位变迁时间(level transition time) TT,准位变迁时间 TT 大于等于图框时间的二百分之一,并小于等于图框时间的二分之一。通过上述设计,电阻元件 101

的功用相当于一开关元件。

[0067] 另外,本实施例的电阻元件 101 的材质可包含非晶硅、n<sup>+</sup> 非晶硅或其组合。在制作工艺中,电阻元件 101 可与薄膜晶体管的制造一并形成。图 4 为一般液晶显示面板的一薄膜晶体管的结构示意图,其主要包含一栅极层 201、一栅极绝缘层 202、一通道层 203、一掺杂层 204、以及一漏极层 205 与一源极层 206。通道层 203 的材质为非晶硅(a-Si),掺杂层 204 的材质为 n<sup>+</sup> 非晶硅,其是由非晶硅掺杂高浓度磷(Ph<sub>3</sub>)而形成。电阻元件 101 可由非晶硅制成,在制作工艺中可于制作通道层 203 时一并制成。在此情况下,电阻元件 101 在受到光线(例如由背光模块发出)照射时,可具有适当的高阻抗值。另外,电阻元件 101 可由 n<sup>+</sup> 非晶硅制成,在制作工艺中可于制作掺杂层 204 时一并制成。在此情况下,电阻元件 101 受光照可具有适当的高阻抗值。当然,电阻元件 101 亦可由非晶硅与 n<sup>+</sup> 非晶硅共同制成。

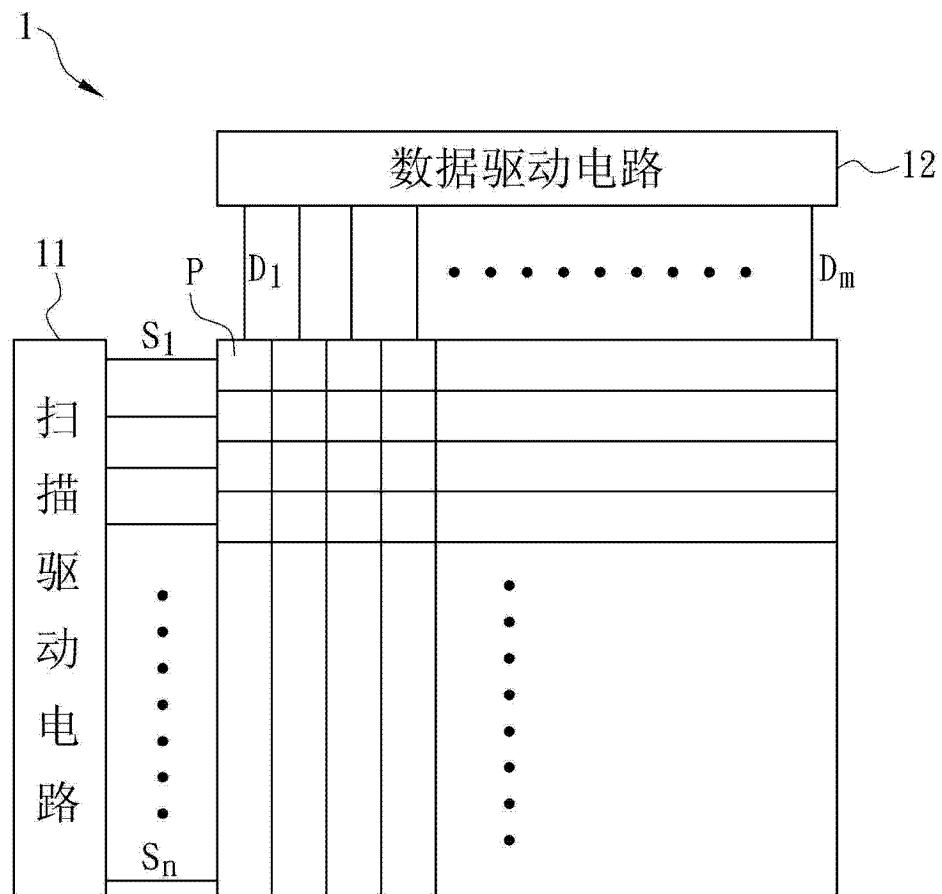

[0068] 图 5 为本发明第二实施例的一像素 P2 的电路示意图,像素 P2 为该等像素 P 的其中之一。像素 P2 具有一第一电容 C<sub>1</sub>、一第二电容 C<sub>2</sub> 以及一补偿电容 C<sub>T</sub>,第一电容 C<sub>1</sub> 经由一阻抗单元 102 与补偿电容 C<sub>T</sub> 电连接。一扫描线 S 与一第一晶体管 T<sub>1</sub> 及一第二晶体管 T<sub>2</sub> 的栅极电连接。一数据线 D 分别经由第一晶体管 T<sub>1</sub> 及第二晶体管 T<sub>2</sub> 与第一电容 C<sub>1</sub> 及第二电容 C<sub>2</sub> 电连接。

[0069] 在本实施例中,像素 P2 具有一亮区及一暗区而达到低色偏功效。当扫描线 S 开启第一晶体管 T<sub>1</sub> 与第二晶体管 T<sub>2</sub> 时,数据线 D 经由第一晶体管 T<sub>1</sub> 与第二晶体管 T<sub>2</sub> 写入数据信号至第一电容 C<sub>1</sub> 及第二电容 C<sub>2</sub> 而进行充电。在本实施例中,第一电容 C<sub>1</sub> 与第二电容 C<sub>2</sub> 各包含一液晶电容 C<sub>LC1</sub>、C<sub>LC2</sub> 与一储存电容 C<sub>ST1</sub>、C<sub>ST2</sub>,液晶电容 C<sub>LC1</sub>、C<sub>LC2</sub> 的一端接收数据信号的电压,另一端接收一共同电压(来自共同电极侧)。储存电容 C<sub>ST1</sub>、C<sub>ST2</sub> 的一端接收数据信号的电压,另一端接收一共同电压(例如来自具有共同电压的一信号线 S<sub>C</sub>)。当扫描线 S 关闭第一晶体管 T<sub>1</sub> 与第二晶体管 T<sub>2</sub> 时,第一电容 C<sub>1</sub> 开始向补偿电容 C<sub>T</sub> 放电,而形成一暗区。

[0070] 阻抗单元 102 的阻抗值为 R,一图框时间为 T,第一电容的电容值为 C<sub>1</sub>,补偿电容的电容值为 C<sub>T</sub>,阻抗值 R 符合下列方程式:

$$[0071] T/1400 < RC < T/14, C = (C_1 * C_T) / (C_1 + C_T)。$$

[0072] 通过上述设计,阻抗单元 102 的功用相当于一开关元件,并可产生较佳的低色偏功效。

[0073] 此外,当数据线 D 写入数据信号至第一电容 C<sub>1</sub> 及第二电容 C<sub>2</sub> 而进行充电时,第一电容 C<sub>1</sub> 与第一晶体管 T<sub>1</sub> 连接的一节点 n 电压达到一充电状态,而当第一电容 C<sub>1</sub> 放电于补偿电容 C<sub>T</sub> 至平衡时,节点 n 电压达到一放电状态。请参照图 3,从充电状态至放电状态具有一准位变迁时间 TT,准位变迁时间 TT 大于等于图框时间的二百分之一,并小于等于图框时间的二分之一。

[0074] 另外,本实施例的阻抗单元 102 的材质可包含非晶硅、n<sup>+</sup> 非晶硅或其组合。由于此技术特征已于上详述,故于此不再赘述。本实施例的阻抗单元 102 可包含至少一电阻元件。

[0075] 另外,在其他实施例中,阻抗单元 102 可包含一晶体管元件,晶体管元件的栅极电连接于一共同电压。如此节点 n 的电压亦可如图 3 所示,并据此带来较佳低色偏的功效。

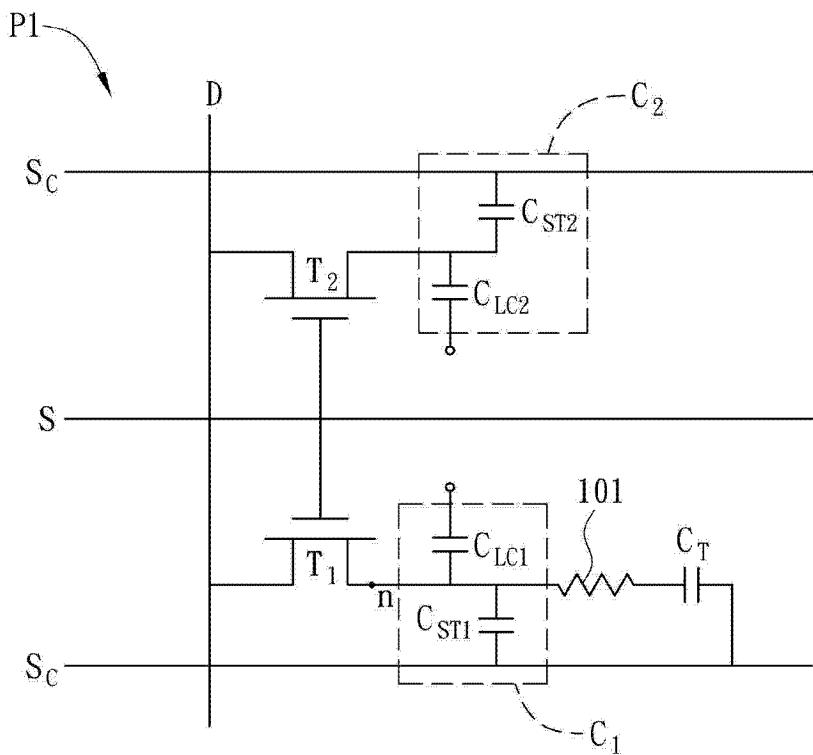

[0076] 图 6 为本发明第三实施例的一像素 P3 的电路示意图,像素 P3 为该等像素 P 的其中之一。像素 P3 具有一第一电容 C<sub>1</sub>、一第二电容 C<sub>2</sub> 以及一补偿电容 C<sub>T</sub>,第一电容 C<sub>1</sub> 经由一阻抗单元 102 与补偿电容 C<sub>T</sub> 电连接。一扫描线 S 与一第一晶体管 T<sub>1</sub> 及一第二晶体管 T<sub>2</sub> 的

栅极电连接。一数据线 D 分别经由第一晶体管  $T_1$  及第二晶体管  $T_2$  与第一电容  $C_1$  及第二电容  $C_2$  电连接。

[0077] 在本实施例中,像素 P3 具有一亮区及一暗区而达到低色偏功效。当扫描线 S 开启第一晶体管  $T_1$  与第二晶体管  $T_2$  时,数据线 D 经由第一晶体管  $T_1$  与第二晶体管  $T_2$  写入数据信号至第一电容  $C_1$  及第二电容  $C_2$  而进行充电。在本实施例中,第一电容  $C_1$  与第二电容  $C_2$  各包含一液晶电容  $C_{LC1}$ 、 $C_{LC2}$  与一储存电容  $C_{ST1}$ 、 $C_{ST2}$ ,液晶电容  $C_{LC1}$ 、 $C_{LC2}$  的一端接收数据信号的电压,另一端接收一共同电压(来自共同电极侧)。储存电容  $C_{ST1}$ 、 $C_{ST2}$  的一端接收数据信号的电压,另一端接收一共同电压(例如来自具有共同电压的一信号线  $S_c$ )。当扫描线 S 关闭第一晶体管  $T_1$  与第二晶体管  $T_2$  时,第一电容  $C_1$  开始向补偿电容  $C_T$  放电,而形成一暗区。

[0078] 当数据线 D 写入数据信号至第一电容  $C_1$  及第二电容  $C_2$  而进行充电时,第一电容与第一晶体管连接的一节点 n 电压达到一充电状态,而当第一电容  $C_1$  放电于补偿电容  $C_T$  至平衡时,节点 n 电压达到一放电状态。请参照图 3,从充电状态至放电状态具有一准位变迁时间 TT,准位变迁时间 TT 大于等于图框时间的二百分之一,并小于等于图框时间的二分之一。通过上述设计,阻抗单元 102 的功用相当于一开关元件,并可产生较佳的充、放电效果以及低色偏功效。

[0079] 阻抗单元 102 的阻抗值为 R,一图框时间为 T,第一电容的电容值为 C1,补偿电容的电容值为 CT,阻抗值 R 符合下列方程式 :

$$[0080] T/1400 < RC < T/14, C = (C1 * CT) / (C1 + CT) .$$

[0081] 通过上述设计,阻抗单元 102 可产生较佳的低色偏功效。

[0082] 另外,本实施例的阻抗单元 102 的材质可包含非晶硅、 $n^+$  非晶硅或其组合。由于此技术特征已于上详述,故于此不再赘述。本实施例的阻抗单元 102 可包含一电阻元件。

[0083] 另外,在其他实施例中,阻抗单元 102 可包含一晶体管元件,且晶体管元件的栅极电连接于一共同电压。如此节点 n 的电压亦可如图 3 所示,并据此带来较佳低色偏的功效。

[0084] 综上所述,在本发明的液晶显示装置中,用具有高阻抗值的阻抗单元代替现有技术的暗区的薄膜晶体管及控制此晶体管的扫描线,进而达到低色偏目的,同时由于省略一晶体管元件,而能提升开口率并减少制造成本。其中,阻抗单元例如为一电阻元件,其具有一高阻抗值,在第一晶体管被扫描线开启之后,电阻元件可避免补偿电容被充电,而当第一晶体管关闭时,第一电容放电于补偿电容而使亮度降低并形成暗区,藉以达到低色偏功效。换言之,第一电容与第一晶体管连接的一节点电压具有一准位变迁时间,准位变迁时间从节点的一充电状态到一放电状态,而当准位变迁时间大于等于一图框时间的二百分之一,并小于等于图框时间的二分之一时,会使低色偏的效果最佳。

[0085] 以上所述仅为举例性,而非为限制性者。任何未脱离本发明的精神与范畴,而对其进行的等效修改或变更,均应包含于权利要求书所保护的范围中。

图 1

图 2

图 3

图 4

图 5

图 6

|                |                                                   |         |            |

|----------------|---------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置                                            |         |            |

| 公开(公告)号        | <a href="#">CN103777419A</a>                      | 公开(公告)日 | 2014-05-07 |

| 申请号            | CN201210410154.9                                  | 申请日     | 2012-10-24 |

| [标]申请(专利权)人(译) | 群康科技(深圳)有限公司<br>群创光电股份有限公司                        |         |            |

| 申请(专利权)人(译)    | 群康科技(深圳)有限公司<br>奇美电子股份有限公司                        |         |            |

| 当前申请(专利权)人(译)  | 群康科技(深圳)有限公司<br>奇美电子股份有限公司                        |         |            |

| [标]发明人         | 谢耀联<br>欧阳祥睿<br>黄钰胜<br>吴青龙                         |         |            |

| 发明人            | 谢耀联<br>欧阳祥睿<br>黄钰胜<br>吴青龙                         |         |            |

| IPC分类号         | G02F1/1362 G02F1/1368 G02F1/133 G09G3/36 G09G3/34 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>    |         |            |

## 摘要(译)

本发明提供一种液晶显示装置包含多个像素、一扫描驱动电路以及一数据驱动电路。至少其中一像素具有一第一电容、一第二电容以及一补偿电容，第一电容经由一电阻元件与补偿电容电连接。扫描驱动电路经由多条扫描线驱动该等像素。一扫描线与一第一晶体管及一第二晶体管的栅极电连接。数据驱动电路经由多条数据线驱动该等像素。第一电容经由该第一晶体管与该一数据线电连接，第二电容经由第二晶体管与一数据线电连接。通过本发明的液晶显示装置，能够在改善色偏的同时，亦能使开口率提升并减少制造成本。