# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 110223649 A (43)申请公布日 2019.09.10

(21)申请号 201910408790.X

(22)申请日 2019.05.16

(71)申请人 深圳市华星光电技术有限公司 地址 518132 广东省深圳市光明新区塘明 大道9-2号

(72)发明人 陈帅

(74)专利代理机构 深圳翼盛智成知识产权事务 所(普通合伙) 44300

代理人 黄威

(51) Int.CI.

**G09G** 3/36(2006.01)

权利要求书2页 说明书5页 附图4页

### (54)发明名称

GOA电路及液晶显示器

#### (57)摘要

本发明提供一种GOA电路及液晶显示器,其中,GOA电路包括2N个GOA单元,所述2N个GOA单元中第N级GOA单元与第N+1级GOA单元共用同一个下拉维持电路,N为正整数。通过共用一个下拉维持电路,减少了GOA电路中电路的数量,从而节省了GOA电路在液晶显示器上所占据的空间,且同时提高了TFT器件中电路的使用效率,有利于液晶显示器的窄边框设计。

- 1.一种GOA电路,用于液晶显示器,其特征在于,所述GOA电路包括2N个GOA单元,所述2N个GOA单元中第N级GOA单元与第N+1级GOA单元共用同一个下拉维持电路,其中,N为正整数。

- 2.根据权利要求1所述的GOA电路,其特征在于,所述第N级GOA单元依次对显示区域的第N级水平扫描线充电,所述第N级GOA单元包括上拉控制电路、上拉电路、下传电路、下拉电路和时钟信号线;

其中,所述N级上拉控制电路与所述N+1级上拉控制电路采用相同的控制信号。

3.根据权利要求2所述的GOA电路,其特征在于,所述上拉控制电路包括第一薄膜晶体管(T11),所述第一薄膜晶体管(T11)的栅极用以接受第N+M级的GOA单元的触发信号,第一薄膜晶体管(T11)的源极与所述下传电路连接;

其中,M大于或等于2,N大于4。

- 4.根据权利要求3所述的GOA电路,其特征在于,所述信号下传电路包括第二薄膜晶体管(T22),所述第二薄膜晶体管(T22)的栅极与所述第一薄膜晶体管(T11)的源极连接,所述第二薄膜晶体管(T22)的漏极与时钟信号线连接,所述第二薄膜晶体管(T22)的源极与所述下拉单元连接,所述信号下传电路用以控制下一级GOA单元中信号的打开和关闭。

- 5.根据权利要求2所述的GOA电路,其特征在于,所述上拉电路包括第三薄膜晶体管 (T21),所述第三薄膜晶体管 (T21)的漏极与当前信号下传电路所属的GOA单元同级的扫描 线连接。

- 6.根据权利要求2所述的GOA电路,其特征在于,所述信号下拉电路包括第四薄膜晶体管 (T41) 和第五薄膜晶体管 (T31),所述第四薄膜晶体管 (T41)的栅极与所述第五薄膜晶体管 (T31)的栅极连接,所述第四薄膜晶体管 (T41)的漏极与所述第二薄膜晶体管 (T22)的栅极连接,所述第四薄膜晶体管 (T41)的源极与当前信号下拉电路所属的GOA单元同级的下拉信号线连接,所述第五薄膜晶体管 (T31)的栅极与所述第四薄膜晶体管 (T41)的栅极连接,所述第五薄膜晶体管 (T31)的漏极与当前GOA电路中的扫描线连接,所述第五薄膜晶体管 (T31)的源极与所述当前信号下拉电路所属的GOA单元同级的下拉信号线连接。

- 7.根据权利要求1所述的GOA电路,其特征在于,所述下拉维持电路包括第六薄膜晶体管(T51)、第七薄膜晶体管(T52)、第八薄膜晶体管(T53)和第九薄膜晶体管(T54);所述第六薄膜晶体管(T51)的栅极与第六薄膜晶体管(T51)的漏极连接高电平信号所述第六薄膜晶体管(T51)的源极与所述第七薄膜晶体管(T52)的漏极连接;所述第七薄膜晶体管(T52)的源极与当前信号下拉电路所属的GOA单元同级的下拉信号线连接;所述第七薄膜晶体管(T52)的栅极和第一薄膜晶体管(T11)漏极相连接。

- 8.根据权利要求7所述的GOA电路,其特征在于,所述第八薄膜晶体管(T53)的栅极与所述第六薄膜晶体管(T51)的源极连接,所述第八薄膜晶体管(T53)的源极与所述第九薄膜晶体管(T54)的漏极相连接,所述第八薄膜晶体管(T53)的漏极与所述第六薄膜晶体管(T51)的漏极相连接,所述第九薄膜晶体管(T54)的栅极与所述第一薄膜晶体管(T11)的漏极连接,所述第九薄膜晶体管(T54)的源极与当前信号下拉电路所属的GOA单元同级的下拉信号线连接。

- 9.根据权利要求2所述的GOA电路,其特征在于,所述GOA单元还包括自举电容电路,所述自举电容电路的一端为第一节点,所述自举电容电路通过所述第一节点与第一薄膜晶体管(T11)的源极连接,所述自举电容电路用以维持当前GOA单元中栅极信号点的电位。

10.一种液晶显示器,其特征在于,所述液晶显示器包括如权利要求1-9任一项所述的 GOA电路。

# GOA电,路及液晶显示器

#### 技术领域

[0001] 本发明涉及显示技术领域,尤其涉及一种GOA电路及液晶显示器。

## 背景技术

[0002] 随着薄膜晶体管 (Thin Film Transistor, TFT) 性能的提升,数组基板行扫描驱动 (Gate Driver On Array, GOA) 技术是利用薄膜晶体管液晶显示器Array制程,将Gate行扫描驱动信号制作在Array基板上,实现对Gate逐行扫描的驱动方式的一项技术,目前已经普遍应用于我们的面板中,GOA技术具有很多的优点,可以提升产品良率,实现无边框设计等。 [0003] 随着市场对产品要求的不断提高,大尺寸、高分辨率、高刷新频率的液晶面板成为各大厂商竞相发展的目标,随着窄边框设计的日益流行,面板设计的周边空间被逐渐压缩,在传统的GOA电路设计中,每一级GOA电路的布线空间高度h和对应的像素尺寸是一致的,现在4k或者更高分辨率 (pixel per inch, PPI) 产品的逐渐普及,像素的尺寸越来越小,留给GOA电路进行布线的空间高度也随之减小,由于高度受到限制,在布线时只能用更大的宽度来进行弥补,且GOA电路本身的尺寸也越来越大,功能越来越复杂导致边框变得越来越宽,对窄边框的设计非常不利。

## 发明内容

[0004] 本发明实施例提供一种GOA电路及液晶显示器,通过将GOA电路中相邻两级之间的GOA单元设置为共用同一个下拉维持电路,减少了GOA电路中电路的数量,节省了GOA电路所占据的空间,且同时提高了TFT器件中电路的使用效率,有利于液晶显示器的窄边框设计。

[0005] 为了解决上述问题,第一方面,本申请提供一种GOA电路,用于液晶显示器,该GOA电路包括2N个GOA单元,所述2N个GOA单元中第N级GOA单元与第N+1级GOA单元共用同一个下拉维持电路,其中,N为正整数。

[0006] 进一步的,该第N级GOA单元依次对显示区域的第N级水平扫描线充电,所述第N级GOA单元包括上拉控制电路、上拉电路、下传电路、下拉电路和时钟信号线:

[0007] 其中,所述N级上拉控制电路与所述N+1级上拉控制电路采用相同的控制信号。

[0008] 进一步的,该上拉控制电路包括第一薄膜晶体管T11,所述第一薄膜晶体管T11的 栅极用以接受第N-4级的G0A单元的触发信号,第一薄膜晶体管T11的源极与所述下传电路连接;

[0009] 其中,M大于或等于2,N大于4。

[0010] 进一步的,该信号下传电路包括第二薄膜晶体管T22,所述第二薄膜晶体管T22的栅极与所述第一薄膜晶体管T11的源极连接,所述第二薄膜晶体管T22的漏极与时钟信号线连接,所述第二薄膜晶体管T22的源极与所述下拉单元连接,所述信号下传电路用以控制下一级GOA单元中信号的打开和关闭。

[0011] 进一步的,该上拉电路包括第三薄膜晶体管T21,所述第三薄膜晶体管T21的漏极与当前信号下传电路所属的GOA单元同级的扫描线连接。

[0012] 进一步的,该信号下拉电路包括第四薄膜晶体管T41和第五薄膜晶体管T31,所述第四薄膜晶体管T41的栅极与所述第五薄膜晶体管T31的栅极连接,所述第四薄膜晶体管T41的漏极与所述第二薄膜晶体管T22的栅极连接,所述第四薄膜晶体管T41的源极与当前信号下拉电路所属的G0A单元同级的下拉信号线连接,所述第五薄膜晶体管T31的栅极与所述第四薄膜晶体管T41的栅极连接,所述第五薄膜晶体管T31的漏极与当前G0A电路中的扫描线连接,所述第五薄膜晶体管T31的源极与当前信号下拉电路所属的G0A单元同级的下拉信号线连接。

[0013] 进一步的,该下拉维持电路包括第六薄膜晶体管T51、第七薄膜晶体管T52、第八薄膜晶体管T53和第九薄膜晶体管T54;所述第六薄膜晶体管T51的栅极与第六薄膜晶体管T51的漏极连接高电平信号所述第六薄膜晶体管T51的源极与所述第七薄膜晶体管T52的漏极连接;所述第七薄膜晶体管T52的源极与当前信号下拉电路所属的G0A单元同级的下拉信号线连接;所述第七薄膜晶体管T52的栅极和第一薄膜晶体管T11漏极相连接。

[0014] 进一步的,该第八薄膜晶体管T53的栅极与所述第六薄膜晶体管T51的源极连接,所述第八薄膜晶体管T53的源极与所述第九薄膜晶体管T54的漏极相连接,所述第八薄膜晶体管T53的漏极与所述第六薄膜晶体管T51的漏极相连接;所述第九薄膜晶体管T54的栅极与所述第一薄膜晶体管T11的漏极连接,所述第九薄膜晶体管T54的源极与当前信号下拉电路所属的G0A单元同级的下拉信号线连接。

[0015] 进一步的,该GOA单元还包括自举电容电路,所述自举电容电路的一端为第一节点,所述自举电容电路通过所述第一节点与第一薄膜晶体管T11的源极连接所述自举电容电路用以维持当前GOA单元中栅极信号点的电位。

[0016] 第二方面,本发明还申请一种液晶显示器,所述液晶显示器包括如上任一项所述的GOA电路。

#### 附图说明

[0017] 为了更清楚地说明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单介绍,显而易见地,下面描述中的附图仅仅是发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

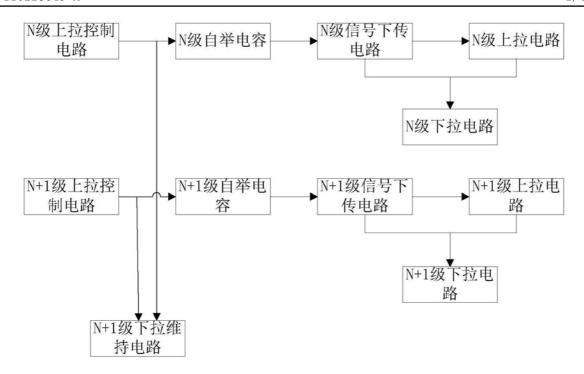

[0018] 图1为本发明所提供的一种GOA电路中各个电路的连接关系一实施例示意图:

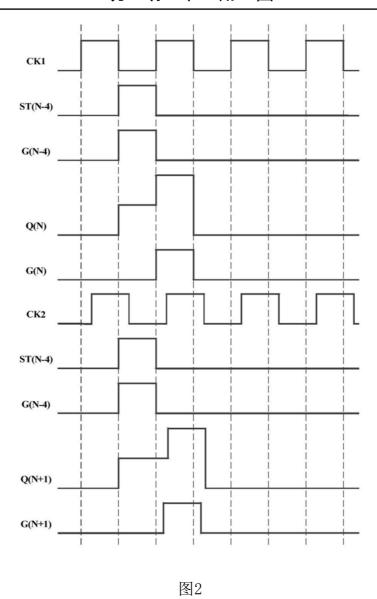

[0019] 图2为本发明提供的一种GOA电路中各个位置的一实施例波形图;

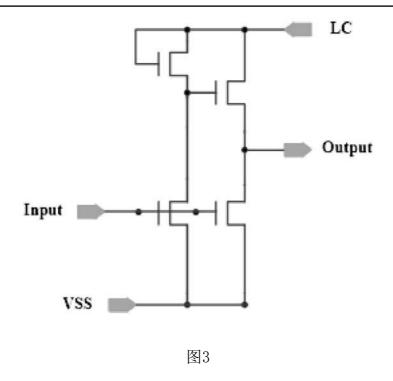

[0020] 图3为本发明提供的一种下拉维持电路的一实施例示意图:

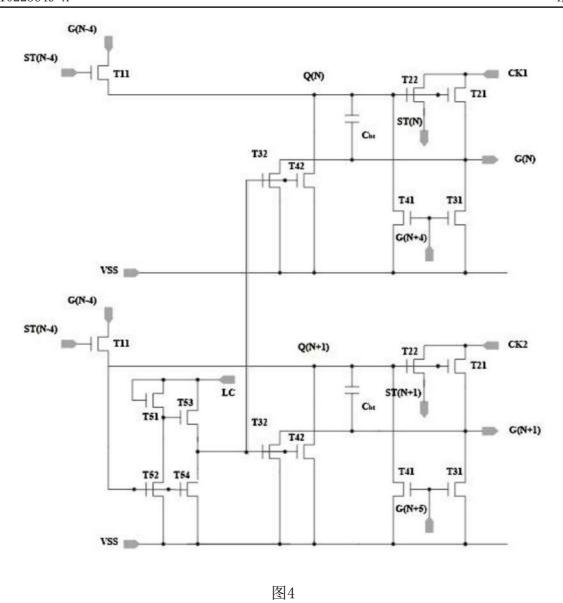

[0021] 图4为本发明提供的GOA电路中元器件的具体连接关系图。

### 具体实施方式

[0022] 以下各实施例的说明是参考附加的图示,用以例示本发明可用以实施的特定实施例。本发明所提到的方向用语,例如[上]、[下]、[前]、[后]、[左]、[右]、[内]、[外]、[侧面]等,仅是参考附加图式的方向。因此,使用的方向用语是用以说明及理解本发明,而非用以限制本发明。在图中,结构相似的单元是用以相同标号表示。

[0023] 附图和说明被认为在本质上是示出性的,而不是限制性的。在图中,结构相似的单

元是用以相同标号表示。另外,为了理解和便于描述,附图中示出的每个组件的尺寸和厚度都是任意示出的,但是本发明不限于此。

[0024] 在附图中,为了清晰起见,夸大了层、膜、面板、区域等的厚度。在附图中,为了理解方便和便于描述,夸大了一些层和区域的厚度。需要说明的是,当例如层、膜、区域或基底的组件被称作"在"另一组件"上"时。所述组件可以直接在所述另一组件上,或者也可以存在中间组件。

[0025] 另外,在说明书中,除非明确地描述为相反的,否则词语"包括"将被理解为意指包括所述组件,但是不排除任何其他组件。此外在说明书中,"在……上"意指位于目标组件上方或者下方,而不意指必须位于基于重力方向的顶部上。

[0026] 为更进一步阐述本发明为达成预定发明所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本发明提出的GOA电路及液晶显示器,其具体实施方式、结构、特征及其功效,详细说明如下。

[0027] 请参阅图1,为本发明所提供的一种GOA电路中各个电路的连接关系一实施例示意图,下面以第N级GOA单元和第N+1级GOA单元为例,该GOA电路可以包括:N级上拉控制电路、N级上拉电路、N级下传电路、N级下拉电路、N级自举电容和N+1上拉控制电路、N+1级上拉电路、N+1级下传电路、N+1级下拉电路、N+1级下拉维持电路、N+1级自举电容。

[0028] 其中,N级上拉电路及下拉维持电路分别与第N级栅极信号点Q(N)和第N级水平扫描线G(N)连接,N级上拉控制电路、N级下拉电路与第N级栅极信号点Q(N)连接。

[0029] N+1级上拉电路及下拉维持电路分别与第N+1级栅极信号点Q(N+1)和第N+1级水平扫描线G(N+1)连接,N+1级上拉控制电路、N+1级下拉电路与第N+1级栅极信号点Q(N+1)连接。

[0030] 下拉维持电路在第N级水平扫描线G(N) 充电后维持第N级栅极信号点Q(N) 及第N级水平扫描线G(N) 的电位至低电位,在第N+1级水平扫描线G(N+1) 充电后维持第N+1级栅极信号点Q(N+1) 及第N级水平扫描线G(N+1) 的电位至低电位。

[0031] 具体地,N级上拉控制电路在接收信号后抬高第N级栅极信号点Q(N)的电位值高电位并控制N级上拉电路打开,接收N级时钟信号CK(N)从而对第N级水平扫描线G(N)充电,充电完成后,N级下拉电路下拉第N级栅极信号点Q(N)的电位至低电位,同时关闭N级上拉电路,下拉维持电路下拉并维持第N级栅极信号点Q(N)和第N级水平扫描线G(N)的电位至低电位并维持低电位。

[0032] 两级电路的工作期间,下拉维持电路在第一时钟信号CK1和第二时钟信号CK2的控制下同时下拉两级电路的电位至低电位并维持低电位。

[0033] 参阅图2为本发明所提供的一种GOA电路中各个位置的一实施例波形图。

[0034] 在本发明一实施例中,由于第N级和第N+1级的上拉控制单元采用相同的控制信号,均为ST (N-4)和G (N-4),因此Q (N)点和Q (N+1)点第一阶段的充电是同一时间开始的,但由于时钟信号的差异,第二充电阶段却是不同时间完成的。

[0035] 区别于现有技术,本实施方式通过将相邻的两级GOA单元进行耦合,使两级GOA单元共用同一个下拉维持电路,该下拉维持电路在第一级GOA电路充电完后维持第一级GOA电路至低电位,在第二级GOA电路充电完后维持第二级GOA电路至低电位。采用这样的方式可以减少GOA电路中的电路数量,从而节省GOA电路所占据的空间,有利于液晶显示器的窄边

框设计。

[0036] 在本发明的一些实施例中,共用同一个下拉维持电路的GOA单元也可以为相邻的两个或多个下拉维持电路。例如,共用同一个下拉维持电路的GOA单元可以为第一级、第二级、第二级、第二级、第三级等多 个GOA单元。或者,共用同一个下拉维持电路的GOA单元可以为第一级、第二级、第三级等多个GOA单元。

[0037] 在本发明的一些其他实施例中,共用同一个下拉维持电路的GOA单元也可以为并不相邻的两个或多个GOA单元。例如,共用同一个下拉维持电路的GOA单元可以为第一级、第三级GOA单元。或者,共用同一个下拉维持电路的GOA单元可以为第一级、第三级、第五级GOA单元。

[0038] 参阅图3,在本发明的一些实施例中,该下拉维持电路可以为一种反相器,其中,LC 端为高电平信号,VSS端为低电平信号,当Input端输入高电位信号时,Output端输出低电位信号,当Input端输入低电位信号时,Output端输出高电位信号。

[0039] 请参阅图4为本发明所提供的GOA电路中元器件的具体连接关系图。其中,上拉控制电路包括第一薄膜晶体管T11,第一薄膜晶体管T11的栅极接收控制信号,第一薄膜晶体管T11的源极与所述下传电路连接。

[0040] 优选的,本发明一实施例中,第一薄膜晶体管T11的栅极可以接收来自第N-4级G0A单元触发的信号,N大于4。

[0041] 在本发明的一些实施例中,信号下传电路可以包括第二薄膜晶体管T22,所述第二薄膜晶体管T22的栅极与所述第一薄膜晶体管T11的源极连接,所述第二薄膜晶体管T22的漏极与时钟信号线连接,所述第二薄膜晶体管T22的源极与所述下拉单元连接,所述信号下传电路用以控制下一级G0A单元中信号的打开和关闭。

[0042] 该上拉电路可以包括第三薄膜晶体管T21,所述第三薄膜晶体管T21的漏极与当前信号下传电路所属的G0A单元同级的扫描线连接。第三薄膜晶体管T21的源极与当前下拉电路所属的G0A单元同级的时钟信号线连接。

[0043] 在本发明的一些其他实施例中,所述信号下拉电路可以包括第四薄膜晶体管T41和第五薄膜晶体管T31,所述第四薄膜晶体管T41的栅极与所述第五薄膜晶体管T31的栅极连接,所述第四薄膜晶体管T41的漏极与所述第二薄膜晶体管T22的栅极连接,所述第四薄膜晶体管T41的源极与当前信号下拉电路所属的G0A单元同级的下拉信号线连接,所述第五薄膜晶体管T31的栅极与所述第四薄膜晶体管T41的栅极连接,所述第五薄膜晶体管T31的漏极与当前G0A电路中的扫描线连接,所述第五薄膜晶体管T31的源极与当前信号下拉电路所属的G0A单元同级的下拉信号线连接。

[0044] 优选的,在本发明的一些实施例中,所述下拉维持电路可以包括第六薄膜晶体管T51、第七薄膜晶体管T52、第八薄膜晶体管T53和第九薄膜晶体管T54;所述第六薄膜晶体管T51的栅极与第六薄膜晶体管T51的漏极连接高电平信号;所述第六薄膜晶体管T51的源极与所述第七薄膜晶体管T52的漏极连接;所述第七薄膜晶体管T52的源极与所述下拉信号线连接;所述第七薄膜晶体管T52的栅极和第一薄膜晶体管T11漏极相连接。

[0045] 优选的,所述第八薄膜晶体管T53的栅极与所述第六薄膜晶体管T51的源极连接, 所述第八薄膜晶体管T53的源极与所述第九薄膜晶体管T54的漏极相连接,所述第八薄膜晶体管T53的漏极与所述第六薄膜晶体管T51的漏极相连接;所述第九薄膜晶体管T54的栅极 与所述第一薄膜晶体管T11的漏极连接,所述第九薄膜晶体管T54的源极与所述当前下拉维持电路所属的G0A单元同级的下拉信号线连接。

[0046] 优选的,在本发明所提供的GOA电路中,该GOA单元还可以包括自举电容电路,所述自举电容电路的一端为栅极信号点Q(N),所述自举电容电路通过所述栅极信号点Q(N)与第一薄膜晶体管T11的源极连接所述自举电容电路用以维持当前GOA单元中栅极信号点Q(N)的电位。

[0047] 根据本发明的上述目的,提出一种液晶显示器,包括上述的GOA电路。本实施例提供的液晶显示器的工作原理,与前述GOA电路的实施例工作原理一致,具体结构关系及工作原理参见前述GOA电路实施例,此处不再赘述。

[0048] 综上所述,虽然本发明已以优选实施例揭露如上,但上述优选实施例并非用以限制本发明,本领域的普通技术人员,在不脱离本发明的精神和范围内,均可作各种更动与润饰,因此本发明的保护范围以权利要求界定的范围为准。

图1

12

| 专利名称(译)        | GOA电路及液晶显示器         |         |            |  |

|----------------|---------------------|---------|------------|--|

| 公开(公告)号        | <u>CN110223649A</u> | 公开(公告)日 | 2019-09-10 |  |

| 申请号            | CN201910408790.X    | 申请日     | 2019-05-16 |  |

| [标]申请(专利权)人(译) | 深圳市华星光电技术有限公司       |         |            |  |

| 申请(专利权)人(译)    | 深圳市华星光电技术有限公司       |         |            |  |

| 当前申请(专利权)人(译)  | 深圳市华星光电技术有限公司       |         |            |  |

| [标]发明人         | 陈帅                  |         |            |  |

| 发明人            | 陈帅                  |         |            |  |

| IPC分类号         | G09G3/36            |         |            |  |

| CPC分类号         | G09G3/3677          |         |            |  |

| 代理人(译)         | 黄威                  |         |            |  |

| 外部链接           | Espacenet SIPO      |         |            |  |

## 摘要(译)

本发明提供一种GOA电路及液晶显示器,其中,GOA电路包括2N个GOA单元,所述2N个GOA单元中第N级GOA单元与第N+1级GOA单元共用同一个下拉维持电路,N为正整数。通过共用一个下拉维持电路,减少了GOA电路中电路的数量,从而节省了GOA电路在液晶显示器上所占据的空间,且同时提高了TFT器件中电路的使用效率,有利于液晶显示器的窄边框设计。