(12)发明专利申请

(10)申请公布号 CN 111308806 A

(43)申请公布日 2020.06.19

(21)申请号 202010250080.1

(22)申请日 2020.04.01

(71)申请人 TCL华星光电技术有限公司

地址 518132 广东省深圳市光明新区塘明

大道9-2号

(72)发明人 陈兴武 严允晟 张银峰 张鑫

陈黎煊 李冬泽

(74)专利代理机构 深圳紫藤知识产权代理有限

公司 44570

代理人 徐世俊

(51)Int.Cl.

G02F 1/1343(2006.01)

G02F 1/1337(2006.01)

G02F 1/1335(2006.01)

G02F 1/137(2006.01)

权利要求书2页 说明书8页 附图11页

(54)发明名称

一种液晶显示面板

(57)摘要

本申请公开了一种液晶显示面板，包括阵列基板、彩膜基板、第一偏光片以及第二偏光片，第一偏光片的第一偏振方向与第二偏光片的第二偏振方向相互垂直；阵列基板上的每一像素单元包括一像素电极，像素电极包括主干电极，主干电极包括沿第一方向设置的第一主干电极以及沿第二方向设置的第二主干电极，所述第一方向与所述第一偏振方向形成的夹角与直角相异。通过将第一主干电极相对于所述第一偏振方向和所述第二偏振方向倾斜设置，以调整相邻两个畴区中的支干电极与第一主干电极所形成的夹角，可以增大小角度区域处支干电极与第一主干电极之间的夹角，防止对像素电极进行图案化时小角度区域处存在未蚀刻或蚀刻不完全的现象。

1. 一种液晶显示面板，其特征在于，所述液晶显示面板包括：

阵列基板，所述阵列基板包括第一基板以及阵列分布于所述第一基板上的多个像素单元；

彩膜基板，所述彩膜基板与所述阵列基板相对设置；

液晶层，所述液晶层设置于所述阵列基板与所述彩膜基板之间；

第一偏光片，所述第一偏光片设置于所述第一基板远离所述像素单元的一侧上；

第二偏光片，所述第二偏光片设置于所述彩膜基板远离所述阵列基板的一侧上，所述第一偏光片的第一偏振方向与所述第二偏光片的第二偏振方向相互垂直；

其中，每一所述像素单元包括一像素电极，所述像素电极包括主干电极，所述主干电极包括沿第一方向设置的第一主干电极以及沿第二方向设置的第二主干电极，所述主干电极将所述像素单元所在区域限定为4个畴区，任一所述畴区中均设置有与所述主干电极连接的支干电极，所述第一方向与所述第一偏振方向形成的夹角与直角相异。

2. 根据权利要求1所述的液晶显示面板，其特征在于，所述第一主干电极位于沿所述像素单元的行方向排布的相邻两个所述畴区之间，所述第二主干电极位于沿所述像素单元的列方向排布的相邻两个所述畴区之间。

3. 根据权利要求2所述的液晶显示面板，其特征在于，所述第一主干电极包括分别位于所述第二主干电极的两侧的第一分体和第二分体，所述第一分体和第二分体均与所述第二主干电极连接，所述第一分体与所述第二分体错位设置。

4. 根据权利要求2所述的液晶显示面板，其特征在于，所述第二方向与所述第二偏振方向形成的夹角与直角相异。

5. 根据权利要求2所述的液晶显示面板，其特征在于，所述第二方向与所述第二偏振方向平行。

6. 根据权利要求2所述的液晶显示面板，其特征在于，所述第二主干电极包括相间隔的第一部分和第二部分，所述第一部分和所述第二部分通过一连接部电连接，所述连接部的延伸方向与所述第二方向相异。

7. 根据权利要求1所述的液晶显示面板，其特征在于，每一所述像素单元包括相间隔的第一像素区和第二像素区，所述第二像素区沿所述第一像素区的外边界设置；所述像素电极包括位于所述第一像素区内的第一像素电极以及位于所述第二像素区的第二像素电极，所述第一像素电极与所述第二像素电极相间隔且所述第二像素电极沿所述第一像素电极的外边界设置。

8. 根据权利要求7所述的液晶显示面板，其特征在于，所述第一主干电极位于所述第一像素区，所述第二主干电极包括位于所述第一像素区的第三部分和位于所述第二像素区的第四部分。

9. 根据权利要求7所述的液晶显示面板，其特征在于，每一所述畴区包括至少一个位于所述第一像素区的第一分区以及位于所述第二像素区的第二分区。

10. 根据权利要求1所述的液晶显示面板，其特征在于，所述主干电极包括中部主干部分以及位于所述中部主干部分的侧部的侧部主干部分，所述支干电极包括中部支干部分以及位于所述中部支干部分的侧部的侧部支干部分；所述中部主干部分和所述中部支干部分位于所述像素电极的中心区域，所述中部主干部分的宽度大于所述侧部主干部分的宽度，

所述中部支干部分的宽度大于所述侧部支干部分的宽度。

11. 根据权利要求1所述的液晶显示面板，其特征在于，沿所述像素单元的行方向排布且相邻的两个所述畴区中的支干电极分别与所述第一偏振方向形成第一夹角和第二夹角，所述第一夹角为0~30度，所述第二夹角为60~90度。

12. 根据权利要求1所述的液晶显示面板，其特征在于，所述第一方向与所述第一偏振方向形成第三夹角，所述第三夹角为5~25度。

13. 根据权利要求1所述的液晶显示面板，其特征在于，所述液晶层的光程差为300~550纳米，所述液晶层的厚度为2.5~4微米，所述液晶层中的液晶材料的螺距为所述液晶层的厚度的2~10倍。

## 一种液晶显示面板

### 技术领域

[0001] 本申请涉及显示技术领域,尤其涉及一种液晶显示面板。

### 背景技术

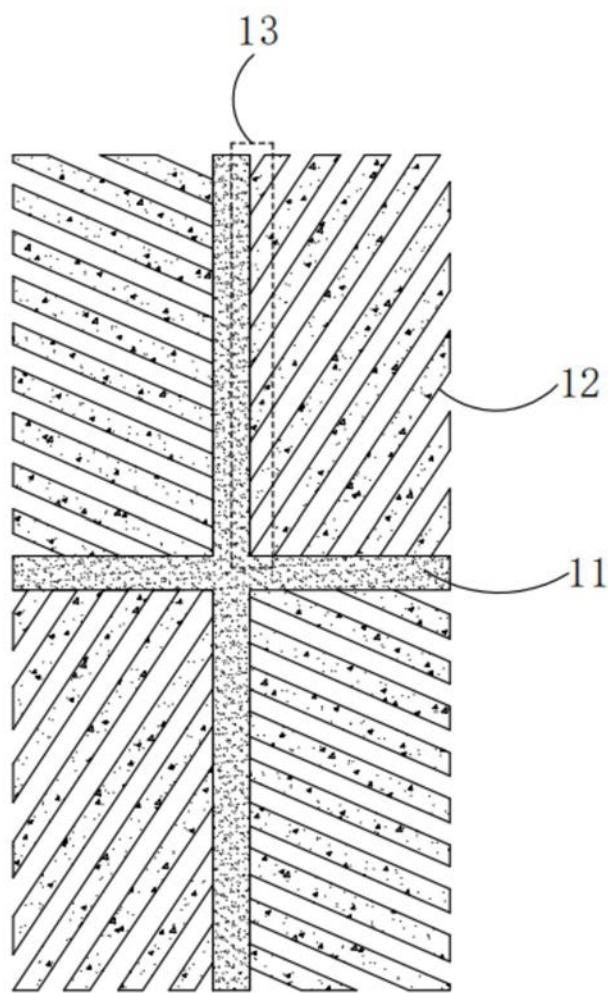

[0002] 液晶显示面板一般包括相对设置的阵列基板和彩膜基板,阵列基板和彩膜基板之间填充液晶层,阵列基板上设置有用于驱动液晶转动的像素电极。如图1所示,在多畴区的液晶显示面板中,像素电极呈图案化,像素电极一般包括主电极11和与主电极11连接的分支电极12。

[0003] 然而,在分支电极12与主电极11形成的夹角的角度较小的小角度区域13,在对像素电极图案化的过程中,由于机台限制,小角度区域13处的像素电极难以蚀刻,导致小角度区域13处预设蚀刻的像素电极存在未蚀刻或蚀刻不完全的现象,从而导致进行液晶配向时小角度区域处会产生暗纹。

### 发明内容

[0004] 本申请实施例提供一种液晶显示面板,以解决现有的液晶显示面板,在对像素电极图案化的过程中,小角度区域处预设蚀刻的像素电极存在未蚀刻或蚀刻不完全的现象,从而导致进行液晶配向时小角度区域处会产生暗纹的技术问题。

[0005] 为解决上述问题,本发明提供的技术方案如下:

[0006] 一种液晶显示面板,所述液晶显示面板包括:

[0007] 阵列基板,所述阵列基板包括第一基板以及阵列分布于所述第一基板上的多个像素单元;

[0008] 彩膜基板,所述彩膜基板与所述阵列基板相对设置;

[0009] 液晶层,所述液晶层设置于所述阵列基板与所述彩膜基板之间;

[0010] 第一偏光片,所述第一偏光片设置于所述第一基板远离所述像素单元的一侧上;

[0011] 第二偏光片,所述第二偏光片设置于所述彩膜基板远离所述阵列基板的一侧上,所述第一偏光片的第一偏振方向与所述第二偏光片的第二偏振方向相互垂直;

[0012] 其中,每一所述像素单元包括一像素电极,所述像素电极包括主干电极,所述主干电极包括沿第一方向设置的第一主干电极以及沿第二方向设置的第二主干电极,所述主干电极将所述像素单元所在区域限定为4个畴区,任一所述畴区中均设置有与所述主干电极连接的支干电极,所述第一方向与所述第一偏振方向形成的夹角与直角相异。

[0013] 在一些实施例中,所述第一主干电极位于沿所述像素单元的行方向排布的相邻两个所述畴区之间,所述第二主干电极位于沿所述像素单元的列方向排布的相邻两个所述畴区之间。

[0014] 在一些实施例中,所述第一主干电极包括分别位于所述第二主干电极的两侧的第一分体和第二分体,所述第一分体和第二分体均与所述第二主干电极连接,所述第一分体与所述第二分体错位设置。

- [0015] 在一些实施例中,所述第二方向与所述第二偏振方向形成的夹角与直角相异。

- [0016] 在一些实施例中,所述第二方向与所述第二偏振方向平行。

- [0017] 在一些实施例中,所述第二主干电极包括相间隔的第一部分和第二部分,所述第一部分和所述第二部分通过一连接部电连接,所述连接部的延伸方向与所述第二方向相异。

- [0018] 在一些实施例中,每一所述像素单元包括相间隔的第一像素区和第二像素区,所述第二像素区沿所述第一像素区的外边界设置;所述像素电极包括位于所述第一像素区内第一像素电极以及位于所述第二像素区的第二像素电极,所述第一像素电极与所述第二像素电极相间隔且所述第二像素电极沿所述第一像素电极的外边界设置。

- [0019] 在一些实施例中,所述第一主干电极位于所述第一像素区,所述第二主干电极包括位于所述第一像素区的第三部分和位于所述第二像素区的第四部分。

- [0020] 在一些实施例中,每一所述畴区包括至少一个位于所述第一像素区的第一分区以及位于所述第二像素区的第二分区。

- [0021] 在一些实施例中,所述主干电极包括中部主干部分以及位于所述中部主干部分的侧部的侧部主干部分,所述支干电极包括中部支干部分以及位于所述中部支干部分的侧部的侧部支干部分;所述中部主干部分和所述中部支干部分位于所述像素电极的中心区域,所述中部主干部分的宽度大于所述侧部主干部分的宽度,所述中部支干部分的宽度大于所述侧部支干部分的宽度。

- [0022] 在一些实施例中,沿所述像素单元的行方向排布且相邻的两个所述畴区中的支干电极分别与所述第一偏振方向形成第一夹角和第二夹角,所述第一夹角为0~30度,所述第二夹角为60~90度。

- [0023] 在一些实施例中,所述第一方向与所述第一偏振方向形成第三夹角,所述第三夹角为5~25度。

- [0024] 在一些实施例中,所述液晶层的光程差为300~550纳米,所述液晶层的厚度为2.5~4微米,所述液晶层中的液晶材料的螺距为所述液晶层的厚度的2~10倍。

- [0025] 本发明申请的有益效果为:通过将第一主干电极相对于所述第一偏振方向和所述第二偏振方向倾斜设置,以调整相邻两个畴区中的支干电极与第一主干电极所形成的夹角,可以增大小角度区域处支干电极与所述第一主干电极之间的夹角,防止对像素电极进行图案化时小角度区域处存在未蚀刻或蚀刻不完全的现象,从而防止进行液晶配向时小角度区域处产生暗纹。

## 附图说明

- [0026] 下面结合附图,通过对本申请的具体实施方式详细描述,将使本申请的技术方案及其它有益效果显而易见。

- [0027] 图1为本申请背景技术中液晶显示面板的结构示意图;

- [0028] 图2为本申请具体实施方式中液晶显示面板的第一种结构示意图;

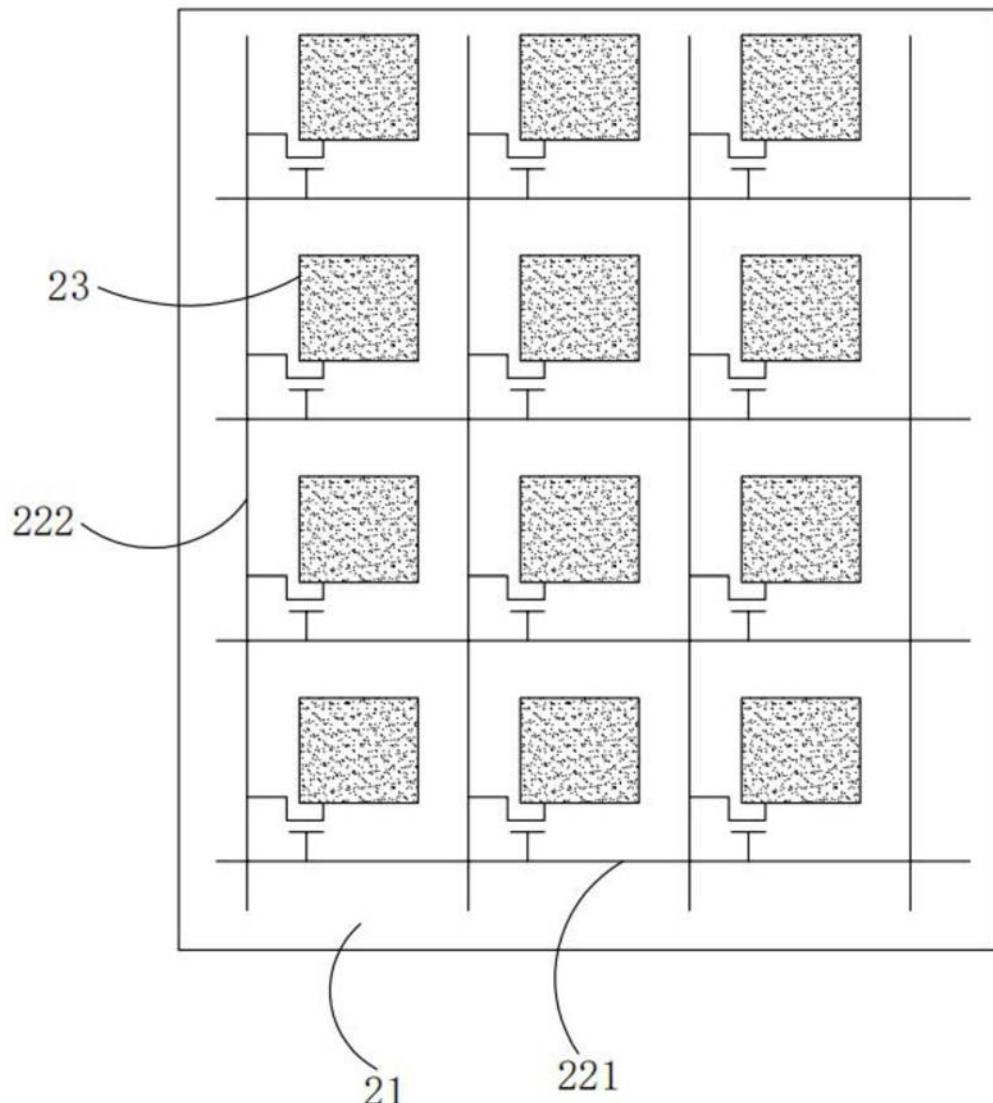

- [0029] 图3为本申请一实施方式中像素单元的排布示意图;

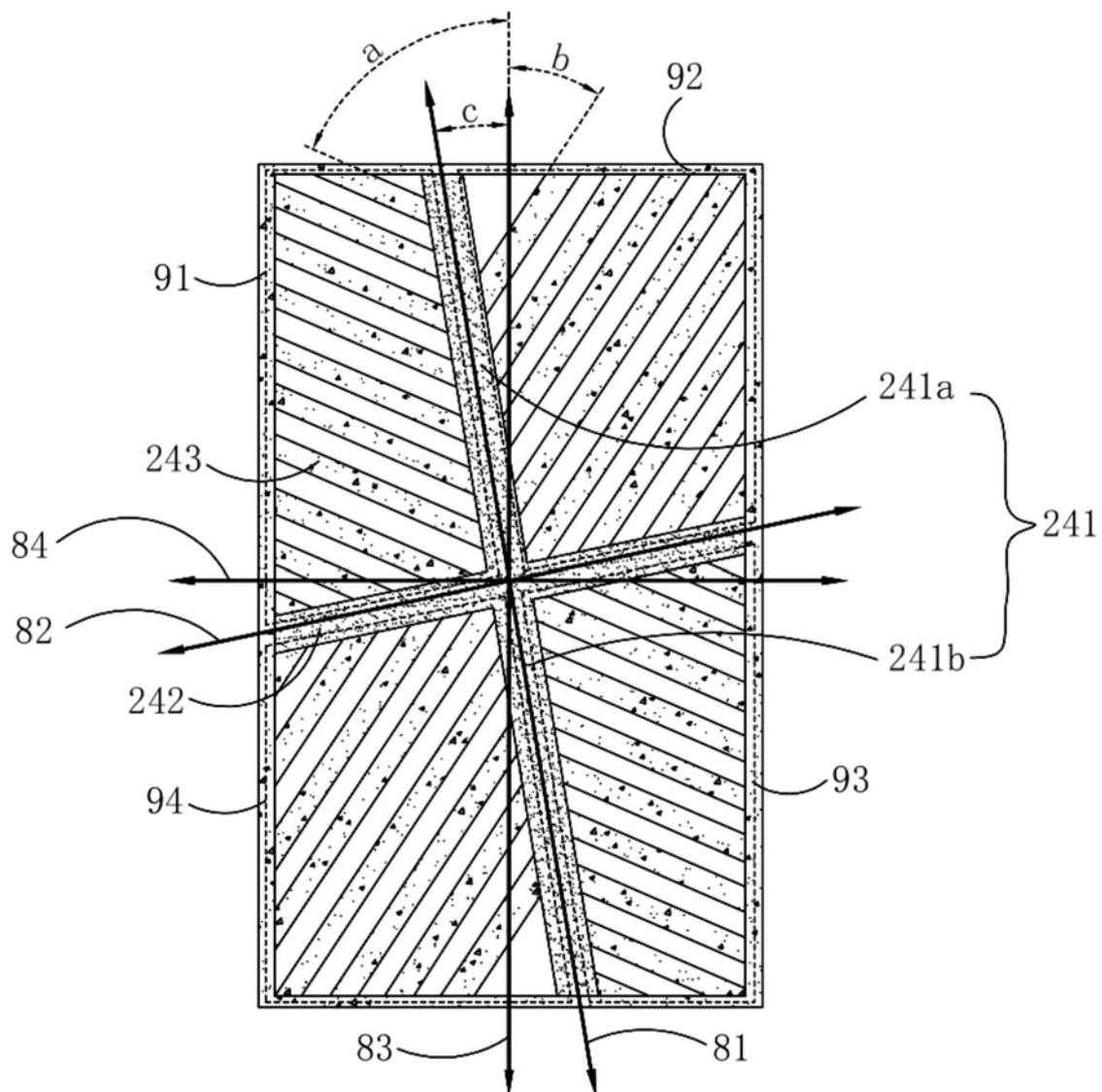

- [0030] 图4为本申请具体实施方式中像素电极的第一种结构示意图;

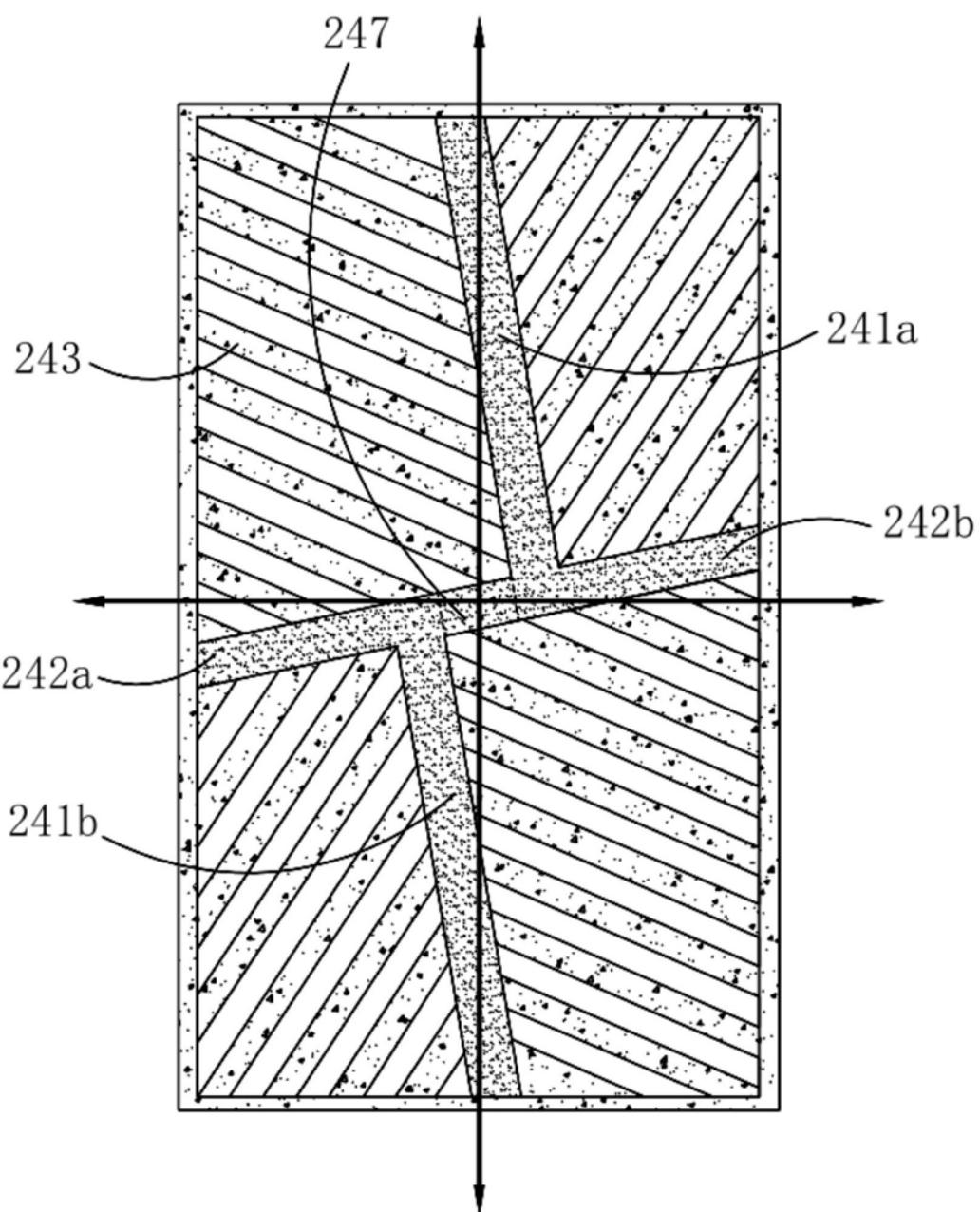

- [0031] 图5为本申请具体实施方式中像素电极的第二种结构示意图;

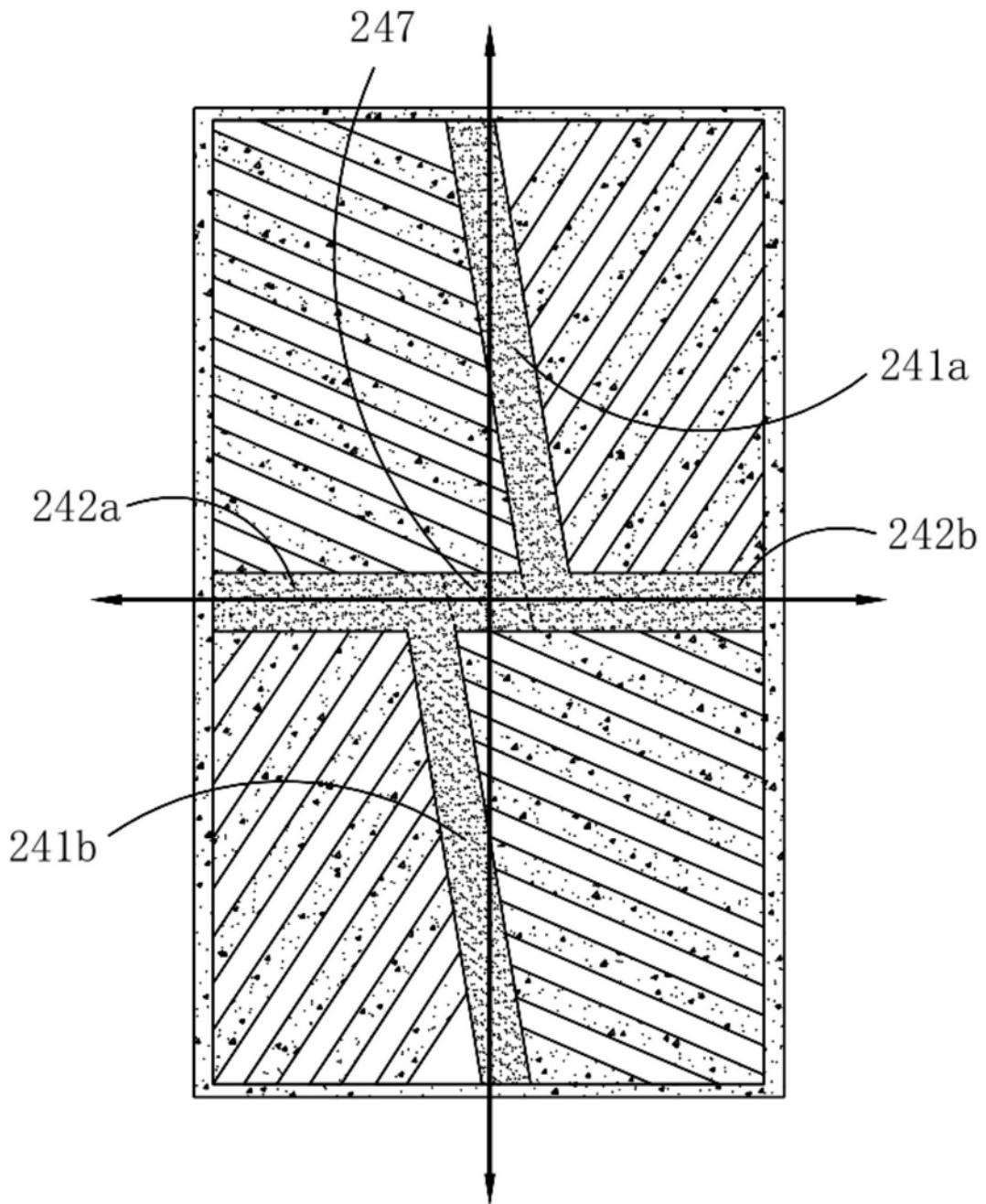

- [0032] 图6为本申请具体实施方式中像素电极的第三种结构示意图；

[0033] 图7为本申请具体实施方式中像素电极的第四种结构示意图；

[0034] 图8为本申请具体实施方式中像素电极的第五种结构示意图；

[0035] 图9为本申请具体实施方式中像素电极的第六种结构示意图；

[0036] 图10为本申请具体实施方式中像素电极的第七种结构示意图；

[0037] 图11为本申请具体实施方式中液晶材料的螺距与第一夹角和第二夹角的关系示意图；

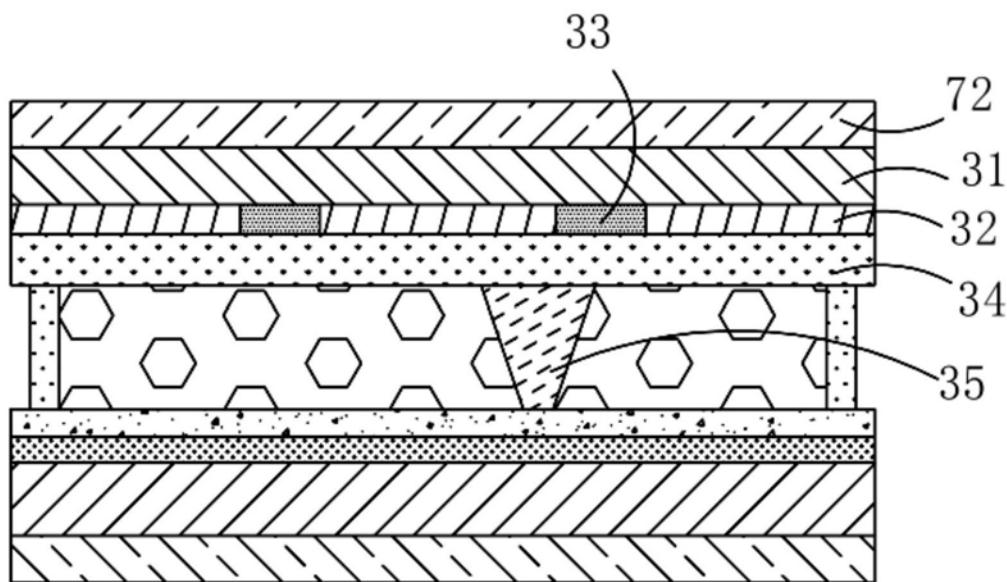

[0038] 图12为本申请具体实施方式中液晶显示面板的第二种结构示意图。

[0039] 附图标记：

[0040] 11、主电极；12、分支电极；13、小角度区域；20、阵列基板；21、第一基板；22、薄膜晶体管层；221、扫描线；222、数据线；23、像素单元；231、第一像素区；232、第二像素区；24、像素电极；241、第一主干电极；241a、第一分体；241b、第二分体；242、第二主干电极；242a、第一部分；242b、第二部分；242c、第三部分；242d、第四部分；243、支干电极；243a、中部支干部分；243b、侧部支干部分；244、第一像素电极；245、第二像素电极；246a、第一边缘电极；246b、第二边缘电极；246c、第三边缘电极；247、连接部；248a、中部主干部分；248b、侧部主干部分；30、彩膜基板；31、第二基板；32、色阻块；33、遮光块；34、共通电极；35、支撑柱；40、液晶层；50、框胶；71、第一偏光片；72、第二偏光片；81、第一方向；82、第二方向；83、第一偏振方向；84、第二偏振方向；91、第一畴区；92、第二畴区；93、第三畴区；94、第四畴区；95、第一分区；96、第二分区；97、中心区域。

## 具体实施方式

[0041] 下面将结合本申请实施例中的附图，对本申请实施例中的技术方案进行清楚、完整地描述。显然，所描述的实施例仅仅是本申请一部分实施例，而不是全部的实施例。基于本申请中的实施例，本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例，都属于本申请保护的范围。

[0042] 在本申请的描述中，需要理解的是，术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系，仅是为了便于描述本申请和简化描述，而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作，因此不能理解为对本申请的限制。此外，术语“第一”、“第二”仅用于描述目的，而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此，限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本申请的描述中，“多个”的含义是两个或两个以上，除非另有明确具体的限定。

[0043] 在本申请的描述中，需要说明的是，除非另有明确的规定和限定，术语“安装”、“相连”、“连接”应做广义理解，例如，可以是固定连接，也可以是可拆卸连接，或一体地连接；可以是机械连接，也可以是电连接或可以互相通讯；可以是直接相连，也可以通过中间媒介间接相连，可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言，可以根据具体情况理解上述术语在本申请中的具体含义。

[0044] 在本申请中，除非另有明确的规定和限定，第一特征在第二特征之“上”或之“下”

可以包括第一和第二特征直接接触，也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且，第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方，或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方，或仅仅表示第一特征水平高度小于第二特征。

[0045] 下文的公开提供了许多不同的实施方式或例子用来实现本申请的不同结构。为了简化本申请的公开，下文中对特定例子的部件和设置进行描述。当然，它们仅为示例，并且目的不在于限制本申请。此外，本申请可以在不同例子中重复参考数字和/或参考字母，这种重复是为了简化和清楚的目的，其本身不指示所讨论各种实施方式和/或设置之间的关系。此外，本申请提供了的各种特定的工艺和材料的例子，但是本领域普通技术人员可以意识到其他工艺的应用和/或其他材料的使用。

[0046] 本申请针对现有的液晶显示面板，在对像素电极图案化的过程中，小角度区域处预设蚀刻的像素电极存在未蚀刻或蚀刻不完全的现象，从而导致进行液晶配向时小角度区域处会产生暗纹的技术问题。本申请可以解决上述问题。

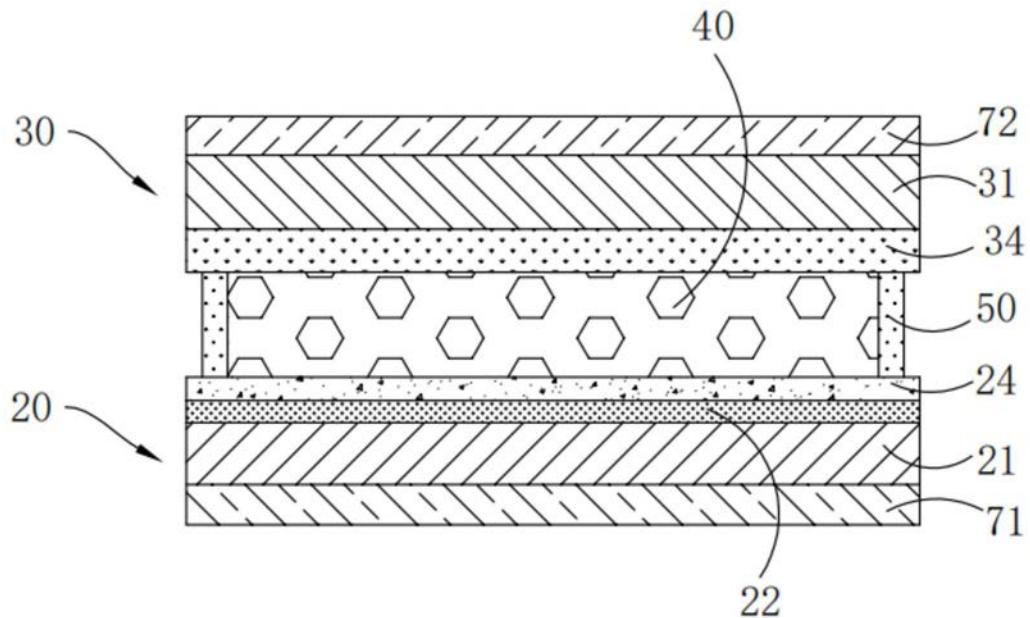

[0047] 一种液晶显示面板，如图2和图3所示，所述液晶显示面板包括阵列基板20、彩膜基板30和液晶层40，所述彩膜基板30与所述阵列基板20相对设置，所述液晶层40设置于所述阵列基板20与所述彩膜基板30之间；所述阵列基板20与所述彩膜基板30之间设置有框胶50，所述框胶50与所述阵列基板20和所述彩膜基板30之间形成用于容纳液晶层40的容纳腔。

[0048] 具体的，所述阵列基板20包括第一基板21以及阵列分布于所述第一基板21上的多个像素单元23，每一所述像素单元23包括薄膜晶体管层22和位于所述薄膜晶体管层22上的像素电极24；所述彩膜基板30包括第二基板31以及设置于所述第二基板31上且与所述像素单元23相对设置的共通电极34，通过所述像素电极24与共通电极34之间的压差形成的电场驱动液晶层40中的液晶旋转。

[0049] 其中，所述第一基板21和所述第二基板31可以为柔性基板或硬质基板，所述第一基板21和所述第二基板31可以为玻璃基板或塑料基板。

[0050] 在一实施方式中，所述薄膜晶体管层22包括设置于所述第一基板21的第一金属层和位于所述第一金属层上方的第二金属层。

[0051] 其中，所述第一金属层包括多条扫描线221，所述扫描线221沿所述像素单元23的行方向设置且多条所述扫描线221沿所述像素单元23的列方向间隔排布；所述第二金属层包括多条数据线222，所述数据线222沿所述像素单元23的列方向设置且多条所述数据线222沿所述像素单元23的行方向间隔排布，相邻两条所述数据线222和相邻两条所述扫描线221之间交叉限定的区域为设置一个所述像素单元23的区域。

[0052] 在一实施方式中，一条所述扫描线221与一行所述像素单元23对应并电性连接，以为所述像素单元23提供扫描信号；一条所述数据线222与一列所述像素单元23对应并电连接，以为所述像素单元23提供数据信号。

[0053] 具体的，所述液晶显示面板还包括第一偏光片71和第二偏光片72，所述第一偏光片71设置于所述第一基板21远离所述像素单元23的一侧上，所述第二偏光片72设置于所述彩膜基板30远离所述阵列基板20的一侧上。

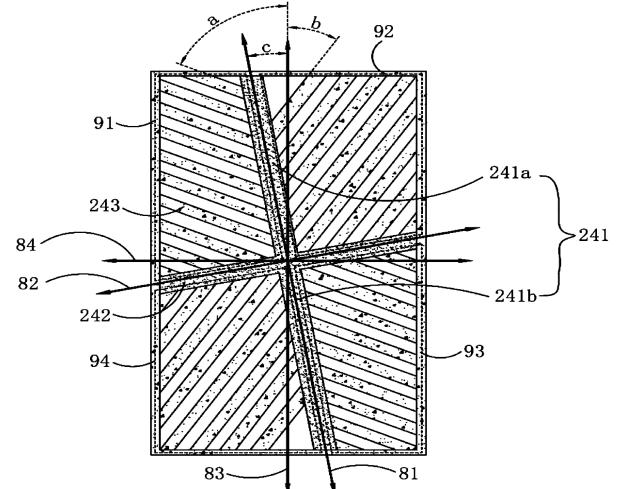

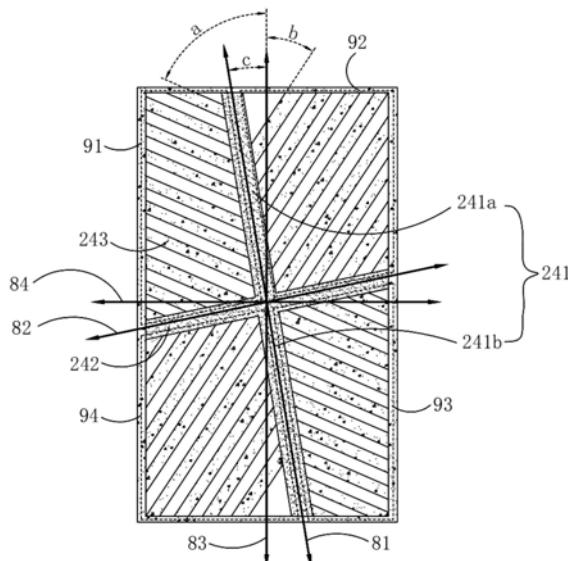

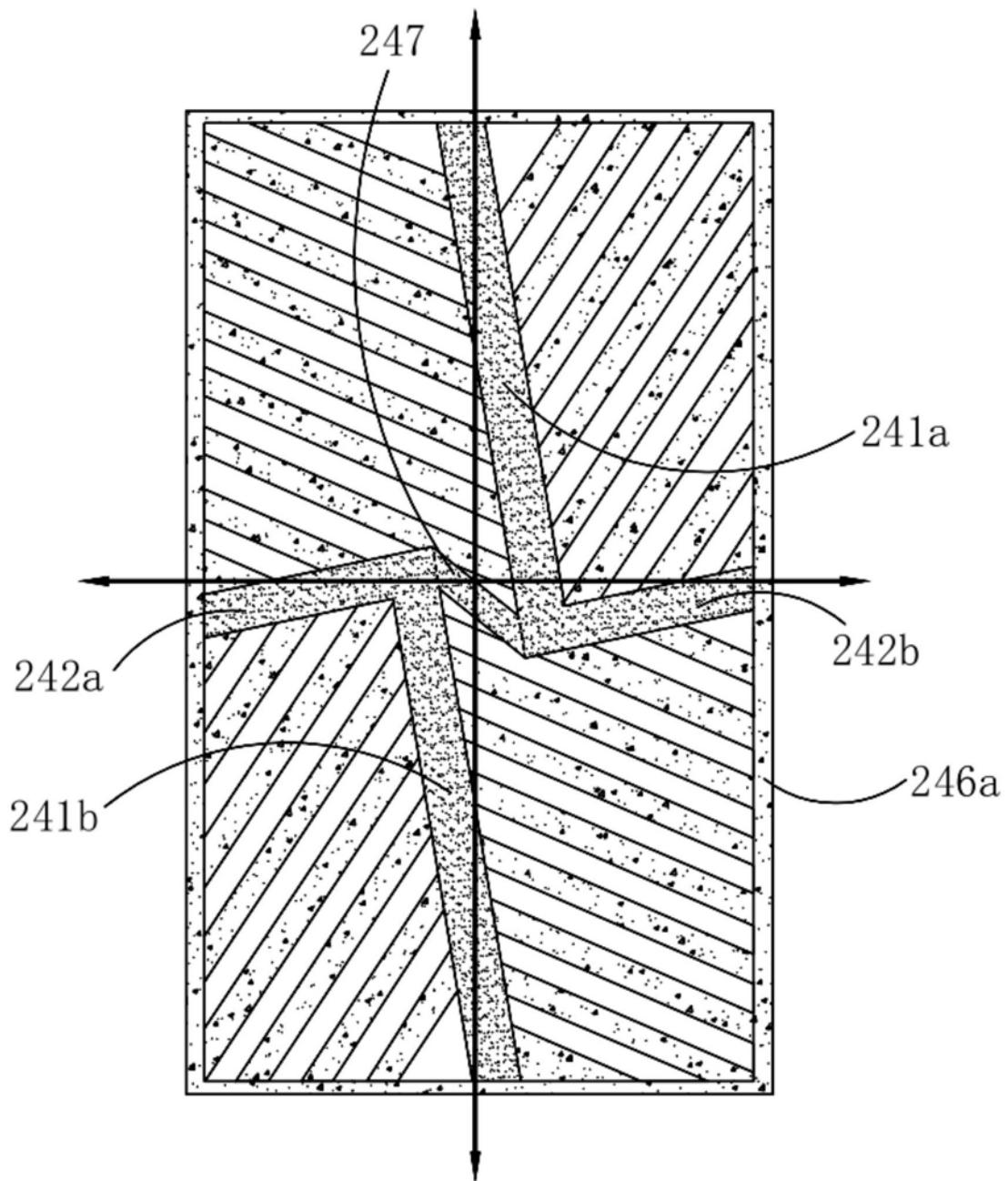

[0054] 具体的,如图4所示,所述第一偏光片71具有第一偏振方向83,所述第二偏光片72具有第二偏振方向84,所述第一偏光片71的第一偏振方向83与所述第二偏光片72的第二偏振方向84相互垂直。

[0055] 具体的,所述像素电极24包括主干电极,所述主干电极包括沿第一方向81设置的第一主干电极241以及沿第二方向82设置的第二主干电极242,所述主干电极将所述像素单元23所在区域限定为4个畴区,任一所述畴区中均设置有与所述主干电极连接的支干电极243,任一所述畴区中的多条所述支干电极243可以间隔设置,以增大像素电极24的穿透率。

[0056] 其中,所述第一方向81与所述第一偏振方向83形成的夹角与直角相异,即所述第一方向81与所述第一偏振方向83和所述第二偏振方向84均不平行。

[0057] 需要说明的是,通过将第一主干电极241相对于所述第一偏振方向83和所述第二偏振方向84倾斜设置,在保证相邻两个畴区中的支干电极243所形成的夹角不变的情况下,可以增大小角度区域处支干电极243与所述第一主干电极241之间形成的夹角,防止对像素电极24进行图案化时小角度区域处存在未蚀刻或蚀刻不完全的现象,从而防止进行液晶配向时小角度区域处产生暗纹。

[0058] 其中,所述第一方向81可以与所述第二方向82相互垂直,所述主干电极可以与所述支干电极243一体成型。

[0059] 在一实施方式中,所述第一主干电极241位于沿所述像素单元23的行方向排布的相邻两个所述畴区之间,所述第二主干电极242位于沿所述像素单元23的列方向排布的相邻两个所述畴区之间。

[0060] 需要说明的是,也可以设置成所述第一主干电极241位于沿所述像素单元23的列方向排布的相邻两个所述畴区之间,所述第二主干电极242位于沿所述像素单元23的行方向排布的相邻两个所述畴区之间。

[0061] 具体的,所述第一主干电极241包括分别位于所述第二主干电极242的两侧的第一分体241a和第二分体241b,所述第一分体241a和第二分体241b均与所述第二主干电极242连接。

[0062] 具体的,所述像素单元23包括第一畴区91、沿所述像素单元23的行方向与所述第一畴区91相邻的第二畴区92、沿所述像素单元23的列方向与所述第二畴区92相邻的第三畴区93以及沿所述像素单元23的行方向与所述第三畴区93相邻的第四畴区94。

[0063] 在一实施方式中,每一所述畴区中,所有所述支干电极243相互平行;所述第一畴区91中的支干电极243和所述第一偏振方向83所形成的夹角与所述第二畴区92中的支干电极243和所述第一偏振方向83所形成的夹角相异,所述第一畴区91中的支干电极243与所述第三畴区93中的支干电极243相互平行,所述第二畴区92中的支干电极243与所述第四畴区94中的支干电极243平行。

[0064] 其中,沿所述像素单元23的行方向排布且相邻的两个所述畴区中的支干电极243分别与所述第一偏振方向83形成第一夹角a和第二夹角b,所述第一方向81与所述第一偏振方向83形成第三夹角c。

[0065] 参见图4,以所述第一主干电极241位于沿所述像素单元23的行方向排布的相邻两个所述畴区之间,所述第二主干电极242位于沿所述像素单元23的列方向排布的相邻两个所述畴区之间,所述第一偏振方向83平行于所述像素单元23的列方向,所述第二偏振方向

84平行于所述像素单元23的行方向为例。

[0066] 其中,第一畴区91中的支干电极243与第一偏振方向83形成所述第一夹角a,第二畴区92中的支干电极243与第一偏振方向83形成所述第二夹角b,第一夹角a大于第二夹角b时,所述第一分体241a向第一畴区91倾斜,即所述第一分体241a位于所述第一畴区91和所述第一偏振方向83之间,此时第二畴区92中的支干电极243与第一主干电极241所形成的夹角等于第二夹角b和第三夹角c之和,在第一畴区91中的支干电极243的方向和第二畴区92中的支干电极243的方向均保持不变的情况下,通过将第一主干电极241倾斜设置以增大第二畴区92中的支干电极243与第一主干电极241所形成的夹角,改善小角度区域蚀刻不均的问题,从而防止进行液晶配向时小角度区域处产生暗纹。

[0067] 需要说明的是,第二夹角b大于第一夹角a时,所述第一分体241a向第二畴区92倾斜设置即可,即所述第一分体241a位于所述第二畴区92和所述第一偏振方向83之间。

[0068] 需要说明的是,实际实施中,也可以设置为所述第一偏振方向83平行于所述像素单元23的行方向,所述第二偏振方向84平行于所述像素单元23的列方向;还可以设置为所述第一偏振方向83与所述像素单元23的行方向和列方向均不平行。

[0069] 具体的,所述第一夹角a为0~30度,所述第二夹角b为60~90度,所述第三夹角c为5~25度。通过对位于不同畴区中的支干电极243与第一偏振方向83形成的夹角以及第一主干电极241与第一偏振方向83形成的夹角进行设计,改善小角度区域蚀刻不均的问题,同时可以增大像素电极24的穿透率。

[0070] 如图4所示,所述第一分体241a可以与所述第二分体241b位于同一直线上。

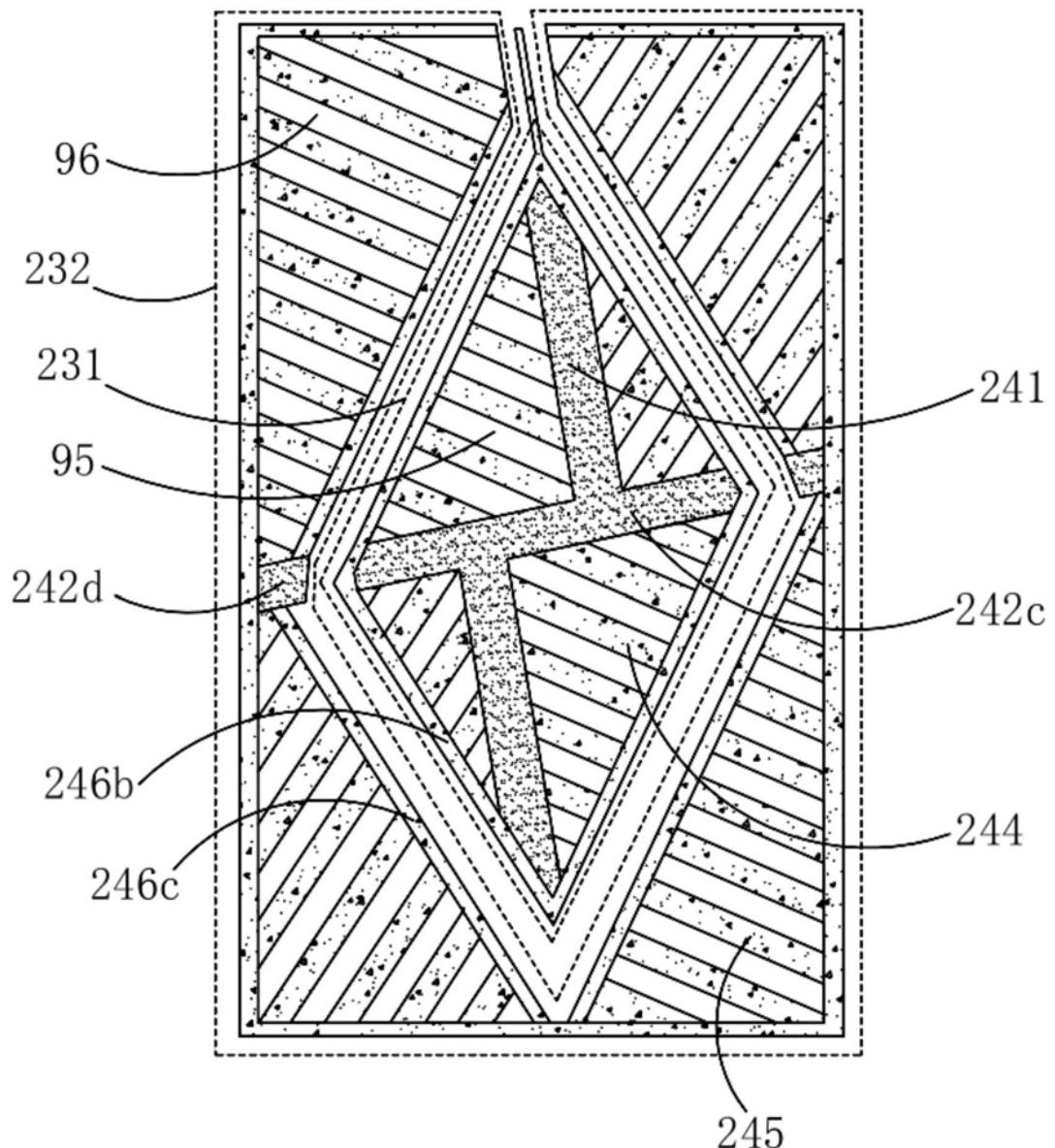

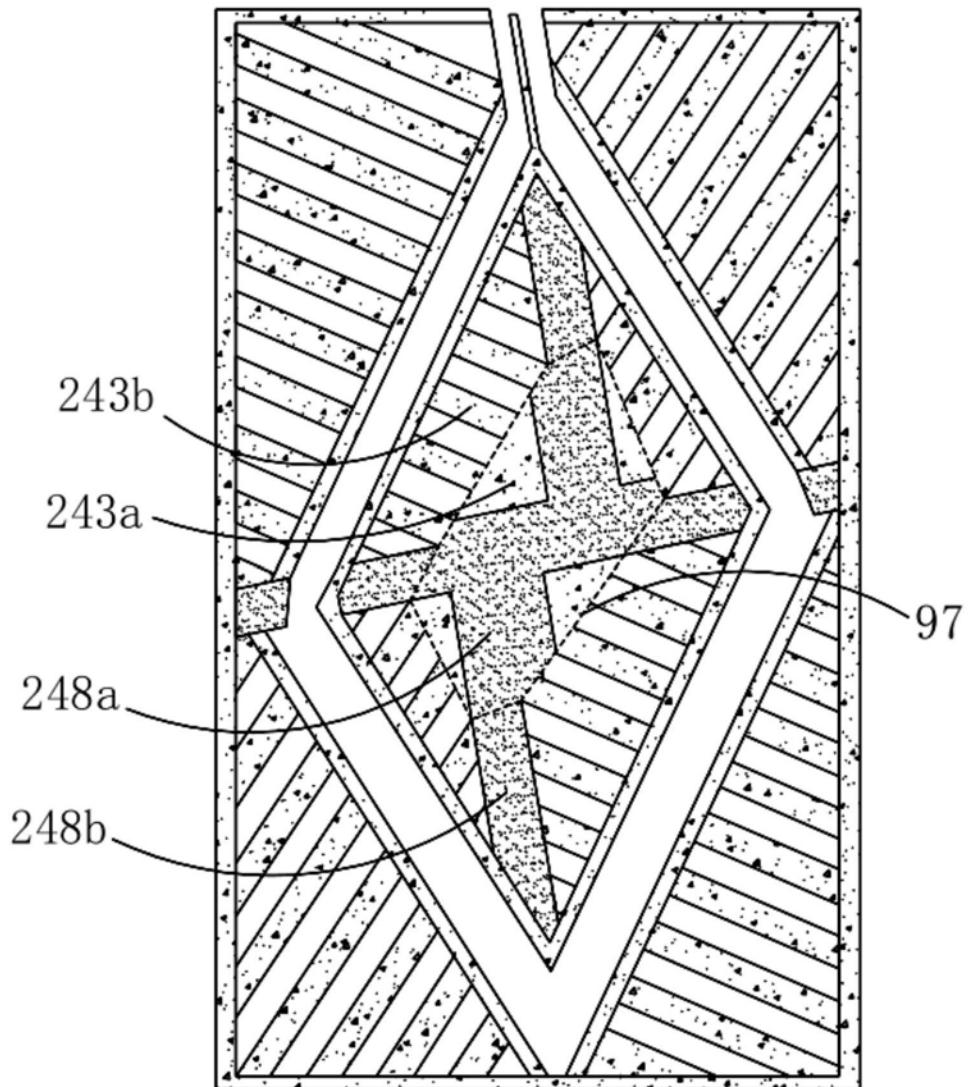

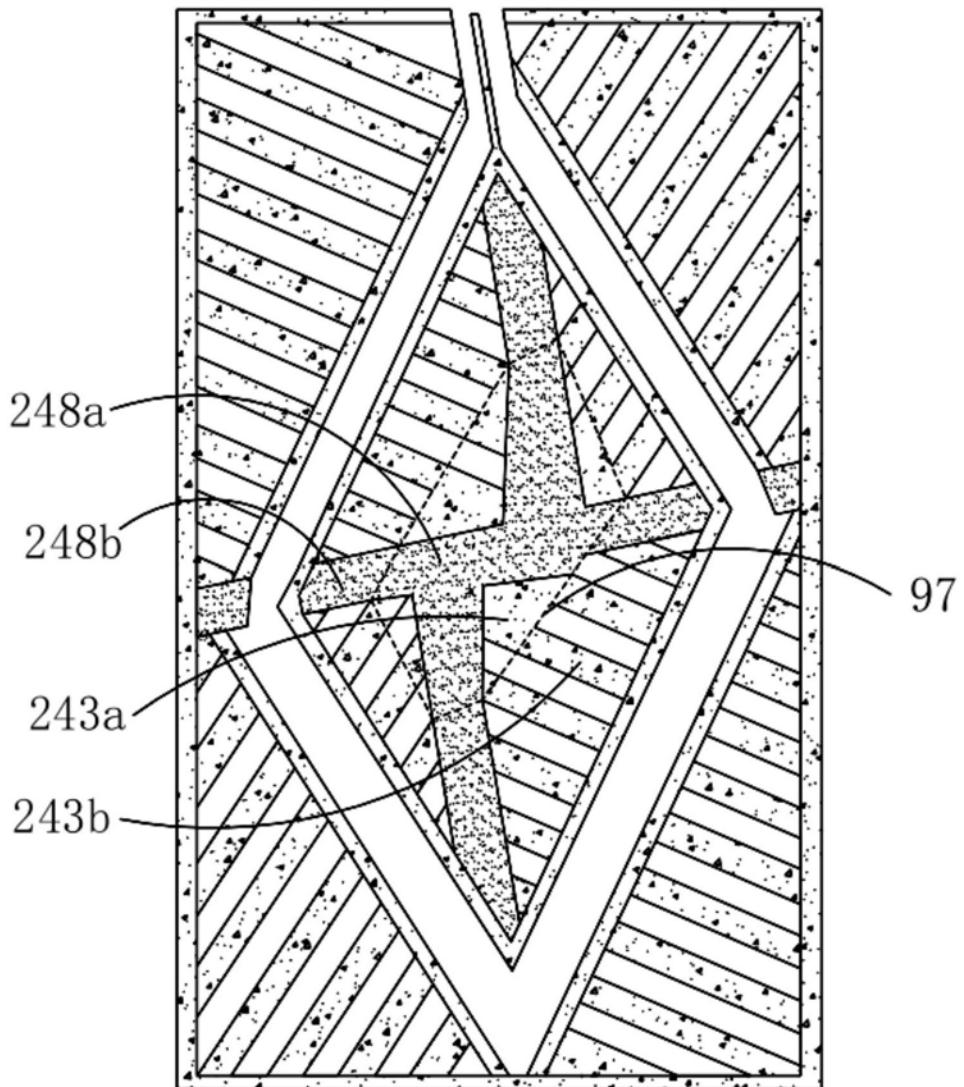

[0071] 如图5至图7所示,所述第一分体241a还可以与所述第二分体241b错位设置。

[0072] 需要说明的是,所述第一分体241a与所述第二分体241b错位设置时,沿所述第二方向82,所述第一分体241a与所述第二分体241b之间的距离可以为3~25μm。

[0073] 具体的,如图5至图7所示,所述第二主干电极242包括分别位于所述第一主干电极241的两侧的第一部分242a和第二部分242b,所述第一部分242a和所述第二部分242b均与所述第一主干电极241连接,所述第一部分242a和所述第二部分242b通过一连接部247电连接,所述连接部247可以与所述第一部分242a和所述第二部分242b一体成型。

[0074] 其中,如图5所示,所述第二方向82与所述第二偏振方向84形成的夹角可以与直角相异,即所述第二方向82与所述第一偏振方向83和所述第二偏振方向84均不平行。

[0075] 如图6所示,所述第二方向82也可以与所述第二偏振方向84平行。

[0076] 具体的,如图5和图6所示,所述第一部分242a可以与所述第二部分242b位于同一直线上,此时所述连接部247的延伸方向可以与所述第二方向82平行。

[0077] 如图7所示,所述第一部分242a还可以与所述第二部分242b错位设置,此时所述连接部247的延伸方向可以与所述第二方向82相异,即所述连接部247的延伸方向可以与所述第二方向82不平行。

[0078] 其中,所述第一部分242a与所述第二部分242b错位设置时,沿所述第一方向81,所述第一部分242a与所述第二部分242b之间的距离可以为3~25μm。

[0079] 参见图4至图7所示,在一实施方式中,所述像素电极24还包括第一边缘电极246a,所述第一边缘电极246a围绕所述主干电极的外边界设置以形成一封闭的第一容纳区,所述主干电极和所述支干电极243均位于所述第一容纳区内,所述主干电极和所述支干电极243

均与所述第一边缘电极246a连接，所述主干电极和所述支干电极243可以与所述第一边缘电极246a一体成型。

[0080] 在一实施方式中，如图8至图10所示，每一所述像素单元23包括相间隔的第一像素区231和第二像素区232，所述第二像素区232沿所述第一像素区231的外边界设置；所述像素电极24包括位于所述第一像素区231内的第一像素电极244以及位于所述第二像素区232的第二像素电极245，所述第一像素电极244与所述第二像素电极245相间隔且所述第二像素电极245沿所述第一像素电极244的外边界设置。

[0081] 需要说明的是，形成所述像素电极24后，对所述像素电极24进行蚀刻，以形成相间隔的所述第一像素电极244和所述第二像素电极245，输入至所述第一像素电极244的电压与输入至所述第二像素电极245的电压不同，从而在配向过程使得第一像素区231的液晶和第二像素区232的液晶形成的预倾角不同，增加液晶不同方向的倒向，有利于视角优化。

[0082] 其中，所述第一像素电极244为主像素电极，所述第二像素电极245为次像素电极。

[0083] 具体的，所述第一主干电极241位于所述第一像素区231，所述第二主干电极242包括位于所述第一像素区231的第三部分242c和位于所述第二像素区232的第四部分242d。

[0084] 在增加液晶不同方向的倒向的前提下，第一像素电极244和第二像素电极245共用一套主干电极，从而减少主干电极所占用的像素区域，从而减少像素单元23内暗纹的产生，提高像素单元23内的穿透率和液晶效率。

[0085] 具体的，每一所述畴区包括至少一个位于所述第一像素区231的第一分区95以及位于所述第二像素区232的第二分区96。

[0086] 其中，每一所述畴区中的第一分区95中的支干电极243可以与第二分区96中的支干电极243相互平行或不平行。

[0087] 在一实施方式中，所述像素电极24还包括第二边缘电极246b和第三边缘电极246c，所述第二边缘电极246b围绕所述第一像素电极244的外边界设置以形成一封闭的第二容纳区，所述第一像素电极244位于所述第二容纳区内，所述第一像素电极244与所述第二边缘电极246b连接，所述第一像素电极244可以与所述第二边缘电极246b一体成型；所述第三边缘电极246c围绕所述第二像素电极245的外边界设置以形成一封闭的第三容纳区，所述第二像素电极245位于所述第三容纳区内，所述第二像素电极245与所述第三边缘电极246c连接，所述第二像素电极245可以与所述第三边缘电极246c一体成型。

[0088] 如图9和图10所示，所述主干电极包括中部主干部分248a以及位于所述中部主干部分248a的侧部的侧部主干部分248b，所述支干电极243包括中部支干部分243a以及位于所述中部支干部分243a的侧部的侧部支干部分243b；所述中部主干部分248a和所述中部支干部分243a位于所述像素电极24的中心区域97，所述中部主干部分248a的宽度大于所述侧部主干部分248b的宽度，所述中部支干部分243a的宽度大于所述侧部支干部分243b的宽度。

[0089] 需要说明的是，通过增大像素电极24的中心区域97处的中部主干部分248a和中部支干部分243a的宽度，以增加像素电极24的中心区域97处的电场，从而增加配向时像素电极24的中心区域97处的液晶的预倾角，而液晶的预倾角越大，响应速度越快，从而有效改善像素电极24的中心区域97处的暗纹，同时像素电极24的中心区域97的电场与像素电极24的边侧区域的电场不同，从而增加液晶不同方向的倒向，有利于视角优化。

[0090] 如图9所示,所述像素电极24的中心区域97处可以填满像素电极材料,以进一步增大像素电极24的中心区域97处的电场;如图10所示,所述像素电极24的中心区域97处还可以具有镂空结构,以提高像素电极24的中心区域97处的穿透率。

[0091] 具体的,所述液晶层40包括液晶材料和手性剂。

[0092] 需要说明的是,通过在液晶材料中加入手性剂,使液晶分子可以发生周期性旋转,利用手性剂产生的螺旋扭曲力带动像素电极24边缘位置处的液晶分子转动,有效的缩小像素电极24边缘位置处的暗纹的宽度。

[0093] 其中,所述手性剂可以为左旋手性剂或右旋手性剂,所述液晶材料为负性液晶。

[0094] 如图11所示,图11为液晶材料的螺距P与第一夹角a和第二夹角b的关系。

[0095] 需要说明的是,螺距P为液晶分子旋转360度回到原始取向的层间距,通过调节液晶材料的螺距P与第一夹角a和第二夹角b的关系,可有效减小相邻两个所述像素电极24之间的暗区宽度,增加有效开口率,提升穿透率。

[0096] 具体的,所述液晶层40的光程差为300~550纳米,所述液晶层40的厚度为2.5~4微米,所述液晶材料的螺距P为所述液晶层40的厚度的2~10倍,以提高像素单元23单位面积的穿透率。

[0097] 在一实施方式中,如图12所示,所述彩膜基板30还包括设置于所述第二基板31远离所述第二偏光片72的一侧上的色阻层,所述共通电极34设置于所述色阻层上。

[0098] 其中,所述色阻层包括多个间隔设置的色阻块32,所述色阻块32可以为红色色阻块、蓝色色阻块以及绿色色阻块中的任一种,以实现彩色显示。

[0099] 其中,相邻所述色阻块32之间设置有遮光块33,以避免相邻色阻块32之间的间隙处产生漏光。

[0100] 具体的,所述共通电极34上设置有与所述共通电极34和所述像素电极24接触的支撑柱35,所述支撑柱35用于维持所述彩膜基板30与所述阵列基板20之间的间距。

[0101] 本发明的有益效果为:通过将第一主干电极241相对于所述第一偏振方向83和所述第二偏振方向84倾斜设置,以调整相邻两个畴区中的支干电极243与第一主干电极241所形成的夹角,可以增大小角度区域处支干电极243与所述第一主干电极241之间形成的夹角,防止对像素电极24进行图案化时小角度区域处存在未蚀刻或蚀刻不完全的现象,从而防止进行液晶配向时小角度区域处产生暗纹。

[0102] 在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

[0103] 本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例的技术方案的范围。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

|                       | 左旋液晶                |                     | 右旋液晶                |                     |

|-----------------------|---------------------|---------------------|---------------------|---------------------|

| P/微米                  | 第一夹角/度              | 第二夹角/度              | 第一夹角/度              | 第二夹角/度              |

| $11 \leq P$           | $75 \leq a \leq 90$ | $0 \leq b \leq 15$  | $0 \leq a \leq 15$  | $75 \leq b \leq 90$ |

| $11 \leq P \leq 13.5$ | $75 \leq a \leq 90$ | $0 \leq b \leq 15$  | $0 \leq a \leq 15$  | $75 \leq b \leq 90$ |

| $13.5 \leq P \leq 16$ | $70 \leq a \leq 90$ | $0 \leq b \leq 20$  | $0 \leq a \leq 20$  | $70 \leq b \leq 90$ |

| $16 \leq P \leq 18.5$ | $65 \leq a \leq 90$ | $5 \leq b \leq 25$  | $5 \leq a \leq 25$  | $65 \leq b \leq 90$ |

| $18.5 \leq P$         | $60 \leq a \leq 90$ | $10 \leq b \leq 30$ | $10 \leq a \leq 30$ | $60 \leq b \leq 90$ |

图11

图12

|         |                                            |                      |            |

|---------|--------------------------------------------|----------------------|------------|

| 专利名称(译) | 一种液晶显示面板                                   |                      |            |

| 公开(公告)号 | <a href="#">CN111308806A</a>               | 公开(公告)日              | 2020-06-19 |

| 申请号     | CN202010250080.1                           | 申请日                  | 2020-04-01 |

| [标]发明人  | 陈兴武<br>严允晟<br>张银峰<br>张鑫<br>陈黎暄<br>李冬泽      |                      |            |

| 发明人     | 陈兴武<br>严允晟<br>张银峰<br>张鑫<br>陈黎暄<br>李冬泽      |                      |            |

| IPC分类号  | G02F1/1343 G02F1/1337 G02F1/1335 G02F1/137 |                      |            |

| 代理人(译)  | 徐世俊                                        |                      |            |

| 外部链接    | <a href="#">Espacenet</a>                  | <a href="#">Sipo</a> |            |

**摘要(译)**

本申请公开了一种液晶显示面板，包括阵列基板、彩膜基板、第一偏光片以及第二偏光片，第一偏光片的第一偏振方向与第二偏光片的第二偏振方向相互垂直；阵列基板上的每一像素单元包括一像素电极，像素电极包括主干电极，主干电极包括沿第一方向设置的第一主干电极以及沿第二方向设置的第二主干电极，所述第一方向与所述第一偏振方向形成的夹角与直角相异。通过将第一主干电极相对于所述第一偏振方向和所述第二偏振方向倾斜设置，以调整相邻两个畴区中的支干电极与第一主干电极所形成的夹角，可以增大小角度区域处支干电极与第一主干电极之间的夹角，防止对像素电极进行图案化时小角度区域处存在未蚀刻或蚀刻不完全的现象。