(12) 发明专利申请

(10) 申请公布号 CN 105700259 A

(43) 申请公布日 2016. 06. 22

(21) 申请号 201610239613. X

(22) 申请日 2016. 04. 18

(71) 申请人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路 10 号

申请人 重庆京东方光电科技有限公司

(72) 发明人 栗鹏 金熙哲 朴正湜 金在光

(74) 专利代理机构 北京同达信恒知识产权代理

有限公司 11291

代理人 黄志华

(51) Int. Cl.

G02F 1/1362(2006. 01)

G02F 1/1343(2006. 01)

权利要求书1页 说明书5页 附图6页

(54) 发明名称

一种阵列基板、液晶显示面板及显示装置

(57) 摘要

本申请提供了一种阵列基板、液晶显示面板及显示装置,用以降低 ADS 模式显示器的存储电容,本申请提供的一种阵列基板包括:衬底基板、在所述衬底基板上交叉布置的扫描线、数据线,以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元,所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极,其中,所述公共电极与所述像素电极成一夹角设置。

1. 一种阵列基板，所述阵列基板包括：衬底基板、在所述衬底基板上交叉布置的扫描线、数据线，以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元，所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极，其特征在于，所述公共电极与所述像素电极成一夹角设置。

2. 根据权利要求1所述的阵列基板，其特征在于，所述公共电极为狭缝状电极。

3. 根据权利要求2所述的阵列基板，其特征在于，所述公共电极包括沿同一方向延伸的多条第一条状电极。

4. 根据权利要求3所述的阵列基板，其特征在于，每一所述第一条状电极的宽度大于或等于2微米且小于或等于10微米，相邻的两个所述第一条状电极之间的间距大于或等于2微米且小于或等于10微米。

5. 根据权利要求1所述的阵列基板，其特征在于，所述像素电极为狭缝状电极。

6. 根据权利要求5所述的阵列基板，其特征在于，所述像素电极包括沿同一方向延伸的多条第二条状电极。

7. 根据权利要求6所述的阵列基板，其特征在于，每一所述第二条状电极的宽度大于或等于2微米且小于或等于5微米，相邻的两个所述第二条状电极之间的间距大于或等于4微米且小于或等于10微米。

8. 根据权利要求1~7任一权项所述的阵列基板，其特征在于，所述公共电极与所述像素电极之间的夹角大于或等于5度且小于或等于85度。

9. 一种液晶显示面板，其特征在于，包括权利要求1~8任一权项所述的阵列基板。

10. 一种显示装置，其特征在于，包括权利要求9所述的液晶显示面板。

## 一种阵列基板、液晶显示面板及显示装置

### 技术领域

[0001] 本申请涉及显示技术领域,尤其涉及一种阵列基板、液晶显示面板及显示装置。

### 背景技术

[0002] 薄膜晶体管液晶显示器(Thin Film Transistor Liquid Crystal Display, TFT-LCD)具有体积小、功耗低、无辐射等特点,在当前的平板显示器市场中占据了主导地位。目前广视角显示技术成为人们研究的热点。

[0003] 广视角液晶显示器按照显示模式可以分为:平面转换(1n Plane Switching, 1PS)型和高级超维场开关(Advanced Super Dimension Switch, ADS)型。其中,ADS模式液晶显示器通过液晶显示器中同一平面内狭缝电极边缘所产生的电场以及狭缝电极层与板状电极层间产生的电场形成多维电场,该多维电场使液晶盒内狭缝电极间、电极正上方所有指向液晶分子都能够产生旋转,从而提高了液晶工作效率并增大了透光效率。高级超维场开关技术可以提高TFT-LCD的画面品质,具有高分辨率、高透过率、低功耗、宽视角、高开口率、低色差、无挤压水波纹(push Mura)等优点。

[0004] 而ADS模式液晶显示器,其阵列基板中由像素电极与公共电极交叠区域形成存储电容 $C_{st}$ , $C_{st} = \epsilon S / 4\pi k d$ ,其中,  $\epsilon$ 表示介电常数,  $S$ 表示两电极正对面积,  $k$ 表示静电力常数,  $d$ 表示两电极之间的距离,像素电极与公共电极的交叠面积越大,存储电容也越大,导致TFT充电时困难,目前一般通过增加像素电极与公共电极之间的绝缘层厚度(即增加厚度 $d$ )或者减小开口率(即减小开口面积 $S$ )实现降低存储电容,而增加像素电极与公共电极绝缘层厚度的方案会增加显示器的厚度,不利于显示器减薄,减小开口率的方案会降低显示器的开口率,从而影响产品的品质。

### 发明内容

[0005] 本申请实施例提供了一种阵列基板、液晶显示面板及显示装置,用以降低ADS模式显示器的存储电容。

[0006] 本申请实施例提供的一种阵列基板包括:衬底基板、在所述衬底基板上交叉布置的扫描线、数据线,以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元,所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极,其中,所述公共电极与所述像素电极成一夹角设置。

[0007] 本申请实施例提供的阵列基板,包括:衬底基板、在所述衬底基板上交叉布置的扫描线、数据线,以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元,所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极,并且,所述公共电极与所述像素电极成一夹角设置,这样可以减小像素电极与公共电极的交叠面积,从而能够降低ADS模式显示器的存储电容。

[0008] 较佳地,所述公共电极为狭缝状电极。

[0009] 较佳地,所述公共电极包括沿同一方向延伸的多条第一条状电极。

[0010] 较佳地,每一所述第一条状电极的宽度大于或等于2微米且小于或等于10微米,相邻的两个所述第一条状电极之间的间距大于或等于2微米且小于或等于10微米。

[0011] 较佳地,所述像素电极为狭缝状电极。

[0012] 较佳地,所述像素电极包括沿同一方向延伸的多条第二条状电极。

[0013] 较佳地,每一所述第二条状电极的宽度大于或等于2微米且小于或等于5微米,相邻的两个所述第二条状电极之间的间距大于或等于4微米且小于或等于10微米。

[0014] 较佳地,所述公共电极与所述像素电极之间的夹角大于或等于5度且小于或等于85度。

[0015] 本申请实施例提供的一种液晶显示面板,包括本申请实施例提供的上述的阵列基板。

[0016] 由于本申请实施例提供的液晶显示面板,采用上述的阵列基板,而上述的阵列基板包括:衬底基板、在所述衬底基板上交叉布置的扫描线、数据线,以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元,所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极,并且,所述公共电极与所述像素电极成一夹角设置,这样可以减小像素电极与公共电极的交叠面积,从而能够降低ADS模式显示器的存储电容。

[0017] 本申请实施例提供的一种显示装置,包括本申请实施例提供的上述的液晶显示面板。

[0018] 由于本申请实施例提供的显示装置,采用上述的液晶显示面板,并且,液晶显示面板采用上述的阵列基板,而上述的阵列基板包括:衬底基板、在所述衬底基板上交叉布置的扫描线、数据线,以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元,所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极,并且,所述公共电极与所述像素电极成一夹角设置,这样可以减小像素电极与公共电极的交叠面积,从而能够降低ADS模式显示器的存储电容。

## 附图说明

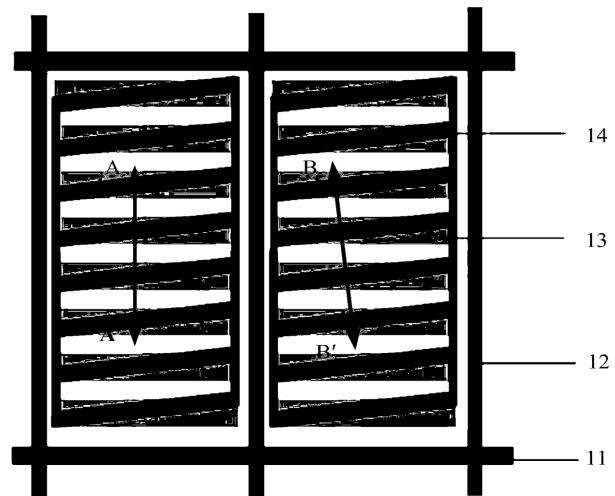

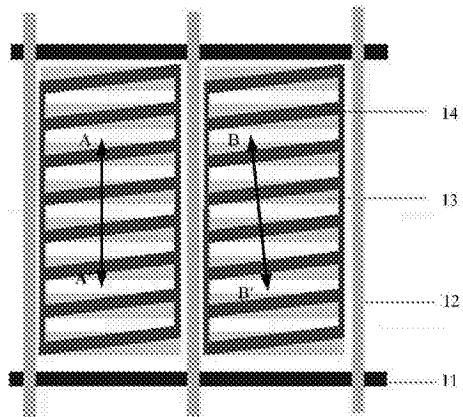

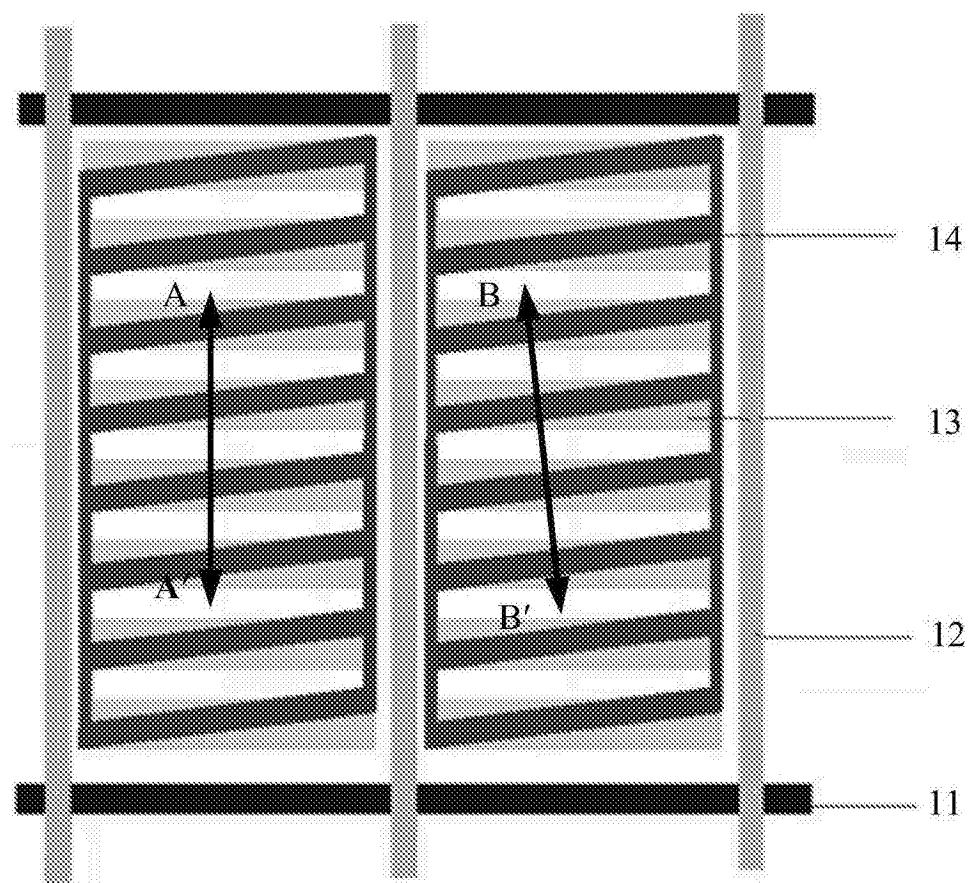

[0019] 图1为本申请实施例提供的阵列基板的平面结构示意图;

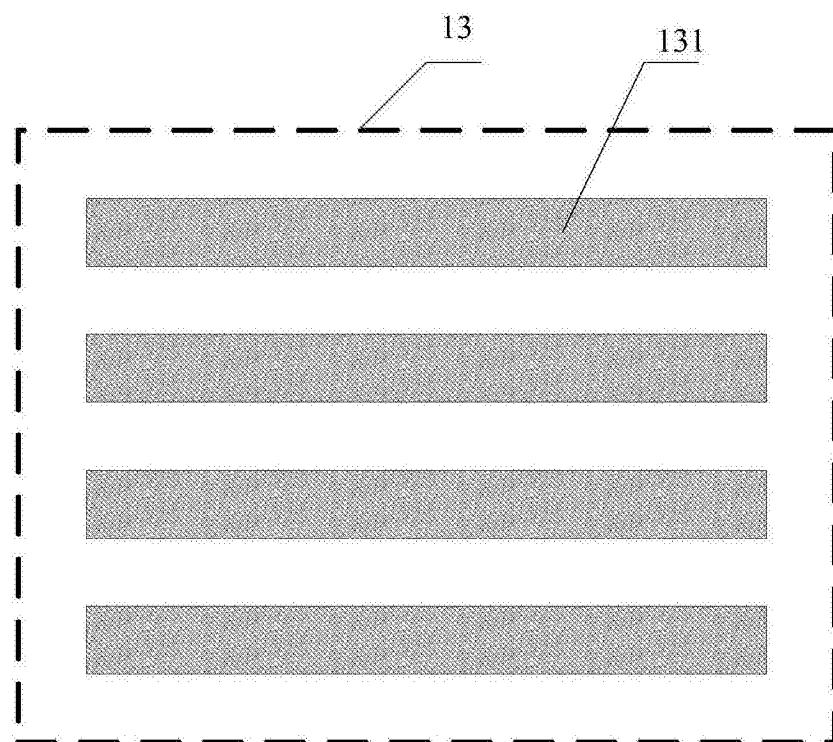

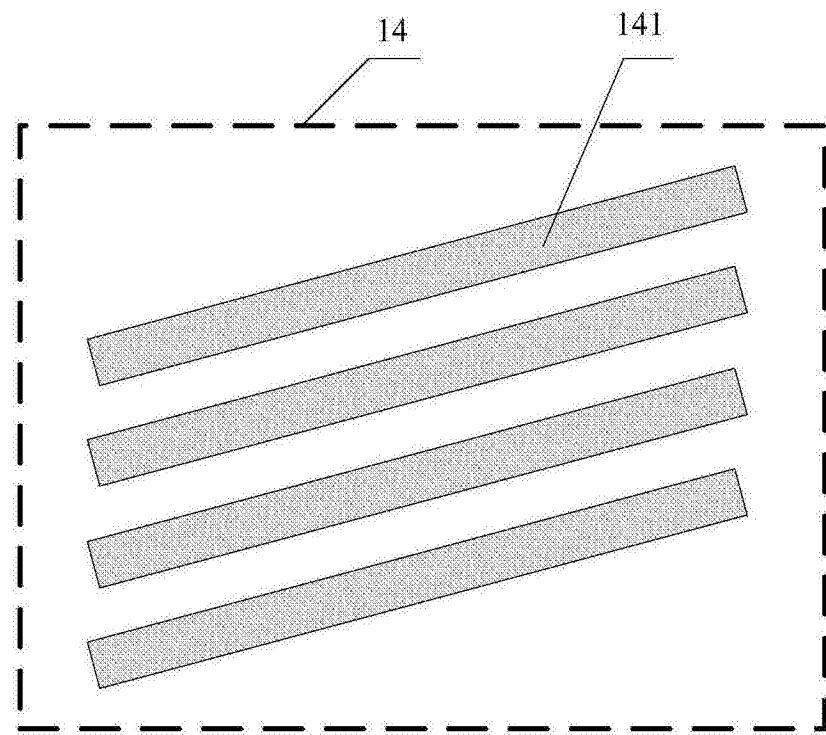

[0020] 图2为本申请实施例提供的狭缝状公共电极结构示意图;

[0021] 图3为本申请实施例提供的狭缝状像素电极结构示意图;

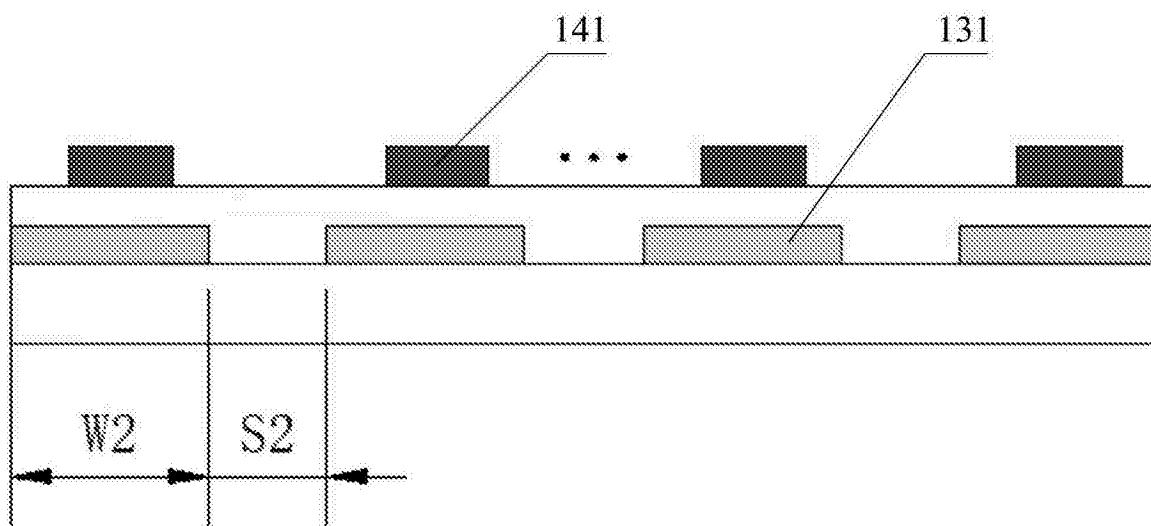

[0022] 图4为沿图1中A-A'方向的阵列基板的剖面结构示意图;

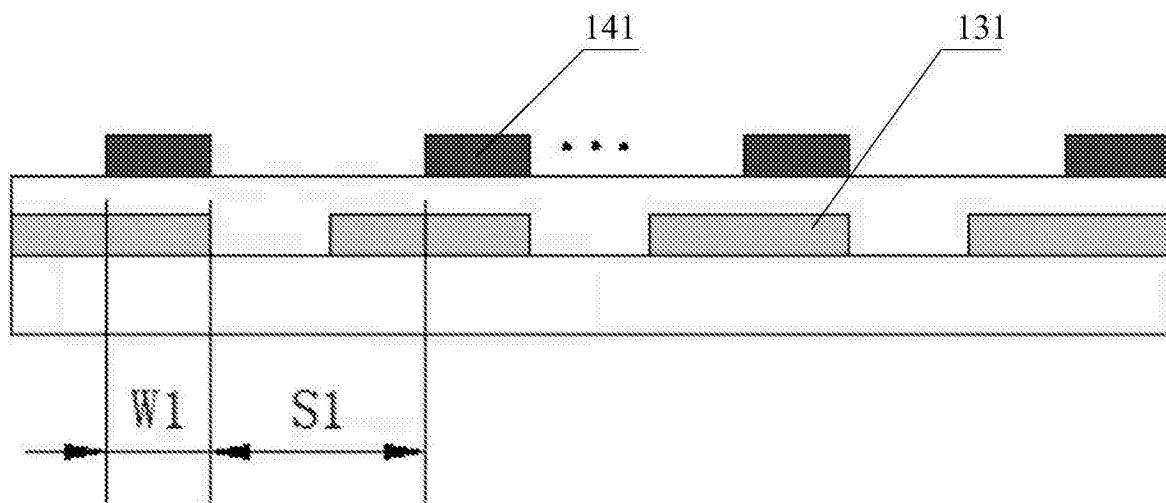

[0023] 图5为沿图1中B-B'方向的阵列基板的剖面结构示意图;

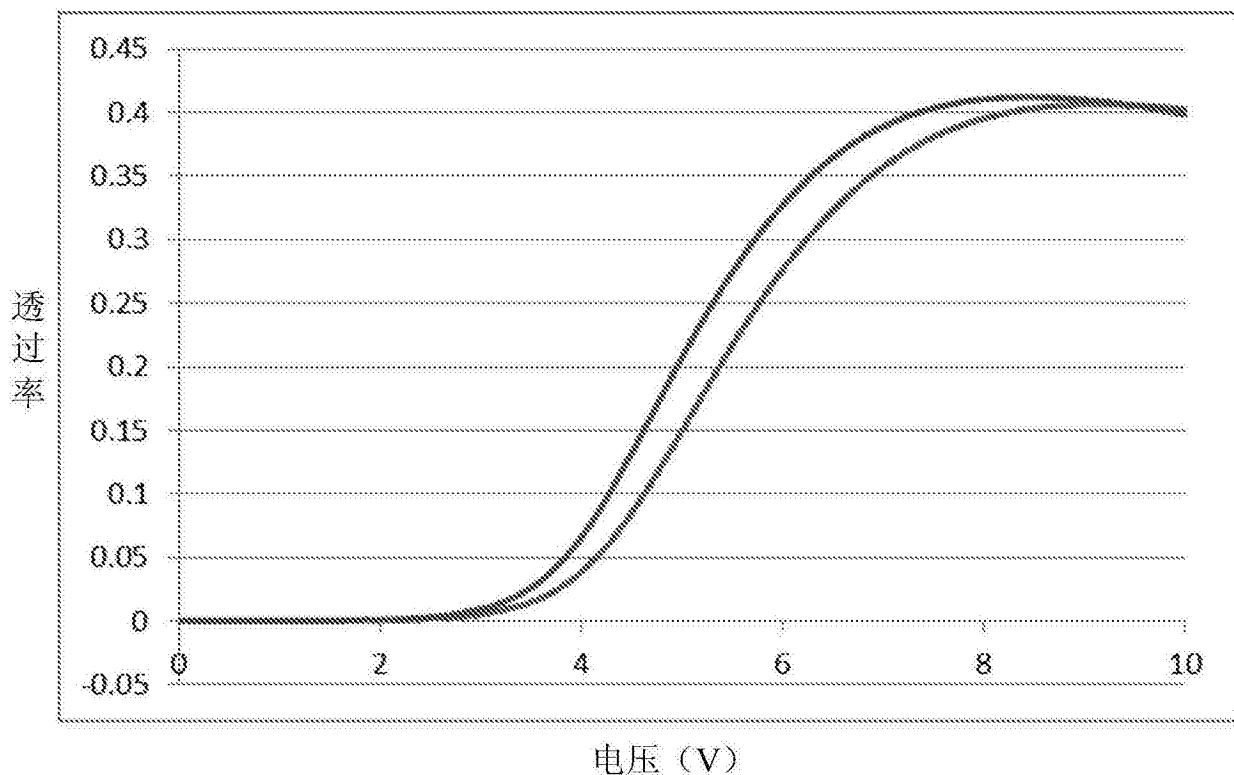

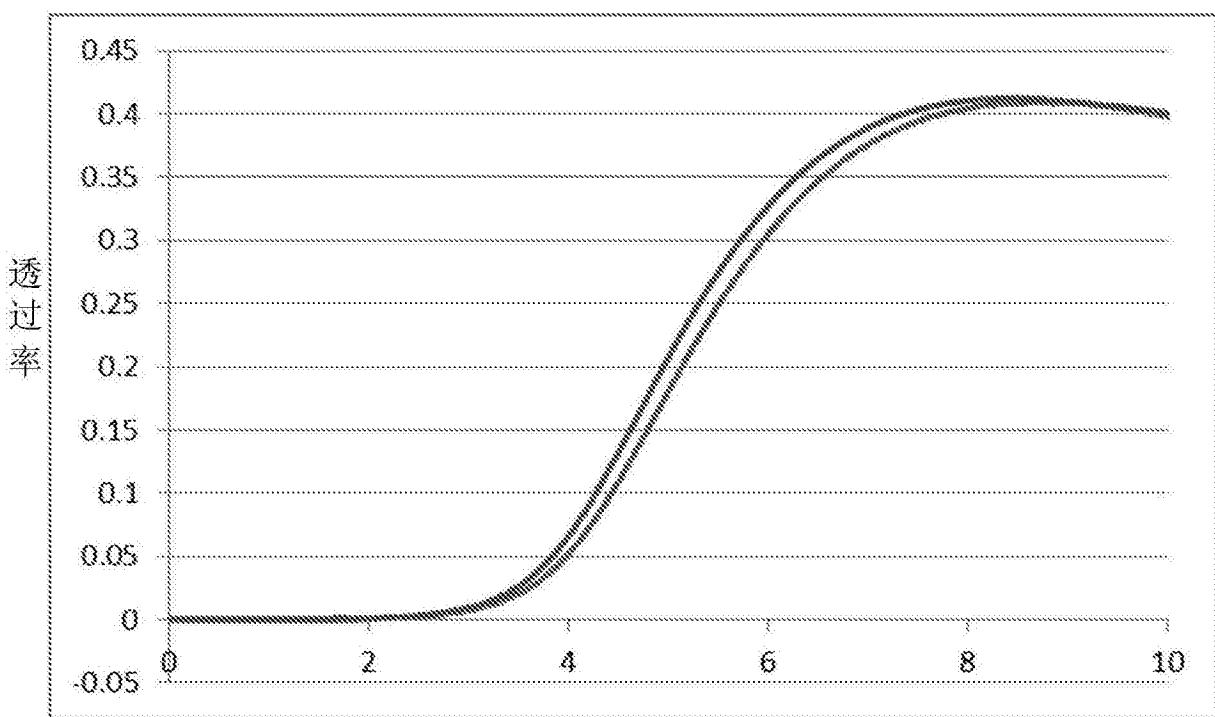

[0024] 图6为本申请实施例提供的一种透过率随电压变化的曲线图;

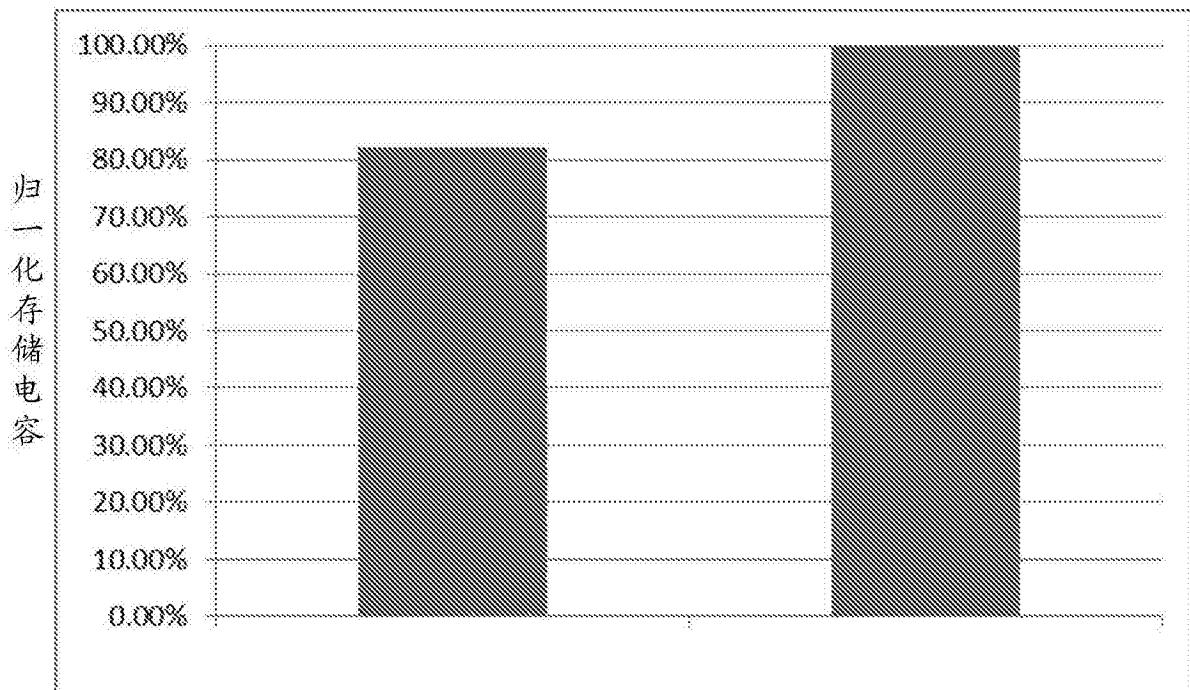

[0025] 图7为本申请实施例提供的一种归一化存储电容的柱形图;

[0026] 图8为本申请实施例提供的另一种透过率随电压变化的曲线图;

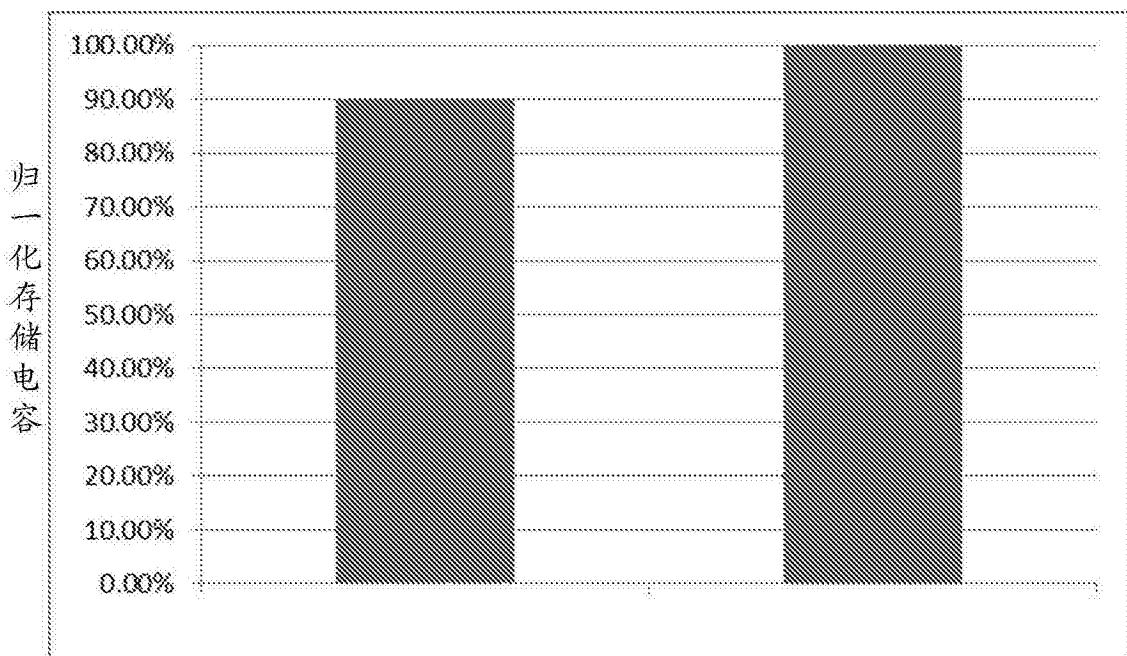

[0027] 图9为本申请实施例提供的另一种归一化存储电容的柱形图;

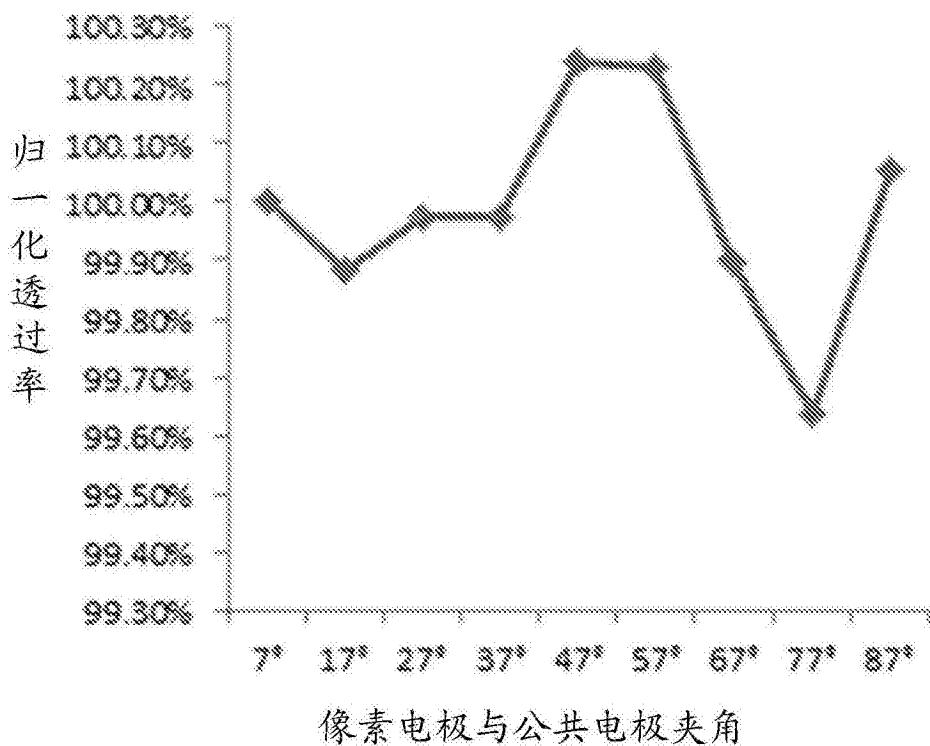

[0028] 图10为本申请实施例提供的一种归一化透过率随像素电极与公共电极夹角变化的曲线图;

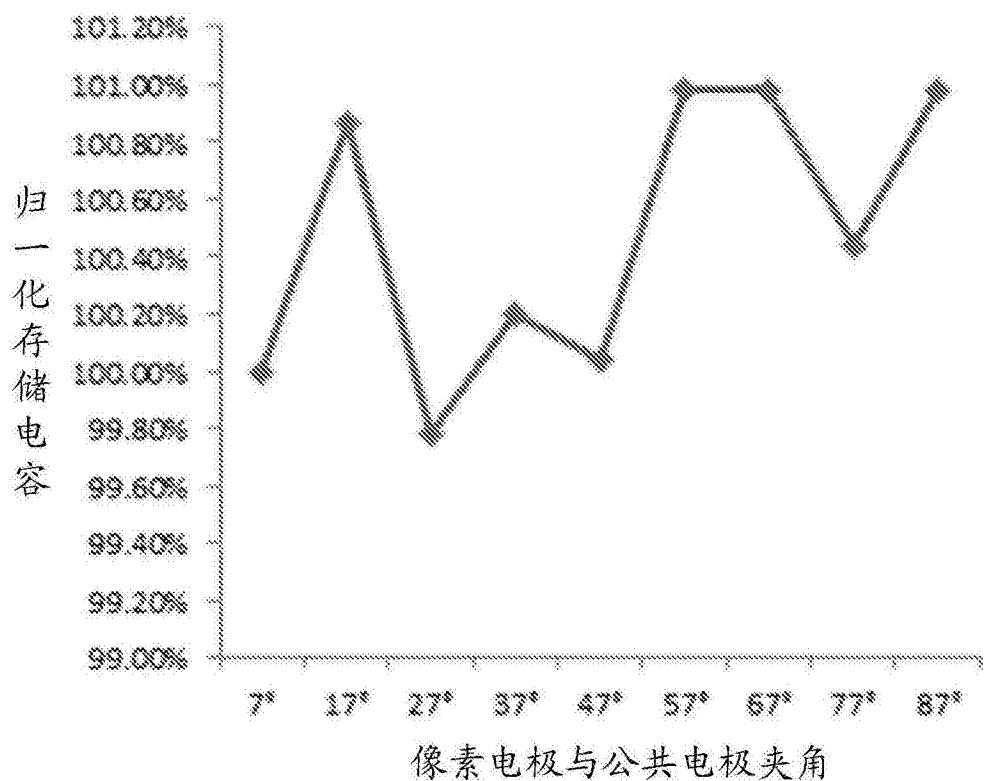

[0029] 图11为本申请实施例提供的一种归一化存储电容随像素电极与公共电极夹角变化的曲线图。

## 具体实施方式

[0030] 本申请实施例提供了一种阵列基板、液晶显示面板及显示装置,用以降低ADS模式显示器的存储电容。

[0031] 下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员所获得的所有其他实施例,都属于本申请保护的范围。

[0032] 需要说明的是,本申请实施例提供的技术方案和附图中的各结构仅是用于解释本申请,并不用于限定本申请,且附图中各膜层的比例和大小不代表真实的比例和大小。

[0033] 本申请实施例提供的一种阵列基板,参见图1,图1为本申请实施例提供的阵列基板的平面结构示意图,该阵列基板包括:衬底基板(并未在图1中示出)、在该衬底基板上交叉布置的扫描线11、数据线12,以及由扫描线11和数据线12划分出的呈矩阵排列的像素单元,该像素单元内设置有公共电极13和位于公共电极13之上的像素电极14,其中,公共电极13与像素电极14成一夹角设置。通过这种设置,可以减小像素电极14与公共电极13的交叠面积,从而能够降低ADS模式显示器的存储电容。

[0034] 其中,公共电极13与像素电极14之间的夹角为 $\theta$ , $\theta$ 可以大于或等于1度且小于或等于89度,可以表示为 $1^\circ \leq \theta \leq 89^\circ$ ,较佳地, $\theta$ 的取值可以为 $5^\circ \leq \theta \leq 85^\circ$ 。

[0035] 扫描线11的制作材料一般为铬(Cr)、钨(W)、钛(Ti)、钼(Mo)、铝(Al)、铜(Cu)等非透明金属及其合金。

[0036] 数据线12的制作材料一般为非透明的金属材料或其合金。

[0037] 较佳地,像素电极14与公共电极13为透明金属氧化物膜层,例如可以为铟锡氧化物ITO或铟锌氧化物IZO等。

[0038] 较佳地,公共电极13可以为狭缝状电极,参见图2,图2为本申请实施例提供的狭缝状公共电极结构示意图,图2中虚线框表示公共电极13,该公共电极13包括沿同一方向延伸的多条第一条状电极131,多条第一条状电极131相互平行排列,相邻的两条第一条状电极131之间的间距可以相同。

[0039] 较佳地,像素电极14可以为狭缝状电极,参见图3,图3为本申请实施例提供的狭缝状像素电极结构示意图,图3中虚线框表示像素电极14,该像素电极14包括沿同一方向延伸的多条第二条状电极141,多条第二条状电极141相互平行排列,相邻的两条第二条状电极141之间的间距也可以相同。

[0040] 当然,本申请实施例提供的公共电极13和像素电极14也可为其它的结构,例如,公共电极为板状电极,本申请实施例并不限定其结构。

[0041] 较佳地,参见图4,图4为沿图1中A-A'方向的阵列基板的剖面结构示意图,每一第一条状电极131的宽度为W2,W2可以大于或等于2微米且小于或等于10微米,可以表示为 $2\mu\text{m} \leq W2 \leq 10\mu\text{m}$ ,相邻的两个第一条状电极131之间的间距为S2,S2可以大于或等于2微米且小于或等于10微米,可以表示为 $2\mu\text{m} \leq S2 \leq 10\mu\text{m}$ 。

[0042] 较佳地,参见图5,图5为沿图1中B-B'方向的阵列基板的剖面结构示意图,每一第二条状电极141的宽度为W1,W1可以大于或等于2微米且小于或等于5微米,可以表示为 $2\mu\text{m} \leq W1 \leq 5\mu\text{m}$ 。

$\leq W1 \leq 5\mu\text{m}$ , 相邻的两个第二条状电极141之间的间距S1, S1可以大于或等于4微米且小于或等于10微米, 可以表示为 $4\mu\text{m} \leq S1 \leq 10\mu\text{m}$ 。

[0043] 下面以第一条状电极的宽度W2、相邻的两个第一条状电极之间的间距S2、第二条状电极的宽度W1、相邻的两个第二条状电极之间的间距S1、公共电极与像素电极之间的夹角 $\theta$ 分别取不同的值为例, 并结合ADS模式液晶显示器的电光特性曲线图来说明本申请实施例提供的技术方案。

[0044] 实施方式一:

[0045] 当第一条状电极的宽度 $W2=5\mu\text{m}$ , 间隔 $S2=3\mu\text{m}$ , 第二条状电极的宽度 $W1=2.6\mu\text{m}$ , 间隔 $S1=5.4\mu\text{m}$ , 公共电极与像素电极之间的夹角 $\theta=7^\circ$ 时, ADS模式液晶显示器的电光特性曲线图如图6、图7所示, 图6为本申请实施例提供的一种透过率随电压变化的曲线图, 横坐标表示电压, 单位为伏特(V), 纵坐标表示透过率, 图6中左边曲线为公共电极与像素电极为原结构时(即 $\theta=0^\circ$ 时)的透过率随电压变化的曲线, 图6中右边曲线为公共电极与像素电极为本申请实施方式一提供的结构时透过率随电压变化的曲线, 图7为本申请实施例提供的一种归一化存储电容的柱形图, 纵坐标表示归一化存储电容, 图7中左边柱形为公共电极与像素电极为本申请实施方式一提供的结构时的归一化存储电容, 图7中右边柱形为公共电极与像素电极为原结构时(即 $\theta=0^\circ$ 时)的归一化存储电容, 从图6和图7中可以看出, 本申请实施方式一提供的公共电极与像素电极结构, 相对于原结构的公共电极与像素电极结构, ADS模式液晶显示器的驱动电压增大0.6V, 透过率下降1.4%, 存储电容下降18%。

[0046] 实施方式二:

[0047] 当第一条状电极的宽度 $W2=6\mu\text{m}$ , 间隔 $S2=2\mu\text{m}$ , 第二条状电极的宽度 $W1=2.6\mu\text{m}$ , 间隔 $S1=5.4\mu\text{m}$ , 公共电极与像素电极之间的夹角 $\theta=7^\circ$ 时, ADS模式液晶显示器的电光特性曲线图如图8、图9所示, 图8为本申请实施例提供的另一种透过率随电压变化的曲线图, 横坐标表示电压, 单位为伏特(V), 纵坐标表示透过率, 图8中左边曲线为公共电极与像素电极为原结构时(即 $\theta=0^\circ$ 时)的透过率随电压变化的曲线, 图8中右边曲线为公共电极与像素电极为本申请实施方式二提供的结构时透过率随电压变化的曲线, 图9为本申请实施例提供的另一种归一化存储电容的柱形图, 纵坐标表示归一化存储电容, 图9中左边柱形为公共电极与像素电极为本申请实施方式二提供的结构时的归一化存储电容, 图9中右边柱形为公共电极与像素电极为原结构时(即 $\theta=0^\circ$ 时)的归一化存储电容, 从图8和图9中可以看出, 本申请实施方式二提供的公共电极与像素电极结构, 相对于原结构的公共电极与像素电极结构, ADS模式液晶显示器的驱动电压增大0.2V, 透过率下降0.7%, 存储电容下降10%。

[0048] 实施方式三:

[0049] 当第一条状电极的宽度 $W2=5\mu\text{m}$ , 间隔 $S2=3\mu\text{m}$ , 第二条状电极的宽度 $W1=2.6\mu\text{m}$ , 间隔 $S1=5.4\mu\text{m}$ , 公共电极与像素电极之间的夹角 $\theta$ 发生变化时, 透过率和存储电容的变化曲线分别如图10、图11所示, 图10为本申请实施例提供的一种归一化透过率随像素电极与公共电极夹角变化的曲线图, 横坐标表示像素电极与公共电极夹角, 单位为度( $^\circ$ ), 纵坐标表示归一化透过率, 其中, 归一化透过率指将像素电极与公共电极夹角为 $7^\circ$ 获得的透过率作为参考, 其它角度获得的透过率与其的比值, 图10中从左到右的黑点分别表示像素电极与公共电极夹角 $\theta$ 为 $7^\circ$ 、 $17^\circ$ 、 $27^\circ$ 、 $37^\circ$ 、 $47^\circ$ 、 $57^\circ$ 、 $67^\circ$ 、 $77^\circ$ 、 $87^\circ$ 时的归一化透过率; 图11为本申请实施例提供的一种归一化存储电容随像素电极与公共电极夹角变化的曲线图, 横坐标

表示像素电极与公共电极夹角,单位为度( $^{\circ}$ ),纵坐标表示归一化存储电容,其中,归一化存储电容指将像素电极与公共电极夹角为 $7^{\circ}$ 获得的存储电容作为参考,其它角度获得的存储电容与其的比值,图11中从左到右的黑点分别表示像素电极与公共电极夹角 $\theta$ 为 $7^{\circ}$ 、 $17^{\circ}$ 、 $27^{\circ}$ 、 $37^{\circ}$ 、 $47^{\circ}$ 、 $57^{\circ}$ 、 $67^{\circ}$ 、 $77^{\circ}$ 、 $87^{\circ}$ 时的归一化存储电容。

[0050] 需要指出的是,在实际应用时,当第一条状电极与第二条状电极的宽度、间隔一定时,可以由模拟软件优化像素电极与公共电极夹角 $\theta$ ,使得ADS模式显示器的存储电容最小,然后根据优化后的夹角 $\theta$ 制备ADS模式显示器。

[0051] 基于同一发明构思,本申请实施例还提供了一种液晶显示面板,该液晶显示面板包括本申请实施例提供的上述的阵列基板。

[0052] 由于本申请实施例提供的液晶显示面板,采用上述的阵列基板,而上述的阵列基板包括:衬底基板、在所述衬底基板上交叉布置的扫描线、数据线,以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元,所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极,并且,所述公共电极与所述像素电极成一夹角设置,这样可以减小像素电极与公共电极的交叠面积,从而能够降低ADS模式显示器的存储电容。

[0053] 基于同一发明构思,本申请实施例还提供了一种显示装置,该显示装置包括本申请实施例提供的上述的液晶显示面板。该显示装置可以为液晶显示器、液晶电视等。

[0054] 由于本申请实施例提供的显示装置,采用上述的液晶显示面板,并且,液晶显示面板采用上述的阵列基板,而上述的阵列基板包括:衬底基板、在所述衬底基板上交叉布置的扫描线、数据线,以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元,所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极,并且,所述公共电极与所述像素电极成一夹角设置,这样可以减小像素电极与公共电极的交叠面积,从而能够降低ADS模式显示器的存储电容。

[0055] 综上所述,本申请实施例提供的技术方案,阵列基板包括:衬底基板、在所述衬底基板上交叉布置的扫描线、数据线,以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元,所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极,并且,所述公共电极与所述像素电极成一夹角设置,这样可以减小像素电极与公共电极的交叠面积,从而能够降低ADS模式显示器的存储电容。

[0056] 显然,本领域的技术人员可以对本申请进行各种改动和变型而不脱离本申请的精神和范围。这样,倘若本申请的这些修改和变型属于本申请权利要求及其等同技术的范围之内,则本申请也意图包含这些改动和变型在内。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

|                |                                                     |         |            |

|----------------|-----------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种阵列基板、液晶显示面板及显示装置                                  |         |            |

| 公开(公告)号        | <a href="#">CN105700259A</a>                        | 公开(公告)日 | 2016-06-22 |

| 申请号            | CN201610239613.X                                    | 申请日     | 2016-04-18 |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司<br>重庆京东方光电科技有限公司                      |         |            |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司<br>重庆京东方光电科技有限公司                      |         |            |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司<br>重庆京东方光电科技有限公司                      |         |            |

| [标]发明人         | 栗鹏<br>金熙哲<br>朴正淏<br>金在光                             |         |            |

| 发明人            | 栗鹏<br>金熙哲<br>朴正淏<br>金在光                             |         |            |

| IPC分类号         | G02F1/1362 G02F1/1343                               |         |            |

| CPC分类号         | G02F1/136213 G02F1/134309 G02F2201/121 G02F2201/123 |         |            |

| 代理人(译)         | 黄志华                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>      |         |            |

## 摘要(译)

本申请提供了一种阵列基板、液晶显示面板及显示装置，用以降低ADS模式显示器的存储电容，本申请提供的一种阵列基板包括：衬底基板、在所述衬底基板上交叉布置的扫描线、数据线，以及由所述扫描线和数据线划分出的呈矩阵排列的像素单元，所述像素单元内设置有公共电极和位于所述公共电极之上的像素电极，其中，所述公共电极与所述像素电极成一夹角设置。