## (12)发明专利申请

(10) 申请公布号 CN 110703515 A

(43)申请公布日 2020.01.17

(21)申请号 201910935905.0

(22)申请日 2019.09.29

(71)申请人 深圳市华星光电半导体显示技术有限公司

地址 518132 广东省深圳市光明新区公明

街道塘明大道9-2号

(72)发明人 汤爱华

(74)专利代理机构 深圳翼盛智成知识产权事务所(普通合伙) 44300

代理人 汪阮磊

(51) Int. Cl.

G02F 1/1343(2006.01)

权利要求书1页 说明书4页 附图4页

(54)发明名称

## 显示面板及其制作方法

## (57) 摘要

本发明提供一种显示面板及其制作方法，所述显示面板包括相对设置的阵列基板及彩膜基板、以及设于阵列基板与彩膜基板之间的液晶层；所述阵列基板包括透明电极层；所述透明电极层包括间隔的像素电极以及DBS电极，所述DBS电极相对于像素电极的高度低0到1微米。通过降低DBS电极相对于像素电极的垂直高度，可有效压缩数据线的电场范围，显著降低数据线上下视角的漏光问题，改善垂直串扰的问题，且不使开口率下降。

1. 一种显示面板，其特征在于，所述显示面板包括相对设置的阵列基板及彩膜基板、以及设于所述阵列基板与所述彩膜基板之间的液晶层；所述阵列基板包括TFT层以及设于所述TFT层与所述液晶层之间的透明电极层；所述TFT层包括阵列排布的多个TFT、多列数据线、多行扫描线、以及阵列基板公共电极，所述TFT连接所述数据线和所述扫描线，所述透明电极层包括间隔的像素电极以及DBS电极，所述像素电极与所述TFT连接，所述DBS电极覆盖所述数据线；所述彩膜基板靠近所述液晶层一侧设有彩膜基板公共电极；所述DBS电极与所述阵列基板公共电极相连；

其中，所述DBS电极相对于所述像素电极的高度低0到1微米。

2. 根据权利要求1所述的显示面板，其特征在于，所述DBS电极与所述像素电极的高度一致。

3. 根据权利要求1所述的显示面板，其特征在于，所述DBS电极的高度比所述像素电极的高度低0.2微米。

4. 根据权利要求1所述的显示面板，其特征在于，所述DBS电极的高度比所述像素电极的高度低0.5微米。

5. 根据权利要求1所述的显示面板，其特征在于，所述DBS电极的高度比所述像素电极的高度低1微米。

6. 一种显示面板的制作方法，其特征在于，包括以下步骤：

步骤S1、提供阵列基板；

其中所述阵列基板包括阵列基板衬底，在所述阵列基板衬底上制作TFT层，在所述TFT层上制作像素电极和DBS电极；

其中，在制作所述像素电极和所述DBS电极时采用半透膜光罩，所述半透膜光罩中全透部对应所述像素电极的导通孔，所述半透膜光罩中半透膜部对应所述DBS电极；

步骤S2、提供彩膜基板；

其中，所述彩膜基板包括彩膜基板衬底，彩膜基板公共电极层设于所述彩膜基板衬底上，且所述彩膜基板衬底与所述彩膜基板公共电极层之间还设有彩色光阻层；以及

步骤S3、在所述阵列基板和所述彩膜基板之间注入液晶，形成液晶层。

7. 根据权利要求6所述的显示面板的制作方法，其特征在于，在步骤S1中，控制半透膜光罩的透光率，使所述像素电极与所述DBS电极的高度一致。

8. 根据权利要求6所述的显示面板的制作方法，其特征在于，在步骤S1中，控制半透膜光罩的透光率，使所述DBS电极的高度比所述像素电极的高度低0.2微米。

9. 根据权利要求6所述的显示面板的制作方法，其特征在于，在步骤S1中，控制半透膜光罩的透光率，使所述DBS电极的高度比所述像素电极的高度低0.5微米。

10. 根据权利要求6所述的显示面板的制作方法，其特征在于，在步骤S1中，控制半透膜光罩的透光率，使所述DBS电极的高度比所述像素电极的高度低1微米。

## 显示面板及其制作方法

### 技术领域

[0001] 本发明涉及显示技术领域,尤其涉及一种显示面板及其制作方法。

### 背景技术

[0002] 液晶显示器(Liquid Crystal Display,LCD)具有机身薄、省电、无辐射等众多优点,得到了广泛的应用,在平板显示领域中占主导地位。现有市场上的液晶显示器大部分为背光型液晶显示器,其包括液晶显示面板及背光模组(backlight module)。液晶显示面板的工作原理是在薄膜晶体管阵列基板(thin film transistor array substrate,TFT array substrate)与彩色滤光片基板(Color Filter,CF)之间灌入液晶分子,并在两片基板上施加驱动电压来控制液晶分子的旋转方向,以将背光模组的光线折射出来产生画面。

[0003] 传统的液晶显示面板需要在彩膜基板一侧设置黑色矩阵(black matrix,BM)以进行遮光,当应用于曲面液晶显示面板时,对面板进行弯曲会使BM的位置产生偏移(shift)而导致漏光及色偏,为解决这一问题,现有技术采用减少数据线上的黑色矩阵(data line BM less, DBS)的设计。它是在数据线上方覆盖以ITO(即氧化铟锡)的走线,ITO走线的宽度略宽于数据线,这些ITO走线连接COM即公共电极,在面板正常工作时,这些ITO COM电极形成的电场可以使液晶分子保持不偏转的状态,从而起到遮光的目的。

[0004] 为提高开口率,在设计面板产品时往往会选择去掉子像素处的屏蔽金属,仅靠DBS电极来遮蔽数据线上方的漏光。而这种设计通常会出现DBS电极覆盖不充分的问题,导致面板产生漏光的风险。

### 发明内容

[0005] 本发明提供一种显示面板及制作方法,通过降低DBS电极与像素电极的相对高度能有效减小其两侧漏光,改善上下视角垂直区块的串扰。

[0006] 为解决上述问题,本发明提供的技术方案如下:

[0007] 本发明提供一种显示面板,所述显示面板包括相对设置的阵列基板及彩膜基板、以及设于所述阵列基板与所述彩膜基板之间的液晶层;所述阵列基板包括TFT层以及设于所述TFT层与所述液晶层之间的透明电极层;所述TFT层包括阵列排布的多个TFT、多列数据线、多行扫描线、以及阵列基板公共电极,所述TFT连接所述数据线和所述扫描线,所述透明电极层包括间隔的像素电极以及DBS电极,所述像素电极与所述TFT连接,所述DBS电极覆盖所述数据线;所述彩膜基板靠近所述液晶层一侧设有彩膜基板公共电极;所述DBS电极与阵列基板公共电极相连;

[0008] 其中,所述DBS电极相对于所述像素电极的高度低0到1微米。

[0009] 根据本发明实施例所提供的显示面板,所述DBS电极与所述像素电极的高度一致。

[0010] 根据本发明实施例所提供的显示面板,所述DBS电极的高度比所述像素电极的高度低0.2微米。

[0011] 根据本发明实施例所提供的显示面板,所述DBS电极的高度比所述像素电极的高

度低0.5微米。

[0012] 根据本发明实施例所提供的显示面板，所述DBS电极的高度比所述像素电极的高度低1微米。

[0013] 本发明实施例还提供了一种显示面板的制作方法，包括以下步骤：

[0014] 步骤S1、提供阵列基板；

[0015] 其中所述阵列基板包括阵列基板衬底，在所述阵列基板衬底上制作TFT层，在所述TFT层上制作像素电极和DBS电极；

[0016] 其中，在制作所述像素电极和所述DBS电极时采用半透膜光罩，所述半透膜光罩中全透部对应所述像素电极的导通孔，所述半透膜光罩中半透膜部对应所述DBS电极；

[0017] 步骤S2、提供彩膜基板；

[0018] 其中，所述彩膜基板包括彩膜基板衬底，彩膜基板公共电极层设于所述彩膜基板衬底上，且所述彩膜基板衬底与所述彩膜基板公共电极层之间还设有彩色光阻层；以及

[0019] 步骤S3、在所述阵列基板和所述彩膜基板之间注入液晶，形成液晶层。

[0020] 根据本发明实施例所提供的显示面板的制作方法，在步骤S1中，控制半透膜光罩的透光率，使所述像素电极与所述DBS电极的高度一致。

[0021] 根据本发明实施例所提供的显示面板的制作方法，在步骤S1中，控制半透膜光罩的透光率，使所述DBS电极的高度比所述像素电极的高度低0.2微米。

[0022] 根据本发明实施例所提供的显示面板的制作方法，在步骤S1中，控制半透膜光罩的透光率，使所述DBS电极的高度比所述像素电极的高度低0.5微米。

[0023] 根据本发明实施例所提供的显示面板的制作方法，在步骤S1中，控制半透膜光罩的透光率，使所述DBS电极的高度比所述像素电极的高度低1微米。

[0024] 本发明的有益效果为：通过降低DBS电极相对于像素电极的垂直高度，可有效压缩数据线的电场范围，显著降低数据线上下视角的漏光问题，改善垂直串扰的问题，且不使开口率下降。

## 附图说明

[0025] 为了更清楚地说明实施例或现有技术中的技术方案，下面将对实施例或现有技术描述中所需要使用的附图作简单介绍，显而易见地，下面描述中的附图仅仅是发明的一些实施例，对于本领域普通技术人员来讲，在不付出创造性劳动的前提下，还可以根据这些附图获得其他的附图。

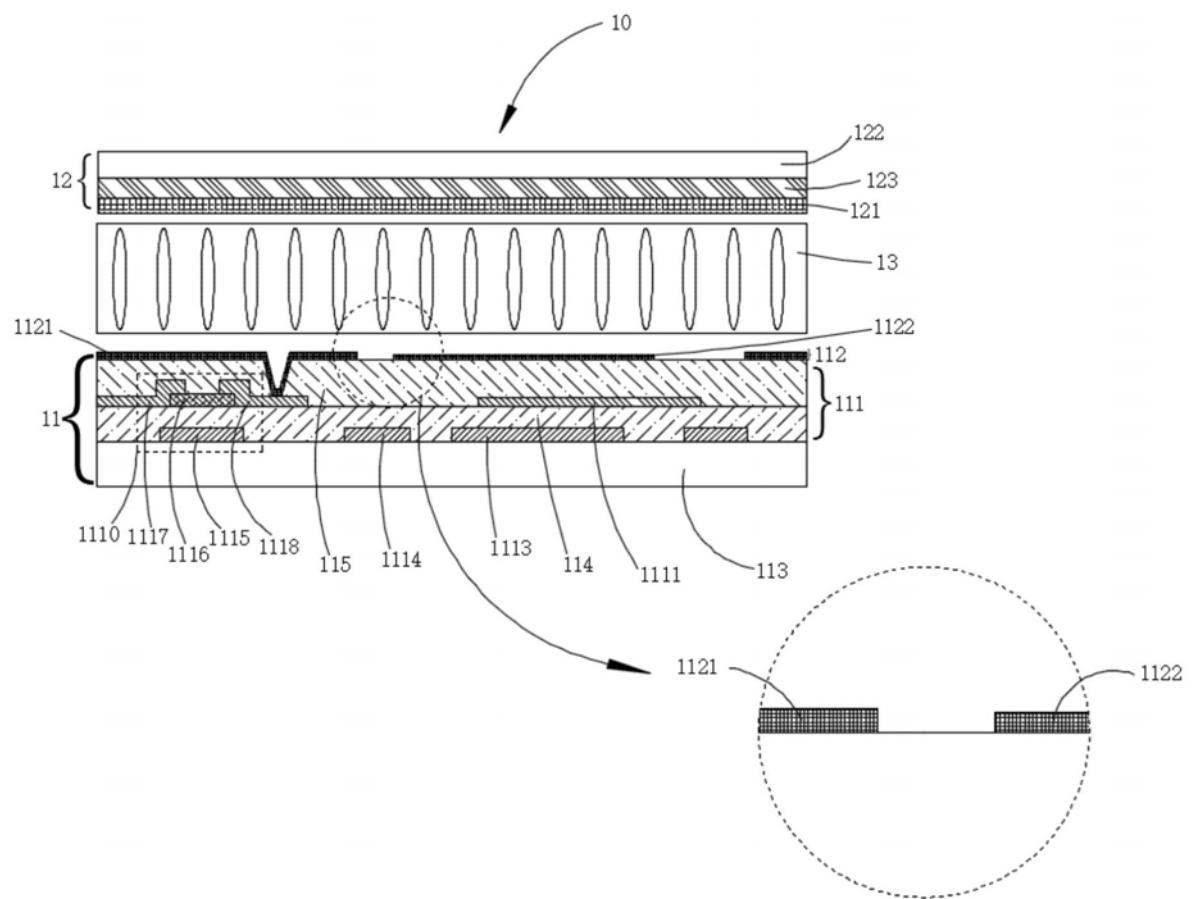

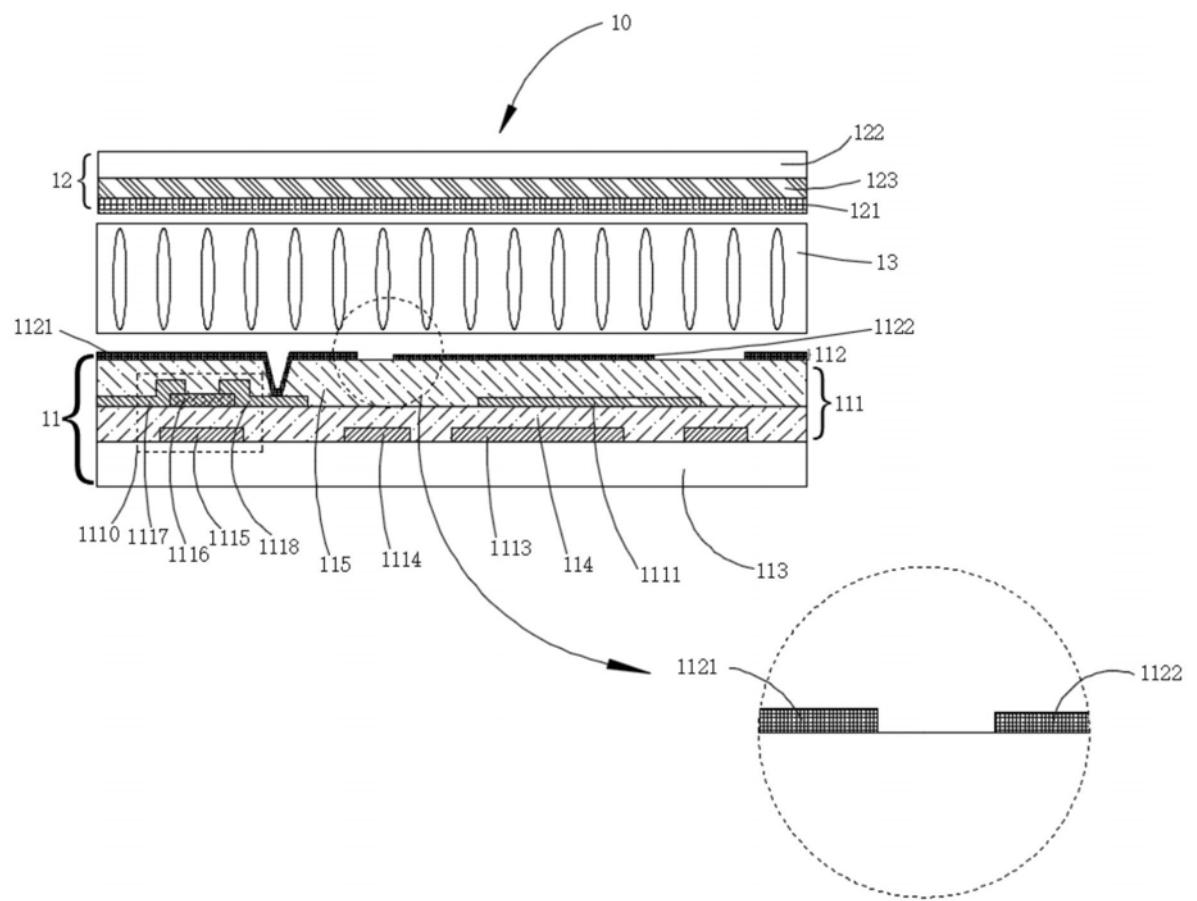

[0026] 图1为本发明实施例所提供的一种显示面板是结构示意图。

[0027] 图2为本发明实施例所提供的另一种显示面板是结构示意图。

[0028] 图3为本发明实施例所提供的另一种显示面板是结构示意图。

[0029] 图4为本发明实施例所提供的另一种显示面板是结构示意图。

## 具体实施方式

[0030] 以下各实施例的说明是参考附加的图示，用以示本发明可用以实施的特定实施例。本发明所提到的方向用语，例如[上]、[下]、[前]、[后]、[左]、[右]、[内]、[外]、[侧面]等，仅是参考附加图式的方向。因此，使用的方向用语是用以说明及理解本发明，而非用以

限制本发明。在图中,结构相似的单元是用以相同标号表示。

[0031] 本发明针对现有技术的显示面板,存在大视角垂直串扰以及视角漏光的问题,而目前可行的串扰解决方案均存在不同程度的缺陷,如增加屏蔽金属会损失开口率等问题。

[0032] 本发明提供一种显示面板及制作方法,通过降低DBS电极与像素电极的相对高度能有效减小其两侧漏光,改善上下视角垂直区块的串扰。

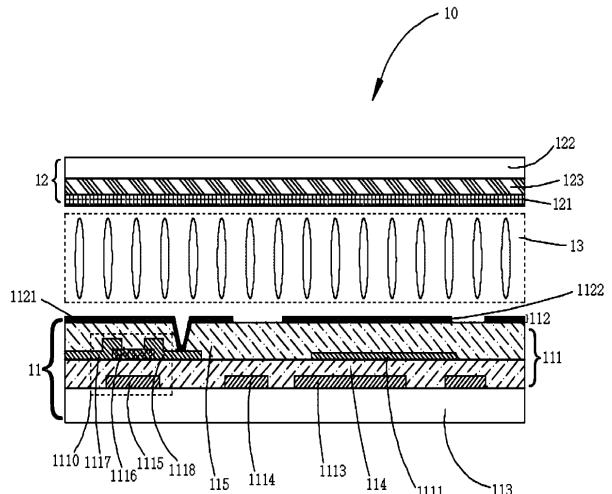

[0033] 请参阅图1,为本发明实施例所提供的一种显示面板是结构示意图。

[0034] 如图1所示,本实施例所提供的显示面板10包括相对设置的阵列基板11及彩膜基板12、以及设于阵列基板11与彩膜基板12之间的液晶层13;所述阵列基板11包括TFT层111、设于TFT层111与液晶层13之间的透明电极层112;所述TFT层111包括阵列排布的多个TFT1110、多列数据线1111、多行扫描线(图中未画出)、以及阵列基板公共电极1113,每一TFT1110均连接一数据线1111和一扫描线(图中未画出),所述透明电极层112包括间隔的像素电极1121以及DBS电极1122,所述像素电极1121与TFT1110连接,所述DBS电极1122覆盖数据线1111;所述彩膜基板12靠近液晶层13一侧设有彩膜基板公共电极121;所述显示面板10的DBS电极1122与阵列基板公共电极1113相连。

[0035] 其中,所述DBS电极1122相对于像素电极1121的高度低0到1微米。

[0036] 具体地,在本发明实施例中,显示面板10的阵列基板11中,TFT层111形成于阵列基板衬底113上,而TFT层111与透明电极层112之间设置有钝化层115。

[0037] 具体地,请参阅图1,所述TFT1110具体包括:设于阵列基板衬底113上的栅极1115、覆盖栅极1115的栅极绝缘层114、设于栅极绝缘层114上的有源层1116、设于栅极绝缘层114上且分别连接有源层1116两端的源极1117及漏极1118,像素电极1121经贯穿钝化层115的过孔与漏极1118连接。

[0038] 具体地,阵列基板公共电极1113与栅极1115均位于第一金属层,均设于阵列基板衬底113上。进一步地,所述TFT层111还包括设于阵列基板衬底113上且遮挡像素电极1121与DBS电极1122之间间隙的遮光层1114。所述遮光层1114也位于第一金属层。

[0039] 具体地,所述数据线1111与源极1117及漏极1118均位于第二金属层,均设于栅极绝缘层114上。

[0040] 具体地,在本发明实施例中,显示面板10的彩膜基板12中,彩膜基板公共电极121设于第二衬底122上,且第二衬底122与彩膜基板公共电极121之间还设有彩色光阻层123。

[0041] 如图1所示,在本实施例一中,若将所述DBS电极1122与所述像素电极1121的高度设为一致,则显示面板10的最大漏光亮度为0.000661。

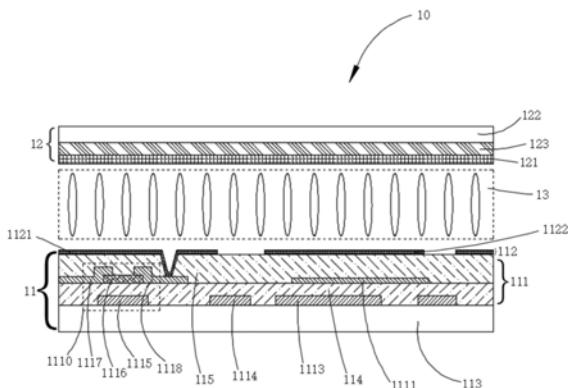

[0042] 如图2所示,降低所述DBS电极1122的高度,将所述DBS电极1122的高度设置为比所述像素电极1121的高度低0.2微米,则可将显示面板10的最大漏光亮度减小至0.000552,即显示面板10的最大漏光亮度相对于实施例一中的最大漏光亮度减小了16%。

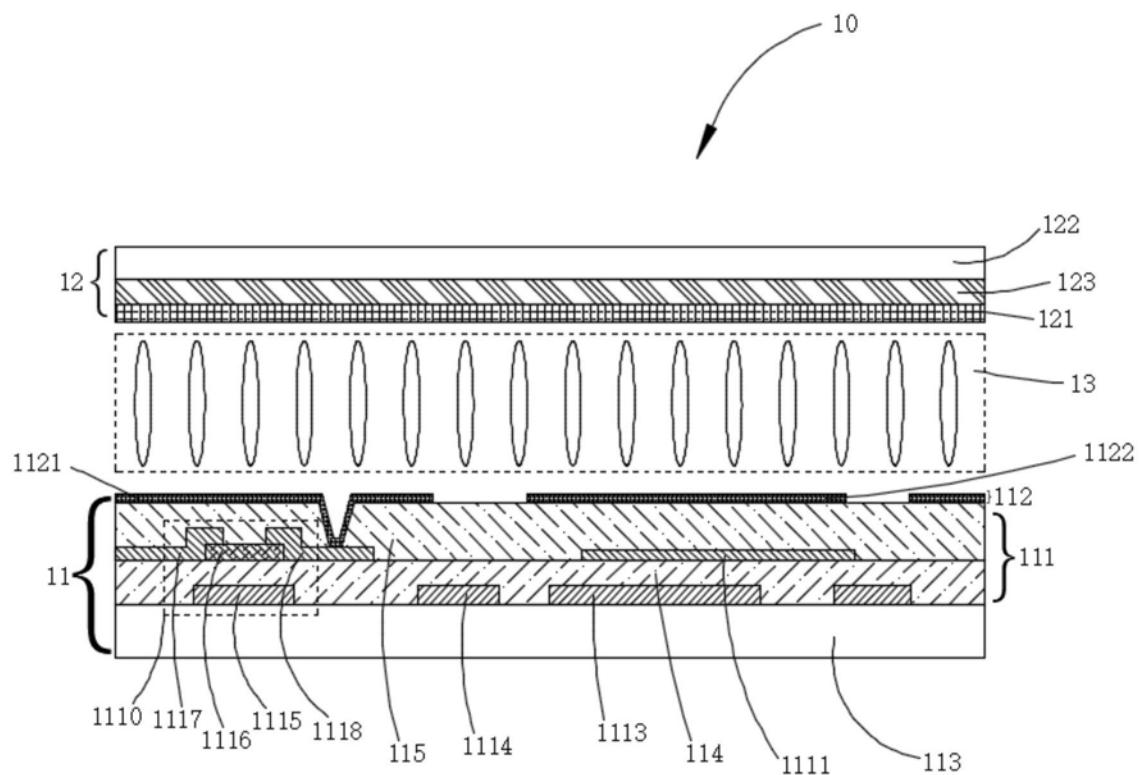

[0043] 如图3所示,降低所述DBS电极1122的高度,将所述DBS电极1122的高度设置为比所述像素电极1121的高度低0.5微米,则可将显示面板10的最大漏光亮度减小至0.000403,即显示面板10的最大漏光亮度相对于实施例一中的最大漏光亮度减小了39%。

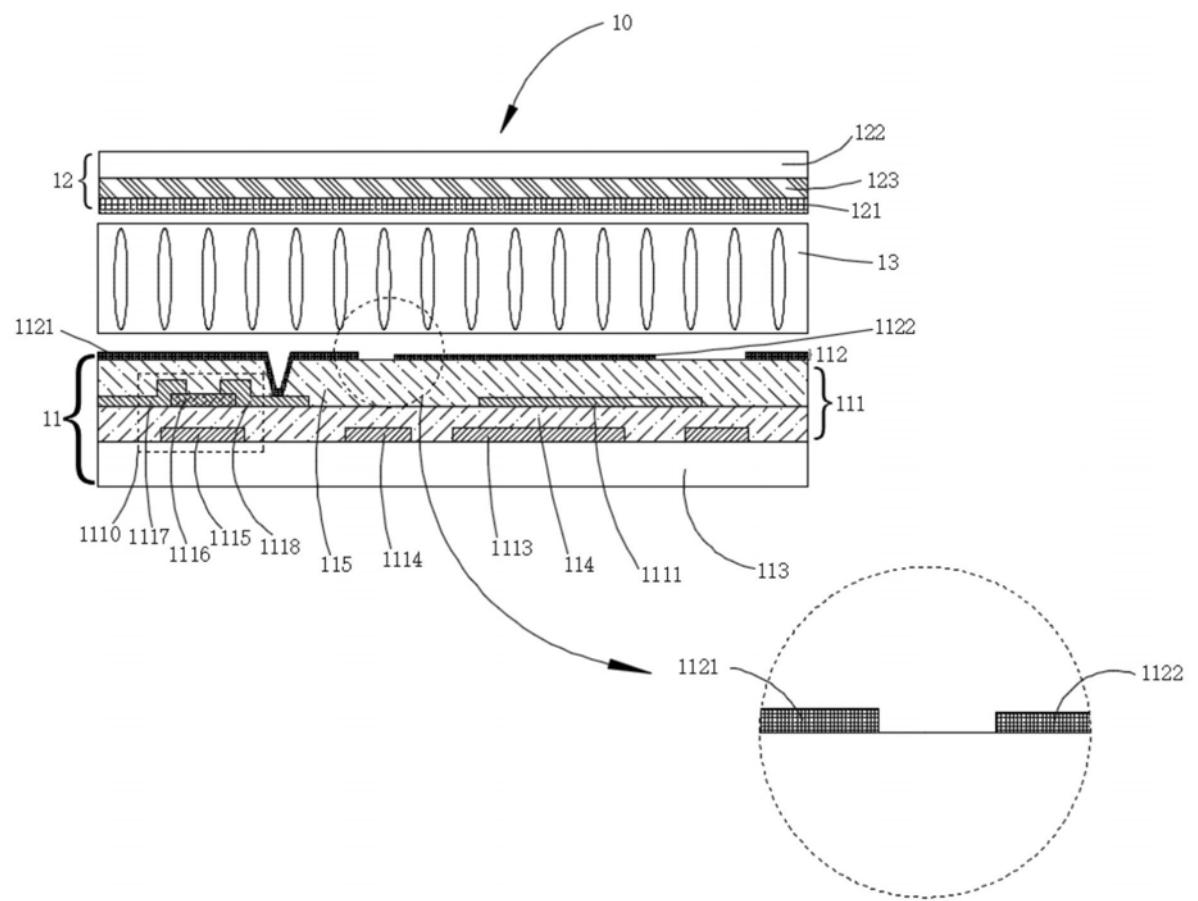

[0044] 如图4所示,降低所述DBS电极1122的高度,将所述DBS电极1122的高度设置为比所述像素电极1121的高度低1微米,则可将显示面板10的最大漏光亮度减小至0.000199,即显示面板10的最大漏光亮度相对于实施例一中的最大漏光亮度减小了70%。即通过调整DBS

电极1122与像素电极1121的相对高度,可以减小显示面板10的漏光。

[0045] 本发明实施例还提供了一种显示面板的制作方法,包括以下步骤:

[0046] 步骤S1、提供阵列基板;

[0047] 其中所述阵列基板包括阵列基板衬底,在所述阵列基板衬底上制作TFT层,在所述TFT层上制作像素电极和DBS电极;

[0048] 其中,在制作像素电极和DBS电极时采用半透膜光罩,所述半透膜光罩中全透部位对应像素电极的导通孔部位,所述半透膜光罩中半透膜部位对应DBS电极部位;

[0049] 步骤S2、提供彩膜基板;

[0050] 其中,所述彩膜基板包括彩膜基板衬底,彩膜基板公共电极层设于彩膜基板衬底上,且所述彩膜基板衬底与所述彩膜基板公共电极层之间还设有彩色光阻层;

[0051] 步骤S3、在所述阵列基板和彩膜基板之间注入液晶,形成液晶层。

[0052] 通过在步骤S1中,控制半透膜光罩的透光率,使所述DBS电极的高度与所述像素电极的高度低0到1微米。可选的不仅仅是使所述DBS电极的高度比所述像素电极的高度低0微米;使所述DBS电极的高度比所述像素电极的高度低0.2微米;使所述DBS电极的高度比所述像素电极的高度低0.5微米;使所述DBS电极的高度比所述像素电极的高度低1微米。

[0053] 有益效果为:通过降低DBS电极相对于像素电极的垂直高度,可有效压缩数据线的电场范围,显著降低数据线上下视角的漏光问题,改善垂直串扰的问题,且不使开口率下降。

[0054] 综上所述,虽然本发明已以优选实施例揭露如上,但上述优选实施例并非用以限制本发明,本领域的普通技术人员,在不脱离本发明的精神和范围内,均可作各种更动与润饰,因此本发明的保护范围以权利要求界定的范围为准。

图1

图2

图3

图4

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示面板及其制作方法                                     |         |            |

| 公开(公告)号        | <a href="#">CN110703515A</a>                   | 公开(公告)日 | 2020-01-17 |

| 申请号            | CN201910935905.0                               | 申请日     | 2019-09-29 |

| [标]申请(专利权)人(译) | 深圳市华星光电技术有限公司                                  |         |            |

| [标]发明人         | 汤爱华                                            |         |            |

| 发明人            | 汤爱华                                            |         |            |

| IPC分类号         | G02F1/1343                                     |         |            |

| CPC分类号         | G02F1/134309                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明提供一种显示面板及其制作方法，所述显示面板包括相对设置的阵列基板及彩膜基板、以及设于阵列基板与彩膜基板之间的液晶层；所述阵列基板包括透明电极层；所述透明电极层包括间隔的像素电极以及DBS电极，所述DBS电极相对于像素电极的高度低0到1微米。通过降低DBS电极相对于像素电极的垂直高度，可有效压缩数据线的电场范围，显著降低数据线上下视角的漏光问题，改善垂直串扰的问题，且不使开口率下降。