(12)发明专利申请

(10)申请公布号 CN 111381408 A

(43)申请公布日 2020.07.07

(21)申请号 201811644419.5

(22)申请日 2018.12.29

(71)申请人 咸阳彩虹光电科技有限公司

地址 712000 陕西省咸阳市秦都区高科一路一号

(72)发明人 胡佳乔 吴永良 陈宥烨

(74)专利代理机构 西安嘉思特知识产权代理事务所(普通合伙) 61230

代理人 郝梦玲

(51)Int.Cl.

G02F 1/1362(2006.01)

G02F 1/1368(2006.01)

权利要求书1页 说明书6页 附图3页

(54)发明名称

一种像素阵列及其液晶面板

(57)摘要

本发明涉及一种像素阵列及其液晶面板，其中所述像素阵列，包括：多条相互交错的第一扫描线和数据线；多条第二扫描线，多个像素单元，所述像素单元包括：第一开关；第二开关，第三开关，与所述第二开关和所述第二扫描线电性连接；主像素电极，与所述第一开关电性连接；亚像素电极，与所述第二开关和所述第三开关电性连接；多条共通线，所述第三开关还与其中一条共通线电性连接。本发明提供了一种像素阵列，在现有技术的基础上，增加第三开关和第二扫描线，通过第三开关和第二开关并联，并通过第二扫描线控制第三开关，从而控制亚像素的电位，使得亚像素的电位能够根据实际需求进行自由设计，从而能够更好地改善色偏。

1. 一种像素阵列，其特征在于，包括：

多条相互交错的第一扫描线和数据线；

多条第二扫描线，位于相邻的两条第一扫描线之间；

多个像素单元，任一个所述像素单元与其中一条第一扫描线、其中一条第二扫描线以及其中一条数据线电性连接，且所述像素单元包括：

第一开关；

第二开关，所述第二开关和所述第一开关与同一条数据线和同一条第一扫描线电性连接；

第三开关，与所述第二开关和所述第二扫描线电性连接；

主像素电极，与所述第一开关电性连接；

亚像素电极，与所述第二开关和所述第三开关电性连接；

多条共通线，所述第三开关还与其中一条共通线电性连接。

2. 根据权利要求1所述的像素阵列，其特征在于，所述多个像素单元还包括：

第一电容电极，与所述主像素电极一起构成第一存储电容；

第二电容电极，与所述亚像素电极一起构成第二存储电容。

3. 根据权利要求2所述的像素阵列，其特征在于，所述多个像素单元还包括：

主像素耦合电容，一端与所述主像素电极电性连接，另一端与其中一条共通线电性连接；

亚像素耦合电容，一端与所述亚像素电极电性连接，另一端与其中一条共通线电性连接。

4. 根据权利要求1所述的像素阵列，其特征在于，所述第一开关为第一薄膜晶体管，所述第一薄膜晶体管的栅极与其中一条第一扫描线电性连接，所述第一薄膜晶体管的源极与其中一条数据线电性连接，所述第一薄膜晶体管的漏极与所述主像素电极电性连接。

5. 根据权利要求4所述的像素阵列，其特征在于，所述第二开关为第二薄膜晶体管，所述第二薄膜晶体管的栅极与其中一条第一扫描线电性连接，所述第二薄膜晶体管的源极与其中一条数据线电性连接，所述第二薄膜晶体管的漏极与所述第三开关以及所述亚像素电极电性连接。

6. 根据权利要求5所述的像素阵列，其特征在于，所述第三开关为第三薄膜晶体管，所述第三薄膜晶体管的栅极与其中一条第二扫描线电性连接，所述第三薄膜晶体管的源极与多条共通线中的一条电性连接，所述第三薄膜晶体管的漏极与所述第二薄膜晶体管的漏极以及所述亚像素电极电性连接。

7. 根据权利要求1所述的像素阵列，其特征在于，所述第二扫描线与扫描驱动器连接，所述扫描驱动器用于控制所述第二扫描线的驱动时序。

8. 一种液晶面板，其特征在于，所述液晶面板包括如权利要求1-7任一项所述的像素阵列。

## 一种像素阵列及其液晶面板

### 技术领域

[0001] 本发明涉及液晶显示屏领域,具体涉及一种像素阵列及其液晶面板。

### 背景技术

[0002] 液晶显示器(Liquid Crystal Display,LCD)具有机身薄、省电、无辐射等众多优点,得到了广泛的应用,如:液晶电视、移动电话、个人数字助理(PDA)、数字相机、计算机屏幕或笔记本电脑屏幕等,在平板显示领域中占主导地位。

[0003] 目前主流的液晶显示面板是由一片薄膜晶体管阵列基板(Thin Film Transistor Array Substrate,TFT Array Substrate)与一片彩色滤光片(Color Filter,CF)基板贴合而成,且在TFT基板与CF基板之间灌入液晶。通过通电与否来控制液晶分子改变方向,将背光模组的光线折射出来产生画面。

[0004] 其中,CF基板一侧具有多个呈阵列式排布的像素单元,每一像素单元包括红色子像素、绿色子像素、蓝色子像素,黑色矩阵(Black Matrix,BM)分布于每一子像素的外围,用于遮光。CF基板上对应于红、绿、蓝三色的光阻区以及对应于黑色矩阵的遮光区的面积大小直接影响液晶显示器的开口率和对比度,从而影响液晶显示器整体的显示质量。开口率是液晶显示面板的一个重要的参数,指的是液晶显示面板的有效透光区域与全部面积的比例。当光线经由背光模组发射出来时,并不是所有的光线都能穿过液晶显示面板:对于TFT基板而言,液晶显示面板源极驱动芯片及栅极驱动芯片所用的信号走线、储存电压用的储存电容等,这些地方除了不完全透光外,经过这些地方的光线并不受电压的控制,所以需要利用黑色矩阵加以遮蔽;对于CF基板而言,透光区主要为红、绿、蓝子像素对应的光阻区,而黑色矩阵则为遮光区,主要是用来防止各子像素红、绿、蓝光阻的混色,以提高面板的对比值。

[0005] 在液晶显示屏中,每个TFT开关的栅极连接至水平方向的扫描线,源极连接至垂直方向的数据线,而漏极连接至液晶像素电极和存储电容。显示屏一次只启动一条栅极扫描线,以将相应一行的TFT开关打开。垂直方向的数据线送入对应的视频信号,对液晶存储电容充电至适当的电压,用于显示对应行的图像。

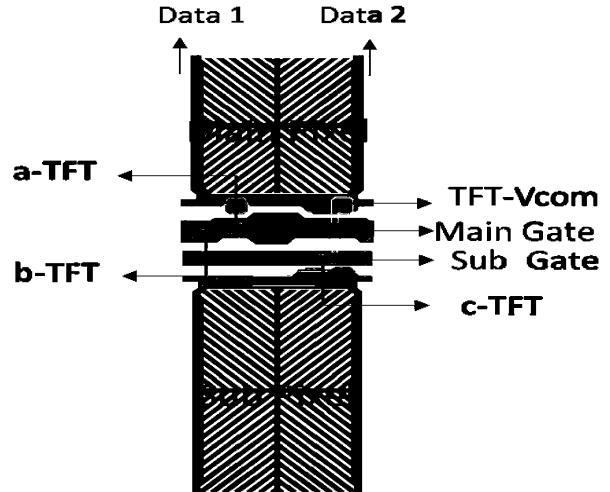

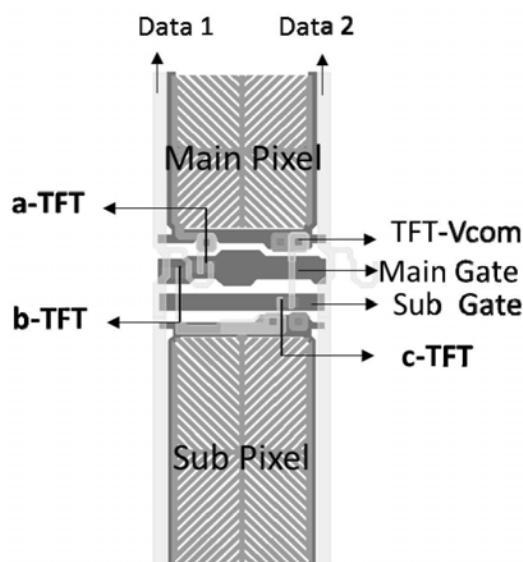

[0006] 由于不同视野角下液晶分子的折射率存在各向异性,导致了RGB像素亮度差异,最终形成了色偏。CC Type(Capacitance Coupling Type,电容耦合技术)是常见的8畴显示设计方式。现有的CC Type技术如图1-图2所示,像素设计确定时,主像素Main pixel的充电电压由数据线和扫描线的时序进行控制;亚像素sub pixel的充电电压由数据线data、扫描线gate以及电容Cx共通确定,亚像素的电压受到电容Cx和存储电容的比值的影响,该种设计结构中,一方面像素设计中具有两条金属电极,使得像素的开口率降低。另一方面亚像素受到ITO悬浮电极电位的影响,使得电荷释放能力较低,容易出现残像。

[0007] 因此,有必要提供一种新的更有效的解决色偏问题的技术方案。

## 发明内容

[0008] 为了解决现有技术中存在的上述问题，本发明提供了一种像素阵列及 其液晶面板。本发明要解决的技术问题通过以下技术方案实现：

[0009] 本发明实施例提供一种像素阵列，包括：

[0010] 多条相互交错的第一扫描线和数据线；

[0011] 多条第二扫描线，位于相邻的两条第一扫描线之间；

[0012] 多个像素单元，任一个所述像素单元与其中一条第一扫描线、其中一 条第二扫描线以及其中一条数据线电性连接，且所述像素单元包括：

[0013] 第一开关；

[0014] 第二开关，所述第二开关和所述第一开关与同一条数据线和同一条第 一扫描线电性连接；

[0015] 第三开关，与所述第二开关和所述第二扫描线电性连接；

[0016] 主像素电极，与所述第一开关电性连接；

[0017] 亚像素电极，与所述第二开关和所述第三开关电性连接；

[0018] 多条共通线，所述第三开关还与其中一条共通线电性连接。

[0019] 在一个具体的实施例中，所述多个像素单元还包括：

[0020] 第一电容电极，与所述主像素电极一起构成第一存储电容；

[0021] 第二电容电极，与所述亚像素电极一起构成第二存储电容。

[0022] 在一个具体的实施例中，所述多个像素单元还包括：

[0023] 主像素耦合电容，一端与所述主像素电极电性连接，另一端与其中一 条共通线电性连接；

[0024] 亚像素耦合电容，一端与所述亚像素电极电性连接，另一端与其中一 条共通线电性连接。

[0025] 在一个具体的实施例中，所述第一开关为第一薄膜晶体管，所述第一 薄膜晶体管的栅极与其中一条第一扫描线电性连接，所述第一薄膜晶体管 的源极与其中一条数据线电性连接，所述第一薄膜晶体管的漏极与所述主 像素电极电性连接。

[0026] 在一个具体的实施例中，所述第二开关为第二薄膜晶体管，所述第二 薄膜晶体管的栅极与其中一条第一扫描线电性连接，所述第二薄膜晶体管 的源极与其中一条数据线电性连接，所述第二薄膜晶体管的漏极与所述第 三开关以及所述亚像素电极电性连接。

[0027] 在一个具体的实施例中，所述第三开关为第三薄膜晶体管，所述第三 薄膜晶体管的栅极与其中一条第二扫描线电性连接，所述第三薄膜晶体管 的源极与多条共通线中的一条电性连接，所述第三薄膜晶体管的漏极与所 述第二薄膜晶体管的漏极以及所述亚像 素电极电性连接。

[0028] 在一个具体的实施例中，所述第二扫描线与扫描驱动器连接，所述扫 描驱动器用于控制所述第二扫描线的驱动时序。

[0029] 本发明实施例还提供一种液晶面板，所述液晶面板包括上述任一项所 述的像素阵列。

[0030] 与现有技术相比，本发明的有益效果：

[0031] 本发明提供了一种像素阵列，在现有技术的基础上，增加第三开关和 第二扫描

线,通过第三开关和第二开关并联,并通过第二扫描线控制第三开关,从而控制亚像素的电位,使得亚像素的电位能够根据实际需求进行自由设计,从而能够更好地改善色偏。

### 附图说明

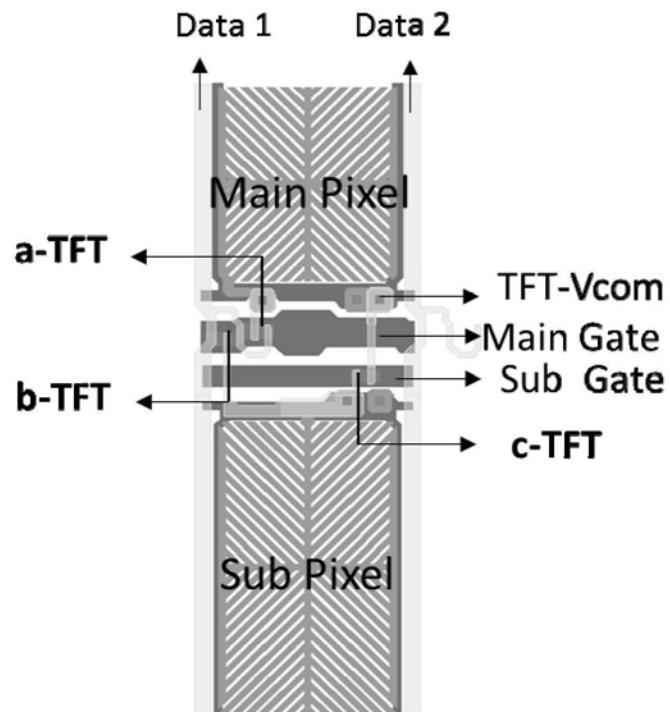

- [0032] 图1为现有技术中的像素阵列的结构示意图;

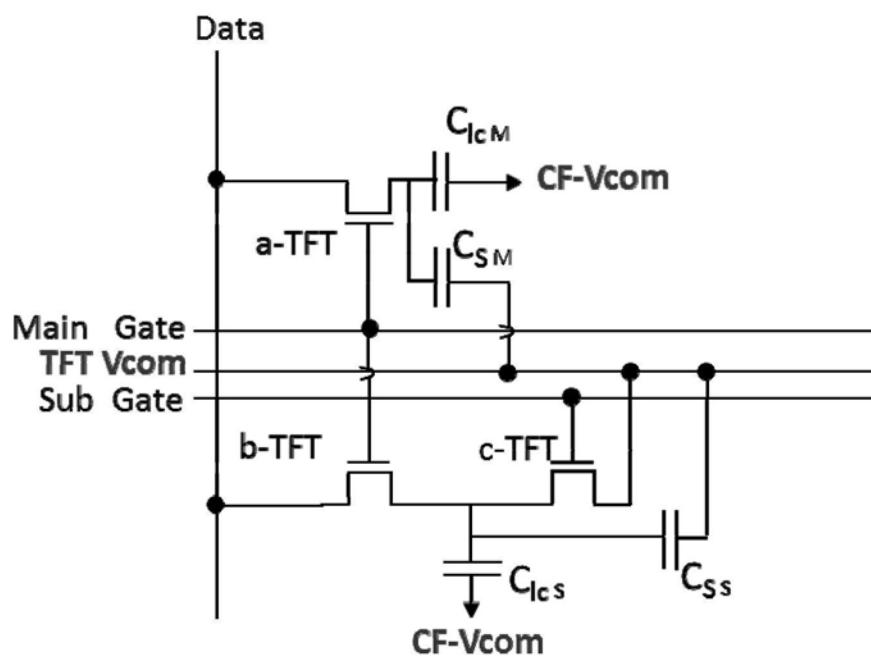

- [0033] 图2为现有技术中的驱动电路示意图;

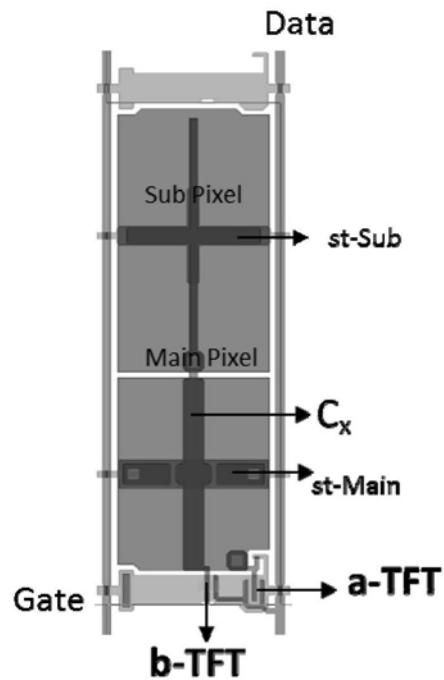

- [0034] 图3为本发明实施例提供的像素阵列的结构示意图;

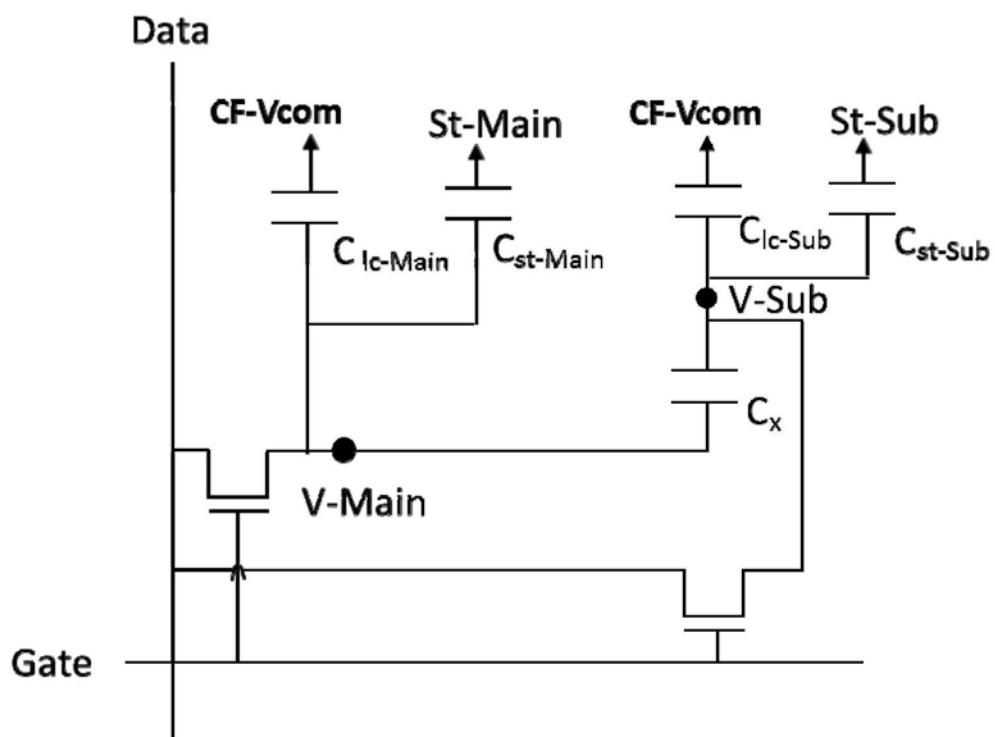

- [0035] 图4为本发明实施例提供的驱动电路示意图;

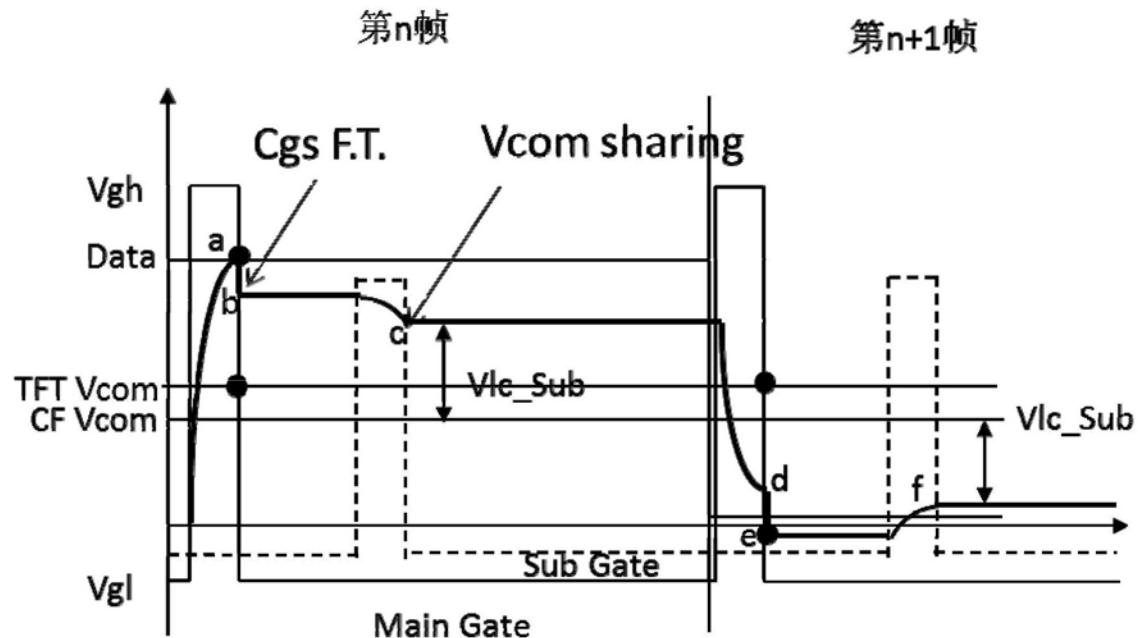

- [0036] 图5为本发明实施例提供的V-T曲线图。

### 具体实施方式

[0037] 在以下的叙述中,为了使读者更好地理解本申请而提出了许多技术细节。但是,本领域的普通技术人员可以理解,即使没有这些技术细节和基于以下各实施方式的种种变化和修改,也可以实现本申请所要求保护的技术方案。

[0038] 为使本发明的目的、技术方案和优点更加清楚,下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

[0039] 如图3-图4所示,图3为本发明实施例提供的像素阵列的结构示意图;图4为本发明实施例提供的驱动电路示意图;本实施例的像素阵列包括交叉且绝缘设置的多条第一扫描线10(i)、多条第一扫描线20(i)和多条数据线30(j),第一扫描线10(i)和数据线20(j)交叉位置处限定出像素区域,多个像素单元40分别配置在其中一个像素区域中;像素阵列还包括多条共通线50(i);进一步的,像素单元40与其中一条第一扫描线10(i)、其中一条第二扫描线20(i)、其中一条数据线30(j)以及其中一条共通线50(i)电性连接,其中,i,j都为自然数,多条共通线50(i)可彼此连接;多个像素单元40排列成多行,且排列在同一行的像素单元与同一条第一扫描线以及同一条第二扫描线电性连接,也即第一扫描线10(i)、第二扫描线20(i)以及共通线50(i)分别与排列于第i行的像素单元40电性连接;进一步的,数据线30(j)则与排列在j列的像素单元40电性连接;需要说明的是,第一扫描线10(i)、第二扫描线20(i)以及共通线50(i)彼此电性绝缘。

[0040] 在本实施例中,第一扫描线10(i)、第二扫描线20(i)以及共通线50(i)的延伸方向实质上平行,而数据线30(j)的延伸方向则垂直于第一扫描线10(i)的延伸方向。

[0041] 进一步的,如图3所示,像素单元包括第一开关a-TFT,第二开关b-TFT和第三开关c-TFT,主像素电极以及亚像素电极,第一开关a-TFT、第二开关b-TFT与同一条数据线Data和同一条第一扫描线Main gate电性连接;并且第一开关a-TFT与主像素电极电性连接,第二开关b-TFT与亚像素电极电性连接;进一步的,第三开关c-TFT分别与第二开关b-TFT、第二扫描线Sub gate以及共通线TFT Vcom电性连接,其中,第三开关c-TFT与第二开关b-TFT为并联关系,且并联后与亚像素电极电性连接。

[0042] 数据线和第一扫描线导通,向该数据线和该第一扫描线限定的子像素充电,此时,第一开关a-TFT导通,主像素电极通电,主像素充电;第二扫描线导通,第二开关b-TFT和第三开关c-TFT导通,亚像素电极通电,亚像素充电,在此过程中,主像素的充电过程通过第一开关a-TFT控制,亚像素的充电过程由第二开关b-TFT和第三开关c-TFT共同控制,

第三开关c-TFT的导通由第二扫描线和共通线控制,更进一步的,可以通过第二扫描线的电位来调节亚像素电极的电位高低,从而影响亚像素的充电电位,这样就可以根据需求调整亚像素电位,从而更好地实现改善色偏的效果。

[0043] 具体的,第二扫描线和扫描驱动器连接,扫描驱动器向第二扫描线提供驱动信号,第二扫描线向第三开关c-TFT提供驱动信号,第二扫描线通电,第三开关c-TFT导通,向亚像素电极充电,第一扫描线通电,第一开关a-TFT和第二开关b-TFT导通;需要说明的是,第二扫描线的驱动电压大小是可以根据需要进行自由设计,具体包括在第二扫描线上加载大于像素电压,或者加载小于像素电压或者加载与像素电压相同的电压,就是说加载不同的电压可以与像素电压形成不同的压差,当压差越大时,并联分压的效果就越明显,亚像素上的电位更低。

[0044] 由此可知,本发明实施例将第一开关a-TFT、第二开关b-TFT与第三开关c-TFT的驱动控制分开进行,一方面提高了第三开关c-TFT的控制灵活性,使得亚像素的电位能够根据实际需求进行自由设计,从而能够更好地改善色偏。另一方面降低了第一扫描线的工作延迟,提升了面板显示质量。

[0045] 进一步的,像素单元还包括第一电容和第二电容,其中,第一电容电极和主像素电极构成第一存储电容,第一电容电极为公共电极CF-Vcom,第一开关a-TFT用于向第一存储电容充电;第二电容电极和亚像素电极构成第二存储电容,第二电容电极也为公共电极CF-Vcom,第二开关b-TFT和第三开关c-TFT一起用于向第二存储电容充电;

[0046] 具体的实际应用时,数据线导通后,第一扫描线、第二扫描线和共通线同时导通;此时数据线和第一扫描线交叉点的像素单元的驱动过程如下:

[0047] 第一开关a-TFT导通,向第一存储电容充电;主像素电位通过数据线和第一扫描线控制;

[0048] 第三开关c-TFT和第二开关b-TFT导通,向第二存储电容充电,第二存储电容的充电时长受到共通线和第二扫描线的影响,本实施例中,第一扫描线的电位高于共通线的电位,共通线的电位也是可以自由设计的,一般情况采取5V;但第二扫描线的电位与共通线以及第一扫描线没有相关性。该种设计方式,一方面能够满足亚像素的液晶驱动,另一方面能够更加灵活地调整亚像素的电位。

[0049] 本发明实施例中,第二开关b-TFT和第三开关c-TFT并联分压的原理如公式1、公式2和图5所示,

$$[0050] V_{Main} = \int_0^{T_{gate}} \frac{I_{data}}{C_{total}} dt \quad \text{式 1}$$

$$[0051] V_{Sub} = \int_0^{T_{gate}} \frac{I_{data}}{C_{total}} dt + \int_N^{N+\Delta t} \frac{I_{Vcom}}{C_{total}} dt \quad \text{式 2}$$

[0052] 其中,式1中,V<sub>Main</sub>是主像素电压,T<sub>gate</sub>是gate关闭的时间点,I<sub>data</sub>是data电流,C<sub>total</sub>是像素总电容。

[0053] 式2中,V<sub>Sub</sub>是亚像素电压,T<sub>gate</sub>是gate关闭的时间点,I<sub>data</sub>是data电流,C<sub>total</sub>是像素总电容,I<sub>Vcom</sub>是共通线电流。

[0054] 如图5所示,图5主要显示亚像素的电位变化情况。数据线、第一扫描线以及共通线提供电位信号,在第N帧时刻,数据线和第一扫描线提供电位信号,第一开关a-TFT和第

二开关b-TFT导通，主像素和亚像素开始通电，亚像素电位上升至a点，然后第一扫描线关闭，受到馈通电压的影响，电位从a点降低到b点并保持，直到第二扫描线导通，原来的电位b点受到第三开关c-TFT的分压影响降低至c点，并保持到下一帧，第二扫描线的导通时间点以及导通时长(虚线的宽度)可以根据实际需求进行设定。

[0055] 在第N+1帧时，数据线提供与前一帧极性相反电位信号，第一扫描线打开，第一开关a-TFT和第二开关b-TFT导通，主像素和亚像素开始通电，亚像素电位下降至d点，然后第一扫描线关闭，受到馈通电压的影响，电位从d点降低到e点并保持，直到第二扫描线导通，原来的电位e点受到第三开关c-TFT的分压影响上升至f点，并保持到下一帧。

[0056] 进一步的，本发明实施例相比于现有技术，减少了主像素和亚像素上的两条金属电极，提高了像素的开口率。

[0057] 进一步的，像素单元还包括主像素耦合电容和亚像素耦合电容，主像素耦合电容的一端与主像素电极电性连接，另一端和共通线电性连接；亚像素耦合电容的一端与亚像素电极电性连接，另一端和共通线电性连接。主像素耦合电容和亚像素耦合电容，是第一存储电容和第二存储电容在充电过程中的必然结果，将主像素耦合电容和亚像素耦合电容用于提供一个稳定的电压，因此，主像素耦合电容和亚像素耦合电容的电压漂移较小，能够起到稳定电压的作用。

[0058] 在一个优选的实施例中，第一开关a-TFT为第一薄膜晶体管，第一薄膜晶体管具有与第一扫描线连接的栅极，与数据线连接的源极和与主像素电极连接的漏极；第二开关b-TFT为第二薄膜晶体管，具有与第一扫描线连接的栅极，与数据线连接的源极和与第三开关c-TFT以及亚像素电极连接的漏极；第三开关c-TFT为第三薄膜晶体管，具有与第二扫描线连接的栅极，与共通线连接的漏极和与第二薄膜晶体管的漏极以及亚像素电极电性连接的源极，其中，第一薄膜晶体管和第二薄膜晶体管连接在同一条数据线上，第三薄膜晶体管通过第二薄膜晶体管与同一条数据线连接，第三薄膜晶体管的另外两端分别与第二扫描线和共通线连接，从而使得第三薄膜晶体管与第二薄膜晶体管形成并联关系。

[0059] 需要说明的是，本实施例中像素单元包括主像素和亚像素，主像素电极和多组第一狭缝定义出第一显示区，亚像素电极和多组第二狭缝定义出第二显示区；如图3所示，主像素具有四个第一显示区，亚像素具有四个第二显示区，因此，一个像素单元具有8个显示区，多个显示区使得像素单元具有广视角的特性，能够较好地改善色偏问题。

[0060] 本发明实施例还提供一种液晶面板，该液晶面板包括上述任一实施例所提供的像素阵列，应用了上述像素阵列的液晶面板能够较好地改善色偏和残像问题，具有较好的视觉体验。

[0061] 需要说明的是，在本申请文件中，诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来，而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且，术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含，从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素，而且还包括没有明确列出的其他要素，或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下，由语句“包括一个”限定的要素，并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。本专利的

申请文件中,如果提到根据某要素执行某行为,则是指至少根据该要素执行该行为的意思,其中包括了两种情况:仅根据 该要素执行该行为、和根据该要素和其它要素执行该行为。

[0062] 以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简 单推演或替换,都应当视为属于本发明的保护范围。

图1

图2

图3

图4

图5

|         |                                                |         |            |

|---------|------------------------------------------------|---------|------------|

| 专利名称(译) | 一种像素阵列及其液晶面板                                   |         |            |

| 公开(公告)号 | <a href="#">CN111381408A</a>                   | 公开(公告)日 | 2020-07-07 |

| 申请号     | CN201811644419.5                               | 申请日     | 2018-12-29 |

| [标]发明人  | 胡佳乔<br>吴永良<br>陈宥烨                              |         |            |

| 发明人     | 胡佳乔<br>吴永良<br>陈宥烨                              |         |            |

| IPC分类号  | G02F1/1362 G02F1/1368                          |         |            |

| 外部链接    | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

## 摘要(译)

本发明涉及一种像素阵列及其液晶面板，其中所述像素阵列，包括：多条相互交错的第一扫描线和数据线；多条第二扫描线，多个像素单元，所述像素单元包括：第一开关；第二开关，第三开关，与所述第二开关和所述第二扫描线电性连接；主像素电极，与所述第一开关电性连接；亚像素电极，与所述第二开关和所述第三开关电性连接；多条共通线，所述第三开关还与其中一条共通线电性连接。本发明提供了一种像素阵列，在现有技术的基础上，增加第三开关和第二扫描线，通过第三开关和第二开关并联，并通过第二扫描线控制第三开关，从而控制亚像素的电位，使得亚像素的电位能够根据实际需求进行自由设计，从而能够更好地改善色偏。