(12)发明专利申请

(10)申请公布号 CN 109240010 A

(43)申请公布日 2019.01.18

(21)申请号 201811366372.0

(22)申请日 2018.11.16

(71)申请人 成都中电熊猫显示科技有限公司

地址 610200 四川省成都市双流区公兴街道青栏路1778号

(72)发明人 八木敏文 陈盈惠 杨桂冬

储周硕 日比野吉高 孙学军

(74)专利代理机构 北京同立钧成知识产权代理

有限公司 11205

代理人 李小波 刘芳

(51)Int.Cl.

G02F 1/1362(2006.01)

权利要求书1页 说明书7页 附图3页

(54)发明名称

阵列基板及液晶显示面板

(57)摘要

本发明提供一种阵列基板及液晶显示面板，所述阵列基板包括：扫描线、数据线和存储电容总线；多条所述扫描线和多条所述数据线交叉设置，相邻两条所述扫描线和相邻两条数据线围合成多个像素区；所述存储电容总线平行于所述扫描线设置，且所述存储电容总线靠近所述扫描线并与所述扫描线电连接；所述像素区在显示时具有因光配向导致的配向暗纹，所述扫描线、所述数据线以及所述电容总线中至少有一者与所述配向暗纹部分重叠。本发明提供一种阵列基板及液晶显示面板，可有效提高像素的透过率。

1. 一种阵列基板,其特征在于,包括:扫描线、数据线和存储电容总线;

多条所述扫描线和多条所述数据线交叉设置,相邻两条所述扫描线和相邻两条数据线围合成多个像素区;

所述存储电容总线平行于所述扫描线设置,且所述存储电容总线靠近所述扫描线并与所述扫描线电连接;

所述像素区在显示时具有因光配向导致的配向暗纹,所述扫描线、所述数据线以及所述电容总线中至少有一者与所述配向暗纹部分重叠。

2. 根据权利要求1所述的阵列基板,其特征在于,所述配向暗纹为万字纹,所述万字纹包括沿顺时针方向排列的第一暗纹、第二暗纹、第三暗纹和第四暗纹。

3. 根据权利要求2所述的阵列基板,其特征在于,所述扫描线和存储电容总线分别与相邻两个所述像素区的所述第一暗纹和所述第三暗纹重叠。

4. 根据权利要求2所述的阵列基板,其特征在于,所述数据线与相邻两个像素区的第二暗纹和第四暗纹重叠。

5. 根据权利要求2所述的阵列基板,其特征在于,所述扫描线和存储电容总线分别与相邻两个所述像素区的所述第一暗纹和所述第三暗纹重叠,并且所述数据线与相邻两个像素区的第二暗纹和第四暗纹重叠。

6. 根据权利要求1-5任一项所述的阵列基板,其特征在于,还包括:像素电极,所述像素电极为覆盖在所述像素区内的透明导电薄膜。

7. 根据权利要求6所述的阵列基板,其特征在于,所述像素电极覆盖在所述存储电容总线、相邻两个所述扫描线中远离所述存储电容总线的一个扫描线、以及相邻两个数据线围合成的区域内。

8. 根据权利要求7所述的阵列基板,其特征在于,所述像素区还设置有栅极、源极和漏极,所述栅极与所述扫描线电连接,所述源极与所述数据线电连接,所述漏极与所述像素电极电连接,所述源极和漏极之间设置有IGZO层。

9. 根据权利要求8所述的阵列基板,其特征在于,所述像素电极为ITO薄膜。

10. 一种液晶显示面板,其特征在于,包括:如权利要求1-9任一项所述的阵列基板,与所述阵列基板相对设置的彩膜基板,以及夹持在所述阵列基板和所述彩膜基板之间的液晶分子层。

## 阵列基板及液晶显示面板

### 技术领域

[0001] 本发明涉及液晶显示领域,尤其涉及一种阵列基板及液晶显示面板。

### 背景技术

[0002] 液晶显示面板的透过率对液晶显示面板的整体显示性能起着极为重要的作用,透过率越高,液晶显示面板的可显示亮度越高,背光源的亮度就可以做的更低,从而降低产品成本,因此如何提升液晶显示面板的透过率是一个非常重要的研究课题。

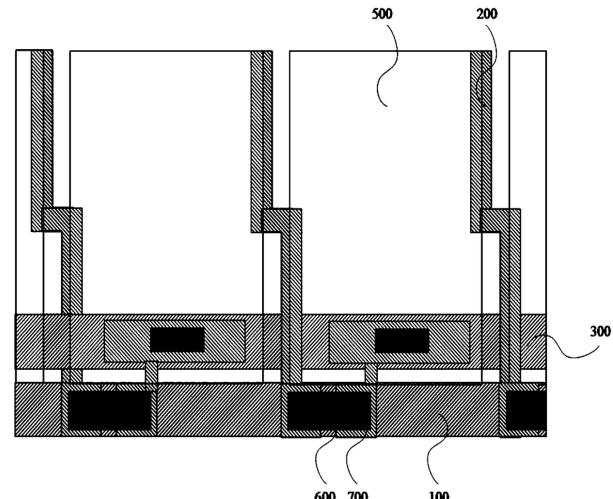

[0003] 图1为现有技术提供的阵列基板的线路设计示意图,参考图1所示,现有技术中,液晶显示面板中的薄膜电晶体(Thin Film Transistor,简称TFT)包括纵横交叉设置的扫描线100和数据线200,相邻的两条扫描线100和相邻的两条数据线200围合成多个像素区。在每个像素区的中心平行于所述扫描线100设置有与扫描线100电连接的存储电容总线300。

[0004] 但是,由于存储电容总线300的金属层遮光面积大,使得像素区的开口率低下,整体的透过率低。

### 发明内容

[0005] 本发明提供一种阵列基板及液晶显示面板,可有效提高像素的透过率。

[0006] 本发明一方面提供一种阵列基板,包括:扫描线、数据线和存储电容总线;

[0007] 多条所述扫描线和多条所述数据线交叉设置,相邻两条所述扫描线和相邻两条数据线围合成多个像素区;

[0008] 所述存储电容总线平行于所述扫描线设置,且所述存储电容总线靠近所述扫描线并与所述扫描线电连接;

[0009] 所述像素区在显示时具有因光配向导致的配向暗纹,所述扫描线、所述数据线以及所述电容总线中至少有一者与所述配向暗纹部分重叠。

[0010] 如上所述的阵列基板,所述配向暗纹为万字纹,所述万字纹包括沿顺时针方向排列的第一暗纹、第二暗纹、第三暗纹和第四暗纹。

[0011] 如上所述的阵列基板,所述扫描线和存储电容总线分别与相邻两个所述像素区的所述第一暗纹和所述第三暗纹重叠。

[0012] 如上所述的阵列基板,所述数据线与相邻两个像素区的第二暗纹和第四暗纹重叠。

[0013] 如上所述的阵列基板,所述扫描线和存储电容总线分别与相邻两个所述像素区的所述第一暗纹和所述第三暗纹重叠,并且所述数据线与相邻两个像素区的第二暗纹和第四暗纹重叠。

[0014] 如上所述的阵列基板,还包括:像素电极,所述像素电极为覆盖在所述像素区内的透明导电薄膜。

[0015] 如上所述的阵列基板,所述像素电极覆盖在所述存储电容总线、相邻两个所述扫描线中远离所述存储电容总线的一个扫描线、以及相邻两个数据线围合成的区域内。

[0016] 如上所述的阵列基板,所述像素区还设置有栅极、源极和漏极,所述栅极与所述扫描线电连接,所述源极与所述数据线电连接,所述漏极与所述像素电极电连接,所述源极和漏极之间设置有IGZO层600。

[0017] 如上所述的阵列基板,所述像素电极为ITO薄膜。

[0018] 本发明提供的阵列基板,通过使阵列基板上的扫描线、数据线和存储电容总线与部分配向暗纹重合,从而将影响透过率的区域遮蔽,使原先透过率高的区域不受线路的影响,以提高面板的整体透过率。进一步地,存储电容总线和扫描线靠近设置,数据线弯折设置,以使得存储电容总线、扫描线和数据线遮挡部分万字纹,即遮蔽透过率弱的配向暗纹区域,从而提高像素整体的透过率。并且,通过对存储电容总线和扫描线的间隙位置处不设置像素电极,可有效降低液晶电容和扫描线的负荷。

[0019] 本发明另一方面还提供一种液晶显示面板,包括:如上所述的阵列基板,与所述阵列基板相对设置的彩膜基板,以及夹持在所述阵列基板和所述彩膜基板之间的液晶分子层。

[0020] 本发明实施例提供的液晶面板,通过使阵列基板上的扫描线、数据线和存储电容总线与部分配向暗纹重合,从而将影响透过率的区域遮蔽,使原先透过率高的区域不受线路的影响,以提高面板的整体透过率。进一步地,存储电容总线和扫描线靠近设置,数据线弯折设置,以使得存储电容总线、扫描线和数据线遮挡部分万字纹,即遮蔽透过率弱的配向暗纹区域,从而提高像素整体的透过率。并且,通过对存储电容总线和扫描线的间隙位置处不设置像素电极,可有效降低液晶电容和扫描线的负荷。

## 附图说明

[0021] 为了更清楚地说明本发明或现有技术的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

[0022] 图1为现有技术提供的阵列基板的线路设计示意图;

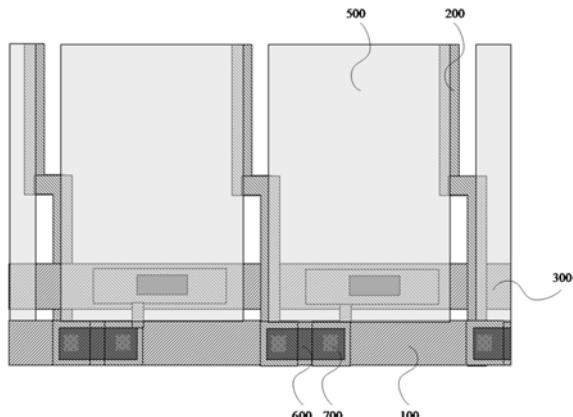

[0023] 图2为本发明实施例提供的阵列基板的线路设计示意图;

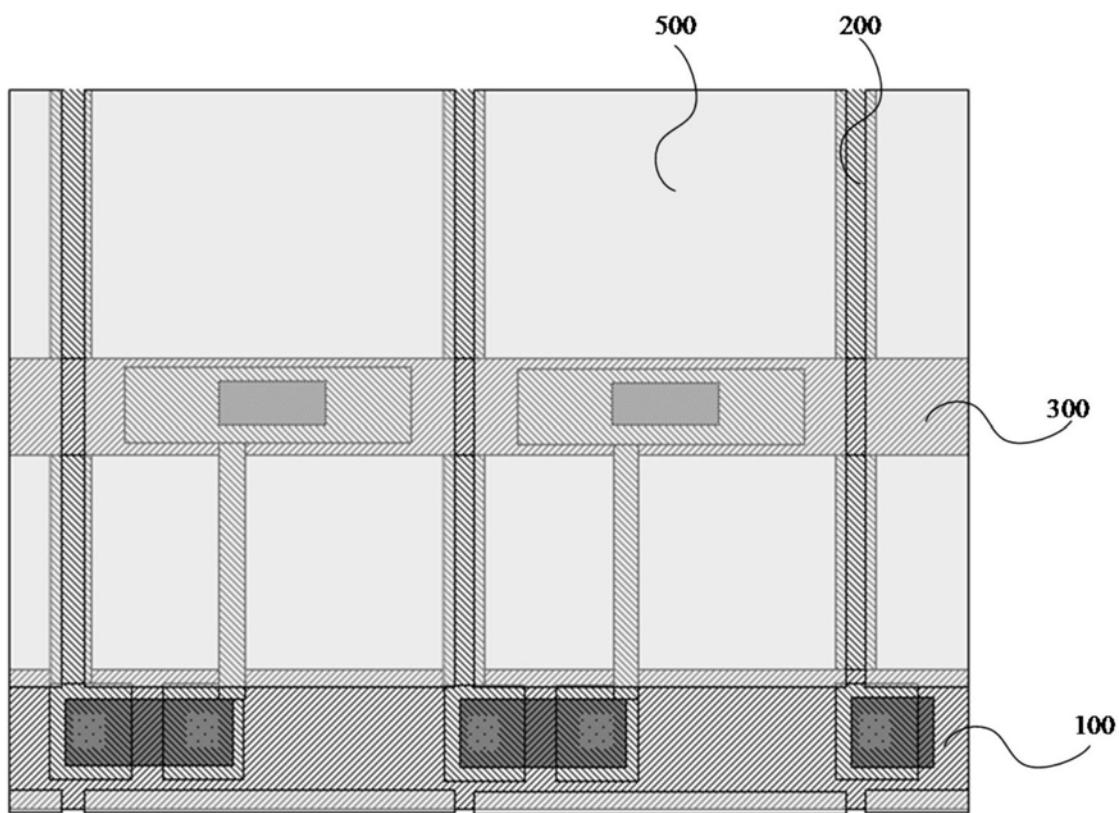

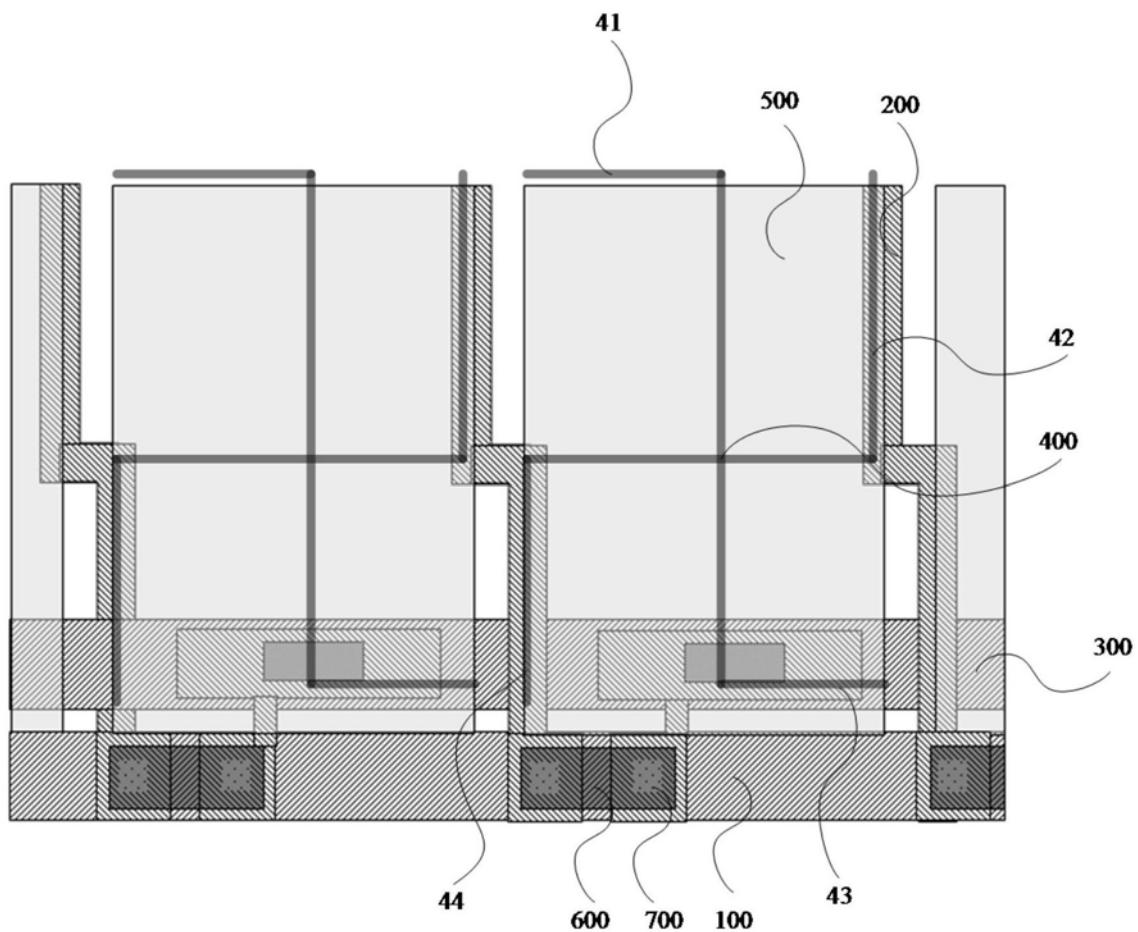

[0024] 图3为本发明实施例提供的阵列基板的线路设计与配向暗纹的位置关系示意图。

[0025] 附图标记:

[0026] 100-扫描线

[0027] 200-数据线

[0028] 300-存储电容总线

[0029] 400-配向暗纹

[0030] 41-第一暗纹

[0031] 42-第二暗纹

[0032] 43-第三暗纹

[0033] 44-第四暗纹

[0034] 500-像素电极

[0035] 600-IGZO

[0036] 700-接触孔

### 具体实施方式

[0037] 为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明中的附图,对本发明中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0038] 需要说明的是,液晶显示面板的垂直配向(Vertical Alignment,简称VA)技术的原理为,在不载入电场的状态下使液晶分子基本垂直于面板面进行配向,载入电场时,液晶分子倾倒,状态发生变化;为控制载入电场时液晶分子的倾倒方向,可以在液晶面板上设计突起和狭缝隙,通过改变它们的形状来实现液晶分子稍微倾斜的状态和稳定的状态。载入电场时,突起和狭缝隙附近的液晶分子首先开始倾倒,然后按照多米诺骨牌效应,随着推倒其它液晶分子。

[0039] 控制配向方向一般采用摩擦配向或者光配向,摩擦配向会产生静电和颗粒污染的问题,且由于摩擦配向只能在一个水平方向上配向,不适用于需要扩大视角的多象限垂直配向(Mutil-domain Vertical Alignment,简称MVA)。光配向是一种非接触式的配向技术,利用线偏振光照射在光敏感的高分子聚合物配向膜上,形成倾角。

[0040] UV<sup>2</sup>A(Ultra Violet Vertical Alignment)技术是一种采用紫外线(Ultra Violet,简称UV)进行液晶配向的垂直配向(Vertical Alignment,简称VA)的技术。通过导入UV<sup>2</sup>A技术,可以省去目前在VA模式液晶面板中用于控制液晶分子配向的狭缝隙和突起,从而提高液晶面板的开口率。

[0041] 由于受到TFT和CF两侧的光配向和ITO边缘电场的双重作用,像素在白态时会出现暗纹。暗纹的形成与配向的区域的多少密切相关,在同一个区域内,液晶分子的初始配向角度时一样的,在加电压后,就可以向着初始配向角度的方向倾倒,但是不同区域的初始配向角度不同。由于液晶存在多米诺骨牌效应,一个液晶向一个方向倾倒,就会拉拽附近的液晶向相同的方向倾倒,两个区域之间的液晶受到两边两个方向倾倒的液晶的拉拽,因此存在一种不平衡,两个区域之间的液晶进入一种紊乱状态,从而形成暗纹。

[0042] 在四象限垂直配向技术中,像素区被划分为四个具有不同配向的象限,因而像素区内形成的暗纹一般为“卍”字形状或者“卐”字形状,统称配向暗纹,配向暗纹会降低液晶显示面板的透过率。

[0043] 下面参考附图并结合具体的实施例描述本发明。

[0044] 实施例一

[0045] 图2为本发明实施例提供的阵列基板的线路设计示意图,图3为本发明实施例提供的阵列基板的线路设计与配向暗纹的位置关系示意图,参考图2和图3所示,本发明一方面提供一种阵列基板,包括:扫描线100、数据线200和存储电容总线300;多条扫描线100和多条数据线200交叉设置,相邻两条扫描线100和相邻两条数据线200围合成多个像素区;存储电容总线300平行于扫描线100设置,且存储电容总线300靠近扫描线100并与扫描线100电连接;像素区在显示时具有因光配向导致的配向暗纹400,扫描线100、数据线200以及电容总线中至少有一者与配向暗纹400部分重叠。

[0046] 本发明实施例的设计思路为,使阵列基板上的扫描线100、数据线200和存储电容总线300中的部分线路与配向暗纹400的部分区域重叠,从而使得扫描线100、数据线200和存储电容总线300将影响透过率的配向暗纹400部分遮挡,同时不影响原先透过率较高的区域,从而提高液晶显示面板整体的透过率。

[0047] 其中,数据线200用于进行资料的传输,扫描线100用于作为控制TFT的开关,扫描线100和数据线200绝缘交叉,扫描线100和数据线200分隔区域形成有像素电极,扫描线100和数据线200的交叉处设置有薄膜晶体管TFT。一般地,多条扫描线100平行设置,并沿第一方向延伸;多条数据线200平行设置,并沿第二方向延伸;第一方向和第二方向垂直交叉。

[0048] 参考图3所示,配向暗纹400为万字纹,万字纹包括沿顺时针方向排列的第一暗纹41、第二暗纹42、第三暗纹43和第四暗纹44。其中,第一暗纹41和第三暗纹43沿第一方向延伸且分别接近于相邻的两条扫描线100,第二暗纹42和第四暗纹44沿第二方向延伸且分别接近于相邻的两条数据线200,第一暗纹41和第二暗纹42、第三暗纹43和第四暗纹44分别呈中心对称。

[0049] 优选地,第一方向为图3中的横向,第二方向为图3中的纵向,应当理解的是,其它方位摆放时,第一方向和第二方向可以为其它方位描述。优选地,在四象限垂直配向技术中,像素区400被划分为四个具有不同配向的象限,因而像素区内部形成的配向暗纹400的形状为“卍”字形状,或者由于摆放的方位不同可以为“卐”字形状,统一称作万字纹。此时,配向暗纹400包括位于像素区400中心位置处的“十”字形状的配向暗纹主体,以及位于像素区300边缘位置的第一暗纹41、第二暗纹42、第三暗纹43和第四暗纹44。

[0050] 在一种可行的实施例中,扫描线100和存储电容总线300分别与相邻两个像素区的第一暗纹41和第三暗纹43重叠。由于扫描线100和存储电容总线300的位置接近,设置一个像素区的存储电容总线300与第三暗纹43重叠时,接近存储电容总线300的扫描线100与相邻的像素区的第一暗纹41重叠。整体上看,每一个像素区内的第一暗纹41和第三暗纹43均被扫描线100和存储电容总线300遮蔽,因此,可有效提高像素的透过率。

[0051] 在另一种可行的实施例中,数据线200与相邻两个像素区的第二暗纹42和第四暗纹44重叠。可以理解地,数据线200弯折设置,数据线200与相邻两个像素区的第二暗纹42和第四暗纹44重叠,换而言之,相邻的两条数据线200分别与同一个像素区的万字暗纹的第二暗纹42和第四暗纹44重叠。在一个像素区内,数据线200的折线设计为Z形,Z形的两条平行边中的其中一条用于与第二暗纹42或第四暗纹44重叠。多个像素区阵列排布时,数据线200的整体呈矩形波形状,一条数据线200上相邻的波峰和波谷,分别用于遮蔽相邻的两个像素区的第四暗纹44和第二暗纹42。本实施例中,每个像素区内的第二暗纹42和第四暗纹44均被遮蔽,因此有效提高了像素整体的透过率。

[0052] 在再一种可行的实施例中,参考图3所示,扫描线100和存储电容总线300分别与相邻两个像素区的第一暗纹41和第三暗纹43重叠,并且数据线200与相邻两个像素区的第二暗纹42和第四暗纹44重叠。整体上看,每一个像素区内的第一暗纹41和第三暗纹43均被扫描线100和存储电容总线300遮蔽,每一个像素区内的第二暗纹42和第四暗纹44均被数据线200遮蔽。因此,可有效提高像素的透过率。

[0053] 本发明实施例中,阵列基板还包括:像素电极500,像素电极500为覆盖在像素区内的透明导电薄膜。像素电极500的作用是给液晶盒施加电压,为了不影响像素的透过率,像

素电极500需要采用透明薄膜。

[0054] 可选地,像素电极500为ITO薄膜。氧化铟锡(Indium Tin Oxide,简称ITO)是一种N型半导体材料,具有半导体的导电性能。ITO薄膜的特性包括较高的导电能力、较强的光再现性和光透过率、较强的化学稳定性、热稳定性、良好的刻蚀均匀性和合适的表面形状。

[0055] 进一步地,由于液晶盒与TFT的漏电流会引起像素电极500电压的下降,进而影响液晶显示面板的对比度等显示特性。为了补偿下降的像素电极500电压,可以在阵列基板上设置存储电容。存储电容与液晶电容并联,一共同提高液晶盒的电压保持率,TFT的负载容量为液晶电容与存储电容之和。

[0056] 存储电容的大小主要取决于存储电极的宽度,但是增大存储电极的宽度,虽然有利于提高电压保持率,但同时也增加了TFT的负载容量,且增加了金属遮光面积,会降低像素的开口率。

[0057] 因此,可选地,像素电极500覆盖在存储电容总线300、相邻两个扫描线100 中远离存储电容总线300的一个扫描线100、以及相邻两个数据线200围合成的区域内。换而言之,本实施例中,在存储电容总线300和扫描线100的间隙位置处不设置像素电极500,可以使液晶电容以及扫描线100的负载降低。

[0058] 此外,像素区还设置有栅极、源极和漏极,栅极与扫描线100电连接,源极与数据线200电连接,漏极与像素电极500电连接,源极和漏极之间设置有IGZO 层600。源极和漏极通过接触孔700分别与数据线200和像素电极500连接,接触孔700通过刻蚀形成。其中,IGZO是一种含有铟、镓和锌的非晶氧化物,其载流子迁移率是非晶硅的20-30倍,可以大大提高TFT对像素电极500的充放电速率,提高像素的响应速度,实现更快的刷新率,同时更快的响应也大大提高了像素的行扫描速率。

[0059] 本发明实施例提供的阵列基板,通过使阵列基板上的扫描线、数据线和存储电容总线与部分配向暗纹重合,从而将影响透过率的区域遮蔽,使原先透过率高的区域不受线路的影响,以提高面板的整体透过率。进一步地,存储电容总线和扫描线靠近设置,数据线弯折设置,以使得存储电容总线、扫描线和数据线遮挡部分万字纹,即遮蔽透过率弱的配向暗纹区域,从而提高像素整体的透过率。并且,通过对存储电容总线和扫描线的间隙位置处不设置像素电极,可有效降低液晶电容和扫描线的负荷。

[0060] 实施例二

[0061] 本发明实施例另一方面还提供一种液晶显示面板,包括:阵列基板,与所述阵列基板相对设置的彩膜基板,以及夹持在所述阵列基板和所述彩膜基板之间的液晶分子层。

[0062] 液晶显示面板的通常结构包括从上至下依次设置的偏光板、彩膜基板、液晶层、阵列基板和偏光板。其中,偏光板的作用是控制背光源的光只让特定方向的光线通过,过滤掉其它方向的光线。经过偏光板处理后的光线,经过液晶分子的扭转作用,可以控制射出显示屏的光线亮度,从而控制射出显示屏的光线亮度,从而控制薄膜晶体管液晶显示屏画面的亮暗程度。控制液晶扭转的是加在液晶上的像素电压,阵列基板上集成着TFT开关阵列,像素点可以通过TFT开关阵列进行精确控制。在彩膜基板上,一个像素分割为红色R、绿色G、蓝色B三个子像素,起光阀作用的液晶对透过彩膜基板的RGB三原色的光亮进行调节,可以得到所需的彩色显示。

[0063] 其中,阵列基板包括:扫描线100、数据线200和存储电容总线300;多条扫描线100

和多条数据线200交叉设置,相邻两条扫描线100和相邻两条数据线200围合成多个像素区;存储电容总线300平行于扫描线100设置,且存储电容总线300靠近扫描线100并与扫描线100电连接;像素区在显示时具有因光配向导致的配向暗纹400,扫描线100、数据线200以及电容总线中至少有一者与配向暗纹400部分重叠。

[0064] 配向暗纹400为万字纹,万字纹包括沿顺时针方向排列的第一暗纹41、第二暗纹42、第三暗纹43和第四暗纹44。

[0065] 在一种可行的实施例中,扫描线100和存储电容总线300分别与相邻两个像素区的第一暗纹41和第三暗纹43重叠。

[0066] 在另一种可行的实施例中,数据线200与相邻两个像素区的第二暗纹42和第四暗纹44重叠。

[0067] 在一种优选的实施例中,扫描线100和存储电容总线300分别与相邻两个像素区的第一暗纹41和第三暗纹43重叠,并且数据线200与相邻两个像素区的第二暗纹42和第四暗纹44重叠。

[0068] 阵列基板还包括:像素电极500,像素电极500为覆盖在像素区内的透明导电薄膜。

[0069] 可选地,像素电极500为ITO薄膜。

[0070] 可选地,像素电极500覆盖在存储电容总线300、相邻两个扫描线100中远离存储电容总线300的一个扫描线100、以及相邻两个数据线200围合成的区域内。

[0071] 进一步地,像素区还设置有栅极、源极和漏极,栅极与扫描线100电连接,源极与数据线200电连接,漏极与像素电极500电连接,源极和漏极之间设置有IGZO层600。

[0072] 本发明实施例提供的液晶面板,通过使阵列基板上的扫描线、数据线和存储电容总线与部分配向暗纹重合,从而将影响透过率的区域遮蔽,使原先透过率高的区域不受线路的影响,以提高面板的整体透过率。进一步地,存储电容总线和扫描线靠近设置,数据线弯折设置,以使得存储电容总线、扫描线和数据线遮挡部分万字纹,即遮蔽透过率弱的配向暗纹区域,从而提高像素整体的透过率。并且,通过对存储电容总线和扫描线的间隙位置处不设置像素电极,可有效降低液晶电容和扫描线的负荷。

[0073] 在本发明的描述中,需要理解的是,所使用的术语“中心”、“长度”、“宽度”、“厚度”、“顶端”、“底端”、“上”、“下”、“左”、“右”、“前”、“后”、“竖直”、“水平”、“内”、“外”“轴向”、“周向”等指示方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的位置或原件必须具有特定的方位、以特定的构造和操作,因此不能理解为对本发明的限制。

[0074] 此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个、三个等,除非另有明确具体的限定。

[0075] 在本发明中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等应做广义理解,例如可以是固定连接,也可以是可拆卸连接,或成为一体;可以是机械连接,也可以是电连接或者可以互相通讯;可以是直接相连,也可以通过中间媒介间接相连,可以使两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

[0076] 在本发明中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

[0077] 最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

图1

图2

图3

|         |                                                |         |            |

|---------|------------------------------------------------|---------|------------|

| 专利名称(译) | 阵列基板及液晶显示面板                                    |         |            |

| 公开(公告)号 | <a href="#">CN109240010A</a>                   | 公开(公告)日 | 2019-01-18 |

| 申请号     | CN201811366372.0                               | 申请日     | 2018-11-16 |

| [标]发明人  | 八木敏文<br>陈盈惠<br>杨桂冬<br>储周硕<br>日比野吉高<br>孙学军      |         |            |

| 发明人     | 八木敏文<br>陈盈惠<br>杨桂冬<br>储周硕<br>日比野吉高<br>孙学军      |         |            |

| IPC分类号  | G02F1/1362                                     |         |            |

| CPC分类号  | G02F1/136286 G02F1/136213                      |         |            |

| 代理人(译)  | 李小波<br>刘芳                                      |         |            |

| 外部链接    | <a href="#">Espacenet</a> <a href="#">SIPO</a> |         |            |

## 摘要(译)

本发明提供一种阵列基板及液晶显示面板，所述阵列基板包括：扫描线、数据线和存储电容总线；多条所述扫描线和多条所述数据线交叉设置，相邻两条所述扫描线和相邻两条数据线围合成多个像素区；所述存储电容总线平行于所述扫描线设置，且所述存储电容总线靠近所述扫描线并与所述扫描线电连接；所述像素区在显示时具有因光配向导致的配向暗纹，所述扫描线、所述数据线以及所述电容总线中至少有一者与所述配向暗纹部分重叠。本发明提供一种阵列基板及液晶显示面板，可有效提高像素的透过率。