### [19] 中华人民共和国国家知识产权局

## [12] 发明专利说明书

[21] ZL 专利号 00135262.8

[45] 授权公告日 2005年3月16日

[11] 授权公告号 CN 1193260C

[22] 申请日 2000.12.11 [21] 申请号 00135262.8

[30] 优先权

[32] 1999. 12. 10 [33] JP [31] 351784/1999

[71] 专利权人 国际商业机器公司 地址 美国纽约州

[72] 发明人 坂口佳民 S·德斯格雷兹 审查员 梁素平 [74] 专利代理机构 中国专利代理(香港)有限公司 代理人 王岳傅康

权利要求书 3 页 说明书 18 页 附图 19 页

[54] 发明名称 液晶显示器、液晶控制器和视频信号传输方法

#### [57] 摘要

本发明的一个目的是减少对 LCD 驱动器的输入端的数量,并通过使用 COG&WOA 技术减少生产成本。 对于液晶显示器,源极驱动器 IC20 级联,通过视频 L/F3 在源极驱动器 IC20 中传输视频信号并在源极驱动器 IC20 中分配视频信号,并且,使用COG&WOA 技术,尽可能地减少与源极驱动器 IC20 的连接线。 也就是说,液晶显示器包括:一个在基片上形成图象显示区域的液晶盒 2;一个源极驱动器 7,经过视频 L/F3 根据视频信号输入将电压施加到所述液晶盒 2 上。 源极驱动器 7 包括多个安装在与液晶盒 2 相同的基片上并使用信号线级联的源极驱动器 IC20。

15

25

- 1. 一种液晶显示器,包括:

- 一个在基片上形成图象显示区域的液晶盒;

- 一个驱动器,用于根据输入视频信号将电压施加到所述液晶盒上, 5 其中所述驱动器包括多个安装在所述基片上的驱动器集成电路和多个 信号线,每个信号线穿过每个串联的驱动器集成电路,其中,所述驱 动器集成电路使用所述信号线串联地级联。

- 2、如权利要求1所述的液晶显示器,其特征在于通过每一个所述 驱动器集成电路的每一金属层将所述多个驱动器集成电路级联到供电 线上。

- 3、如权利要求1所述的液晶显示器,其特征在于所述驱动器集成 电路接收由串行数据组成的视频信号,根据在所述串行数据中包括的 同步图象使所述视频信号同步。

- 4、一种液晶显示器,包括:

- 一个在基片上形成图象显示区域的液晶盒;

- 一个驱动器,用于将输入视频信号分配给多个串联地链式连接的驱动器集成电路并通过使用所述驱动器集成电路给所述液晶盒施加电压,其中每个信号线穿过每个串联的驱动器集成电路,

其中,当由所述多个驱动器集成电路的上游驱动器集成电路给下游 20 驱动器集成电路提供掩蔽信号时所述驱动器给所述多个驱动器集成电 路分配所述视频信号,其中,所述掩蔽信号使所述上游驱动器集成电 路提供的所述视频信号屏蔽。

- 5、如权利要求 4 所述的液晶显示器, 其特征在于所述驱动器的所述下游驱动器集成电路在接收来自于所述上游驱动器集成电路的所述掩蔽信号之后根据所述输入视频信号给所述液晶盒提供电压。

- 6、一种液晶显示器,包括:

- 一个在基片上形成图象显示区域的液晶盒;以及

- 一个驱动器,用于将输入视频信号分配给多个级联的驱动器集成电路并通过使用所述驱动器集成电路给所述液晶盒施加电压,

- 30 其中,通过设置在所述基片上的视频传输线串联级联所述驱动器的 所述多个驱动器集成电路,并由沿所述视频传输线传输的串行数据控

制所述驱动器的所述多个驱动器集成电路,其中所述视频传输线穿过每一个串联的驱动器集成电路。

- 7、如权利要求 6 所述的液晶显示器, 其特征在于连接所述多个驱动器集成电路的视频传输线包括第一信号线、与第一信号线的极性相 5 反的第二信号线。

- 8、如权利要求 6 所述的液晶显示器, 其特征在于所述驱动器进一步包括时钟线和使所述多个驱动器集成电路级联的电源线。

- 9、如权利要求 6 所述的液晶显示器, 其特征在于, 在所述驱动器中, 上游驱动器集成电路包括匹配视频相位和时钟相位的仿真电路。

- 10 10、一种液晶控制器,包括:

- 一个接收来自主机的视频信号以便显示图象的接收器;

- 一个序列发生器,在接收来自所述主机的控制信号时,为将要输出到液晶显示器驱动器的分组数据产生标题信息,所述液晶显示器驱动器包括多个串联地级联的驱动器集成电路和一个穿过每个串联的驱动器集成电路的视频传输线;以及

输出装置,用于将所述接收器接收的所述视频信号转换为串行视频信号,将由所述序列发生器产生的标题信息与所述串行视频信号相加,并且将所得到的分组信号输出给所述液晶显示器驱动器的集成电路。

- 20 11、如权利要求 10 所述的液晶控制器,其特征在于所述序列发生器产生使所述液晶显示器驱动器的所述驱动器集成电路相互同步的标题信息,并且在水平消隐期间所述输出装置提供用于同步的所述标题信息。

- 12、一种将视频信号传输给一个具有多个驱动器集成电路和一个 25 视频传输线的液晶显示器驱动器的视频信号传输方法,包括如下步 骤·

通过串行接口将包括水平消隐周期的视频信号传输给串联的所述 驱动器集成电路,其中,视频传输线穿过每个串联的驱动器集成电路, 驱动器集成电路由所述视频传输线串联地级联;以及

30 在所述水平消隐周期期间传输同步图象以便使所述驱动器集成电路的所述视频信号同步。

13、如权利要求12所述的视频信号传输方法,其特征在于至少在

两个循环传输所述同步图象,并且在传输所述视频信号期间所述驱动器集成电路与所述同步图象一致。

14、一种将视频信号传输给一个具有多个级联的驱动器集成电路 的液晶显示器驱动器的视频信号传输方法,包括如下步骤:

5 通过串行接口将视频信号由一个穿过每个串联的驱动器集成电路的视频传输线传输给串联级联的所述驱动器集成电路;以及

根据每一所述驱动器集成电路接收并要处理的所述视频信号给液晶显示器施加电压;

其中所述视频信号由具有多个属性的信息块构成并且由所述信息 10 块控制所述驱动器。

- 15、如权利要求 14 所述的视频信号传输方法,其特征在于所述信息块之一包括等待所述驱动器集成电路的等待命令,并且其中由处理所述视频信号的每一所述驱动器集成电路产生所述等待命令,并将所述等待命令传输给一个级联的下游驱动器集成电路。

- 16、如权利要求 14 所述的视频信号传输方法, 其特征在于通过使用信息包将所述视频信号传输给所述液晶显示器驱动器, 并由具有所述信息包的标题的协议控制所述多个驱动器集成电路。

10

15

20

25

30

#### 液晶显示器、液晶控制器和视频信号传输方法

#### 技术领域

本发明涉及根据接收到的视频信号显示图象的液晶显示器, 尤其 是涉及一种为液晶显示板提供改进驱动器接口的液晶显示器。

#### 背景技术

通常,当在液晶显示板上显示图象时,首先,通过视频接口输出图象信号,图象信号来自具有PC的系统的图形控制器或系统单元的图形控制器。然后,在接收图象信号时,LCD(液晶显示器)控制器LSI将信号传输给在源极驱动器(X驱动器或LCD驱动器)和栅极驱动器(Y驱动器)中的各个IC的每一个,并将电压施加到设置成矩阵的TFT阵列的每一源极和每一栅极上。

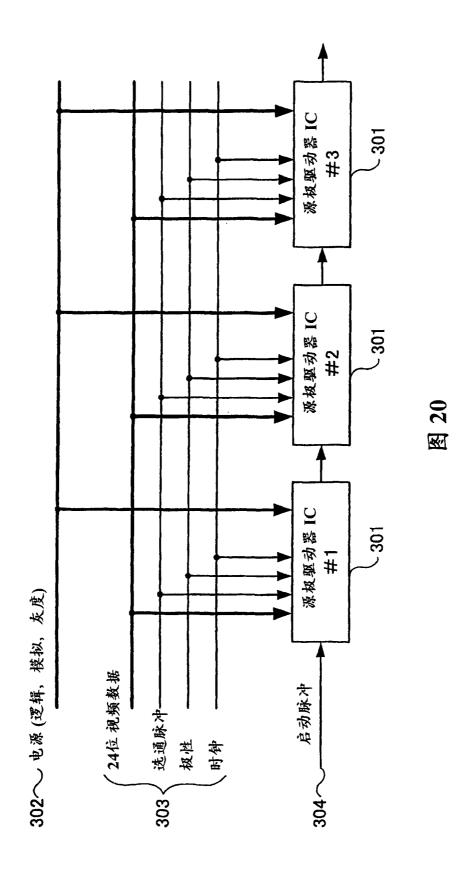

在图 20 中示出了常规 LCD 驱动器使用的接口。在图 20 中,一个源极驱动器的一个组成部分是一个 IC 芯片 301,为一个 LCD 板提供少于 20 的 IC 芯片。这通常由根据玻璃 (COS) 技术的芯片来实现,将芯片 301 安装在玻璃基片上,构成 LCD 板,在一个区域的外面覆盖有滤色片。然后,将每一个芯片 301 与供电线 (电源) 302 相连,并且每一芯片都接收视频接口信号 303 和取样启动信号 (启动脉冲) 304。与 8位的灰度级一致,为视频接口信号 303 和取样启动信号 304 设有总共 28 条传输线,其中 27 条用于视频接口信号 303 携带 24 位的 RGB 视频数据,包括一个用于三基色 R、G和 B的每一色的 8位组、一个用于将接收的 RGB 数据输出给 LCD 的选通脉冲、一个用于标志施加到 LCD 上电压的极性的极性信号和一个用于当使用一个 XGA (1024 × 768) 板时传输大约 65MHz 的点时钟的时钟信号。使用取样启动信号 304 来触发 RGB 视频数据。

正如图 20 所示,对于取样启动信号 304 可以使用级联。然而,将电源线 302 和视频接口信号 303 的 27 条线安装在一个邻接并隔开的印刷电路板 (PCB)或柔性印刷电路板 (FPC)上。也就是说,由于在玻璃基片上的芯片之间设置接线对常规技术来说是很困难的,所以在邻接印刷电路板上形成线接线部分,以便能通过连接芯片的总线来传输

15

20

30

视频数据。在此情况下,考虑视频信号输入与 LCD 源极驱动器的数量 没有出现问题。

最近,为了进一步地降低制作成本,注意力已集中在 COG WOA(在阵列上的布线)技术上。此外,已经开发了另一种技术,将驱动器 LSI设置在 TCP (Tape Carrier Package)上,以便通过 TCP将 LSI与 TFT 阵列基片(玻璃基片)相连。如果使用这些技术,能直接或通过 TCP将集成电路(IC)固定在玻璃基片上并能省去在印刷电路板上形成的接线,能大大地降低生产成本。

然而,使用常规的总线连接,将大量的视频信号输入到 LCD 源极驱动器,不能实现 COG WOA 模块。也就是说,如果将多条线,例如28 条线,不加改变地移动到玻璃基片上,则围绕液晶盒需要 1-2cm的帧空隙。如果设置这样大的框空间,这将出现与当前减小帧尺寸并因而降低产品价格的要求背道而驰的状况。

作为使用 COG 结构减小帧尺寸的技术,在日本未审查专利公开出版物 NO.平5-107551 中提议了一种接线布线,如此构成 FPC 以致于其覆盖芯片并使芯片与 FPC 连接。按照此技术,能减小帧尺寸,但不能减少板的厚度。而且,由于在此结构中所有的芯片都直接与 FPC 相连,所以连接端的数量增加,连接的可靠性将不能满足要求。此外,由于在芯片之间设置有许多 FPC 连接端,所以,在芯片之间需要较大的间隙,而且这样难以减小器件的尺寸。

#### 发明内容

为了克服上述缺点,本发明的一个目的是强有力地减少输入到 LCD 驱动器的视频信号的数量并通过实现 COG WOA 技术来减少生产成本。

25 本发明的另一目的是提供这样一种结构:能构成一种低功耗的、 快速的、小型串行接口,并能使所使用的快速运行电路的数量最少, 从而限制功耗增加和芯片尺寸的增加。

为了实现上述的目的,根据本发明,在可能的最大范围内,级联输入视频信号将被分配到其上的驱动器 IC,以减少连接到各个驱动器 IC 的接线的数量,从而能实现 COG WOA 结构。也就是说,根据本发明的液晶显示器包括:一个在基片上形成图象显示区域的液晶盒;一

15

20

25

个驱动器,用于根据输入视频信号将电压施加到所述液晶盒上,其中所述驱动器包括多个安装在所述基片上并使用信号线级联的驱动器 IC。

最好是,每一驱动器 IC 包括一个输入垫和一个输出垫,并且,由于能容易地在这些驱动器 IC 中实现级联,所以第一驱动器 IC 的输出垫与第二驱动器 IC 的输入垫相连。进一步地,当输入垫和输出垫位于每一驱动器 IC 的两端时,能容易匹配信号线的长度和时钟线的长度,或能容易匹配传输不同信号的成对信号线的长度,并能容易地实现相位调整。此外,驱动器包括多个驱动器 IC,通过每一驱动器 IC 的金属层使所述驱动器 IC 与供电线级联。与供电线设在基片上相比较,在保持低电阻时,能给最远的下游驱动器 IC 提供电源。

驱动器 IC 接收由串行数据组成的视频信号,根据在所述串行数据中包括的同步图象使所述视频信号同步。在视频信号的水平消隐周期期间传输同步图象。

此外,最好是,使用低差分电压传输视频信号,并且,一对线(两条线)用于视频数据,而另一对线(两条线)用于同步时钟。结果是,能有效地实现快速串行接口。

根据本发明的另一方面,液晶显示器包括:

一个在基片上形成图象显示区域的液晶盒;

一个驱动器,用于将榆入视频信号分配给多个链式联接的驱动器 IC 并通过使用所述驱动器 IC 给所述液晶盒施加电压,

其特征在于,当由所述多个驱动器 IC 的上游驱动器 IC 给下游驱动器 IC 提供掩蔽信号时,给所述多个驱动器 IC 分配所述视频信号,并且所述掩蔽信号使由上游驱动器 IC 提供的视频信号屏蔽。用此方案,仅使用视频信号线来分配视频信号。而且,通过将多个(例如,3个)逻辑门加到微分缓冲器来实现屏蔽处理。

驱动器的下游驱动器 IC 在接收来自于上游驱动器 IC 的掩蔽信号,并根据输入视频信号给液晶盒提供电压。

进一步地,根据本发明,液晶显示器包括:

30 一个在基片上形成图象显示区域的液晶盒;

一个驱动器,用于将输入视频信号分配给多个级联的驱动器 IC 并

10

15

20

25

通过使用所述驱动器 IC 给所述液晶盒施加电压,其特征在于通过设置在所述基片上的视频传输线来级联所述驱动器的多个驱动器 IC,并由沿视频传输线传输的串行数据控制所述驱动器的多个驱动器 IC。

连接所述多个驱动器 IC 的视频传输线包括第一信号线、与第一信号线的极性相反的第二信号线。使用此种方案,在快速串行传输期间,能尽可能地减少电磁干扰 (EMI) 的出现,并能保证信号的传输。除视频传输线外,也可以使用一对线用作同步时钟线。

驱动器进一步包括一条时钟线和一条使多个驱动器 IC 级联的电源线。通过有效设置基片接线能实现 WOA。

此外,在驱动器 IC中,上游驱动器 IC包括基本上匹配视频相位和时钟相的仿真电路。在没有为每一驱动器 IC提供 PLL (锁相环)电路的情况下能匹配级联的驱动器 IC的相位。相位不必完全匹配,仅在可允许的范围内必须匹配。

当控制器应用本发明时,液晶控制器包括:一个接收来自主机的视频信号以便显示图象的接收机;一个序列发生器,在接收来自主机控制信号时,为将要输出到 LCD 驱动器的分组数据产生标题信息,所述 LCD 驱动器包括多个级联连接的驱动器 IC;输出装置,用于将所述接收器接收的视频信号转换为串行视频信号、将由所述序列发生器产生的标题信息与到所述串行视频信号相加并且将所得到的串行视频信号输出给所述 LCD 驱动器。使用这种分组数据传输,由使用视频传输线能简单地控制 LCD 驱动器,并且,不需要控制信号的输入,与已有技术一样。

序列发生器产生使所述LCD驱动器的所述驱动器IC相互同步的标题信息,并且在水平消隐周期期间所述输出装置提供用于同步的所述标题信息。

进一步地,根据本发明,一种将视频信号传输给一个具有多个驱动器 IC 的视频信号传输方法,包括如下步骤:

将通过串行接口将包括水平消隐周期的视频信号传输给驱动器 IC;

30 在水平消隐周期期间传输同步图象以便使驱动器 IC 的视频信号同步。

15

25

另外,当至少在两个循传输所述同步同步图象时,驱动器 IC 能提取串行传输的同步图象。此外,当在传输所述视频信号期间,所述驱动器 IC 与所述同步图象一致,即使执行了误差操作,但一行以后能完成同步的恢复。

根据本发明,一种将视频信号传输给一个具有多个级联驱动器 IC 的 LCD 驱动器的视频信号传输方法,包括如下步骤:

通过串行接口将视频信号传输给所述级联的驱动器 IC;

根据每一所述驱动器 IC 接收并要处理的所述视频信号给 LCD 施加一个电压;

10 其特征在于所述视频信号由具有多个属性的信息块构成并且使用 所述信息块控制所述驱动器 IC。

信息块之一包括等待所述驱动器 IC 的等待命令。其特征还在于由处理所述视频信号的每一所述驱动器 IC 产生所述等待命令,并将所述等待命令传输给级联的下游驱动器 IC。按照此方法,使用没有指示将上游驱动器 IC 处理的视频信号给下游驱动器的方法,能分配视频信号。此外,可以使用视频信号线分配视频信号。

通过使用信息包将所述视频信号传输给所述 LCD 驱动器,并由具有所述信息包的标题的协议控制所述多个驱动器 IC。从而,在不要求驱动器 IC 特定控制输入的情况下,能容易地控制所有驱动器 IC。

20 附图说明

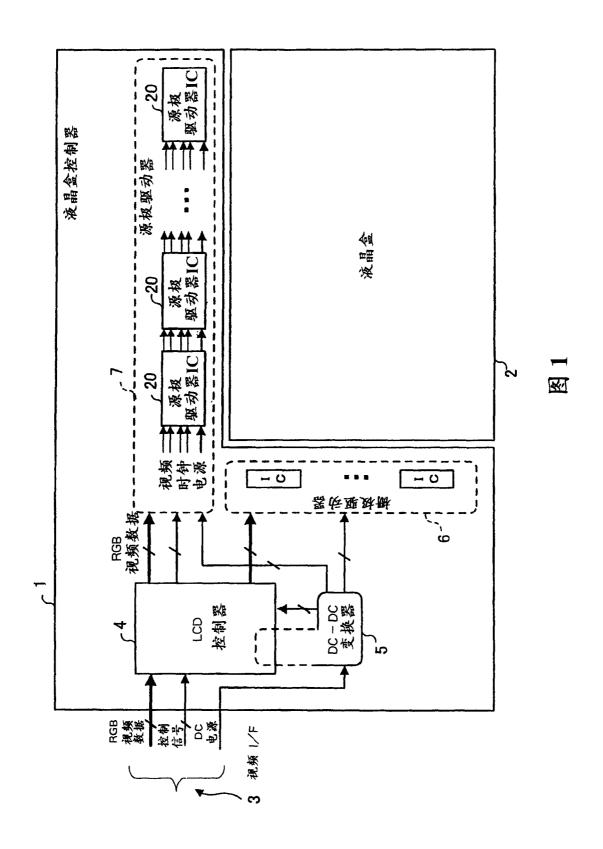

图 1 是描述根据本发明一个实施例的图象显示器的示意图。

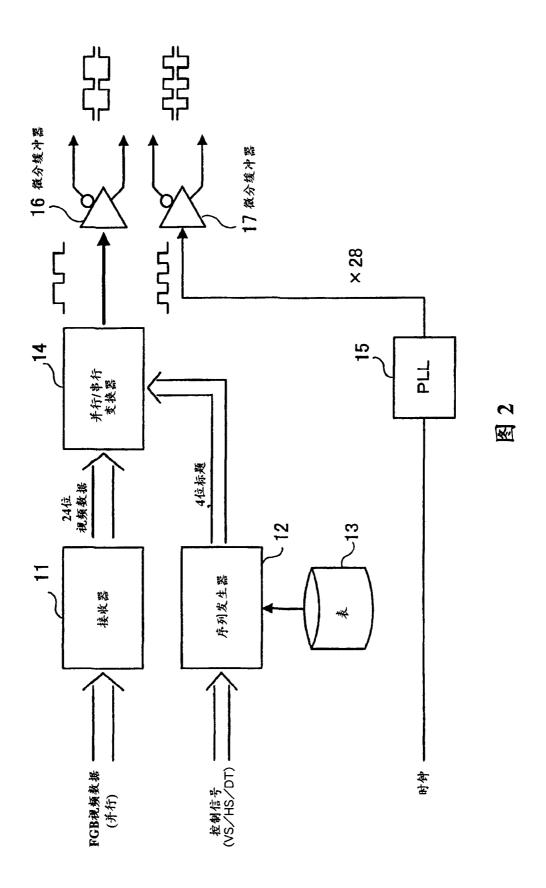

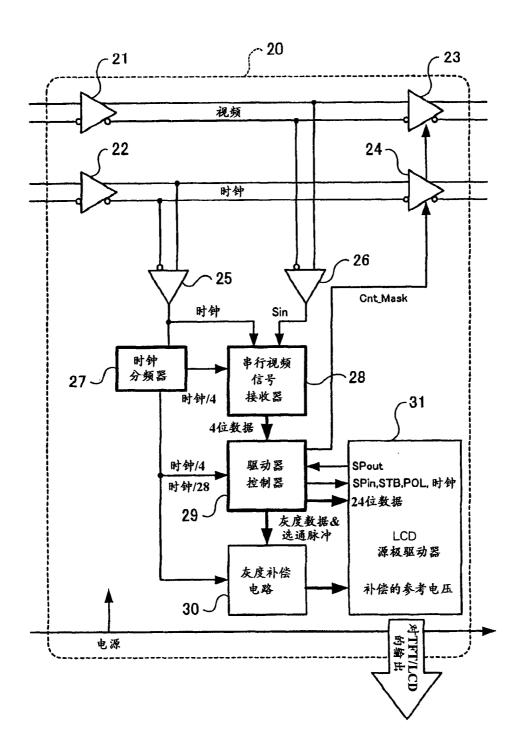

图 2 是解释根据本实例的 LCD 控制器 4 的内部结构的示意图。

图 3 是解释根据本实例的源极驱动器 IC 20 的内部结构的示意图

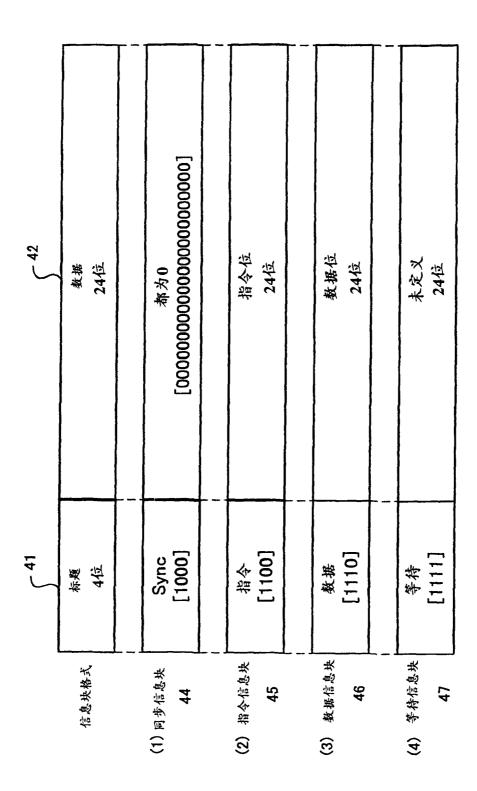

图 4 是示意图,示出了本实施例所用的串行数据格式的例子。

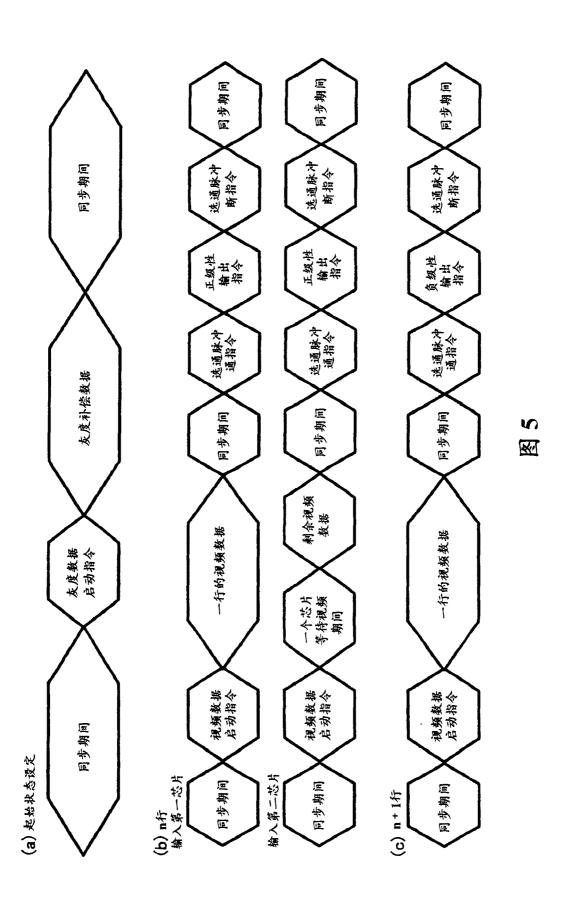

图 5A、5B 和 5C 是描述由序列信息块组成的串行信号传输的示意图。

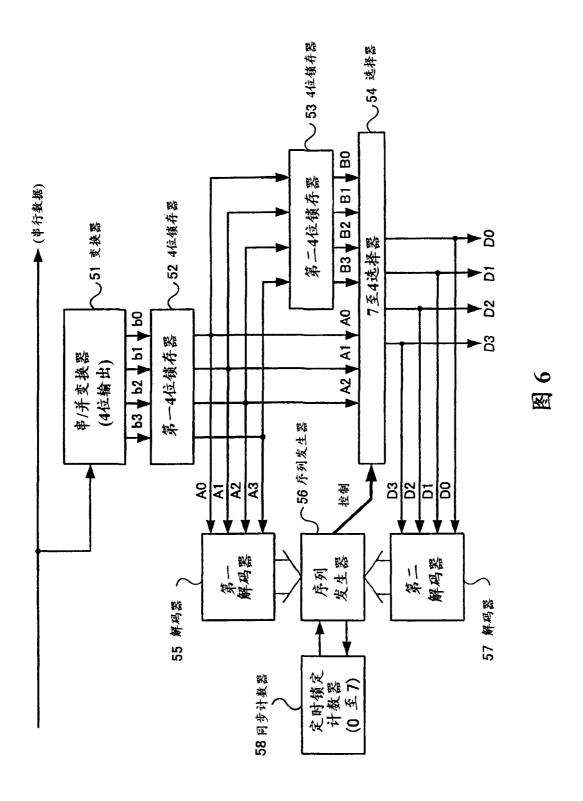

图 6 是描述串行视频信号接收器 28 的布置的示意图。

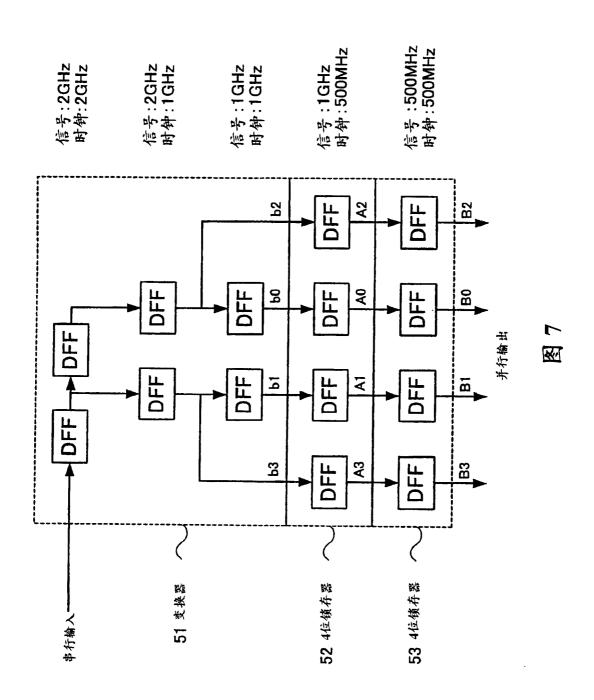

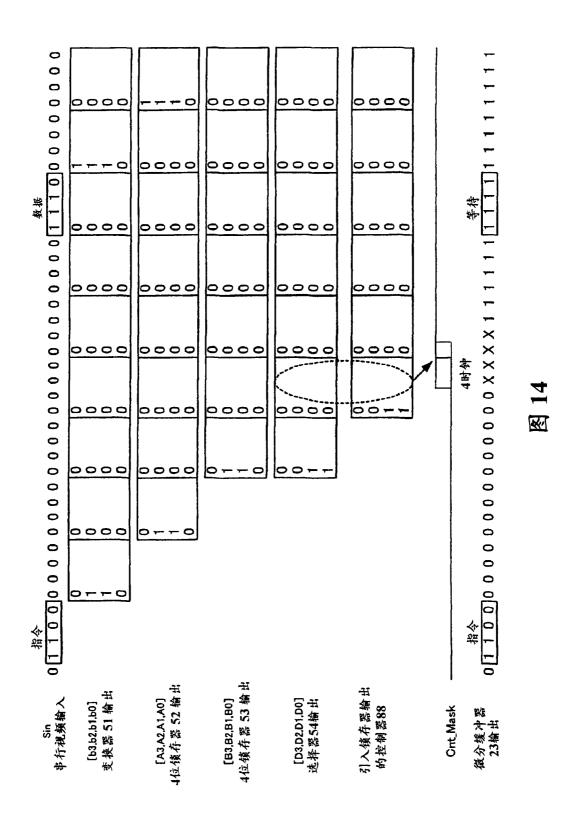

图 7 是表示使用变换器 51 和 4 位锁存器 52、53 的串行/并行变换功能的例子的示意图。

30 图 8 是表示标题 41 的比较图形和选择器 54 的输出之间关系的示意图。

- 图 9 是表示用于数据同步形成的模式的示意图。

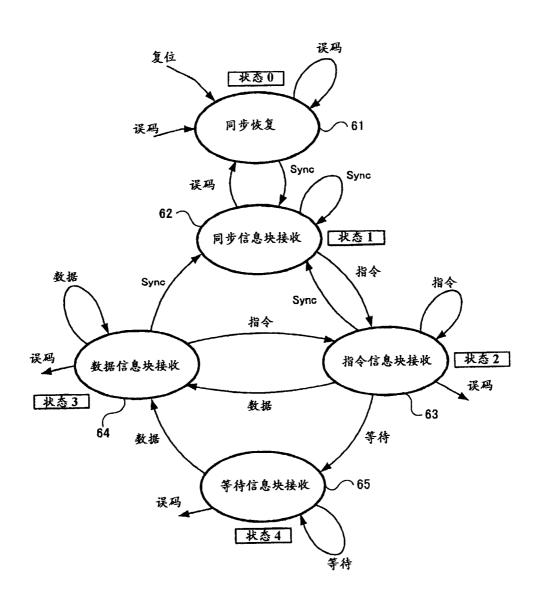

- 图 10 是表示序列发生器 56 的状态移动的示意图。

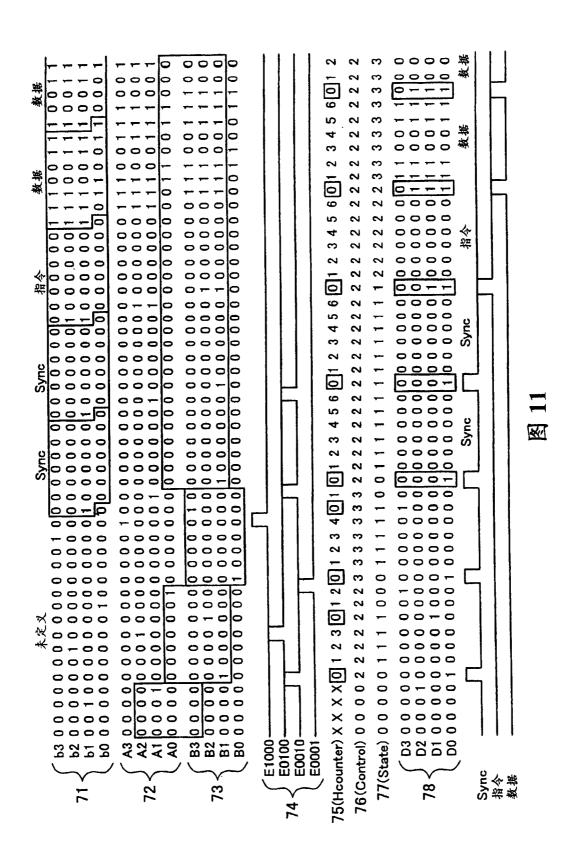

- 图 11 是表示数据同步过程的示意图。

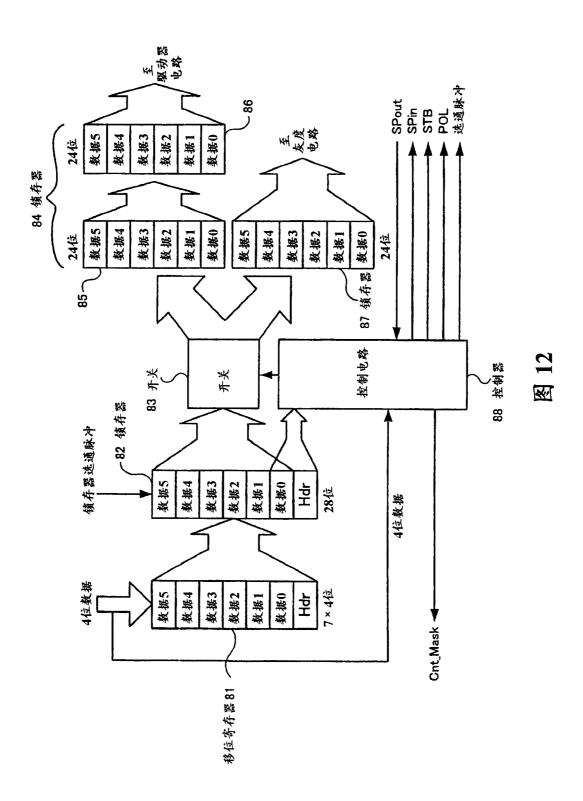

- 图 12 是描述驱动器控制器 29 的布置的示意图。

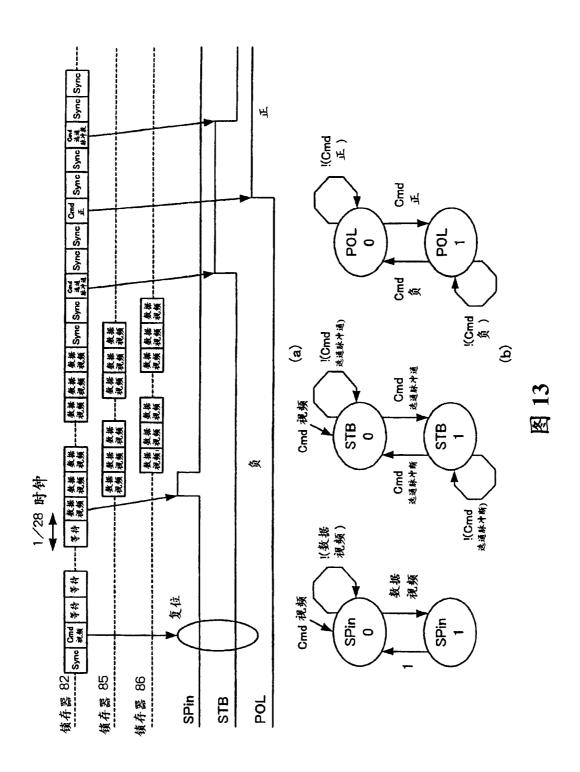

- 5 图 13A 和 13B 示出了产生控制信号的过程(波形和每一控制信号的状态的移位)。

- 图 14 是表示当开始产生等待信息块 47 时数据传输的示意图。

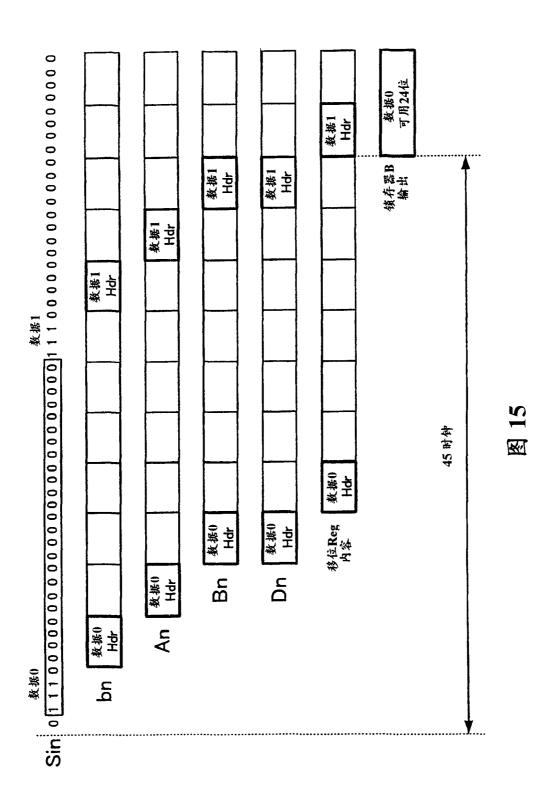

- 图 15 是表示延时从输入串行视频数据开始直到完成 24 位数据为止的示意图。

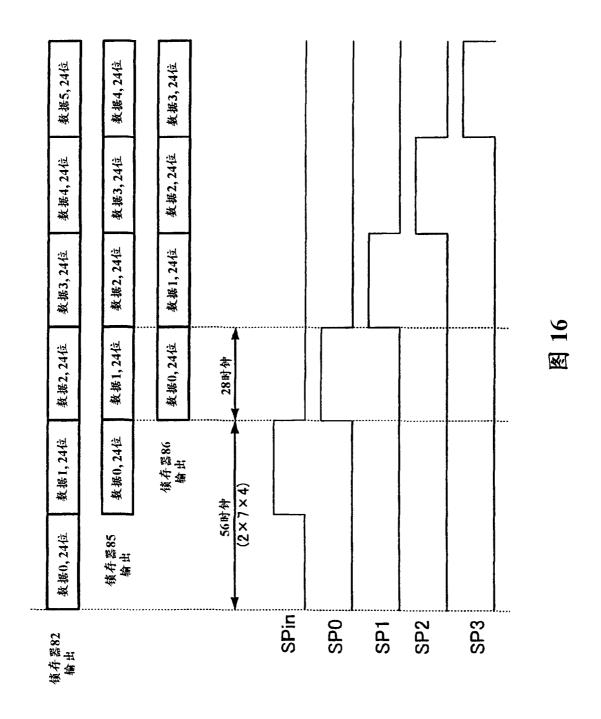

- 10 图 16 是表示輸出给 LCD 源极驱动器 31 的数据和取样数据的定时示意图。

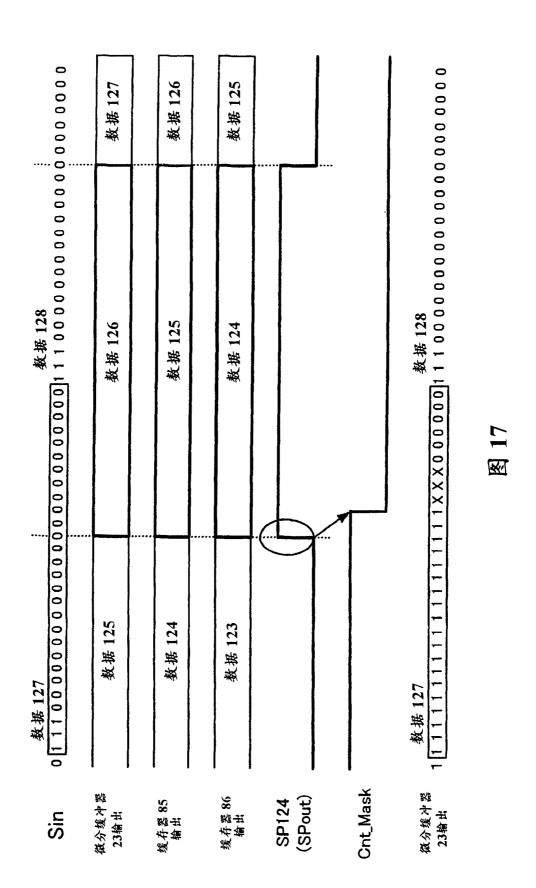

- 图 17 是表示在源极驱动器 IC 20 中分配数据的定时示意图。

- 图 18 是表示产生 Cnt\_Mask 信号的顺序的示意图。

- 图 19 是描述图 3 中輸出微分缓冲器 23 和 24 的设置的示意图。

- 15 图 20 是解释由常规 LCD 源极驱动器所使用的接口的示意图。

在附图中:

- 1: 液晶盒控制器

- 2: 液晶盒

- 3: 视频接口(I/F)

- 20 **4: LCD 控制器**

- 6: 栅极驱动器

- 7: 源极驱动器

- 11: 接收器

- 12: 序列发生器

- 25 13: 表

- 14: 并行/串行变换器

- 15: PLL 电路

- 16, 17: 微分缓冲器

- 20: 源极驱动器 IC

- 30 21, 22, 23, 24: 微分缓冲器

- 25, 26: 变换器

27: 时钟分频器

28: 串行视频信号接收器

29: 驱动器控制器

30: 灰度补偿电路

5 31: LCD 源极驱动器

41: 标题

42: 数据

44: 同步信息块

45: 指令信息块

10 46: 数据信息块

47: 等待信息块

51: 变换器

52, 53: 4位锁存器

54: 选择器

15 55: 解码器

56: 序列发生器

57: 解码器

58: 同步计数器

81: 移位寄存器

20 82: 锁存器

83: 开关

84, 85, 86, 87: 锁存器

88: 控制器

具体实施方式

25

图 1 是描述根据本发明一个实施例的图象显示器的示意图。液晶 盒控制器 1 和液晶盒 2 构成液晶模块,液晶盒 2 具有与薄膜晶体管 (TFT)相同的液晶结构。将液晶模块安装在与主机系统分开的显示器 上,或安装在笔记本 PC 的显示单元上。在液晶盒控制器 1 中,经过主 30 机系统的视频接口 (I/F) 3,由图形控制器 LSI (没有示出)将 RGB 视频数据 (视频信号)或控制信号传输 LCD 控制器 4。另外,通常经过

视频 I/F3 提供 DC (直流) 电源。一个 DC-DC 转换器 5 使用接收的 DC 电源来产生液晶控制器 1 所需要的 DC 电源电压,并将该电压提供给 栅极驱动器 6、源极驱动器 7 和背面照明荣光管(没有示出)。LCD 控制器 4 处理由视频 I/F3 接收的信号,并将由此所获得的信号传输给 栅极驱动器 6 和源极驱动器 7。在水平方向(X方向)上,源

25

30

极驱动器 7 将要施加的电压输出给在液晶盒 2 上以矩阵方式设置的 TFT 的源极。栅极驱动器 6 将电压输出给设置在垂直方向(Y 方向)上的 TFT 的源极。

由多个 IC 构成栅极驱动器 6 和源极驱动器 7. 在本实施例中,源极驱动器 7 包括多个为 LSI 芯片的源极驱动器 IC 20. 为了方便,在图 1 的描述中,液晶盒控制器 1 和液晶盒 2 是分开的。然而,在本实施例中,根据在形成液晶盒 2 的玻璃基片上的 COG 结构形成源极驱动器 20, 并且依据 WOA 结构各条线也位于玻璃基片上。此外,作为一个特性特征,源极驱动器 IC 的 20 的所有线都是级联(连续连接的或复联的顺序连接)。也就是说,由用于驱动的一对数据信号线和一对时钟信号线代替常规用于驱动的 28 个视频接口信号。因此,仅仅必须使4个 IO 垫位于每一源极驱动器 20 的每一端。在此实例中,在每一源极驱动器 IC 20 的右端和左端输入电源信号,并且通过在芯片中的金属层也使电源级联。用此方案,在玻璃基片上,在紧接着在每一源极驱动器 IC 20 下面的一个部分不需要驱动器接线,为了保护 TFT 可以在适当的部分沉积通常所用的短路环线。

图 2 是解释根据本实例的 LCD 控制器 4 的内部结构图。接收器 11 具有接收和锁存经视频 I/F3 输入的 RGB 视频数据的功能(参见图 1). 根据其中存储有形成信息包的信息的表 3,序列发生器 12 通过作用三种控制信号为 4 位信息包制备标题信息,所述三种控制信号是 VS(垂直同步信号)、HS(水平同步信号)和 DT(显示定时信号)。尤其是,序列发生器制备控制源极驱动器 IC 的指令,例如在消隐周期输出"0000"。此外,序列发生器 12 在水平消隐周期传输用于源极驱动器 IC 20 同步的的同步信号。并行/串行变换器 14 将由接收器 11 锁存和输出的 24 位并行视频数据和由序列发生器 12 产生的 4位标题信息变换为串行数据,并将所得到的串行数据传输给微分缓冲器 16。PLL(锁相环)电路 15 形成 28 倍的时钟并将形成的时钟传输给微分缓冲器 17。然后,微分缓冲器 16 和 17 通过分别将从并行/串行变换器 14 中接收的数据、从 PLL 电路中接收的倍数增加的时钟与具有相反极性的相似数据相加,并将微分信号输出给源极驱动器 IC 20。

15

20

25

图 3 是解释根据本实例的源极驱动器 IC 20 的内部结构的示意图. 源极驱动器包括: 微分缓冲器 21 和 22, 用于接收来自 LCD 控制器 4 和前一源极驱动器 IC 20 的微分信号; 微分缓冲器 23 和 24, 用于将微分信号输出给后一源极驱动器 IC 20; 变换器 25, 用于将从微分缓冲器 22 中接收的微分时钟信号变换为信号时钟; 变换器 26, 用于将从微分缓冲器 21 中接收的微分视频信号变换为单个视频信号(Sin);时钟频率分频器 27, 用于将从变换器 25 接收的时钟变换成低同步频率; 串行视频信号接收器 28, 用于使用串行数据产生合适的4位并行数据; 驱动器控制器 29, 用于控制 LCD 源极驱动器 31; 灰度补偿电路 30, 用于产生参考灰度补偿电压; 和 LCD 源极驱动器 31, 用于接收视频数据并将视频电压施加给液晶盒 2.

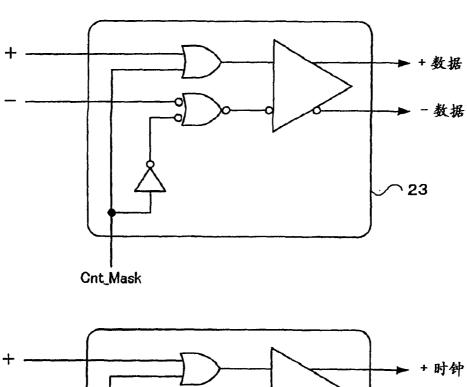

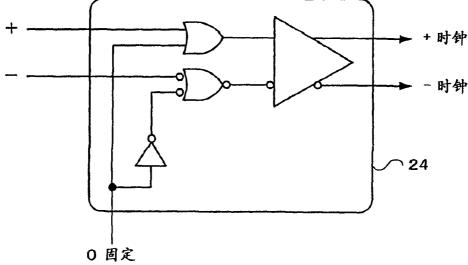

在本实例中, 通过使用由驱动器控制器 29 输出的控制信号 Cnt Mask 可将微分缓冲器 23 和 24 输出的值强制置"1"。使用此方 案,可将用于源极驱动器 IC 20 的视频数据相对于下游源极驱动器 IC 20屏蔽,并且在不需要任何特殊接线的情况下能沿源极驱动器 IC 20 分配视频数据。为了使用微分时钟操作构成源极驱动器 IC 20 的各 个电路, 变换器 25 进行与微分缓冲器 21 和 22 相同的操作。并且当 由外部源输入参考灰度补偿电压而不需要灰度补偿电路 30 时、为了 减少对源极驱动器 IC 20 的输入最好内部产生这样的电压。仅必须 制备多个 10 位正确 DAC 并且仅必须通过本实例的接口下载灰度补偿 数据,公用的LCD源极驱动器可用作LCD源极驱动器31。也就是说, 除图 3 中的灰度补偿电路 30 和 LCD 源极驱动器 31 外, 可将各个电路 的输出带给公用的 LCD 源极驱动器, 从而能实现包括快速串行视频接 口的 LCD 源极驱动器。因为对于 XGA(Extended Graphics Array)(扩 展图形阵列)(1024x768)分辨率而言输入时钟频率大约为 2GHz、所 以最好是使用例如由本发明申请人(IBM)提出的 SiGe(Silicon Germanium)-BiCMOS 技术的方法。在此并不详细地解释 SiGe-BiCMOS 技术。

下面将解释根据本实例的串行传输协议。

30 图 4 是示意图,示出了本实施例所用的串行数据格式的例子。由 LCD 控制器 4 或前一(上游)源极驱动器 IC 20 预备串行数据,并将

串行数据传输给级联的源极驱动器 IC 20。由 28 位携带本实例的串行数据,在本实施例中将此称为信息块。一个信息组由一个具有 4位的标题 41 和具有 24位的数据 42 组成。在图 4 中,根据标题 41,本实施例的协议定义了 4 类信息组,44 至 47。

#### (1) 同步信息块 44

这是一个在消隐周期接收的信息块。标题 41 是 [1000],表示同步信息块,并且数据 41 都是"0"。在此期间,每一源极驱动器 IC 20 都与其接收的视频数据同步。

#### (2) 指令信息块 45

10 这是在消隐周期与任意定时一致地接收到的信息块。代表指令信息块的标题是[1100].每一源极驱动器 IC 20 翻译数据 42 中包含的控制数据,并驱动液晶盒 2。控制数据的例子如下。

(a) 启动视频数据的传输

[0000 - 0000 - 0000 - 0000 - 0000 - 0000]

15 该指令用于通知视频数据传输已经开始。在发出该指令之后,开始使用数据信息块传输视频数据,这将在下面进行描述。

(b) 启动灰度数据传输

[1000 - 1000 - 1000 - 1000 - 1000 - 1000]

该指令用于通知已经开始传输灰度补偿数据(用于产生参考电压 20 的值)。在发出该指令之后,开始使用数据信息块传输灰度数据,这 将在下面进行描述。

(c)选通脉冲通/断

选通脉冲通 [1101-1101-1101-1101-1101-1101] 选通脉冲断 [1100-1100-1100-1100-1100-1100]

25 这些指令用于通知已经开始对液晶盒 2 输出。一接收到指令选通脉冲通,驱动器控制器 29 就将要传输给 LCD 源极驱动器 31 的选通脉冲 (STB) 信号设置为高。而一接收到指令选通脉冲断,驱动器控制器 29 就将要传输给 LCD 源极驱动器 31 的选通脉冲 (STB) 信号设置为低。因而,在选通脉冲为高的期间,对液晶盒 2 的输出可保持在高 30 阻抗状态。

#### (d)输出极性的定义

20

25

正极性输出[1111-1111-1111-1111-1111] 负极性输出[1110-1110-1110-1110-1110-1110]

这些指令用于给液晶盒 2 的电压输出定义极性。一接收到这些指令之一,驱动器控制器 29 就使内部极性控制信号(POL)置位或复位。

#### (3) 数据信息块 46

这是用于传输视频数据或灰度补偿数据的信息块。标题是[1110] 并表示数据信息块,而使用以前传输的指令来识别信息组的内容。

(a)视频数据 [红 8 位] 「绿 8 位] 「蓝 8 位]

顺序传输一行视频数据。对于 XGA, 依次接收 1024 数据信息块 10 46。每一源极驱动器 IC 20 的驱动器 29 仅仅接收其所有的各数据, 并且当其如此做时, 用等待信息块(后面将要描述)代替数据信息块, 将等待信息块传输给后一源极驱动器 IC 20。

(b) 灰度补偿数据 [灰度 10 位] [000000000000000]

这是在产生具有 10 位精度的参考灰度补偿电压的地方为灰度补 15 偿而传输所需数量的数据位所情况。所有源极驱动器 IC 20 的驱动器 29 可以接收相同的数据或接收不同的数据。

#### (4) 等待信息块

仅仅由源极驱动器 IC 20 使用等待信息块。标题 41 是[1111] (等待)并表示等待信息块。在接收视频数据期间,每一源极驱动器 IC 20 将等待信息块 47 传输给后一源极驱动器 IC 20。在接收等待信息块 47 期间,源极驱动器 IC 20 不进行任何处理,并等待接收包含在等待信息块 46 中的视频数据。

图 5A、5B和 5C 是描述由序列信息块组成的串行信号传输的示意图。在图 5A中,示出了设置每一源极驱动器 IC 20 灰度补偿数据的起始状态。首先,在由许多邻接同步信息块 44 提供的同步周期中,源极驱动器获得同步。接着接收在指令信息块 45 中的灰度数据传输启动指令,并然后接收在数据信息块 46 中的灰度补偿数据。正如前面所描述的,灰度补偿数据由所需数量的数据信息块 46 组成。

图 5B 是表示通过使用第一源极驱动器 IC 20 的第一芯片的输入 30 和下一源极驱动器 IC 20 的第二芯片的输入来传输 n 行视频数据的示 意图。在消隐周期(Sync:同步周期)之后,接收指令信息块 45 中的

15

20

25

30

视频数据传输启动指令,并然后接收每一行的视频数据。接着,在适当的时候接收选通脉冲通。在此时,源极驱动器 IC 20 对液晶盒 2 开始写入数据。实际上,当下一次接收选通脉冲断指令时将电压施加到液晶盒 2 上,并且输出一直保持在高阻抗状态,直到当下一次接收选通脉冲断指令时为止。由在选通脉冲通和选通脉冲断之间发出的输出极性定义指令选择正极性输出。在接收其所有的各视频数据期间,在图 5B 上部中的第一芯片给后一级源极驱动器 IC 20 (第二芯片)传输等待信息块 47。在下部的第二芯片跳过等待信息块 47,开始接收视频数据并将数据写入液晶盒 2 中。

图 5C 是表示传输 n+1 行视频数据的示意图。与图 5B 的差别在于选择负极性输出作为输出极性。

正如前面所述,根据本实施例,使用 4 信息块来传输视频数据并控制源极驱动器 IC 20。结果是,所有用于常规 LCD 源极驱动器的控制输入引线都不需要,并且能执行 WOA。

现在描述图 3 中串行视频信号接收器 28 的设置。

图 6 是描述串行视频信号接收器 28 的布置的示意图。串行视频信号接收器 28 使用包含在接收到的串行数据中的同步信息块 44 来自动取得同步,并且输出其标题已经调整的并行数据的 4位。在图 6 中,变换器 51 将串行数据变换成并行数据的 4位,并且 4位锁存器 52 和 53 锁存由变换器 51 输出的串行数据。选择器 54 从 7 个信号 (A0 至 A2 和 B0 至 B3) 中选择 4 个信号。一个解码器 55 对 4 位锁存器 52 的输出进行解码,序列发生器 56 使用由解码器 55 获得的输出来进行同步并控制选择器 54。解码器 57 对选择器 54 的输出进行解码。一个 3 位同步计数器 58 存储信息块的标题位置。

变换器 51 和 4 位锁存器 52、53 将串行数据变换为具有 8 位宽度的并行数据。以所有源极驱动器 IC 20 的组成电路的最高速度操作该部分,并且对于该部分需要小型电路。图 7 是表示使用变换器 51、4 位锁存器 52 和 4 位锁存器 53 的串行/并行变换功能例子的示意图。通过使用 D 触发器 (D-flip-flops)来实现这一功能。在图 7 中,当以 2GHz 输入串行数据时信号/时钟代表信号和时钟的操作频率。将变换器 51 接收的串行数据变换为并行数据,并以 1 GHz 输出可取样

20

25

30

的 1 GHz 时钟和数据(信号)。然后,经过 4 位锁存器 52 和 53 的 D - FF 传输该数据,并以 500MHz 输出可取样的 500MHz 时钟和数据(信号)。

图 6 中的解码器 55 对 4 位锁存器 52 的输出进行解码,并检索同步信息块 44 的标题 41。由 4 位比较器构成解码器 55。图 8 是表示标题 41 的比较图形和选择器 54 的输出之间关系的示意图。左边的一列表示 n 时钟的 4 位锁存器 52 的输出;中间的一列表示 n+1 时钟的选择器 54 的输出;右边的一列表示由序列发生器 56 输出的并且被传输给选择器 54 的控制 ID。一接收到控制 ID,选择器 54 就输出中间一列中的信号。每一比较器将输入 (A3, A2, A1, A0)与图 8 中的位模式进行比较。仅仅在数据的同步出现的期间,序列发生器 56 使用解码器 55 的结果来控制选择器 54,如图 8 所示,并且恢复数据同步。选择器的状态一经设置,就保持该状态直到数据的同步出现为止。

由 4 位比较器构成解码器 57,解码器 57 对选择器 54 的输出进行解码以确定是否已经保持数据同步。图 9 是表示进行数据同步的模式的示意图。如图 9 所示,由 4 位比较器比较的模式是由 4 种信息块组成的标题 41,的模式。序列发生器 56 在适当的时候监视比较结果,并且,如果已经出现异步则恢复数据同步。当例如接通电源或在串行信号线上叠加噪声时,或当重新启动视频数据时,出现数据异步。在此情况下,由解码器 55 和序列发生器 56 提取差错位序列。在本实例中,通过检查解码器 57 的输出能确认数据同步,并且如果出现异步能恢复数据同步。

在产生信息块的标题 41 作为选择器 54 的输出的地方同步计数器 58 传输时间标记。在本实施例中,由于一信息块包括 28 位,选择器 54 的每隔 6 个输出将产生标题 41。因此,在使数据同步的期间(通知序列发生器 56),当解码器 55 发现同步信息块 44 的标题 41 时,同步计数器 58 复位并然后从 0 至 6 重复计数,当同步计数器指示 0 时产生标题 41 作为选择器 54 的输出。序列发生器 56 利用该时间标记来监视解码器 57 的输出以确定是否实现数据同步。

图 10 是表示序列发生器 56 的状态移动的示意图. 当同步计数器 58 指示 0 时出现序列发生器 56 的状态移动. 首先, 当系统复位时,

15

20

25

序列发生器 56 处于"同步恢复"状态 61。在此期间,根据解码器 55 所得到的结果来控制选择器 54,并自动进行数据同步和数据跟踪。当解码器 57 正确地探测到同步信息块的标题 41 时,序列发生器 56 移动到"同步信息块接收"状态 62。在此状态,仅仅序列发生器 56 接收同步信息块 44,并且不进行其它处理。序列发生器 56 接收指令信息块 45 的标题指令时,序列发生器 56 移动到"指令信息块接收"状态 63。如果接收到没有定义位模式,序列发生器 56 将其当作误码,并返回到"同步恢复"状态 61 以再获得数据同步。在"指令信息块接收"状态 63,序列发生器接收各种控制指令。在"数据信息块接收"状态 64,序列发生器 56 接收视频数据或灰度补偿数据。在"等待信息块接收"状态,序列发生器 56 等待接收数据信息块 46。在此期间,在目标源极驱动器 IC 20 上游的源极驱动器 IC 20 进行视频数据取样。目标源极驱动器 IC 20 接收数据信息块 46 以及前一等待信息块47,将该信息组 46 存储在 LCD 源极驱动器 31 中的视频数据存储器(没有示出)中。

图 11 是表示由用于数据同步的串行视频信号接收器 28 执行的操作的示意图. 在图 11 中,bn (b3 至 b0) 71 表示变换器 51 的输出,An (A3 至 A0) 72 表示 4 位锁存器 52 的输出,Bn (B3 至 B0) 73 表示 4 位锁存器 53 的输出。Exxx74 表示由解码器 55 所获得的结果,Sync、Command 和 Data 表示由解码器 57 所获得的结果。Hcounter 75 表示同步计数器 58 的值,并且,当该值为 0 时,移动序列发生器 56 的状态。Control 76 表示用于选择器 54 的控制信号,并起着如图 8 所示的作用。State 77 表示序列发生器 56 的状态; 0 表示"同步恢复"状态 61,1 表示"同步信息块接收"状态 62,2 表示"指令信息块接收"状态 63,3 表示"数据信息块接收"状态 64,而 Dn (D3 至 D0)表示器 54 的输出。在图 11 中,示出了串行输入稳定的过程,在此过程后,按所列的顺序输入 Sync、Command 和 Data 以获得数据同步。对于数据同步需要至少两个循环。

下面将描述图 3 中的驱动器控制器 29 的设置。

30 图 12 是描述驱动器控制器 29 的设置的示意图。如图 12 所示, 驱动器控制器 29 使用一个 4 位、7 电位移位寄存器 81 将由串行视频

20

25

30

信号接收器 28 获得的 4 位并行数据变换为 28 位并行数据。此外,在同步计数器 58 指示 0 时,将移位寄存器 81 的输出存储在 28 位锁存器 82 中。通过由控制器 88 提供控制的开关 83 将存储锁存器 82 中的数据的 24 位存储在 24 位锁存器 84 或 87 中。存在锁存器 84 中的数据是视频信号并被输出给图 3 中的 LCD 源极驱动器 31。锁存器 84 包括两极:一个锁存器 85 和一个锁存器 86,能匹配两极锁存器的定时。存储在锁存器 87 中的数据是灰度补偿数据并被输出给图 3 中的灰度补偿电路 30. 根据事先接收的指令是否是启动视频数据传输或启动灰度数据传输的指令提供开关 83 的控制。

根据接收的指令,控制器 88 产生控制信号并将该控制信号传输给 LCD 源极驱动器 31, 在图 12 中该控制信号包括 Spin、STB、POL。Spin是在接收视频数据时产生的取样启动脉冲; STB 是用于控制对液晶盒 2 的输出的信号,一接收选通脉冲通指令就输出高电平并且一接收选通脉冲断指令就输出低电平; POL 是用于控制对液晶盒 2 的输出极性的信号,一接收正极性输出指令就输出高电平并且一接收负极性输出指令就输出低电平。控制器 88 还接收来自 LCD 源极驱动器 31 的信号 SPout,该信号为一终端的芯片提供视频数据取样的时间通知。因此,控制器 88 使用信号 Spout 和由串行视频信号接收器 28 接收的 4位数据来产生 Cnt\_Mask, Cnt\_Mask 是产生等待信息块 47 的信号。控制器还输出选通脉冲信号以通知接收灰度补偿数据的图 3 中的灰度补偿电路 30。

图 13A 和 13B 示出了产生控制信号过程(波形和每一控制信号的状态的移位)。在图 13A 中,锁存器 82 表示代表图 12 中的锁存器 82的输出,锁存器 85 和 86 代表锁存的并经开关 83 输出给 LCD 源极驱动器 31 的视频数据。如图 13B 所示,当在发出视频数据传输启动指令(Cmd Video)后接收第一视频数据时,输出一个脉冲信号 Spin.也就是说,状态由 0 移到 1.而且,一接收选通脉冲通指令(Cmd StbOn)就使信号 STB 置 1,一接收选通脉冲断指令(Cmd StbOf)就清除信号 STB。此外,一接收输出极性定义指令(Cmd Pos/Cmd Neg),就使信号 POL 移位到代表指定极性的一位。在本实施例中。以输入时钟的 1/28 的频率操作控制器 88.

15

20

25

30

图 14 至 18 是表示由等待信息块 47 的产生而引起视频数据分配的示意图。图 14 是表示当开始产生等待信息块 47 时数据传输的示意图。所有的源极驱动器 IC 20 都进行相同的操作。经过图 6 中的变换器 51、4 位锁存器 52 和 53、选择器 54 将串行视频数据传输给图 12 中的控制器 88。串行视频信号是大约 2GHz 的信号,其它是大约 500MHz (2 GHz 的 1/4) 的信号。在选择器 54 输出信息块的标题 41 时(图 6 中的同步计数器 58 输出 0 时),通知控制器 88:输入信息块是指令信息块 45;在下一 5000 MHz 时钟告知控制器 88:指令是视频数据传输启动指令。此时,由于自动变换器的定时,4 个 2 GHz 时钟的变化出现在 Cnt\_Mask 置 1 的 Cnt\_Mask 转换点。然而,由于在接收紧接在指令信息块之后的数据信息块 41 的标题之前,仍然剩下额外的时间,所以能将标题 [1110]变成 [1111],即,能将数据信息块 46 变换为等待信息块 47。此外,尽管在 Cnt\_Mask 从 0 变为 1 时微分缓冲器 23的输出不稳定,但就后一源极驱动器 IC 20 来说这一周期本来并没有意义并且没有出现问题。

图 15 是表示延时从输入串行视频数据开始直到完成 24 位数据为止的示意图。在图 15 中,示出了延时持续到由图 12 中的锁存器 82获得的 24 位数据为止。图 16 是表示输出给 LCD 源极驱动器 31 的数据和取样数据的定时示意图。在图 16 中,经过图 12 中的锁存器 85和 86将锁存器 82的 24位数据传输给图 3 中的 LCD 源极驱动器 31. SPin 是取样启动脉冲,SPn (SP0, SP1, SP2, SP3...··)是引入 LCD 源极驱动器 31 中的移位寄存器的输出。当 SPin 是 1 时,存储第 n 个数据。图 17 是表示根据图 15 和 16 在源极驱动器 IC 20 中分配数据的定时示意图。在图 17 中使用 384个输出引线(128 X 3 (RGB))的源极驱动器 IC 20 读出数据 0 至数据 127. 从图 17 明显看出,在图 12 中的控制器 88 使用 SP124 作为 SPout,SP124 代表存储数据 124 的定时以使 Cnt\_Mask 在适当的时候返回到 0.当 Cnt\_Mask 已经返回到 0 时,代表等待信息块 47 的串行视频信号变为最初数据信息块 46,从而后一源极驱动器 IC 20 能正确地接收视频数据。

正如前面所述,由于控制 Cnt\_Mask 信号,所以能在级联的源极

15

20

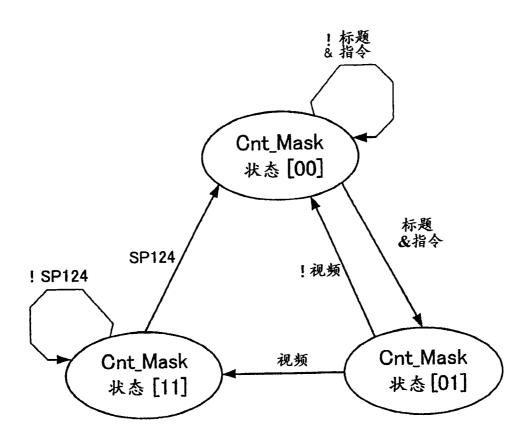

驱动器 IC 20 中正确地分配将视频数据。图 18 是表示产生 Cnt\_Mask 信号的顺序的示意图。每 1/4 时钟(在本实例中 500 MHz)移位状态。在状态[11]使 Cnt\_Mask 置为 1,而在其它状态将 Cnt\_Mask 置为 0。

图 19 是描述图 3 中输出微分缓冲器 23 和 24 的设置的示意图. 在图 19 中,当 Cnt\_Mask 信号为 1 时,使用于视频数据的微分缓冲器 23 的正输出(+数据)为 0。为了让用于时钟的微分缓冲器 24 的特性与视频数据微分缓冲器 23 的匹配,微分缓冲器 24 与微分缓冲器 23 具有相同的结构,并且使控制输入固定为 0。

正如前面所述,在本实例中,将信号垫和电源垫设置在源极驱动器 IC 20 的两侧,源极驱动器 IC 20 为芯片,并且在芯片中的所有线路都是级联连接。此外,由在芯片内具有的金属层也级联电源。结果是,能去掉用于芯片的总线连接,并且能提供 WOA。此外,在视频信号水平消隐时期,传输两个循环的同步图形。并且,在视频数据的传输时期,监视每一信息块的标题图形以确认数据同步。因此,即使当出现误操作时,在一行之后也能恢复数据同步。另外,通过数据包的传输,每一源极驱动器 IC 20 仅使用视频传输线就能控制操作。结果是,不需要通常预备的控制输入端,并且能大大地减少线的数量。而且,由于每一源极驱动器 IC 20 屏蔽其所有的视频数据,所以当属于一个源极驱动器 IC 20 的视频数据没有泄露给后一驱动器时能在芯片中分配视频数据。因而,仅由视频数据传输线也能完成视频数据的分配。

正如上面所述,根据本发明,能减少对 LCD 驱动器的输入端数量,并通过使用 COG&WOA 技术能减少生产成本。

此外,能提供仅需要少量功率的小型、快速串行接口并且能使高 25 速操作电路的数量减为最少,从而能限制功耗和芯片尺寸的增加。

图 3

| 4位锁存器 (n时钟)<br>[A3, A2, A1, A0] | 选择器 (n + 1时钟)<br>[D3, D2, D1, D0] | 控制 ID |

|---------------------------------|-----------------------------------|-------|

| [1, 0, 0, 0]                    | [A2, A1, A0, B3]                  | 0     |

| [0, 1, 0, 0]                    | [A1, A0, B3, B2]                  | 1     |

| [0, 0, 1, 0]                    | [A0, B3, B2, B1]                  | 2     |

| [0, 0, 0, 1]                    | [B3, B2, B1, B0]                  | 3     |

# 图 8

| 信息块类型 | 与选择器输出比较图形<br>[D3, D2, D1, D0] |  |

|-------|--------------------------------|--|

| 同步    | [0, 0, 0, 1]                   |  |

| 指令    | [0, 0, 1, 1]                   |  |

| 数据    | [0, 1, 1, 1]                   |  |

| 等待    | [1, 1, 1, 1]                   |  |

图 9

图 10

35

38

图 18

图 19

| 专利名称(译)        | 液晶显示器、液晶控制器和视频信息                                                         | 号传输方法   |            |  |  |

|----------------|--------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号        | <u>CN1193260C</u>                                                        | 公开(公告)日 | 2005-03-16 |  |  |

| 申请号            | CN00135262.8                                                             | 申请日     | 2000-12-11 |  |  |

| [标]申请(专利权)人(译) | 国际商业机器公司                                                                 |         |            |  |  |

| 申请(专利权)人(译)    | 国际商业机器公司                                                                 |         |            |  |  |

| 当前申请(专利权)人(译)  | 国际商业机器公司                                                                 |         |            |  |  |

| [标]发明人         | 坂口佳民<br>S德斯格雷兹                                                           |         |            |  |  |

| 发明人            | 坂口佳民<br>S·德斯格雷兹                                                          |         |            |  |  |

| IPC分类号         | G02F1/133 G02F1/1345 G09G3/20 G09G3/36 H04N5/66                          |         |            |  |  |

| CPC分类号         | G09G3/3688 G09G2300/0408 G09G2310/027 G09G3/3611 G09G2310/08 G09G2370/08 |         |            |  |  |

| 代理人(译)         | 王岳                                                                       |         |            |  |  |

| 优先权            | 1999351784 1999-12-10 JP                                                 |         |            |  |  |

| 其他公开文献         | CN1299982A                                                               |         |            |  |  |

| 外部链接           | Espacenet SIPO                                                           |         |            |  |  |

|                |                                                                          |         |            |  |  |

#### 摘要(译)

本发明的一个目的是减少对LCD驱动器的输入端的数量,并通过使用COG&WOA技术减少生产成本。对于液晶显示器,源极驱动器IC20级联,通过视频I/F3在源极驱动器IC20中传输视频信号并在源极驱动器IC20中分配视频信号,并且,使用COG&WOA技术,尽可能地减少与源极驱动器IC20的连接线。也就是说,液晶显示器包括:一个在基片上形成图象显示区域的液晶盒2;一个源极驱动器7,经过视频I/F3根据视频信号输入将电压施加到所述液晶盒2上。源极驱动器7包括多个安装在与液晶盒2相同的基片上并使用信号线级联的源极驱动器IC20。