# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**G09G 3/36** (2006.01) **G02F 1/133** (2006.01)

(21) 출원번호 **10-2014-0181235**

(22) 출원일자 **2014년12월16일** 심사청구일자 **2019년11월04일**

(65) 공개번호 **10-2016-0073446**

(43) 공개일자 **2016년06월27일**

(56) 선행기술조사문헌

KR1020080013190 A\*

KR1020100023083 A\*

KR1020110068238 A\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2021년06월22일

(11) 등록번호 10-2268008

(24) 등록일자 2021년06월16일

(73) 특허권자

### 엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

#### 박선자

경상북도 칠곡군 석적읍 동중리9길 13 C동 209호 (중리,LG디스플레이나래원기숙사)

#### 이대진

대구광역시 남구 현충로 40 (대명동) 92 (*뒷면에 계속*)

(74) 대리인

특허법인(유한) 대아

전체 청구항 수 : 총 8 항

심사관 : 추장희

### (54) 발명의 명칭 액정표시장치

#### (57) 요 약

본 발명의 실시예에 따른 액정표시장치는 제1 박막 트랜지스터가 배치된 비표시영역과 제2 박막 트랜지스터가 배치된 표시영역을 포함하는 표시패널, 상기 제1 박막 트랜지스터의 게이트 단자의 공급되는 테스트 게이트 신호의레벨에 따른 상기 제1 박막 트랜지스터의 오프 커런트(off current)를 검출하는 오프 커런트 검출부 및 상기 오프 커런트의 검출 결과를 기초하여 생성된 게이트 신호를 상기 제2 박막트랜지스터에 인가하는 구동부를 포함한다.

### 대 표 도 - 도3

(72) 발명자

곽동곤

# 김현호

대구광역시 북구 연암공원로14길 9-1 (산격동)

경상북도 구미시 상사서로 18 109동 1601호 (상모동,우방신세계타운)

# 명 세 서

# 청구범위

#### 청구항 1

제1 박막 트랜지스터가 배치된 비표시영역과 제2 박막 트랜지스터가 배치된 표시영역을 포함하는 표시패널;

상기 제1 박막 트랜지스터의 게이트 단자의 공급되는 테스트 게이트 신호의 레벨에 따른 상기 제1 박막 트랜지스터의 오프 커런트(off current)를 검출하는 오프 커런트 검출부; 및

상기 오프 커런트의 검출 결과를 기초하여 생성된 게이트 신호를 상기 제2 박막트랜지스터에 인가하는 구동부; 를 포함하고,

상기 오프 커런트 검출부는 상기 테스트 게이트 신호의 로우 레벨을 가변 시켜, 상기 오프 커런트가 최소가 되는 최소 오프 커런트를 검출하고, 상기 최소 오프 커런트를 만족시키는 상기 테스트 게이트 신호의 로우 레벨을 타이밍 콘트롤러 또는 파워부로 출력하고,

상기 타이밍 콘트롤러 또는 상기 파워부는 상기 구동부로부터 출력되어 상기 표시영역 내의 상기 제2 박막 트랜지스터에 공급되는 상기 게이트 신호의 로우 레벨을 조절하여, 상기 제2 박막 트랜지스터의 오프 커런트를 최소화하는 액정표시장치.

#### 청구항 2

제1 항에 있어서,

상기 오프 커런트 검출부는,

상기 제1 박막 트랜지스터의 오프 커런트가 기 설정 범위를 충족하도록 하는 상기 테스트 게이트 신호의 레벨을 검출하는 액정표시장치.

#### 청구항 3

제2 항에 있어서,

상기 기 설정 범위는 상기 제1 박막 트랜지스터의 오프 커런트의 최소값을 포함하는 액정표시장치.

#### 청구항 4

제1 항에 있어서,

상기 제1 및 제2 박막 트랜지스터의 종횡비는 동일한 액정표시장치.

## 청구항 5

제1 항에 있어서.

상기 구동부는 상기 오프 커런트 검출부의 검출 결과를 기초하여 상기 게이트 신호의 로우(Low) 레벨을 조절하는 액정표시장치.

## 청구항 6

제1 항에 있어서,

상기 제1 박막 트랜지스터는 적어도 하나 이상의 박막 트랜지스터를 포함하는 액정표시장치.

#### 청구항 7

제1 항에 있어서,

상기 표시패널의 온도를 검출하는 온도 검출부;를 더 포함하고,

상기 온도 검출부에 의해 검출된 상기 표시패널의 온도가 제1 기 설정 온도 이상 또는 제2 기 설정 온도 이하가 되는 경우 상기 오프 커런트 검출부는 상기 제1 박막 트랜지스터의 오프 커런트를 검출하는 액정표시장치.

#### 청구항 8

제1 항에 있어서,

상기 오프 커런트 검출부는,

상기 제1 박막 트랜지스터에 상기 테스트 게이트 신호 및 테스트 데이터 신호를 공급하는 테스트 신호 공급부;

상기 테스트 게이트 신호의 레벨의 변화에 따른 상기 제1 박막 트랜지스터의 오프 커런트를 검출하는 검출부; 및

상기 오프 커런트가 기 설정 범위에 해당할 때 상기 테스트 게이트 신호를 피드백 받아 상기 구동부로 출력하는 피드백부;를 포함하는 액정표시장치.

#### 발명의 설명

## 기술분야

[0001] 본 발명은 액정표시장치에 관한 발명으로 구체적으로는 액정표시장치의 박막 트랜지스터의 오프 커런트를 최소화하기 위한 발명이다.

#### 배경기술

- [0002] 휴대폰(Mobile Phone), 노트북, 컴퓨터와 같은 각종 포터플기기(potable device) 및, HDTV 등의 고해상도, 고 품질의 영상을 구현하는 정보전자장치가 발전함에 따라, 이에 적용되는 평판표시장치(Flat Panel Display Device)에 대한 수요가 점차 증대되고 있다. 이러한 평판표시장치로는 LCD(Liquid Crystal Display), PDP(Plasma Display Panel), FED(Field Emission Display) 및 OLED(Organic Light Emitting Diodes) 등이 활 발히 연구되었지만, 양산화 기술, 구동수단의 용이성, 고화질의 구현, 대면적 화면의 실현이라는 이유로 인해 현재에는 액정표시장치(LCD)가 각광을 받고 있다. 최근에는 3D 디스플레이와 플렉시블 디스플레이로의 영역으로 확대되고 있다.

- [0003] 박막 트랜지스터(Thin film transistor; TFT) 액정표시장치는 스위치 소자를 TFT로 구성하여 각 화소에 위치시 켜서 제어를 개별적으로 수행하는 능동 매트릭스(Active matrix) 구조는 단순 매트릭스 구조에 비해 해상도, 대비비, 시야각 특성을 향상시킬 수 있는 구조이다.

- [0004] 능동 매트릭스 구조는 순차적으로 턴 온(Turn On)되는 게이트 신호(Gate Signal)에 의하여 턴 온 된 수평 라인 (Horizontal line)의 박막트랜지스터에 일괄적으로 인가되는 데이터 신호(Data signal)가 스캔(Scan) 되고 게이트 턴 오프(Gate turn Off) 후 다음 프레임(Frame)까지 화소(Pixel) 전압에 충전된 차지(Charge)를 홀딩 (Holding) 하는 구동 원리로 동작하게 된다.

- [0005] 이때, 1 프레임(1 Frame)을 수직 해상도(Gate Line 수 )로 나눈 시간 동안 1H 해당 화소(Pixel) 전압을 데이터 신호로 충, 방전하게 되는데 상온 환경에서 박막 트랜지스터(Transistor)의 특성 즉, 누설 전류(오프 커런트; Off Current)에 의존하는 홀딩(Holding) 특성을 최적화하여 게이트 전압을 설정한다. 그러나 고온 구동 환경에서 박막트랜지스터의 특성 변화로 누설 전류(Ioff)의 쉬프트(Shift) 가 발생하여 화소 전압의 홀딩 구간 내에서 누설 전류가 커짐에 따라 액정패널(Panel)내 차징(Charging) 특성이 저하되어 화질 불량이 발생하는 문제가 있다. 이때 엔지니어(Engineer)가 상온에서 게이트 신호의 레벨을 가변한 후 다시 고온에 투입하여 불량 발생 여부를 확인해야 하므로 공정의 시간이 증가하는 문제가 있다.

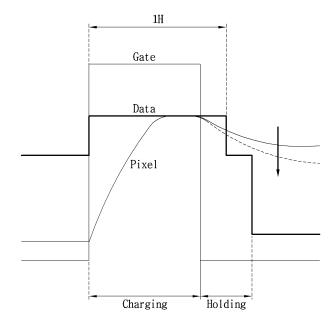

- [0006] 도 1은 누설 전류에 따른 홀딩 구간에서의 화소 전압의 변동을 나타내는 파형도이다.

- [0007] 게이트 전압(Gate)과 데이터 신호(Data)에 따라 화소에 전압(Pixel)이 중전되고(Chaging), 홀딩(Holing) 구간 동안 화소 전극의 누설 전류에 따라 화소 전압이 화살표 방향으로 떨어지는 문제가 있다. 그리하여 화질 불량 문제가 있고, 이를 개선하기 위하여 엔지니어가 최적의 게이터 신호의 레벨을 설정하는데 있어서 공정 시간의 로스(Loss)가 커지는 문제가 있다.

- [0008] 특히 현재 박막트랜지스터에는 비정질 실리콘(a-Si:H)이 많이 적용되고 있으나, a-Si:H TFT는 단결정 Si 및 다

결정 Si에 비해 낮은 전자 이동도, 온도 및 빛에 의한 높은 누설전류, 장시간 동작 시 문턱 전압(threshold voltage)의 쉬프트(shift) 따른 회로의 불안정성이 문제되고, 이러한 비정질 실리콘을 적용한 박막트랜지스터의 경우 전술한 문제점이 더 크게 부각되고 있다.

# 발명의 내용

## 해결하려는 과제

- [0009] 본 발명의 실시예에 따른 액정표시장치는 박막 트랜지스터의 오프 커런트를 최소화할 수 있는 액정표시장치를 제공할 수 있다.

- [0010] 또한 본 발명의 실시예에 따른 액정표시장치는 고온 환경에서 박막 트랜지스터의 특성 변화로 오프 커런트의 쉬 프트가 발생할 때 최적의 게이트 전압의 레벨을 설정하여 오프 커런트를 최소화하여 화질을 개선할 수 있는 액 정표시장치를 제공할 수도 있다.

## 과제의 해결 수단

[0011]

본 발명의 실시예에 따른 액정표시장치는 제1 박막 트랜지스터가 배치된 비표시영역과 제2 박막 트랜지스터가 배치된 표시영역을 포함하는 표시패널, 상기 제1 박막 트랜지스터의 게이트 단자의 공급되는 테스트 게이트 신 호의 레벨에 따른 상기 제1 박막 트랜지스터의 오프 커런트(off current)를 검출하는 오프 커런트 검출부 및 상 기 오프 커런트의 검출 결과를 기초하여 생성된 게이트 신호를 상기 제2 박막트랜지스터에 인가하는 구동부를 포함한다. 그리하여 상기 테스트용 박막 트랜지스터인 제1 박막 트랜지스터의 특성을 검출하여 이를 기초로 상 기 표시영역 내의 제2 박막 트랜지스터에 인가되는 게이트 신호의 레벨을 조절함으로써, 상기 표시영역 내의 제 2 박막 트랜지스터의 특성 변화에 따른 오프 커런트를 최소화할 수 있다. 또한 상기 오프 커런트 검출부는, 상 기 제1 박막 트랜지스터의 오프 커런트가 기 설정 범위를 충족하도록 하는 상기 테스트 게이트 신호의 레벨을 검출하고, 상기 기 설정 범위는 상기 제1 박막 트랜지스터의 오프 커런트의 최소값을 포함하고, 상기 제1 및 제 2 박막 트랜지스터의 종횡비는 동일하다. 즉, 상기 제1 및 제2 박막 트랜지스터를 동일 환경에서 동일 조건하에 서, 각각의 채널(Channel) 폭(W)과 길이(L)에 관한 종횡비(W/L)를 동일하게 설계할 수 있다. 그리하여 상기 제1 및 제2 박막 트랜지스터의 특성이 매우 유사하도록 함으로써, 모니터링을 위한 제1 박막 트랜지스터의 오프 커 런트에 대한 정보를 기초하여 제2 박막 트랜지스터의 오프 커런트에 관한 정보를 획득할 수 있도록 할 수 있다. 또한 상기 구동부는 상기 오프 커런트 검출부의 검출 결과를 기초하여 상기 게이트 신호의 로우(Low) 레벨을 조 절하고, 상기 제1 박막 트랜지스터는 적어도 하나 이상의 박막 트랜지스터를 포함하고, 상기 표시패널의 온도를 검출하는 온도 검출부를 더 포함하고, 상기 온도 검출부에 의해 검출된 상기 표시패널의 온도가 제1 기 설정 온 도 이상 또는 제2 기 설정 온도 이하가 되는 경우 상기 오프 커런트 검출부는 상기 제1 박막 트랜지스터의 오프 커런트를 검출하고, 상기 오프 커런트 검출부는, 상기 제1 박막 트랜지스터에 상기 테스트 게이트 신호 및 테스 트 데이터 신호를 공급하는 테스트 신호 공급부, 상기 테스트 게이트 신호의 레벨의 변화에 따른 상기 제1 박막 트랜지스터의 오프 커런트를 검출하는 검출부 및 기 오프 커런트가 기 설정 범위에 해당할 때 상기 테스트 게이 트 신호를 피드백 받아 상기 구동부로 출력하는 피드백부를 포함하는 액정표시장치를 제공한다. 이를 통해 본 발명의 실시예에 따른 액정표시장치는 저온 또는 고온 구동 환경에서 최적의 게이트 신호의 레벨을 설정하기 위 해 표시영역 내의 제2 박막트랜지스터의 유효한 전압 영역을 기준으로 게이트 로우 신호를 가변 및 보상함으로 써, 온도 변화에 따른 제2 박막트랜지스터의 특성 변화를 보상하고 그에 따라 화소 전극의 홀딩 구간 내에서의 오프 커런트를 최소화하여 화질을 개선할 수 있다. 또한 주변 환경 변화에 대응하여 게이트 로우 신호의 레벨을 조절함으로써 화상의 품질을 유지할 수 있다. 또한 액정표시장치의 제조 과정에서 최적의 게이트 신호의 레벨을 셋팅하는데 소요되는 시간을 줄여 공정 시간과 검사 비용을 절감할 수 있다.

# 발명의 효과

[0012] 본 발명의 실시예에 따른 액정표시장치는 박막 트랜지스터의 오프 커런트를 최소화할 수 있는 액정표시장치에 관한 발명으로 고온 환경에서 박막 트랜지스터의 특성 변화로 오프 커런트의 쉬프트가 발생할 때 최적의 게이트 전압의 레벨을 설정하여 오프 커런트를 최소화하여 화질을 개선할 수 있는 액정표시장치를 제공할 수 있다.

#### 도면의 간단한 설명

[0013] 도 1은 누설 전류에 따른 홀딩 구간에서의 화소 전압의 변동을 나타내는 파형도.

도 2는 본 발명의 실시예에 따른 액정표시장치를 나타낸 도면.

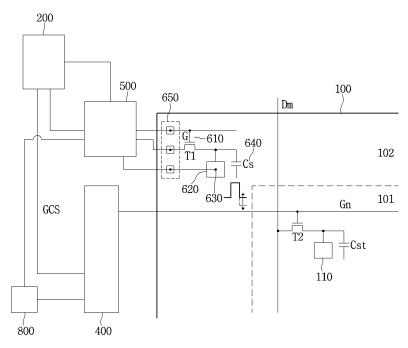

도 3은 본 발명의 실시예에 따른 오프 커런트 검출부를 나타낸 도면.

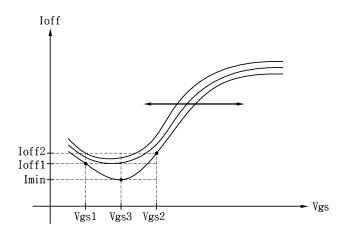

도 4는 제1 박막 트랜지스터의 게이트-소스 단자의 전압에 따른 오프 커런트를 나타낸 그래프.

도 5는 비표시영역 내의 제1 박막 트랜지스터와 표시영역 내의 제2 박막 트랜지스터를 포함하는 액정표시장치의 일부를 나타낸 도면.

#### 발명을 실시하기 위한 구체적인 내용

- [0014] 이하, 본 발명의 실시예에 의한 액정표시장치의 도면을 참고하여 상세하게 설명한다. 다음에 소개되는 실시 예들은 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 예로서 제공되는 것이다. 따라서, 본 발명은 이하 설명되는 실시 예들에 한정되지 않고 다른 형태로 구체화될 수도 있다. 그리고, 도면들에 있어서, 장치의 크기 및 두께 등은 편의를 위하여 과장되어 표현될 수도 있다. 명세서 전체에 걸쳐서 동일한 참조 번호들은 동일한 구성요소들을 나타낸다.

- [0015] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나, 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성요소를 지칭한다. 도면에서 층 및 영역들의 크기 및 상대적인 크기는 설명의 명료성을 위해 과장될 수 있다.

- [0016] 본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며, 따라서 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 "포함한다 (comprise)" 및/또는 "포함하는(comprising)"은 언급된 구성요소, 단계, 동작 및/또는 소자는 하나 이상의 다른 구성요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다.

- [0017] <실시예에 따른 액정표시장치>

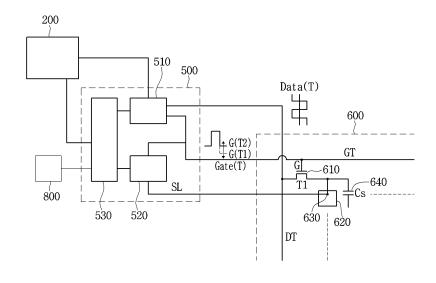

- [0018] 도 2는 본 발명의 실시예에 따른 액정표시장치를 나타낸 도면이다.

- [0019] 도 2를 참조하면, 본 발명의 실시예에 따른 액정표시장치(10)는 표시패널(100), 타이밍 콘트롤러(200), 데이터 구동회로(300), 게이트 구동회로(400) 및 파워부(800)를 구비할 수 있다. 그리고 상기 타이밍 콘트롤러(200), 데이터 구동회로(300), 게이트 구동회로(400) 및 파워부(800)를 표시패널(100)을 구동하기 위한 구동부로 지칭할 수 있다. 그리고 액정표시장치(10)는 추가적으로 오프 커런트 검출부(500)와 온도 검출부(700)를 포함할 수 있다. 그리고 상기 표시패널(100)은 화상을 표시하는 표시영역(101)과 화상이 표시되지 않는 비표시영역(102)을 포함할 수 있고, 상기 비표시영역(102) 상에는 표시영역(101) 내의 박막 트랜지스터(T2)의 특성을 모니터링 하기 위한 테스트용 박막 트랜지스터부(600)가 배치될 수 있다. 즉, 상기 테스트용 박막 트랜지스터부(600)의 특성을 검출하여 이를 기초로 상기 표시영역(101) 내의 박막 트랜지스터(T2)에 인가되는 게이트 신호의 레벨을 조절함으로써, 상기 표시영역(101) 내의 박막 트랜지스터(T2)의 특성 변화에 따른 오프 커런트를 최소화할 수 있다. 또한 오프 커런트에 따라 표시영역(101) 내의 박막 트랜지스터(T2)에 인가되는 게이트 신호의 로우 레벨을 조절하는데 이는 게이트 로우 신호의 레벨에 따라서 표시영역(101) 내의 박막 트랜지스터(T2)의 오프 커런트가 달라지기 때문이다.

- [0020] 상기 표시패널(100)은 두 장의 유리기판 사이에 배치된 액정분자들을 구비한다. 이 표시패널(100)에는 데이터라 인들(D1 내지 Dm)과 게이트라인들(G1 내지 Gn)의 교차 구조에 의해 매트릭스 형태로 m×n (m, n은 양의 정수)개의 서브 화소 영역이 정의되고, 상기 서브 화소 영역 각각에 액정셀들(Clc)이 배치된다. 또한 복수의 게이트 라인과 복수의 데이터 라인의 교차에 의해 정의되는 서브 화소 영역은 제1 색을 표시하는 제1 서브 화소, 제2 색을 표시하는 제2 서브 화소 및 제3 색을 표시하는 제3 서브 화소를 포함하거나, 제1 색을 표시하는 제1 서브 화소, 제2 색을 표시하는 제2 서브 화소, 제3 색을 표시하는 제3 서브 화소 및 제4 색을 표시하는 제4 서브 화소를 포함한다. 상기 제1 색은 레드(Red)를 의미하고, 상기 제2 색은 그린(Green)을 의미하고, 상기 제3 색은 불루(Blue)를 의미하며, 상기 제4 색은 화이트(White)를 의미한다.

- [0021] 상기 표시패널(100)의 하부 유리기판에는 m 개의 데이터라인들(D1 내지 Dm), n개의 게이트라인들(G1 내지 Gn), TFT(Thin Film Transister, 박막 트랜지스터, T), TFT들에 각각 접속된 액정셀(Clc)의 화소 전극(110) 및 스토

리지 커패시터(Cst) 등을 포함한 서브 화소가 형성된다.

- [0022] 표시패널(100)의 상부 유리기판 상에는 블랙매트릭스, 컬러필터 및 공통전극(120)이 형성된다. 공통전극(120)은 TN(Twisted Nematic) 모드와 VA(Vertical Alignment) 모드와 같은 수직전계 구동방식에서 상부 유리기판 상에 형성되며, IPS(In Plane Switching) 모드와 FFS(Fringe Field Switching) 모드와 같은 수평전계 구동방식에서 화소전극(1)과 함께 하부 유리기판 상에 형성할 수 있다.

- [0023] 상기 표시패널(100)의 상부 유리기판과 하부 유리기판 각각에는 광축이 직교하는 편광판이 부착되고 액정과 접하는 내면에 액정의 프리틸트각을 설정하기 위한 배향막이 형성될 수 있다.

- [0024] 상기 데이터 구동회로(300)는 다수의 데이터 드라이버 집적회로들을 구비할 수 있다. 상기 데이터 구동회로 (300)는 타이밍 콘트롤러(200)의 제어 하에 디지털 비디오 데이터(RGB or RGBW)를 래치하고 그 디지털 비디오 데이터를 아날로그 정극성/부극성 감마보상전압으로 변환하여 정극성/부극성 데이터전압을 발생한다. 상기 다수의 데이터 드라이버 집적회로들 각각은 복수개로 그룹화된 데이터 라인(D1 내지 Dm) 각각에 데이터 신호를 제공할 수 있다. 따라서 액정표시장치의 해상도에 따라서 상기 데이터 드라이버 집적회로들의 그룹화 정도에 따라서도 상기 데이터 드라이버 집적회로들의 개수는 달라질 수 있다.

- [0025] 상기 데이터 구동회로(300)는 소스 출력 인에이블신호(SOE)가 로우 논리로 유지되는 각 수평기간 동안 데이터전 압을 데이터라인들(D1 내지 Dm)에 공급한다.

- [0026] 데이터 드라이버 집적회로들은 TCP(Tape Carrier Package) 상에 실장되어 TAB(Tape Automated Bonding) 공정에 의해 표시패널(100)의 하부 유리기판에 접합될 수 있다.

- [0027] 상기 게이트 구동회로(400)는 쉬프트 레지스터, 쉬프트 레지스터의 출력신호를 액정셀의 TFT 구동에 적합한 스윙폭으로 변환하기 위한 레벨 쉬프터, 및 레벨 쉬프터와 게이트라인(G1 내지 Gn) 사이에 접속되는 출력 버퍼 등을 포함한다. 게이트 구동회로(400)는 타이밍 콘트롤러(200)의 제어 하에 대략 1 수평기간의 펄스폭을 가지는 게이트 신호들을 게이트라인들(G1 내지 Gn)에 순차적으로 공급한다. 게이트 구동회로(400)는 TCP 상에 실장되어 TAB 공정에 의해 표시패널(100)의 하부 유리기판에 접합되거나, 또는 GIP(Gate driver In Panel) 공정에 의해 화소 어레이와 동시에 하부 유리기판 상에 직접 형성될 수 있다.

- [0028] 상기 파워부(800)는 외부 시스템으로부터 입력되는 전원을 이용하여 액정표시장치를 구동하기 위해 필요한 전원을 상기 데이터 및 게이트 구동회로(300, 400)와 타이밍 콘트롤러(200)등에 제공할 수 있다.

- [0029] 상기 타이밍 콘트롤러(200)는 표시패널(100)이 제1 내지 제4 서브 화소를 구비한 경우, 시스템보드(미도시)로부터 입력되는 디지털 비디오 데이터(RGB) RGBW 비디오 데이터로 변환하고 이를 표시패널(100)에 맞게 재정렬하여 데이터 구동회로(300)에 공급한다. 타이밍 콘트롤러(200)는 시스템보드로부터 수직/수평 동기신호(Vsync, Hsync), 데이터 인에이블(Data Enable), 클럭신호(CLK) 등의 타이밍신호를 입력 받아 데이터 구동회로(300)와 게이트 구동회로(400)의 동작 타이밍을 제어하기 위한 제어신호들(GCS, DCS)을 발생한다. 또한 상기 타이밍 콘트롤러(200)는 오프 커런트 검출부(500)를 제어하여 상기 오프 커런트 검출부(500)가 테스트용 박막 트랜지스터의 오프 커런트를 검출하도록 하고, 검출된 결과에 따라 게이트 구동회로(400)를 제어하고, 상기 게이트 구동회로(400)는 상기 타이밍 콘트롤러(200)의 제어 하에 파워부(800)로부터 제공되는 전원을 이용하여 상기 게이트 구동회로(400)를 직접 제어하여 상기 게이트 신호의 레벨을 조절할 수 있다. 또는 상기 타이밍 콘트롤러(200)는 파워부(800)를 직접 제어하여 상기 게이트 구동회로(400)로 공급되는 게이트 로우 신호 생성을 위한 전원의 레벨을 조절할 수 있다. 또는 상기 오프 커런트 검출부(500)가 검출한 오프 커런트에 관한 정보가 상기 파워부(800)에 출력되어 상기 파워부(800)로부터 출력되는 전원의 레벨 조절을 통해 상기 게이트 로우 신호의 레벨이 조절될수 있다.

- [0030] 상기 게이트 구동회로(400)를 제어하기 위한 게이트 타이밍 제어신호(GCS)는 게이트 스타트 펄스(Gate Start Pulse, GSP), 게이트 쉬프트 클럭(Gate Shift Clock, GSC), 게이트 출력 인에이블신호(Gate Output Enable, GOE) 등을 포함한다. 게이트 스타트 펄스(GSP)는 1 프레임기간 동안 그 프레임기간의 시작과 동시에 1회 발생하여 첫 번째 게이트펄스를 발생시킨다. 게이트 쉬프트 클럭(GSC)은 쉬프트 레지스터를 구성하는 다수의 스테이지들에 공통으로 입력되는 클럭신호로써 게이트 스타트 펄스(GSP)를 쉬프트시킨다. 게이트 출력 인에이블신호 (GOE)는 게이트 구동회로(400)의 출력을 제어한다.

- [0031] 상기 데이터 구동회로(300)를 제어하기 위한 데이터 타이밍 제어신호(DCS)로는 소스 스타트 펄스(Source Start Pulse, SSP), 소스 샘플링 클럭(Source Sampling Clock, SSC), 수직 극성제어신호(Polarity, POL) 및 소스 출력 인에이블신호(Source Output Enable, SOE) 등을 포함한다. 소스 스타트 펄스(SSP)는 데이터 구동회로(300)

의 데이터 샘플링 시작 타이밍을 제어하는 신호이며, 소스 샘플링 클럭(SSC)은 라이징 또는 폴링 에지에 대응하여 데이터 구동회로(300)를 구성하는 각 IC에서 데이터의 샘플링 타이밍을 제어하는 클럭신호이다. 또한, 수직 극성제어신호(Polarity, POL)는 데이터 구동회로(300)에서 출력되는 데이터 전압을 게이트라인들(G1 내지 Gn)별로 수직 극성 반전 타이밍을 제어하고, 소스 출력 인에이블신호(SOE)는 데이터 구동회로(300)의 출력 타이밍을 제어하는 역할을 한다.

- [0032] 상기 데이터 구동회로(300)는 타이밍 콘트롤러(200)의 제어에 따라 입력되는 RGBW DATA(or RGB DATA)를 래치한다. 그리고 수직 극성제어신호(Polarity, POL)를 아날로그 정극성 또는 부극성 감마보상전압(GAMMA)으로 변환하여 모든 데이터 라인(D1 내지 Dm)을 통해 동시에 표시패널(100)로 출력한다.

- [0033] 구체적으로 상기 데이터 구동회로(300)는 타이밍 콘트롤러(200)로부터 제공되는 수직 극성제어신호(POL)가 하이 논리일 때 데이터 구동회로(300)에서 출력되는 데이터 전압의 극성을 정극성으로 할 수 있고, 로우 논리일 때 데이터 구동회로(300)에서 출력되는 데이터 전압의 극성을 부극성으로 할 수 있다.

- [0034] 상기 수직 극성제어신호(POL)에 의하여 수직라인 단위로 극성을 반전할 수 있다.

- [0035] 한편 상기 표시패널(100)의 비표시영역(102)에 실장된 테스트용 박막 트랜지스터를 제1 박막 트랜지스터로 지칭하면 표시영역(101)에 실장된 박막 트랜지스터를 제2 박막 트랜지스터로 지칭할 수 있다.

- [0036] 상기 오프 커런트 검출부(500)는 비표시영역(102) 상의 테스트용 박막 트랜지스터인 제2 박막 트랜지스터의 오프 커런트(off current)를 검출하고, 상기 제2 박막 트랜지스터에 공급된 게이트 신호 중에서 검출된 오프 커런트에 대응하는 게이트 신호에 대한 정보를 타이밍 콘트롤러(200) 또는 파워부(800)에 제공할 수 있다. 상기 타이밍 콘트롤러(200) 또는 파워부(800)는 오프 커런트 검출부(500)에서 검출한 제2 박막 트랜지스터의 오프 커런트 정보에 따라서 게이트 구동회로(400)로부터 출력되는 게이트 로우 신호(VGL)의 레벨을 조절할 수 있다.

- [0037] 상기 온도 검출부(700)는 표시패널(100)의 온도를 검출하여 검출된 온도 정보를 타이밍 콘트롤러(200)에 제공할수 있다. 상기 온도 검출부(700)에 의해 검출된 상기 표시패널(100)의 온도가 제1 기 설정 온도 이상 또는 제2 기 설정 온도 이하가 되는 경우, 상기 타이밍 콘트롤러(200)는 상기 오프 커런트 검출부(500)를 제어하여 상기오프 커런트 검출부(500)가 상기 제1 박막 트랜지스터의 오프 커런트를 검출하도록 할 수 있다.

- [0038] <실시예에 따른 오프 커런트 검출부>

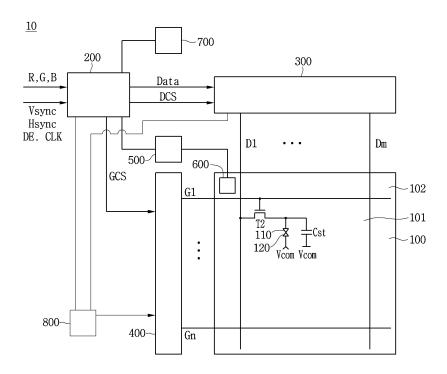

- [0039] 도 3은 본 발명의 실시예에 따른 오프 커런트 검출부를 나타낸 도면이다.

- [0040] 도 3을 참조하면, 본 발명의 실시예에 따른 오프 커런트 검출부(500)는 테스트 신호 공급부(510), 검출부(520) 그리고 피드백부(530)를 포함할 수 있다.

- [0041] 상기 오프 커런트 검출부(500)는 타이밍 콘트롤러(200)와는 별로도 구성되거나 상기 타이밍 콘트롤러(200)에 포함되어 구성될 수 있다. 그리고 상기 오프 커런트 검출부(500)는 타이밍 콘트롤러(200)에 의해 제어되어 테스트용 박막 트랜지스터부(600)의 오프 커런트를 검출하고 검출한 결과를 상기 타이밍 콘트롤러(200)로 피드백 하거나 파워부(800)로 피드백 할 수 있다.

- [0042] 상기 테스트 신호 공급부(510)는 테스트 게이트 라인(GT)과 테스트 데이터 라인(DT)을 통해 상기 제1 박막 트랜지스터(T1; 610)와 연결되어 상기 제1 박막 트랜지스터(610)의 게이트 단자(G)에 테스트 게이트 신호(Gate(T)) 및 테스트 데이터 신호(Data(T))를 공급할 수 있다. 상기 테스트 게이트 신호(Gate(T))의 하이 논리 신호에 의해 상기 제1 박막 트랜지스터(610)는 턴 온되고, 상기 테스트 데이터 신호(Data(T))는 상기 제1 박막 트랜지스터(T1)의 드레인 단자에서 소스 단자를 경유하여 화소 전극(620)에 공급되면서 저장 커패시터(Cs; 640)를 충전할 수 있다. 이 때 상기 게이트 단자(G)에 공급되는 테스트 게이트 신호(Gate(T))의 레벨은 조절될 수 있다. 즉, 상기 테스트 게이트 신호(Gate(T))의 로우 레벨은 제1 테스 게이트 신호 로우 레벨(G(T1))에서부터 제2 테스트 게이트 신호 로우 레벨(G(T2)까지 조절되며 상기 제1 박막 트랜지스터(610)의 턴 오프를 위해 상기 제1 박막 트랜지스터(610)의 게이트 단자(G)에 공급될 수 있다. 또한 상기 테스트 게이트 신호(Gate(T))의 로우 레벨은 일정한 주기를 가지고 조절될 수 있다.

- [0043] 상기 검출부(520)는 상기 제1 박막 트랜지스터(T1)의 오프 커런트를 검출할 수 있다. 구체적으로 상기 검출부 (520)는 센싱 라인(SL)을 통해 화소 전극(620)의 센싱 포인트(Sensing point; 630)와 연결되어, 상기 화소 전 극(620)의 오프 커런트를 검출할 수 있다. 상기 테스트 게이트 신호(Gate(T))의 로우 논리 신호에 의하여 제1 박막 트랜지스터(T1)가 턴 오프된 이후, 상기 검출부(520)는 센싱 라인(SL)을 통해 상기 화소 전극(620)의 전압

의 변화량을 검출하여 오프 커런트의 량을 측정할 수 있다.

- [0044] 또한 상기 검출부(520)는 상기 테스트 신호 공급부(510)로부터 테스트 게이트 신호(Gate(T))를 인가 받을 수 있다. 그리하여 상기 테스트 게이트 신호(Gate(T))의 로우 논리 신호에 동기하여, 상기 테스트 게이트 신호 (Gate(T))가 하이 논리 신호로 변화되기 전까지 상기 화소 전극(620)의 센싱 포인트(Sensing point; 630)로부터 상기 화소 전극(620)의 오프 커런트를 측정할 수 있다.

- [0045] 또한 상기 검출부(520)는 주기를 가지고 상이한 레벨의 로우 논리 신호가 되는 테스트 게이트 신호(Gate(T))에 따른 상기 화소 전극(620)의 오프 커런트가 기 설정 범위에 해당할 때 상기 테스트 게이트 신호(Gate(T))를 피드백부(530)로 출력할 수 있다.

- [0046] 상기 피드백부(530)는 상기 검출부(520)의 출력 신호를 입력 받아 상기 타이밍 콘트롤러(200) 또는 파워부(80 0)로 출력할 수 있다.

- [0047] 한편 테스트용 박막 트랜지스터부(600)에는 보상의 정확도를 고려하기 위하여 적어도 하나 이상의 제1 박막 트랜지스터(610)를 포함할 수 있다. 상기 제1 박막 트랜지스터(610)가 복수개인 경우, 복수개의 제1 박막 트랜지스터(610)들은 테스트 게이트 라인(GT)과 테스트 데이터 라인(DT) 각각에 연결되고, 검출부(520)는 복수개의 제1 박막 트랜지스터(610)들과 연결된 화소 전국(620)들 각각의 오프 커런트를 검출하여 이들의 평균치가 기 설정 범위에 해당하는지 여부를 판단하여 상기 평균치가 기 설정 범위에 해당하는 경우, 이러한 판단 결과를 상기 피드백부(530)로 출력할 수 있다.

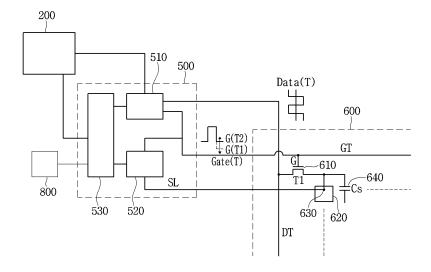

- [0048] 도 4는 제1 박막 트랜지스터의 게이트-소스 단자의 전압에 따른 오프 커런트를 나타낸 그래프이다. 그리고 도 5는 비표시영역 내의 제1 박막 트랜지스터와 표시영역 내의 제2 박막 트랜지스터를 포함하는 액정표시장치의 일부를 나타낸 도면이다.

- [0049] 도 4 및 도 5를 참조하면, 제1 박막 트랜지스터(610)는 온도에 따라서 오프 커런트(Ioff)가 쉬프트 할 수 있고, 그에 따라 게이트-소스 단자의 전압에 따른 오프 커런트 또한 달라질 수 있다. 특히 액정표시장치(10)가 고온 또는 저온의 환경이 조성될 수 있는 장소, 예를 들어 자동차 안에 설치되는 경우, 온도에 따른 오프 커런트의 쉬프트 정도는 크게 달라질 수 있다.

- [0050] 오프 커런트 검출부(500)는 표시패널(100)의 비표상영역(102)에 배치된 패드부(650)를 통해 테스트용 박막 트랜지스터부(600)의 제1 박막 트랜지스터(610)와 연결될 수 있다. 그리고 상기 오프 커런트 검출부(500)는 제1 박막 트랜지스터(610)에 로우 레벨이 가변하는 테스트 게이트 신호(Gate(T))에 대해서 상기 제1 박막 트랜지스터(610)의 오프 커런트를 검출할 수 있다. 이 때 상기 오프 커런트가 기 설정된 범위, 예를 들어 Ioff1 내지 Ioff2의 값을 만족하는 테스트 게이트 전압(Gate(T))를 측정할 수 있고, 이 때 상기 기 설정된 범위 (Ioff1~Ioff2)에는 오프 커런트가 최소가 되는 값(Ioffmin)을 포함할 수 있다. 구체적으로 제1 박막 트랜지스터(T1)에 인가되는 테스트 게이트 신호(Gate(T))의 로우 레벨를 변화시키면서 제1 박막 트랜지스터(T1)의 오프 커런트를 반복적으로 검출한다. 그리고 검출된 오프 커런트가 기 설정된 제1 오프 커런트(Ioff1) 및 제2 오프 커런트(Ioff2)가 될 때, 그 때의 테스트 게이트 신호(Gate(T))의 로우 레벨들의 정보를 피드백부(530)로 출력할 수 있다. 그리고 상기 피드백부(530)는 기 설정 범위에 해당하는 오프 커런트를 충족하는 테스트 게이트 신호에 대한 정보를 타이밍 콘트롤러(200) 또는 파워부(800)에 제공한다. 그리고 상기 타이밍 콘트롤러(200) 또는 파워부(800)는 이를 기초하여 표시영역(101) 내의 제2 박막 트랜지스터(T2)에 인가되는 게이트 신호의 로우 레벨을 상기 기 설정 범위의 오프 커런트를 생성하는 게이트 신호의 로우 레벨의 범위를 기준으로 재 설정하여, 게이트 구동회로(400)가 새롭게 설정된 게이트 로우 신호를 출력 하도록 할 수 있다.

- [0051] 이와 같이 오프 커런트가 기 설정 범위에 만족하도록 하는 테스트 게이트 신호(Gate(T))의 범위(Vgs1-Vgs2)를 검출하는 이유는, 표시영역(101) 내의 제2 박막 트랜지스터(T2)의 차징(Charging) 특성을 고려하여 게이트 로우신호의 레벨을 결정해야 하는 것이 바람직하기 때문이다. 따라서 오프 커런트가 최소에 해당 또는 최소 값에 가까운지 여부와 제2 박막 트랜지스터(T2)의 차징(Charging) 특성을 함께 고려하여 테스트 게이트 신호(Gate(T))의 범위(Vgs1-Vgs2)를 기초로 제2 박막 트랜지스터(T2)에 공급된 게이트 로우 신호의 레벨의 적정치를 결정할수 있다.

- [0052] 또한 상기 오프 커런트 검출부(500)는 테스트 게이트 신호(Gate(T))의 로우 레벨을 가변 시켜, 오프 커런트가 최소가 되는 최소 오프 커런트(Ioffmin)를 검출하고, 최소 오프 커런트(Ioffmin)를 만족시키는 테스트 게이트 신호(Gate(T))의 로우 레벨을 타이밍 콘트롤러(200) 또는 파워부(800)로 출력하여, 상기 타이밍 콘트롤러(200) 또는 파워부(800)가 게이트 구동회로(400)로부터 출력되어 표시영역(101) 내의 제2 박막 트랜지스터(T2)에 공급

되는 게이트 로우 신호의 레벨을 조절하여, 상기 제2 박막 트랜지스터(T2)의 오프 커런트를 최소화할 수 있다.

- [0053] 한편 비표시영역(102) 내의 제1 박막 트랜지스터(T1)와 표시영역(101)내의 제2 박막 트랜지스터(T2)의 종횡비 (aspect ratio), 즉 크기는 동일하게 설계를 할 수 있다.

- [0054] 즉, 상기 제1 및 제2 박막 트랜지스터(T1, T2)를 동일 환경에서 동일 조건하에서, 각각의 채널(Channel) 폭(W) 과 길이(L)에 관한 종횡비(W/L)를 동일하게 설계할 수 있다. 그리하여 상기 제1 및 제2 박막 트랜지스터(T1, T2)의 특성이 매우 유사하도록 함으로써, 모니터링을 위한 제1 박막 트랜지스터(T1)의 오프 커런트에 대한 정보를 기초하여 제2 박막 트랜지스터(T2)의 오프 커런트에 관한 정보를 획득할 수 있도록 할 수 있다.

- [0055] 한편 상기 오프 커런트(500)는 온도 검출부(600)에 의해 검출된 온도 정보에 따라서 동작여부가 결정될 수 있다. 상기 온도 검출부(600)는 주기적으로 표시패널(100)의 온도를 측정하고, 측정된 온도가 기 설정된 온도이하 또는 기 설정된 온도이상, 즉 오프 커런트의 쉬프트를 크게 이동 시킬 수 있는 온도일 때, 이러한 온도정보를 타이밍 콘트롤러(200)에 제공하여 상기 타이밍 콘트롤러(200)가 상기 오프 커런트 검출부(500)를 구동시켜 화상 표시를 위해 이용되는 게이트 신호의 로우 레벨을 조절하도록 할 수 있다.

- [0056] 이와 같은 본 발명의 실시예에 따른 액정표시장치(10)는 저온 또는 고온 구동 환경에서 최적의 게이트 신호의 레벨을 설정하기 위해 표시영역(101) 내의 제2 박막트랜지스터(T2)의 유효한 전압 영역을 기준으로 게이트 로우 신호를 가변 및 보상함으로써, 온도 변화에 따른 제2 박막트랜지스터(T2)의 특성 변화를 보상하고 그에 따라 화소 전극(110)의 홀딩 구간 내에서의 오프 커런트를 최소화하여 화질을 개선할 수 있다. 또한 주변 환경 변화에 대응하여 게이트 로우 신호의 레벨을 조절함으로써 화상의 품질을 유지할 수 있다. 또한 액정표시장치(10)의 제조 과정에서 최적의 게이트 신호의 레벨을 셋팅하는데 소요되는 시간을 줄여 공정 시간과 검사 비용을 절감할수 있다.

- [0057] 한편 본 발명의 실시예에 따른 액정표시장치(10)는 표시패널(100)의 온도와는 무관하게, 주기적으로 비표시영역 (102)의 제1 박막 트랜지스터(T1)의 오프 커런트를 검출하도록 하는 오프 커런트 검출부(500)를 포함할 수 있고, 이 경우 액정표시장치(10)는 온도 검출부(700)를 포함하지 않을 수 있다. 또한 본 발명의 실시예에 따른 액정표시장치(10)는 표시패널(100)의 표시영역(101) 내의 제2 박막 트랜지스터(T2)에 인가되는 최적의 게이트로우 신호를 셋팅하기 위한 용도로 표시패널(100)의 검사 단계에서 상기 오프 커런트 검출부(500)를 이용하고, 완제품으로 제작하여 제품으로 출하 시에는 상기 오프 커런트 검출부(500)를 제거할 수 있다. 이 경우, 실시간으로 최적의 게이트로우 신호를 설정할 수는 없으나, 액정표시장치(100)의 제품 가격을 낮출 수 있고, 검사 공정 과정에서 소요되는 시간과 비용을 절감할 수 있는 효과를 가진다. 또한 본 발명의 실시예에 따른 액정표시장치(10)는 표시패널(100)의 검사 과정에서 다양한 온도 환경에 따른 최적의 게이트로우 신호를 설정하여 별도의메모리에 기억 시켜두고, 완제품으로 출하된 경우 온도 검출부(700)의 검출 온도에 따라 메모리에 기억된 최적의 게이트로우 신호의 레벨을 기초하여 표시영역(101)의 제2 박막 트랜지스터(T2)에 공급되는 게이트 신호를 설정할 수도 있다.

- [0058] 이상에서 설명한 본 발명의 상세한 설명에서는 본 발명의 바람직한 실시 예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자 또는 해당 기술분야에 통상의 지식을 갖는 자라면 후술할 특허청구범위에 기재된 본 발명의 사상 및 기술 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허청구범위에 의해 정하여져야만 할 것이다.

#### 부호의 설명

[0059] 10 액정표시장치

100 표시패널

101 표시영역

102 비표시영역

110 화소 전극

120 공통 전극

200 타이밍 콘트롤러

- 300 데이터 구동회로

- 400 게이트 구동회로

- 500 오프 커런트 검출부

- 510 테스트 신호 공급부

- 520 검출부

- 530 피드백부

- 600 온도 검출부

- 610 제1 박막 트랜지스터

- 620 화소 전극

- 630 센싱 포인트

- 640 저장 커패시터

- 700 온도 검출부

- 800 파워부

# 도면

# 도면1

# 도면2

# 도면3

#### 도면4

# 도면5

【심사관 직권보정사항】

【직권보정 1】

【보정항목】청구범위

【보정세부항목】청구항 1

# 【변경전】

제1 박막 트랜지스터가 배치된 비표시영역과 제2 박막 트랜지스터가 배치된 표시영역을 포함하는 표시패널;

상기 제1 박막 트랜지스터의 게이트 단자의 공급되는 테스트 게이트 신호의 레벨에 따른 상기 제1 박막 트랜지스터의 오프 커런트(off current)를 검출하는 오프 커런트 검출부; 및

상기 오프 커런트의 검출 결과를 기초하여 생성된 게이트 신호를 상기 제2 박막트랜지스터에 인가하는 구동부; 를 포함하고,

상기 오프 커런트 검출부는 상기 테스트 게이트 신호의 로우 레벨을 가변 시켜, 상기 오프 커런트가 최소가 되는 최소 오프 커런트를 검출하고, 상기 최소 오프 커런트를 만족시키는 상기 테스트 게이트 신호의 로우 레벨을 타이밍 콘트롤러 또는 파워부로 출력하고,

상기 타이밍 콘트롤러 또는 상기 파워부는 상기 구동부로부터 출력되어 상기 표시영역 내의 상기 제2 박막

트랜지스터에 공급되는 상기 게이트 로우 신호의 레벨을 조절하여, 상기 제2 박막 트랜지스터의 오프 커런 트를 최소화하는 액정표시장치.

# 【변경후】

제1 박막 트랜지스터가 배치된 비표시영역과 제2 박막 트랜지스터가 배치된 표시영역을 포함하는 표시패널;

상기 제1 박막 트랜지스터의 게이트 단자의 공급되는 테스트 게이트 신호의 레벨에 따른 상기 제1 박막 트랜지스터의 오프 커런트(off current)를 검출하는 오프 커런트 검출부; 및

상기 오프 커런트의 검출 결과를 기초하여 생성된 게이트 신호를 상기 제2 박막트랜지스터에 인가하는 구동부; 를 포함하고,

상기 오프 커런트 검출부는 상기 테스트 게이트 신호의 로우 레벨을 가변 시켜, 상기 오프 커런트가 최소가 되는 최소 오프 커런트를 검출하고, 상기 최소 오프 커런트를 만족시키는 상기 테스트 게이트 신호의 로우 레벨을 타이밍 콘트롤러 또는 파워부로 출력하고,

상기 타이밍 콘트롤러 또는 상기 파워부는 상기 구동부로부터 출력되어 상기 표시영역 내의 상기 제2 박막 트랜지스터에 공급되는 상기 게이트 신호의 로우 레벨을 조절하여, 상기 제2 박막 트랜지스터의 오프 커런 트를 최소화하는 액정표시장치.